00 4i

ilan (N9

Фиг.1

Изобретение относится к вычислительной техни| е и может быть использовано в специализированных вычислителях

Цель изобретения - г овышение быстродействия

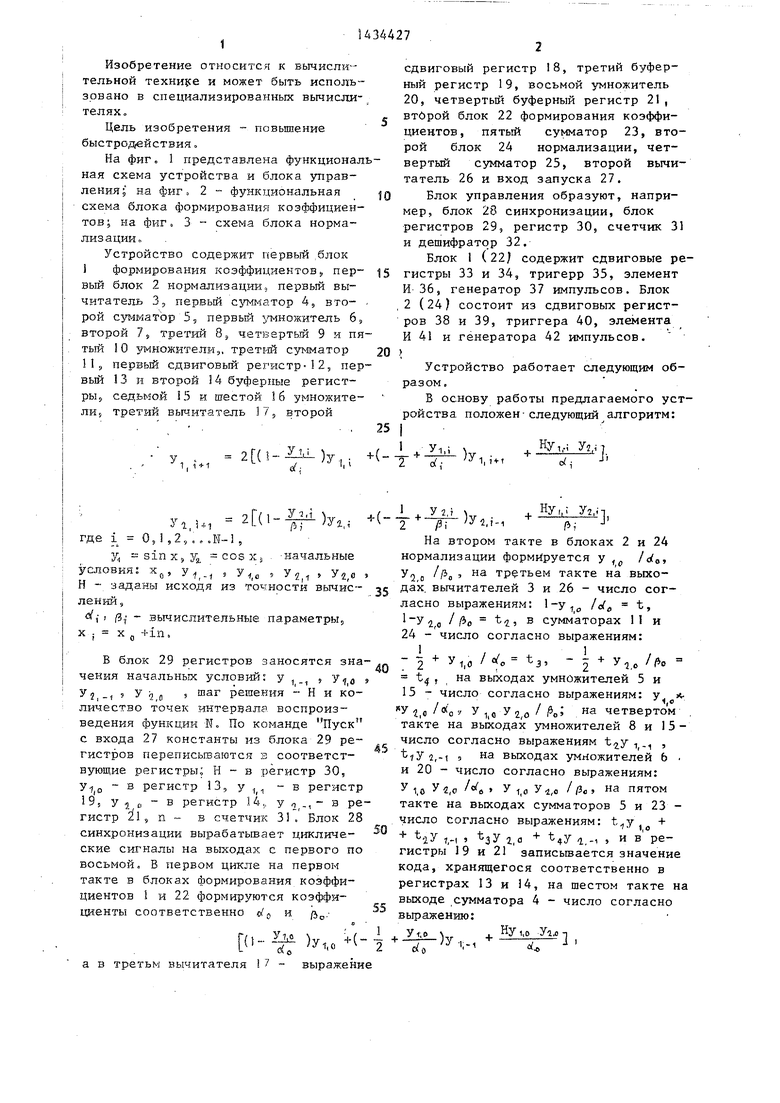

На фиг о 1 представлена функционалная схема устройства и блока управления; на фиг. 2 - функциональная схема блока формирования коэффициентов; на фиг. 3 схема блока нормализации.

Устройство содержит первый блок i формирования коэффициентов., первый блок 2 нормализации, первый вы- читатель 3 первый сумматор 4, вто- рой сумматор 5, первый хтчножитель б, второй 7, третий 8; четвертый 9 и пя5

сдвиговый регистр 18, третий буферный регистр 19, восьмой умножитель 20, четвертый буферный регистр 21 , втОрой блок 22 формирования коэффициентов, пятый сумматор 23, второй блок 24 нормализации, четвертый сумматор 25, второй вычи- татель 26 и вход запуска 27.

Блок управления образуют, например, блок 28 синхронизации, блок регистров 29, регистр 30, счетчик 31 и дешифратор 32.

Блок 1 (22) содержит сдвиговые регистры 33 и 34, тригерр 35, элемент И 36, генератор 37 импульсов. Блок 2 (24 состоит из сдвиговых регистров 38 и 39, триггера 40, элемента И 41 и генератора 42 импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Устройство для вычисления арктангенса | 1985 |

|

SU1314336A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1837320A1 |

| Устройство для вычисления координат | 1989 |

|

SU1635178A1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Устройство для воспроизведения функций @ и @ | 1989 |

|

SU1658151A1 |

| Генератор случайных чисел | 1990 |

|

SU1817093A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Целью изобретения является повышение быстродействия. Устройство содержит первый блок 1 формирования коэффициентов, первый блок 2 нормализации, первый вычитатель 3, пер- вьш сумматор 4, второй сумматор 5, первый умножитель 6, второй умножитель 7, третий умножитель 8, четвер- тьй умножитель 9, пятый умножитель 10, третий сумматор 11 первый сдвиговый регистр 12, первый буферный регистр 13, второй буферный регистр 14, пятый умножитель 15, шестой умножитель 16, третий вычитатель 57, второй сдвиговый регистр 18, третий буферный регистр 19, восьмой умножитель 20, четвертый буферный регистр 2, второй блок 22 формирования коэффициентов, пятый сумматор 23, второй блок 24 нормализации, четвертый сумматор 25, второй вычитатель 26, вход запуска 27. 3 ил. i (Л

тый 10 умножители,, третг-хй сзпФ1атор 20

11э первый сдвиговьЕЙ регистр-12, пер- Устройство работает следующим об- вый 13 н второй 14 буферные регист- разом,

ры седьмой 15 и шестой 16 умножите- В основу работы предлагаемого уст- ЛИ} третий вычитатель 17, второй ройства положенследующий алгоритм: .-/-. - , 25 I

Ну,,; У;,г i

2(У1,

с.)у.

.

У1, i + t

,

Уа,и, 2(l™)y,, где i О,1,2,...N-1,

у sin х, Jv cos Xj начальные условия: х.

о у 1,-1 у i,o У 2,1 Уг,е Н - заданы исходя из точности вычислений 5

й| { /3, - вычислительные параметры, X , X g -f-in.

В блок 29 регистров заносятся значения начальных условий; У ,., j У1 о 2 -( У о 5 реиення -Ни количество точек интервала воспроизведения функции No По команде Пуск с входа 27 константы из блока 29 регистров переписываются в соответствующие регистры; Н - в регистр 30, , в регистр 13, у , - в регистр 19, У2 о в регистр 14., у .j,., - в регистр il п - в счетчик 31 ., Блок 28 синхронизации вырабатывает циклические сигналы на выходах с первого по восьмой., В первом цикле на первом такте в блоках формирования коэффициентов i и 22 формируются коэффициенты соответственно о/ и Ьо

(,-.У 1,0

в третьм вычитателя -/

)У1,о ( 2 выражение

Ну,,; У;,г i

;

У1, i + t

,

-

1

У 2,7

)у.

Ну,,; У2,,

J5

5

/); ,1- fi,- На втором такте в блоках 2 и 24 нормализации формируется у , /а(о y,j //з„ , на третьем такте на выходах, вычитателей 3 и 26 - число согласно выражениям: l-y /«/ t, / ftf t, в сумматорах И и 24 - число согласно выражениям:

1 / / 1 / - 2 1,0 / °fo tj, - 2 y-i.c fto

t, на выходах умножителей 5 и 15 - число согласно выражениям: У, 1,« / У 1,в У 2,0 о , четвертом , такте на выходах умножителей 8 и 15- число согласно выражениям , .., , 1Уг,-1 5 иа выходах умножителей 6 . и 20 - число согласно выражениям: У 1,0 У 2,0 У 1,0 У 1,0 //Зо на пятом такте на выходах сумматоров 5 и 23 .число согласно выражениям: + + t.y ., , + ., , и в регистры 19 и 21 эаписьшается значение кода, хранящегося соответственно в регистрах 13 и 14, на шестом такте на выходе сумматора 4 - число согласно выражению:

У

)У 1,-1

Ну 1,0 У1.0

,

1(1)У,

1

ч-i

yi.fl

.°

На седьмом такте в первом и втором сдвиговых регистрах 12 и 18 происхо- (- дит запись и увеличение вдвое чисел с выходов первого сумматора 4 и третьего вычитателя 17 Соответственно.Значения sin х исозх, полученные на первом шаге решения, на восьмом так- ю те с выходов регистров 12 и 18 заносятся в регистры .13 и 14, стирая предыдущий результат. На этом завершается первый цикл работы устройства. На втоУг.о АО И второго

)у 1-, Н:)

1,Р 4,0

.

блоков нормализации соотзетственно-, вход нормализуемого числа первого блока нормализации объединен., с входом итерационной переменной первого блока формирования коэффициентов, входами первых сомно- щ телей третьего и четвертого умножителей и соединен с выходом первого буферного-; регистра, вход итерационной переменной второго блока формирования козффиинентов объединен с

ром цикле в той же последовательности 15входсУМ нормализуемого числа второго

за восемь тактов, используя в регист-блока нормализации, входами первых

pax 13 и 14 значения функций у, , у,сомножителей пятого и шестого умноа в регистрах 19 и 21 - у . У.в жителей к соединен с выходом второосуществляется вычисление значенийго буферного регистра, выход второго

функции в следующей точке yi,, У д « 20блока формирования коэффициентов соПри этом в счетчике (циклов) 31 уста-единен с входом параметра нормали- навливается число n-l. Процесс вычисления в последующих точках осуществляется в соответствующих циклах

зации второго блока нормализации, выход первого блока нормализации соединен с входом .вычитаемого первого аналогично описанному до тех пор, 25 вычитателя, входом первого слагае- .пока на восьмом такте очередного цик- мого третьего сумматора и входом ла в счетчике 31 не установится нулевая комбинация. В этом случае на

второго сомножителя пятого умножителя, выход второго блока нормализации соединен с входом вычитаемого второго навливается сигнал, приводящий к оста-ЗО вычитателя, входом первого слагаемо- новке блока управления и всего уст- го четвертого сумматора и входом вто- ройства в целом.рого сомножителя четвертого умножителя, выходы первого и второго вычи- тателей соединены с входами вторых Устройство для вычисления тригоно- 25 сомножителей третьего и шестого ум- метрических функций, содержащее три ножителей соответственно, выходы

выходе дешифратора (нуля) 32 устаФормула изобретения

сумматора, четыре умножителя, первый сдвиговый регистр и блок управления, причем выходы первого и второго умножителей соединены с входами первьк слагаемых соответственно первого и второго сумматоров, вход второго слагаемого второго сумматора соединен с выходом третьего умножителя, первый и второй выходы блока управления соединены со стробирующим входом третьего сумматора и входом сдвига первого сдвигового регистра соответственно, отличающееся тем, что, с целью повышения быстродействия, в него дополнительно введены четыре умножителя, два сумматора, три вычитателя, два блока нормализа- 1дии, два блока формирования коэффициентов,, второй сдвиговый регистр и четыре буферных регистра, причем выходы первого и второго блоков формирования коэффициентов соединены с вхо- дами параметра нормализации первого

Уг.о АО И второго

)у 1-, Н:)

1,Р 4,0

.

блоков нормализации соотзетственно-, вход нормализуемого числа первого блока нормализации объединен., с входом итерационной переменной первого блока формирования коэффициентов, входами первых сомно- щ телей третьего и четвертого умножителей и соединен с выходом первого буферного-; регистра, вход итерационной переменной второго блока фортретьего и четвёртого сумматоров соединены с входами первых сомножителей второго и седьмого умножителей

соответственно, выходы пятого и четвертого умножителей соединены с входами первых сомножителей первого и восьмого умножителей, входы вторых сомножителей второго и седьмого умножителей соединены с выходами третьего и четвертого, буферных регистров соответственно, выходы шестого и седьмого умножителей соединены с входами первого и второго слагаемых

пятого сумматора, выходы второго и пятого су маторов соединены с входом второго слагаемого первого сумматора и входом уменьшаемого третьего вычитателя соответственно, вход вычитаемого третьего вьмитателя соединен с выходом восьмого умножителя, выходы первого сумматора и третьего вычитателя соединены с информационными входами первого и второго сдвиговых регистров соответственноj выходы первого и второго сдвиговых регистров являются выходами соответственно си- иуса и косинуса устройства и соединены с информационными входами соот ветственно третьего и четвертого буферных регистров, первый тактовый выход блока управления соединен со стробирукщими входами первого и второго вычитателей, четвертого и пятого умножителей и четвертого сумматора, второй тактовый выход блока управления соединен с входом сдвига второго сдвигового регистраJ третий тактовый выход блока управления соединен со стробирующими входами первого и второго блоков формирования коэффициентов, четвертый тактовый выход блока зпправ- ления соединен со стробиругощими входами первого и второго блоков нормализации, пятый тактовый выход блока управления соединен со стробирую- щими входами умножителей с первого по третий и с шестого по восьмой, шестой тактовый выход блока управления соединен со стробирзпощими входами второго и пятого сумматоров, седьмой тактовый выход блока управления соединен со стробирующими входами первого сумматора и третьего вычи- тателя, восьмой тактовый выход блока управления соединён с синхронизирующими входами первого и второго буферных регистров, синхронйзируннцие входы третьего и четвертого буферных регистров соединены с шестым такто- ;вым выходом блока управления, причем первый и второй блоки формирования

коэффициентов каждый содержат два сдвиговых регистра, триггер, элемент И и генератор импульсов, причем стро- бирующий вход блока формирования коэффициентов соединены с входом сброса т риггера и входами записи первого и второго сдвиговых регистров блока формирования коэффициентов, входы с сдвига первого и второго сдвиговых регистров которого соединены с выходом элемента И, первый и второй входы которого соединены с выходами генератора импульсов и триггера соответственно, выход старшего разряда первого сдвигового регистра соединен с входом f, установки триггера, информационный вход первого сдвигового регистра соединен с входом итерацион- . ной переменной блока формирования коэффициентов, выход второго сдвигового регистра соединен с выходом блока формирования коэффициентов, первый информационный выход блока управления соединен с информационным входом первого буферного регистра, второй информационный выход блока управления соединен с информационным вхо- ; дом третьего буферного регистра,

третий и четвертый информационные выходы блока управления соединены с входами начальной записи второго и четвертого буферных регистров соответственно, пятый информационный выход блока зшравления соединен с входами уменьшаемого первого и второго вычитателей5 шестой информационный выход блока .управления соединен с входами вторых слагаемых

третьего и четвертого сумматоров.

40

Кб

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1182515A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1171785A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-30—Публикация

1986-11-17—Подача