О

о о

- VJ

N

Изобретение относится к автоматике и вычислительной технике.

Цель изобретения - повышение точности преобразователя.

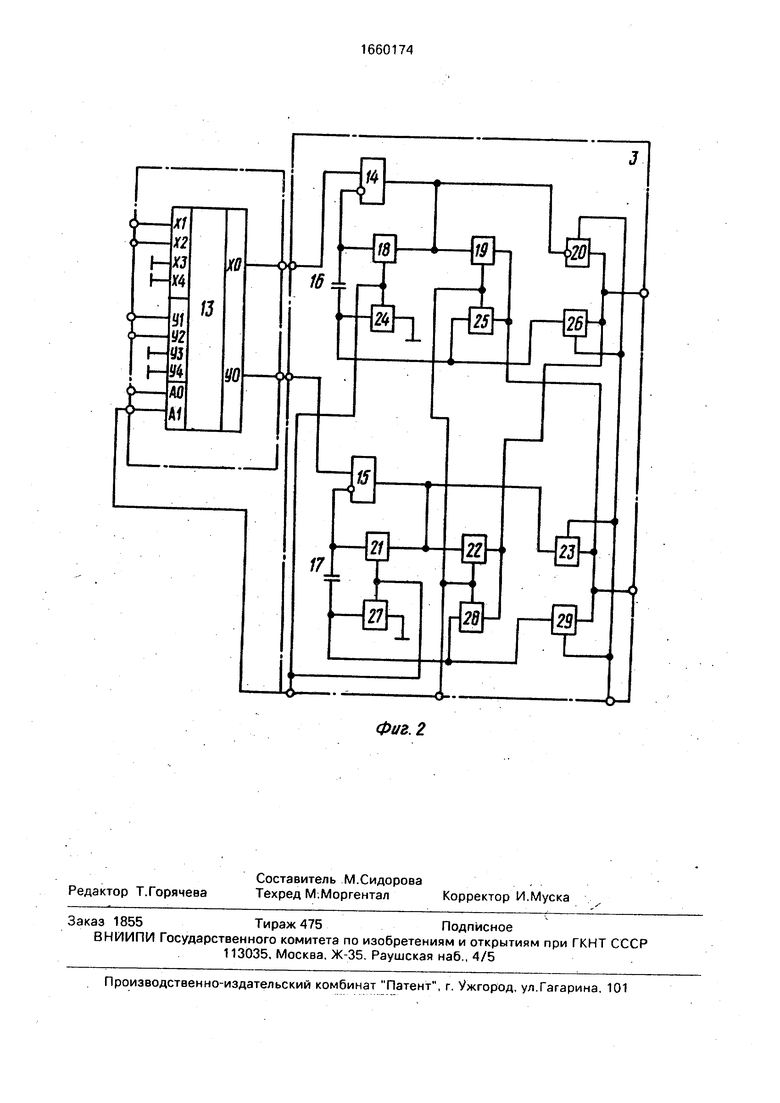

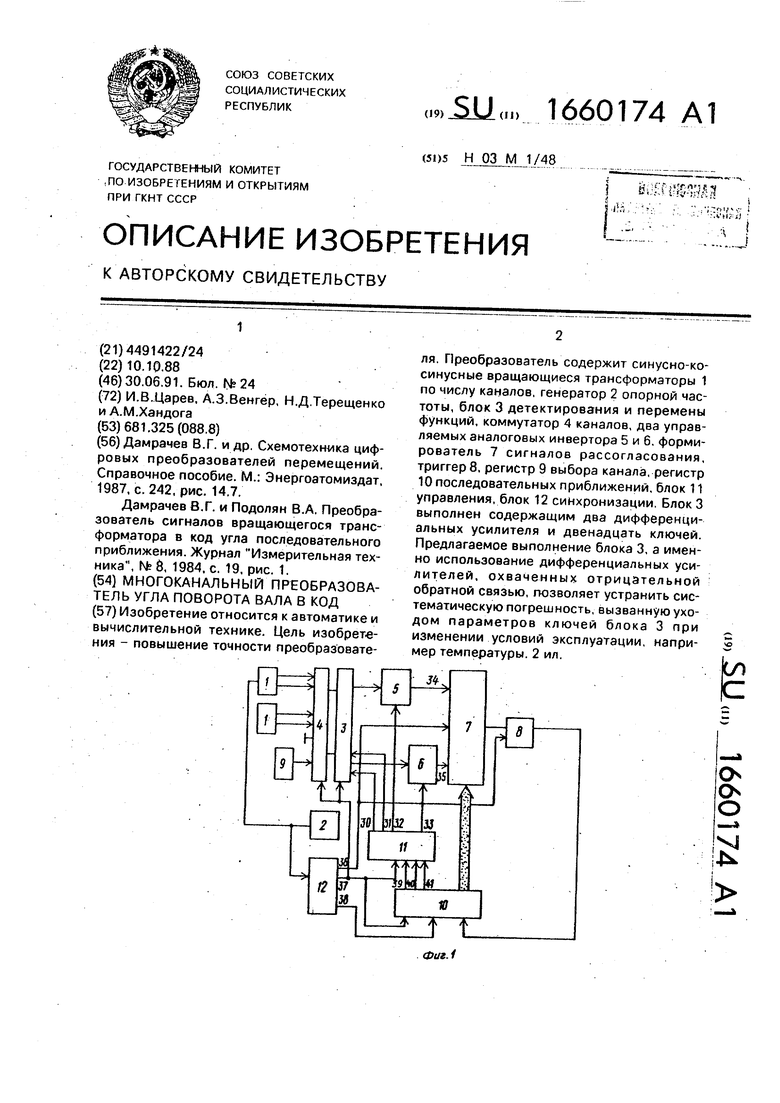

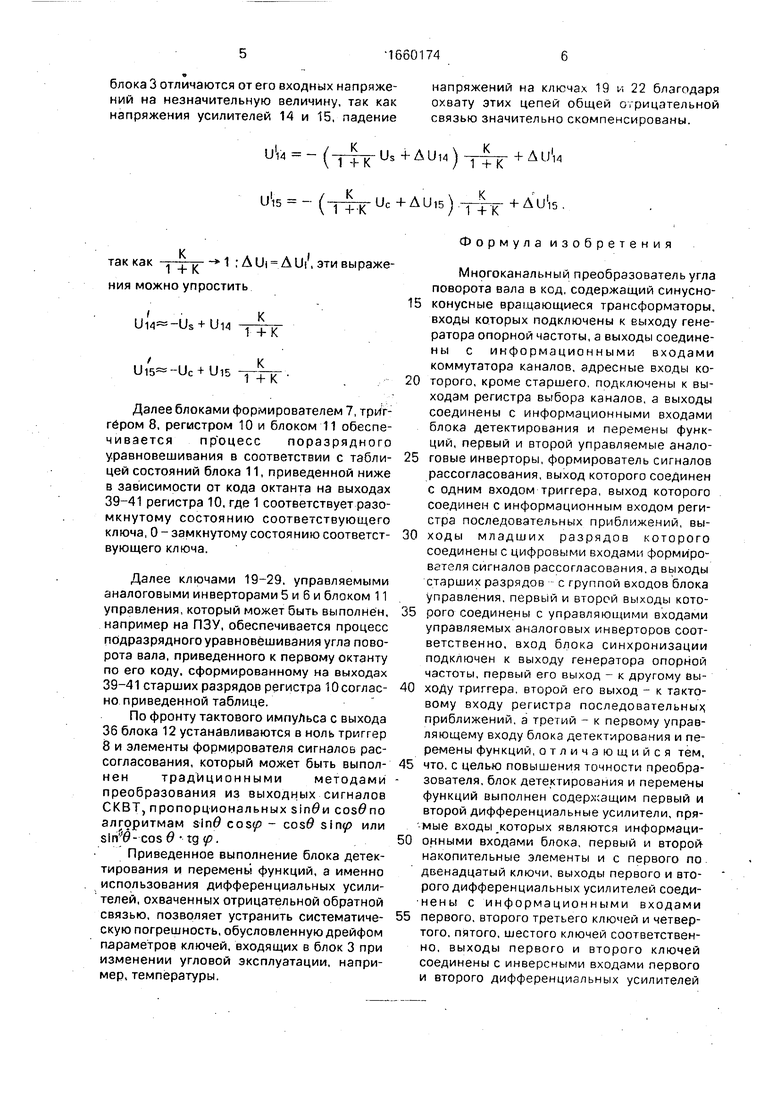

На фиг.1 приведена структурная схема предлагаемого преобразователя; на фиг.2 - структурная схема блока детектирования и перемены функций и пример выполнения коммутатора каналов для случая двухка- нального преобразователя.

Преобразователь содержит синусно-ко- синусные вращающиеся трансформаторы 1 (СКВТ), генератор 2 опорной частоты, блок 3 детектирования и перемены функций, коммутатор 4 каналов, управляемые аналоговые инверторы 5 и 6, формирователь 7 сигналов рассогласования, триггер 8, регистр 9 выбора канала, регистр 10 последовательных приближений, Ьлок 11 управления, например ПЗУ, и блок 12 синхронизации.

Коммутатор 4 каналов содержит мультиплексор 13.

Блок 3 содержит дифференциальные усилители 14 и 15, накопительные элементы 16 и 17 (конденсаторы), аналоговые ключи 18-29, выходы 30-33 блока 11, выходы 34 и 35 инверторов, выходы 36-ЗВ блока 12, выходы 39-41 регистра 10.

Преобразователь работает следующим образом.

В исходном состоянии в регистре 10 записан результат предыдущего цикла преобразования. На выходе 37 блока 12 сохраняется низкий уровень сигнала, соответствующий логическому нулю. При этом к выходам коммутатора 4 подключен канал, соответствующий адресу, поступающему с регистра 9 на младшие разряды адреса мультиплексора 13. При этом на старший разряд адреса мультиплексора 13 поступает сигнал логического нуля с выхода 37 блока 12, Этот же сигнал поступает на первый управляющий вход блока 3, замыкая его ключи 18, 24, 21 и 27. На выходах 30 и 31 блока 11 устанавливаются сигналы логической единицы, закрывающие ключи 19, 20, 22, 23, 25, 26, 28 и 29. Таким образом обеспечивается режим выборки блока 3. При этом на выходах первого и второго конденсаторов 16 и 17 устанавливаются соответственно напряжения

U16 U14

К

1 +К

Us + ДУц

1 +К

Uc + AUi5,

где Д Ui4 и Д Uis напряжения смещения соответственно первого и второго усилителей 14 и 15;

К - коэффициент усиления выбранного

типа дифференциальных усилителей (К 1). В момент положительного градиента опорного напряжения генератора 2 блок 12 формирует из последнего сигнал логической единицы на выходе 37, задержанный

на четверть периода опорного напряжения для запуска регистра 10. Одновременно он поступает на старший разряд адреса А0 мультиплексора 13, осуществляющий подключение на его выходы общей шины вне

зависимости от кода на его входах младших разрядов. Ключи 18,24,21 и 27 размыкаются и блок 3 переводится в режим хранения. По первому тактовому импульсу на выходе 38 блока 12 осуществляется сброс регистра .10

в состояние, начиная со старшего разряда 0111...1, где три старших разряда соответст- вуют-коду первого октанта угла поворота, На выходах 30-33 устанавливается код 1000, замыкающий ключи 20. 26 и 23, 29. В

этом случае образуются цепи обратной связи, выход усилителя 14, ключи 19 и 25, конденсатор 16, заряженный до напряжения Ui6, инвертирующий выход усилителя 14 и выход усилителя 15, ключи 22 и 28, конденсатор 17, заряженный до напряжения Ui, инвертирующий вход усилителя 15. Деист вне обратной связи заключается в том, что сигнал на инвертирующем входе с точностью до напряжения смещения Диподдерживается равным потенциалу шины с нулевйм потенциалом. При этом на входах усилителей 14 и 15 устанавливаются напряжения

U14 -U16

К

1 + К

+ Ли/4

UJ5 -U17

к

1 +К

+ AU/5.

где Д U14 и Д1И5 - напряжения смещения дифференциальных усилителей 14 и 15 в режиме хранения;

1/14 и Uis - напряжение на общих точках ключей 19, 25 и 22, 28 соответственно.

Последнее имеет место, так как через элементы 16 и 17 протекают незначительные токи и падение напряжения на ключах 25 и 28 значительно меньше падения напряжения на ключах 19 и 22, через которые протекают выходные токи усилителей 14 и 15. Следовательно, с учетом приведенных выше соотношений, выходные напряжения

блока 3 отличаются от его входных напряжений на незначительную величину, так как напряжения усилителей 14 и 15, падение

напряжений на ключах 19 и 22 благодаря охвату этих цепей общей о. рицательной связью значительно скомпенсированы.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

| Преобразователь угла поворота вала в код с самоконтролем | 1987 |

|

SU1462484A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1280698A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU842903A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1120383A1 |

| Преобразователь угол-код | 1986 |

|

SU1336242A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1347186A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение точности преобразователя. Преобразователь содержит синусно-косинусные вращающиеся трансформаторы 1 по числу каналов, генератор 2 опорной частоты, блок 3 детектирования и перемены функций, коммутатор 4 каналов, два управляемых аналоговых инвертора 5 и 6, формирователь 7 сигналов рассогласования, триггер 8, регистр 9 выбора канала, регистр 10 последовательных приближений, блок 11 управления, блок 12 синхронизации. Блок 3 выполнен содержащим два дифференциальных усилителя и двенадцать ключей. Предлагаемое выполнение блока 3, а именно использование дифференциальных усилителей, охваченных отрицательной обратной связью, позволяет устранить систематическую погрешность, вызванную уходом параметров ключей блока 3 при изменении условий эксплуатации, например температуры. 2 ил.

U i4 - (T Us+AUi4)T- r+AUli4 U is - ( 1 +к Uc+AUis) -y- +Au is

так как

1 +К ния можно упростить

I

1 ; A Ui A Ui, эти выражеUl4 -Us + U14

К

1 +К

Ul5«-Uc + Ui5

к

1 + К

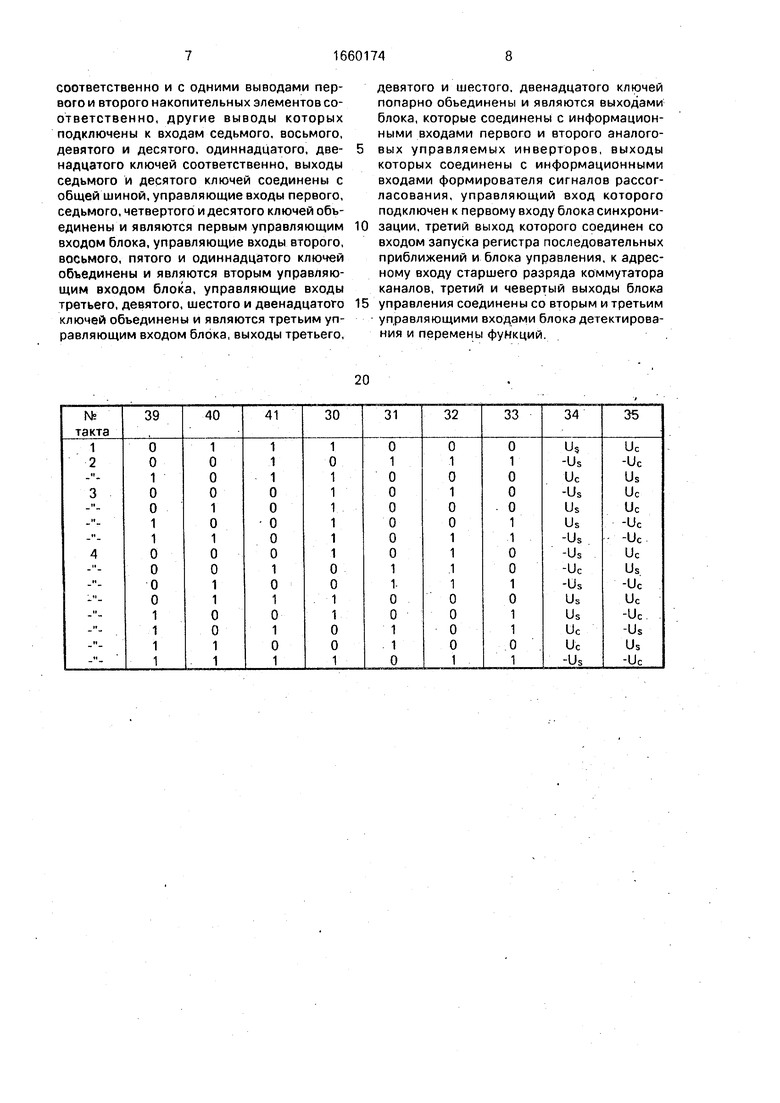

Далее блоками формирователем 7, триггером 8, регистром 10 и блоком 11 обеспечивается процесс поразрядного уравновешивания в соответствии с таблицей состояний блока 11, приведенной ниже в зависимости от кода октанта на выходах 39-41 регистра 10, где 1 соответствует разомкнутому состоянию соответствующего ключа, 0 - замкнутому состоянию соответствующего ключа.

Далее ключами 19-29. управляемыми аналоговыми инверторами 5 и 6 и блоком 11 управления, который может быть выполнен, например на ПЗУ, обеспечивается процесс подразрядного уравновешивания угла поворота вала, приведенного к первому октанту по его коду, сформированному на выходах 39-41 старших разрядов регистра Юсоглас- но приведенной таблице.

По фронту тактового импульса с выхода 36 блока 12 устанавливаются в ноль триггер 8 и элементы формирователя сигналов рассогласования, который может быть выполнен традиционными методами преобразования из выходных сигналов СКВТ, пропорциональных sin0n cos#no алгоритмам sin# cosp - cos# или sln60-cos0 .

Приведенное выполнение блока детектирования и перемены функций, а именно использования дифференциальных усилителей, охваченных отрицательной обратной связью, позволяет устранить систематическую погрешность, обусловленную дрейфом параметров ключей, входящих в блок 3 при изменении угловой эксплуатации, например, температуры.

Формула изобретения

Многоканальный преобразователь угла поворота вала в код, содержащий синусноконусные вращающиеся трансформаторы, входы которых подключены к выходу генератора опорной частоты, а выходы соедине- ны с информационными входами коммутатора каналов, адресные входы которого, кроме старшего подключены к выходам регистра выбора каналов, а выходы соединены с информационными входами блока детектирования и перемены функций, первый и второй управляемые аналоговые инверторы, формирователь сигналов рассогласования, выход которого соединен с одним входом триггера, выход которого соединен с информационным входом регистра последовательных приближений, выходы младших разрядов которого соединены с цифровыми входами формирователя сигналов рассогласования, а выходы старших разрядов с группой входов блока управления, первый и второй выходы которого соединены с управляющими входами управляемых аналоговых инверторов соответственно, вход блока синхронизации подключен к выходу генератора опорной частоты, первый его выход - к другому выходу триггера, второй его выход - к тактовому входу регистра последовательны приближений, а третий - к первому управляющему входу блока детектирования и перемены функций, отличающийся тем,

что, с целью повышения точности преобразователя, блок детектирования и перемены функций выполнен содержащим первый и второй дифференциальные усилители, прямые входы которых являются информационными входами блока, первый и второй накопительные элементы и с первого по двенадцатый ключи, выходы первого и второго дифференциальных усилителей соединены с информационными входами

первого, второго третьего ключей и четвертого, пятого, шестого ключей соответственно, выходы первого и второго ключей соединены с инверсными входами первого и второго дифференциальных усилителей

соответственно и с одними выводами первого и второго накопительных элементов со- ответственно, другие выводы которых подключены к входам седьмого, восьмого, девятого и десятого, одиннадцатого, двенадцатого ключей соответственно, выходы седьмого и десятого ключей соединены с общей шиной, управляющие входы первого, седьмого, четвертого и десятого ключей объединены и являются первым управляющим входом блока, управляющие входы второго, восьмого, пятого и одиннадцатого ключей объединены и являются вторым управляющим входом блока, управляющие входы третьего, девятого, шестого и двенадцатого ключей объединены и являются третьим управляющим входом блока, выходы третьего,

0

5

девятого и шестого, двенадцатого ключей попарно объединены и являются выходами блока, которые соединены с информационными входами первого и второго аналоговых управляемых инверторов, выходы которых соединены с информационными входами формирователя сигналов рассогласования, управляющий вход которого подключен к первому входу блока синхронизации, третий выход которого соединен со входом запуска регистра последовательных приближений и блока управления, к адресному входу старшего разряда коммутатора каналов, третий и чевертый выходы блок-а управления соединены со вторым и третьим управляющими входами блока детектирования и перемены функций.

Фиг. 2

| Дамрачев В.Г | |||

| и др | |||

| Схемотехника цифровых преобразователей перемещений | |||

| Справочное пособие | |||

| М.: Энергоатомиздат, 1987, с | |||

| Металлические подъемные леса | 1921 |

|

SU242A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Дамрачев В.Г | |||

| и Подолян В.А | |||

| Преобразователь сигналов вращающегося трансформатора в код угла последовательного приближения | |||

| Журнал Измерительная техника, № 8, 1984, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-06-30—Публикация

1988-10-10—Подача