4

&

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетное устройство | 1989 |

|

SU1676094A1 |

| Устройство для измерения девиации частоты | 1982 |

|

SU1104434A1 |

| Устройство для измерения экстремумов временных интервалов | 1983 |

|

SU1307438A1 |

| Устройство для ввода информации | 1988 |

|

SU1667121A1 |

| Преобразователь кода в период повторения импульсов | 1987 |

|

SU1495997A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| КОНТРОЛЛЕР РАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2013 |

|

RU2526762C1 |

| Устройство для формирования временного интервала | 1986 |

|

SU1352630A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к импульсной технике и может быть использовано в цифровых устройствах контроля и управления, а также в измерительно-вычислительных комплексах. Целью изобретения является расширение функциональных возможностей. Устройство содержит счетчик 1, регистр 2, D-триггер 3, D-триггер 4, инвертор 5, элемент ИЛИ 6, входы 7, 8 и 9, выход 10. 1 ил.

D

4

4i

О

о

ю о

ГО

f f f

Изобретение относится к импульсной технике и может быть использовано в цифровых устройствах контроля и управления, а также в измерительно-вычислительных комплексах.

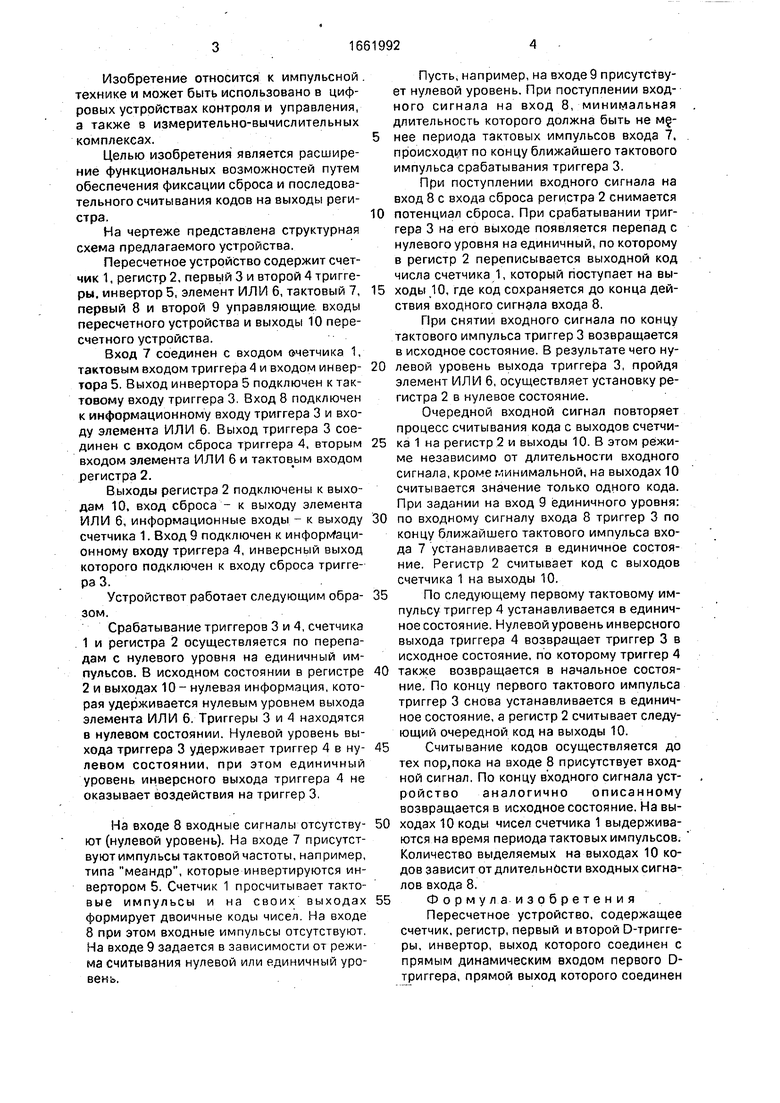

Целью изобретения является расширение функциональных возможностей путем обеспечения фиксации сброса и последовательного считывания кодов на выходы регистра.

На чертеже представлена структурная схема предлагаемого устройства.

Пересчетное устройство содержит счетчик 1, регистр 2, первый 3 и второй 4 триггеры, инвертор 5, элемент ИЛИ 6, тактовый 7, первый 8 и второй 9 управляющие входы пересчетного устройства и выходы 10 пересчетного устройства.

Вход 7 соединен с входом очетчика 1, тактовым входом триггера 4 и входом инвертора 5. Выход инвертора 5 подключен к тактовому входу триггера 3. Вход 8 подключен к информационному входу триггера 3 и входу элемента ИЛИ 6. Выход триггера 3 соединен с входом сброса триггера 4, вторым входом элемента ИЛИ 6 и тактовым входом регистра 2.

Выходы регистра 2 подключены к выходам 10, вход сброса - к выходу элемента ИЛИ 6, информационные входы - к выходу счетчика 1. Вход 9 подключен к информационному входу триггера 4, инверсный выход которого подключен к входу сброса триггера 3.

Устройствот работает следующим образом.

Срабатывание триггеров 3 и 4, счетчика

1и регистра 2 осуществляется по перепадам с нулевого уровня на единичный импульсов. В исходном состоянии в регистре

2и выходах 10- нулевая информация, которая удерживается нулевым уровнем выхода элемента ИЛИ 6. Триггеры 3 и 4 находятся в нулевом состоянии. Нулевой уровень выхода триггера 3 удерживает триггер 4 в нулевом состоянии, при этом единичный уровень инверсного выхода триггера 4 не оказывает воздействия на триггер 3,

На входе 8 входные сигналы отсутствуют (нулевой уровень). На входе 7 присутствуют импульсы тактовой частоты, например, типа меандр, которые инвертируются инвертором 5. Счетчик 1 просчитывает тактовые импульсы и на своих выходах формирует двоичные коды чисел. На входе 8 при этом входные импульсы отсутствуют. На входе 9 задается в зависимости от режима считывания нулевой или единичный уровень.

Пусть, например, на входе 9 присутствует нулевой уровень. При поступлении входного сигнала на вход 8, минимальная длительность которого должна быть не м§нее периода тактовых импульсов входа 7. происходит по концу ближайшего тактового импульса срабатывания триггера 3.

При поступлении входного сигнала на вход 8 с входа сброса регистра 2 снимается

0 потенциал сброса. При срабатывании триггера 3 на его выходе появляется перепад с нулевого уровня на единичный, по которому в регистр 2 переписывается выходной код числа счетчика 1, который поступает на вы5 ходы 10, где код сохраняется до конца действия входного сигнала входа 8.

При снятии входного сигнала по концу тактового импульса триггер 3 возвращается в исходное состояние. В результате чего ну0 левой уровень выхода триггера 3, пройдя элемент ИЛИ 6, осуществляет установку регистра 2 в нулевое состояние.

Очередной входной сигнал повторяет процесс считывания кода с выходов счетчи5 ка 1 на регистр 2 и выходы 10. В этом режиме независимо от длительности входного сигнала, кроме минимальной, на выходах 10 считывается значение только одного кода. При задании на вход 9 единичного уровня:

0 по входному сигналу входа 8 триггер 3 по концу ближайшего тактового импульса входа 7 устанавливается в единичное состояние. Регистр 2 считывает код с выходов счетчика 1 на выходы 10.

5 По следующему первому тактовому импульсу триггер 4 устанавливается в единичное состояние. Нулевой уровень инверсного выхода триггера 4 возвращает триггер 3 в исходное состояние, по которому триггер 4

0 также возвращается в начальное состояние. По концу первого тактового импульса триггер 3 снова устанавливается в единичное состояние, а регистр 2 считывает следующий очередной код на выходы 10.

5 Считывание кодов осуществляется до тех пор,пока на входе 8 присутствует входной сигнал. По концу входного сигнала устройство аналогично описанному возвращается в исходное состояние. На вы0 ходах 10 коды чисел счетчика 1 выдерживаются на время периода тактовых импульсов. Количество выделяемых на выходах 10 кодов зависит от длительности входных сигналов входа 8.

5 Формула изобретения

Пересчетное устройство, содержащее счетчик, регистр, первый и второй D-тригге- ры, инвертор, выход которого соединен с прямым динамическим входом первого D- триггера, прямой выход которого соединен

с тактовым входом регистра, информацией-кодов на выходы регистра, прямой выход

ные входы которого соединены с информа-первого D-триггера соединен с инверционными выходами счетчика, прямойсным входом сброса второго D-триггединамический счетный вход которого сое-ра, инверсный выход которого

динен с входом инвертора, прямым динами-5 соединен с инверсным входом сброса

ческимтактовым входом второго D-триггерапервого D-триггера. D-вход второго

и является тактовым входом пересчетногоD-триггера является вторым управляустройства, а D-вход первого D-триггера яв-ющим входом устройства, а первый упляется первым управляющим входом пере-равляющий вход пересчетного

счетного устройства, отличающееся10 устройства и прямой выход первого Dтем, что, с целью расширения функциональныхтриггера соединены с входами элевозможностей путем обеспечения фиксациимента ИЛИ, выход которого соединен с

сброса и последовательного считыванияинверсным входом сброса регистра.

| Пересчетное устройство | 1979 |

|

SU864578A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1468380, кл | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| Пересчетное устройство | 1979 |

|

SU864577A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1991-07-07—Публикация

1989-08-24—Подача