0 О

ел ел о

00

Изобретение откосится к импульсной ехнике и может быть использовано в устойствах автоматики и контроля.

Цель изобретения - повышение быстроействия при одновременном расширении ункциональных возможностей путем обесечения возможности индикации попадания временного интервала в диапазон опуска и индикации отсутствия входных импульсов.

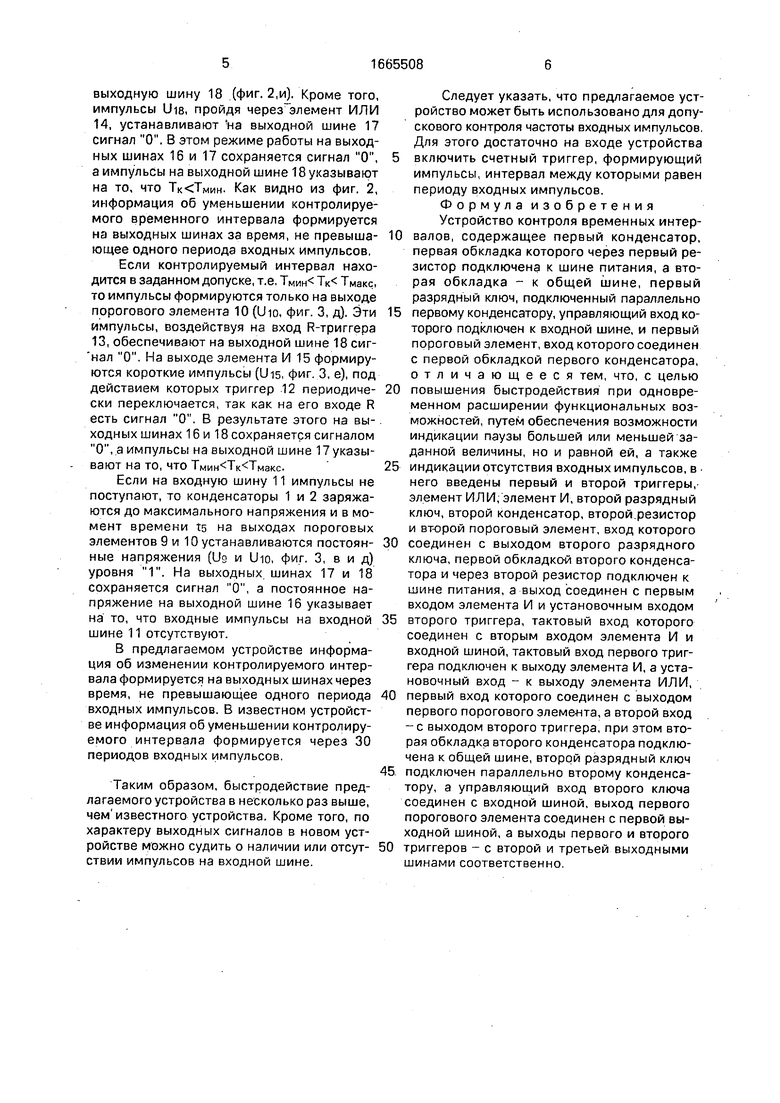

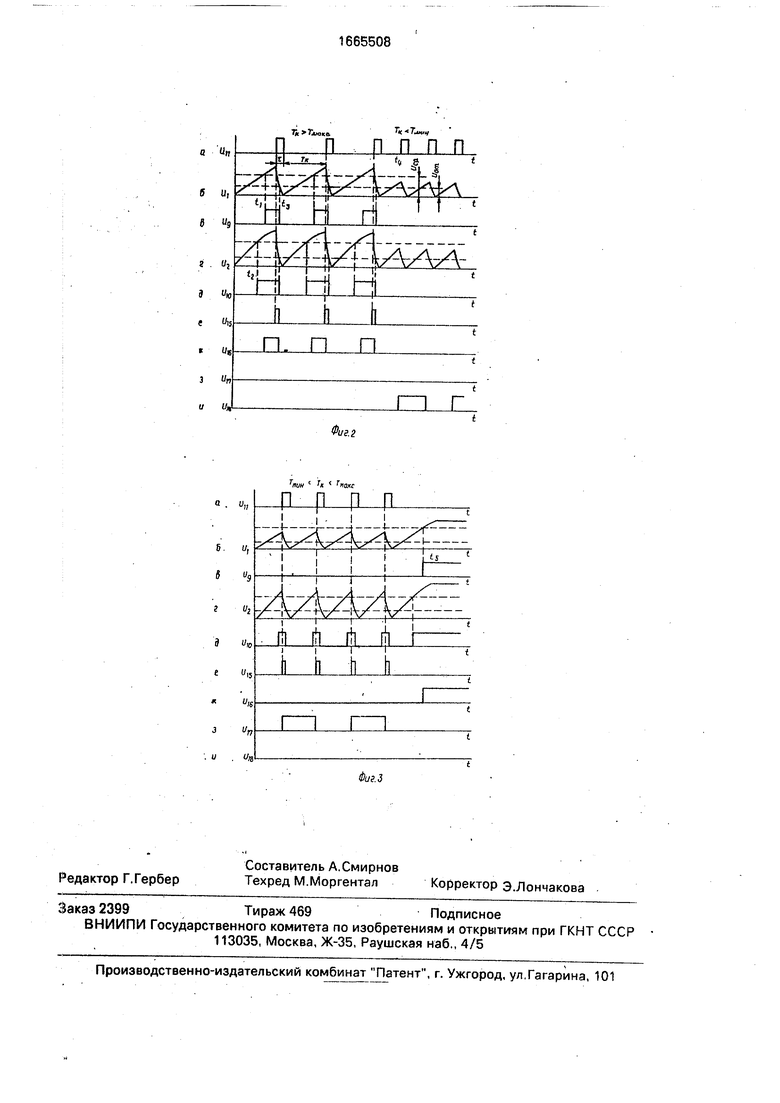

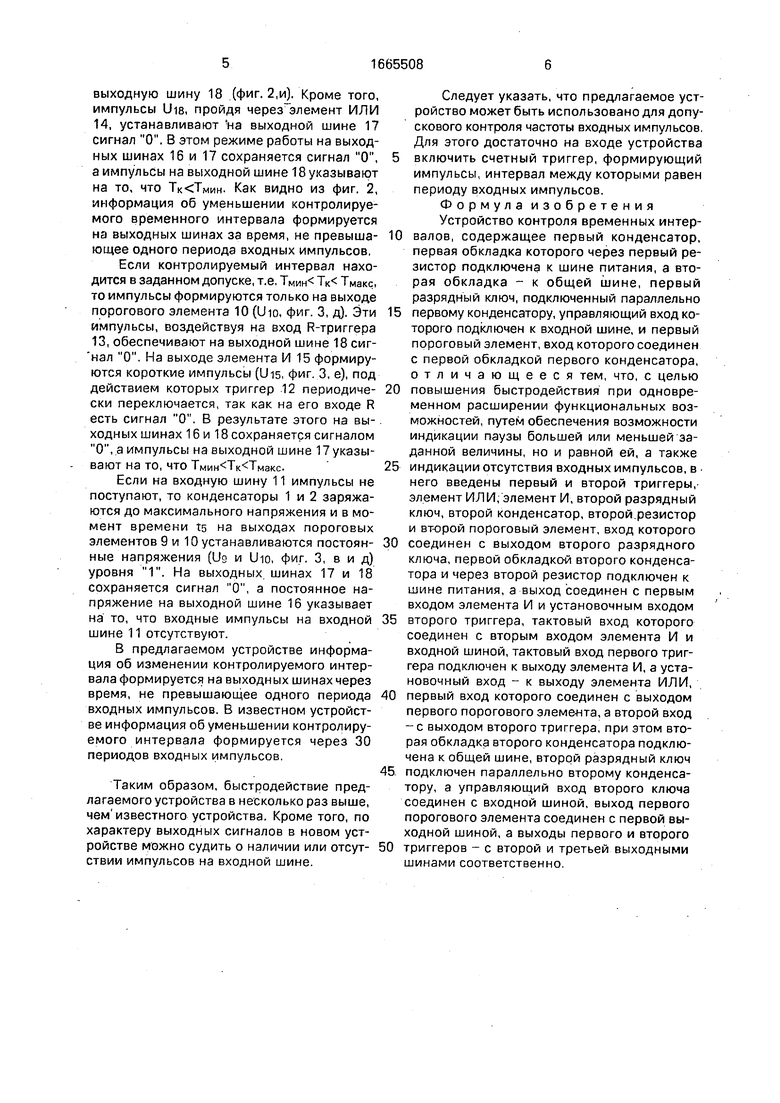

На фиг. 1 приведена структурная схема стройства; на фиг. 2 и 3 - временные диаграммы.

Устройство содержит первый 1 и второй 2 конденсаторы, первый 3 и второй 4 резисторы, шину 5 питания, общую шину 6, пер- вый 7 и второй 8 разрядные ключи,первый 9 и второй, 10 пороговые элементы, входную шину 11, первый 12 и второй 13 триггеры, элемент ИЛИ 14, элемент И 15, первую 16, вторую 17 и третью 18 выходные шины.

Первые обкладки первого 1 и второго 2 конденсаторов через соответственно первый 3 и второй 4 резисторы соединены с шиной 5, а вторые обкладки - с общей шиной 6. Первый 7 и второй 8 разрядные ключи включены параллельно первому 1 и второму 2 конденсаторам соответственно, а их управляющие входы соединены с входной шиной 11 и тактовым входом второго триггера 13, Входы первого 9 и второго 10 пороговых элементов соединены с первыми обкладками первого 1 и второго 2 конденсаторов соответственно. Выход первого порогового элемента 9 соединен с первой шиной 6 и первым входом элемента ИЛИ 14, второй вход которого соединен с третьей выходной шиной 18 и выходом второго триггера 13, а выход - с установочным входом первого триггера 12, выход которого соединен с ЁТО- рой выходной шиной 17, а тактовый вход - с выходом элемента И 15, первый вход которого соединен с выходом второго порогового элемента 10 и установочным входом второго триггера 13, а второй вход- с входной шиной 11 и тактовым входом триггера 13.

Устройство работает следующим образом.

На входную шину 11 поступают входные импульсы (Un, фиг. 2,а), длительность интервала Т« между которыми контролируют. Под действием входных импульсов разрядные ключи 7 и 8 замыкаются на время т и конденсаторы 1 и 2 полностью разряжаются- через ограничительные резисторы, Во время паузы между импульсами (интерврл Т к) конденсаторы 1 и 2 заряжаются через резисторы 3 и 4 соответственно. Постоянная времени цепи из элементов 1 и 3 выбрана

так, чтобы за время Тмакс напряжение на конденсаторе 1 достигало напряжения срабатывания Ucp, порогового элемента 9, а постоянная времени цепи из элементов 2 и

4 такова, чтобы за время Тмин напряжение на конденсаторе 2 достигало напряжения срабатывания порогового элемента 10. (Здесь Тмакс., ТМин. - максимально и минимально допустимые значения контролируе0 мого временного интервала).

Если длительность контролируемого интервала Т к более Тмакс. (фиг. 2), то в моменты времени ti и t2 напряжения на конденсаторах 1 и 2 достигают напряжения Ucp

5 (Ui и U2, фиг. 2, б и г), и на выходах пороговых элементов 9 и 10 формируются сигналы с уровнем логической единицы (в дальнейшем 1). При замыкании разрядных ключей 7 и 8 происходит быстрый разряд конденса0 торов 1 и 2, В момент времени t3 напряжения на конденсаторах 1 и 2 достигают уровня напряжения отпускания UOT пороговых элементов 9 и 10, устанавливаются уровни логического нуля (в дальнейшем О).

5 В результате этого на выходах пороговых элементов формируются прямоугольные импульсы (Ug и Uio, фиг.2, в и д) с частотой входных импульсов.

В результате обработки импульсов Un

0 и Uio элементом И 15 на его выходе формируются короткие импульсы (Uis, фиг. 2, а), которые поступают на тактовый вход триггера 12. На установочный вход R этого триггера через элемент ИЛИ 14 поступают

5 импульсы Ug. Из фиг. 2, а и е видно, что передний фронт импульсов Uis воздействует на тактовый вход триггера 12 в тот момент времени, когда на входе R есть сигнал 1, Поэтому на выходной шине 17 сохраняется

0 уровень О. На выходной шине 18 также сохраняется уровень О, так как передний фронт импульсов U ц воздействует на тактовый вход триггера 13 в тот момент, когда на его вход R воздействует уровень 1 импуль5 сов Uio. Таким образом, для рассмотренного режима работы на выходных шинах 17 и 18 сохраняются сигналы О, а импульсы на выходной шине 16 указывают на то, что Тк Т макс.

0 ТЕсли в моМент времени t4 пауза между импульсами уменьшилась настолько, что стала меньше, чем Тмин (фиг. 2), то напряжения на конденсаторах 1 и 2 не достигают уровния Ucp., и на выходах пороговых эле5 ментов 9 и 10 присутствуют сигналы О (Ug и Uio, фиг. 2, в и д). Сигналом Uio блокируется работа элемента И15 и разрешается счет импульсов Un триггером 13. В резуль: тате этого на его выходе формируются прямоугольные импульсы, поступающие на

выходную шину 18 (фиг. 2,и), Кроме того, импульсы UIB, пройдя через элемент ИЛИ 14, устанавливают на выходной шине 17 сигнал О. В этом режиме работы на выходных шинах 16 и 17 сохраняется сигнал О, а импульсы на выходной шине 18 указывают на то, что . Как видно из фиг. 2, информация об уменьшении контролируемого временного интервала формируется на выходных шинах за время, не превышающее одного периода входных импульсов,

Если контролируемый интервал находится в заданном допуске, т.е. ТМин Тк ТМакс, то импульсы формируются только на выходе порогового элемента 10 (Uio, фиг. 3, д). Эти импульсы, воздействуя на вход R-триггера 13, обеспечивают на выходной шине 18 сиг- нал О, На выходе элемента И 15 формируются короткие импульсы (Uis, фиг. 3, е), под действием которых триггер 12 периодически переключается, так как на его входе R есть сигнал О. В результате этого на выходных шинах 16 и 18 сохраняется сигналом О, а импульсы на выходной шине 17 указывают на ТО, ЧТО Тмин Тк ТМакс.

Если на входную шину 11 импульсы не поступают, то конденсаторы 1 и 2 заряжаются до максимального напряжения и в момент времени ts на выходах пороговых элементов 9 и 10 устанавливаются постоянные напряжения (Ug и Uio, фиг. 3, в и д) уровня 1. На выходных шинах 17 и 18 сохраняется сигнал О, а постоянное напряжение на выходной шине 16 указывает на то, что входные импульсы на входной шине 11 отсутствуют.

В предлагаемом устройстве информация об изменении контролируемого интервала формируется на выходных шинах через время, не превышающее одного периода входных импульсов. В известном устройстве информация об уменьшении контролируемого интервала формируется через 30 периодов входных импульсов.

Таким образом, быстродействие предлагаемого устройства в несколько раз выше, чем известного устройства. Кроме того, по характеру выходных сигналов в новом устройстве можно судить о наличии или отсутствии импульсов на входной шине.

Следует указать, что предлагаемое устройство может быть использовано для допу- скового контроля частоты входных импульсов, Для этого достаточно на входе устройства 5 включить счетный триггер, формирующий импульсы, интервал между которыми равен периоду входных импульсов.

Формула изобретения Устройство контроля временных интер- 0 валов, содержащее первый конденсатор, первая обкладка которого через первый резистор подключена к шине питания, а вторая обкладка - к общей шине, первый разрядный ключ, подключенный параллельно 5 первому конденсатору, управляющий вход которого подключен к входной шине, и первый пороговый элемент, вход которого соединен с первой обкладкой первого конденсатора, отличающееся тем, что, с целью

0 повышения быстродействия при одновременном расширении функциональных возможностей, путем обеспечения возможности индикации паузы большей или меньшей заданной величины, но и равной ей, а также

5 индикации отсутствия входных импульсов, в него введены первый и второй триггеры, элемент ИЛИ, элемент И, второй разрядный ключ, второй конденсатор, второй резистор и второй пороговый элемент, вход которого

0 соединен с выходом второго разрядного ключа, первой обкладкой второго конденсатора и через второй резистор подключен к шине питания, а выход соединен с первым входом элемента И и установочным входом

5 второго триггера, тактовый вход которого соединен с вторым входом элемента И и входной шиной, тактовый вход первого триггера подключен к выходу элемента И, а установочный вход - к выходу элемента ИЛИ,

0 первый вход которого соединен с выходом первого порогового элемента, а второй вход -с выходом второго триггера, при этом вторая обкладка второго конденсатора подключена к общей шине, второй разрядный ключ

5 подключен параллельно второму конденсатору, а управляющий вход второго ключа соединен с входной шиной, выход первого порогового элемента соединен с первой выходной шиной, а выходы первого и второго

0 триггеров - с второй и третьей выходными шинами соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь одиночных импульсов | 1983 |

|

SU1160548A1 |

| Преобразователь напряжения в частоту | 1986 |

|

SU1378062A1 |

| Преобразователь двоичного кода во временной интервал | 1983 |

|

SU1115223A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту | 1982 |

|

SU1102035A1 |

| Формирователь установочного импульса | 1987 |

|

SU1448396A1 |

| Дуплексная система передачи данных с временным разделением сигналов | 1990 |

|

SU1782336A3 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1239867A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU984041A1 |

| Цифроаналоговая следящая система | 1989 |

|

SU1700536A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и контроля. Цель изобретения - повышение быстродействия при одновременном расширении функциональных возможностей путем обеспечения возможности индикации попадания временного интервала в диапазон допуска и индикации отсутствия входных импульсов. Для достижения цели в устройство, содержащее конденсатор 1, резистор 3, разрядный ключ 7, первый пороговый элемент 9 и входную шину 11, введены триггеры 12, 13, элемент ИЛИ 14, элемент И 15, конденсатор 2, регистор 4, разрядный ключ 8 и второй пороговый элемент 10. На конденсаторах 1, 2 во время пауз между входными импульсами формируются нарастающие напряжения. При превышении этими напряжениями уровней, соответствующих Tмин и Tмакс, срабатывают пороговые элементы 9, 10. Логические элементы и триггеры формируют необходимые выходные сигналы. На чертеже показаны также шины 5, 6 питания и выходные шины 16 - 18. 3 ил.

| Устройство допускового контроля импульсов по длительности | 1978 |

|

SU790266A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля частоты | 1979 |

|

SU836599A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-07-23—Публикация

1989-08-11—Подача