со

Nl

00

о о: IND

Изобретение относится к импульсной технике и предназначено для использования в системах сбора и обработки информации различного наз- качения, системах автоматического управления и регулирования.

Целью изобретения является повышение быстродействия.

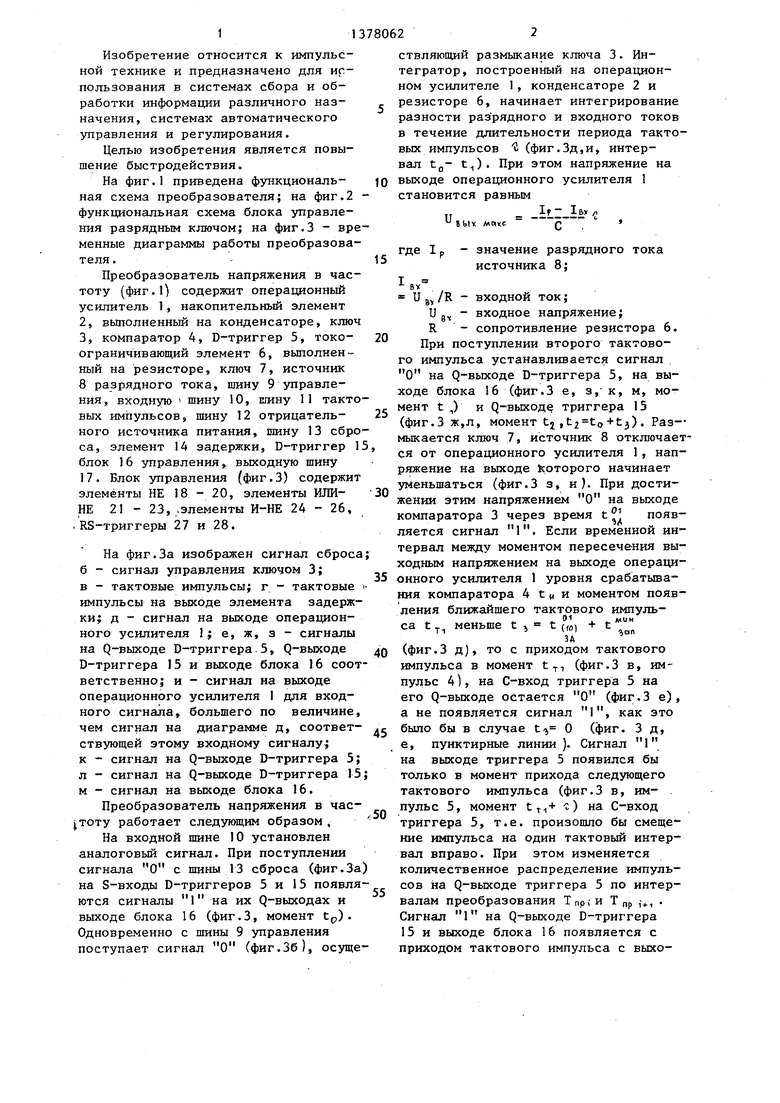

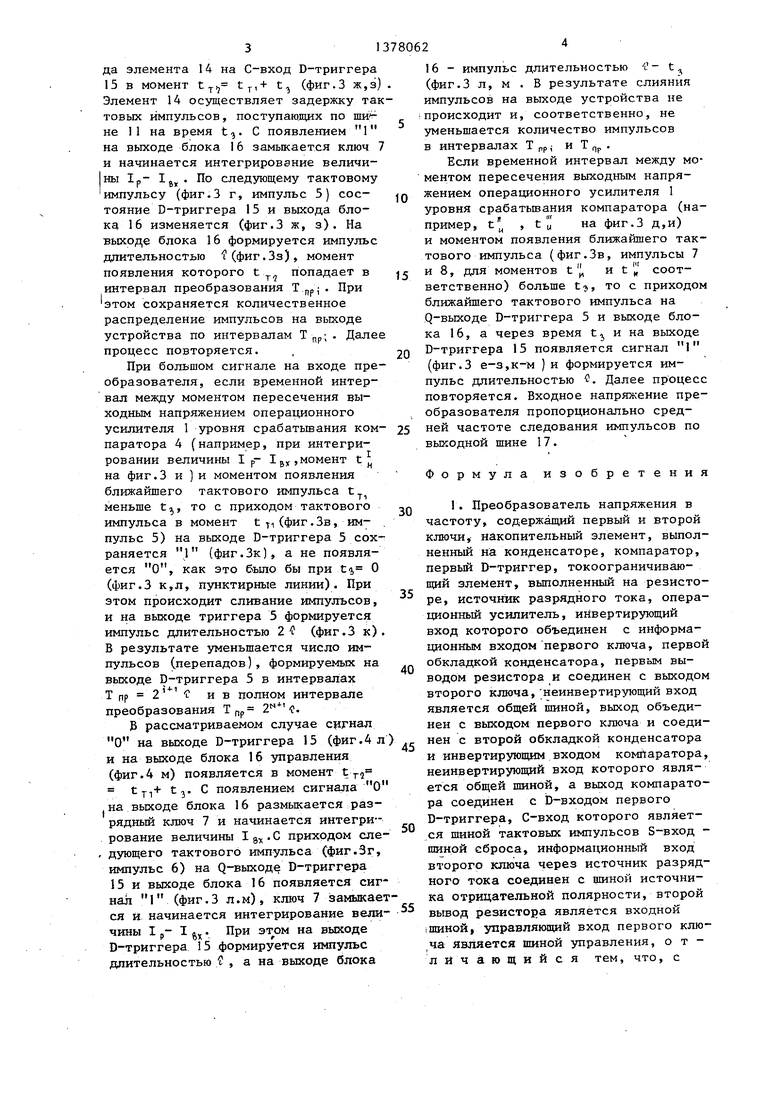

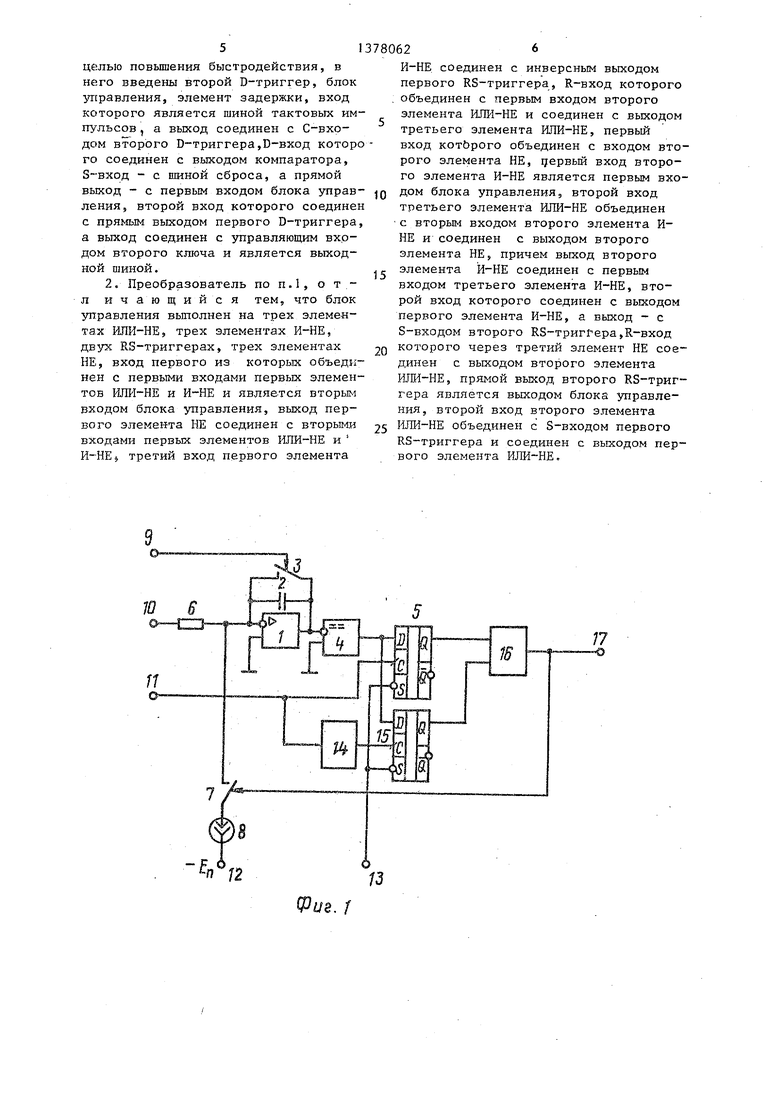

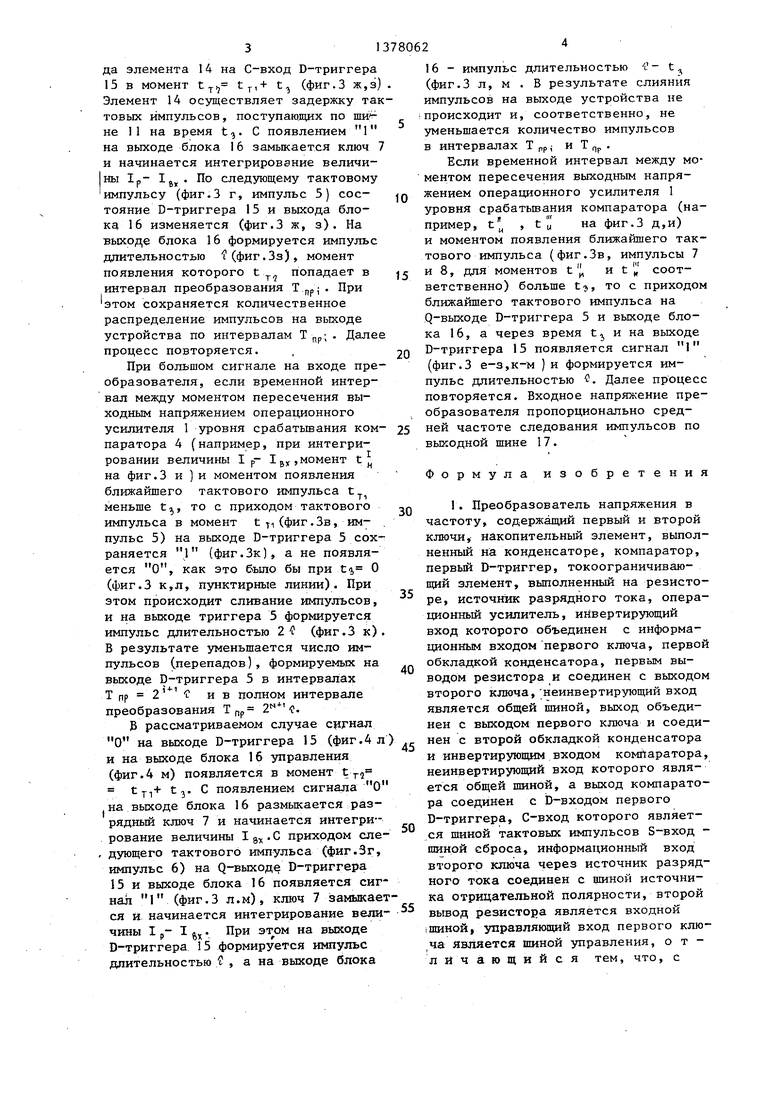

На фиг.) приведена функциональ- ная схема преобразователя; на фиг.2 - функциональная схема блока управления разрядным ключом; на фиг.З - временные диаграммы работы преобразователя.-

Преобразователь напряжения в частоту (фиг.1) содержит операционный усилитель 1, накопительный элемент

2,выполненный на конденсаторе, ключ

3,компаратор 4, D-триггер 5, токо- ограничивающий элемент 6, выполненный на резисторе, ключ 7, источник

8 разрядного тока, шину 9 управления, входную I шину 10, шину П тактовых импульсов, шину 12 отрицатель- ного источника питания, шину 13 сброса, элемент 14 задержки, D-триггер 15 блок 16 управления,, выходную шину 17. Блок управления (фиг.З) содержит элементы НЕ 18 - 20, элементы ИЛИ- НЕ 21 - 23, элементы И-НЕ 24 - 26, . RS-триггеры 27 и 28.

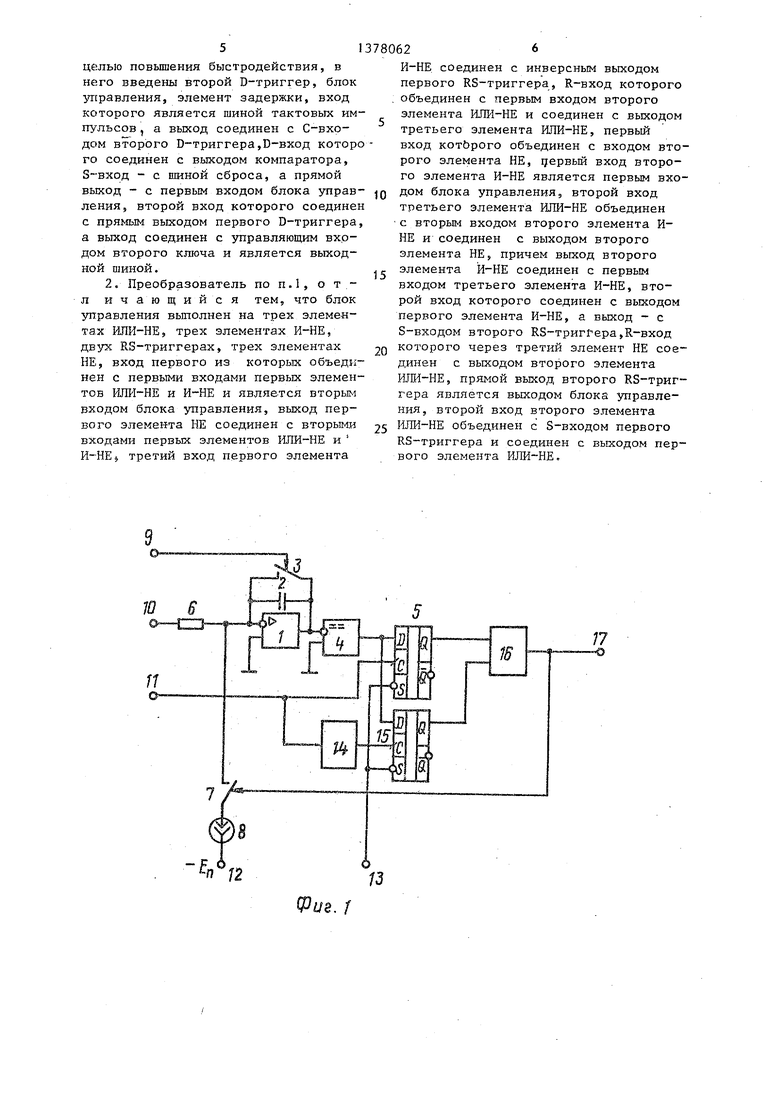

На фиг.За изображен сигнал сброса; б - сигнал управления ключом 3;

в - тактовые импульсы; г - тактовые импульсы на выходе элемента задержки; д - сигнал на выходе операционного усилителя 1; е, ж, з - сигналы на Q-выходе D-триггера 5, Q-выходе D-триггера 15 и выходе блока 16 соответственно; и - сигнал на выходе операционного усилителя 1 для входного сигнала, большего по величине, чем сигнал на диаграмме д, соответствующей этому входному сигналу; к - сигнал на Q-выходе D-триггера 5; л - сигнал на Q-выходе D-триггера 15 м - сигнал на выходе блока 16.

Преобразователь напряжения в час- тоту работает следующим образом ,

На входной шине 10 установлен аналоговый сигнал. При поступлении сигнала О с шины 13 сброса (фиг.За) на S-входы D-триггеров 5 и 15 появляются сигналы 1 на их Q-выходах и выходе блока 16 (фиг.З, момент tp). Одновременно с шины 9 управления поступает сигнал О (фиг.Зб), осуще

ствляющий размыкание ключа 3. Интегратор, построенный на операционном усилителе 1, конденсаторе 2 и резисторе 6, начинает интегрирование разности раз рядного и входного токов в течение длительности периода тактовых импульсов и (фиг.3д,и, интервал tg- t,). При этом напряжение на выходе операционного усилителя 1 становится равным

If - Ibx /1

и

BblY МПХС

ю 15

20

25, 30

35

45

0

50

55

где IP - значение разрядного тока источника 8;

I в.

и j /R - входной ток;

и g - входное напряжение;

R - сопротивление резистора 6. При поступлении второго тактового импульса устанавливается сигнал О на Q-выходе D-триггера 5, на выходе блока 16 (фиг.З е, з, к, м, момент t ) и Q-выходе триггера 15 (фиг.З ж,л, момент tj,t2 to+t3). Раз-- мыкается ключ 7 источник 8 отключается от операционного усилителя 1, напряжение на выходе Которого начинает уменьшаться (фиг.З з, и). При достижении этим напряжением О на выходе компаратора 3 через время t j появляется сигнал 1. Если временной интервал между моментом пересечения вы- ходньм напряжением на выходе операционного усилителя 1 уровня срабатывания компаратора 4 t ц и моментом появления ближайшего тактового импульса t меньше t t (о, + t

ЗА

(фиг.З д), то с приходом тактового импульса в момент (фиг.З в, импульс 4), на С-вход триггера 5 на его Q-выходе остается О (фиг.З е), а не появляется сигнал I, как это было бы в случае t О (фиг. 3 д, е, пунктирные линии ). Сигнал 1 на выходе триггера 5 появился бы только в момент прихода следующего тактового импульса (фиг.З в, импульс 5, момент tti+ J) на С-вход триггера 5, т.е. произошло бы смещение импульса на один тактовый интервал вправо. При этом изменяется количественное распределение импульсов на Q-выходе триггера 5 по интервалам преобразования Тпр;и Т „р ,Vi . Сигнал 1 на Q-выходе D-триггера 15 и выходе блока 16 появляется с приходом тактового импульса с выхоэлементав момент

14 на С-вход D-триггера

да

15 в момент t,j Ст-,+ t, (фиг.З ж,з) . Элемент 14 осуществляет задержку тактовых импульсов, поступающих по ши не 11 на время t С появлением 1 на выходе блока 16 замыкается ключ 7 и начинается интегрирование величины 1„- Ij, . По следующему тактовому

IP импульсу (фиг.З г, импульс 5) состояние D-триггера 15 и выхода блока 16 изменяется (фиг.З ж, з). На выходе блока 16 формируется импульс длительностью D(фиг.За), момент появления которого попадает в интервал преобразования Т „„j . При этом сохраняется количественное распределение импульсов на вькоде

устройства по интервалам Т

пр.

процесс повторяется.

При большом сигнале на входе преобразователя, если временной интервал между моментом пересечения выходным напряжением операционного усилителя 1 уровня срабатьшания компаратора 4 (например, при интегрировании величины I р- Ig,момент t

на фиг.3 и )и моментом появления ближайшего тактового импульса t меньше t,,, то с приходом тактового импульса в момент t i (Фиг.Зв, импульс 5) на выходе D-триггера 5 сохраняется 1 (фиг.Зк), а не появляется О, как это было бы при t4 О (фиг.З к,л, пунктирные линии). При этом происходит сливание импульсов, и на выходе триггера 5 формируется импульс длительностью 21) (фиг.З к). В результате уменьшается число импульсов (.перепадов) , формируемьос на выходе D-триггера 5 в интервалах

Тпр ив полном интервале

N+I,

преобразования Тпр 2 Ч.

В рассматриваемом случае с|1гнал О на выходе D-триггера 15 (фиг.4л и на выходе блока 16 управления (фиг.4 м) появляется в момент t -j t. С появлением сигнала О на выходе блока 16 размыкается разрядный ключ 7 и начинается интегрирование величины I их приходом следующего тактового импульса (фиг.Зг, импульс 6) на Q-вькоде D-триггера 15 и выходе блока 16 появляется сиг нал 1 (фиг.З л.м), ключ 7 :замьжает ся и начинается интегрирование вели

чины

ьfexПри этом на выходе D-триггера 15 формируется импульс длительностью , а на выходе блока

.

10

15

20

25

30

35

40

45

) - 50

16 - импульс длительностью i - t (фиг.З л, м . в результате слияния импульсов на выходе устройства не происходит и, соответственно, не уменьшается количество импульсов в интервалах Трр,- и Т .

Если временной интервал между моментом пересечения выходным напряжением операционного усилителя 1 уровня срабатьшания компаратора (например, t y t u на фиг.З д,и) и моментом появления ближайшего тактового импульса (фиг.Зв, импульсы 7 и 8, для моментов t |, и соответственно) больше t }, то с приходом ближайшего тактового импульса на Q-выходе D-триггера 5 и выходе блока 16, а через время t, и на выходе D-триггера 15 появляется сигнал 1 (фиг.З е-з,к-м ) и формируется импульс длительностью . Далее процесс повторяется. Входное напряжение преобразователя пропорционально средней частоте следования импульсов по выходной шине 17.

Формула изобретения

1. Преобразователь напряжения в частоту, содержащий первый и второй ключи, накопительный элемент, выполненный на конденсаторе, компаратор, первый D-триггер, токоограничиваю- Ещй элемент, выполненный на резисторе, источник разрядного тока, операционный усилитель, инвертирующий вход которого объединен с информационным входом первого ключа, первой обкладкой конденсатора, первым выводом резистора и соединен с выходом второго ключа,;неинвертирующий вход является общей шиной, выход объединен с выходом первого ключа и соединен с второй обкладкой конденсатора и инвертирующим входом комПаратора, неинвертирующий вход которого является общей шиной, а выход компаратора соединен с Ь-входом первого D-триггера, С-вход которого является шиной тактовых импульсов S-вход - шиной сброса, информационный вход второго ключа через источник разрядного тока соединен с шиной источника отрицательной полярности, второй вывод резистора является входной ;шиной, управляющий вход первого клю- ча является шиной управления, отличающийся тем, что, с

це;лыо повышения быстродействия, в введены второй D-триггер, блок ут равления, элемент задержки, вход которого является шиной тактовых импульсов , а выход соединен с С-вхо- дом второго В-триггера,В-вход которого соединен с выходом компаратора, S-вход - с шиной сброса, а прямой выход - с первым входом блока управления, второй вход которого соединен с прямым выходом первого D-триггера, а выход соединен с зшравляющим входом второго ключа и является выходной шиной.

2. Преобразователь по п.1, о т - л ичающийся тем, что блок утгравления вьтолнен на трех элвме«- та.х ИЛИ-НЕ, трех элементах И-НЕ, двух К3 триггерах, трех элементах НЕ, вход первого из которых объединен с первыми входами первых элементов ИЛИ-НЕ и И-НЕ и является вторым входом блока управления, выход первого элемента НЕ соединен с вторыми входами первых элементов ИЛИ-НЕ и И-HEj третий вход первого элемента

И-НЕ. соединен с инверсным выходом первого RS-триггера, R-вход которого объединен с первым входом второго элемента ИЛИ-НЕ и соединен с выходом третьего элемента ИЛИ-НЕ, первый вход котЬрого объединен с входом второго элемента НЕ, цервый вход второго элемента И-НЕ является первым входом блока управления, второй вход третьего элемента ИЛИ-НЕ объединен с вторым входом второго элемента И- НЕ и соединен с выходом второго элемента НЕ, причем выход второго элемента И-НЕ соединен с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, а выход - с S-входом второго RS-триггера,R-вход

которого череэ третий элемент НЕ соединен с выходом второго элемента ИЛИ-НЕ, прямой выход второго RS-триггера является выходом блока управления, второй вход второго элемента

ЮТИ-НЕ объединен с Б-входом первого RS-триггера и соединен с выходом первого элемента ИЛИ-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1239867A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Помехоустойчивый преобразователь напряжения в интервал времени | 1985 |

|

SU1283972A1 |

| Многоканальный аналого-цифровой преобразователь | 1987 |

|

SU1444945A1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Преобразователь напряжения в интервал времени | 1988 |

|

SU1649662A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

Изобретение относится к импульсной технике и может быть использовано в системах сбора и обработки информации различного назначения, системах автоматического управления и регулирования. Изобретение позволяет повысить быстродействие. Это достигается путем повышения стабильности временного положения выходных импульсов за счет введения в преобразователь, содержащий операционный усилитель 1, компаратора 4, ключей 3, 7, источника 8 разрядного тока, D-триггера 5, элемента задержки. 1 з.п.ф-лы, 3 ил.

1 г

Т

я и

Tnaift

tKV

V

| Аналого-цифровой преобразователь | 1983 |

|

SU1106013A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-28—Публикация

1986-06-30—Подача