-S

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый фазометр | 1983 |

|

SU1132252A1 |

| Устройство для передачи и приема двух сигналов по одному проводу | 1989 |

|

SU1741281A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ВЕЩЕСТВ С ПОМОЩЬЮ УЛЬТРАЗВУКОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2169906C2 |

| Фазометр | 1976 |

|

SU569965A1 |

| Аналого-цифровой низкочастотный фазометр | 1990 |

|

SU1780042A1 |

| Устройство для управления многофазным преобразователем частоты | 1982 |

|

SU1023621A1 |

| Устройство для управления вентильным преобразователем со слежением | 1988 |

|

SU1607061A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

Изобретение может быть использовано в устройствах измерения фазового сдвига. Цель - повышение точности измерения сдвига фаз. Аналоговый фазометр содержит усилители - ограничители 1 и 2, интеграторы 3 и 4, разрядные ключи 5 и 6, компараторы 7 и 8, ограничители 9 и 10 верхнего уровня, ограничители 11 и 12 нижнего уровня и выходной сумматор 13. Цель достигается за счет использования компараторов 7 и 8 для управления разрядными ключами, а ограничителей 9 - 12 - для гарантированного обеспечения напряжения на одних входах компараторов 7 и 8, превышающего напряжение на их других входах. 2 ил.

Фиг.1

о о о ю

Os VI

ограничители 11 и 12 нижнего уровня и выходной сумматор 13. Цель достигается за счет использования компараторов 7 и 8 для управления разрядными ключами л ш рани

Изобретение относится к технике электрических измерений, а именно к измерению угла фазового сдвига между двумя гармоническими сигналами.

Цель изобретения - повышение точно- сти измерения сдвига фаз входных сигналов

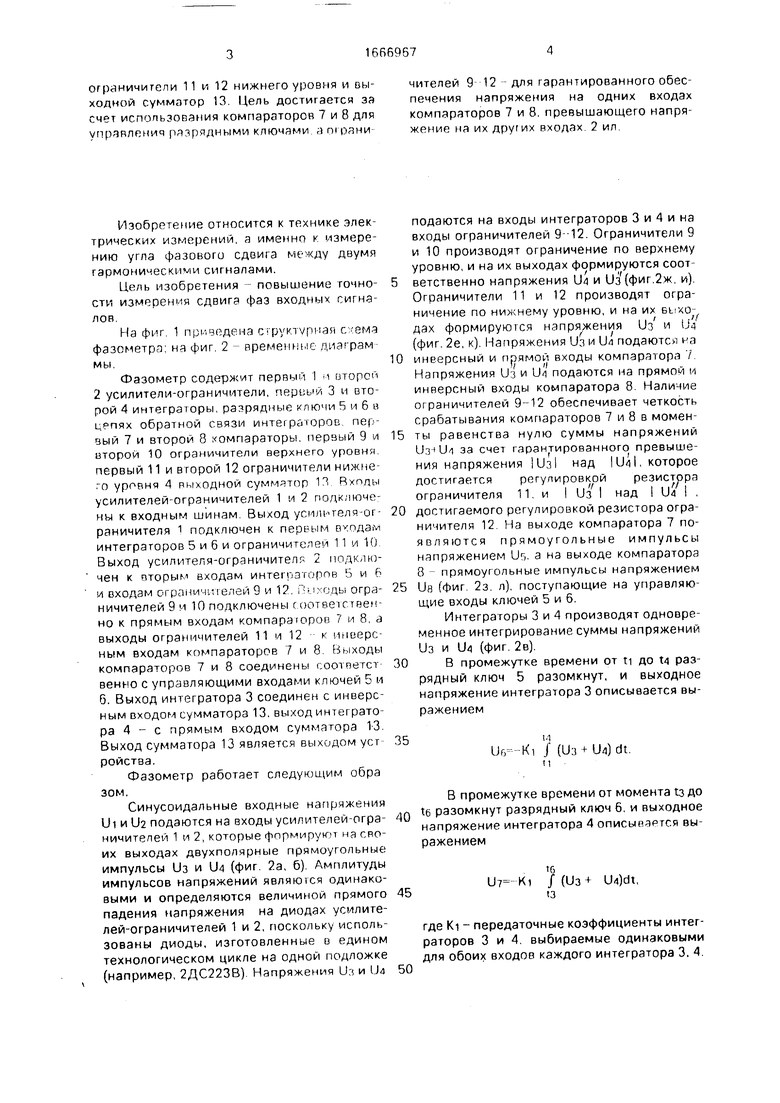

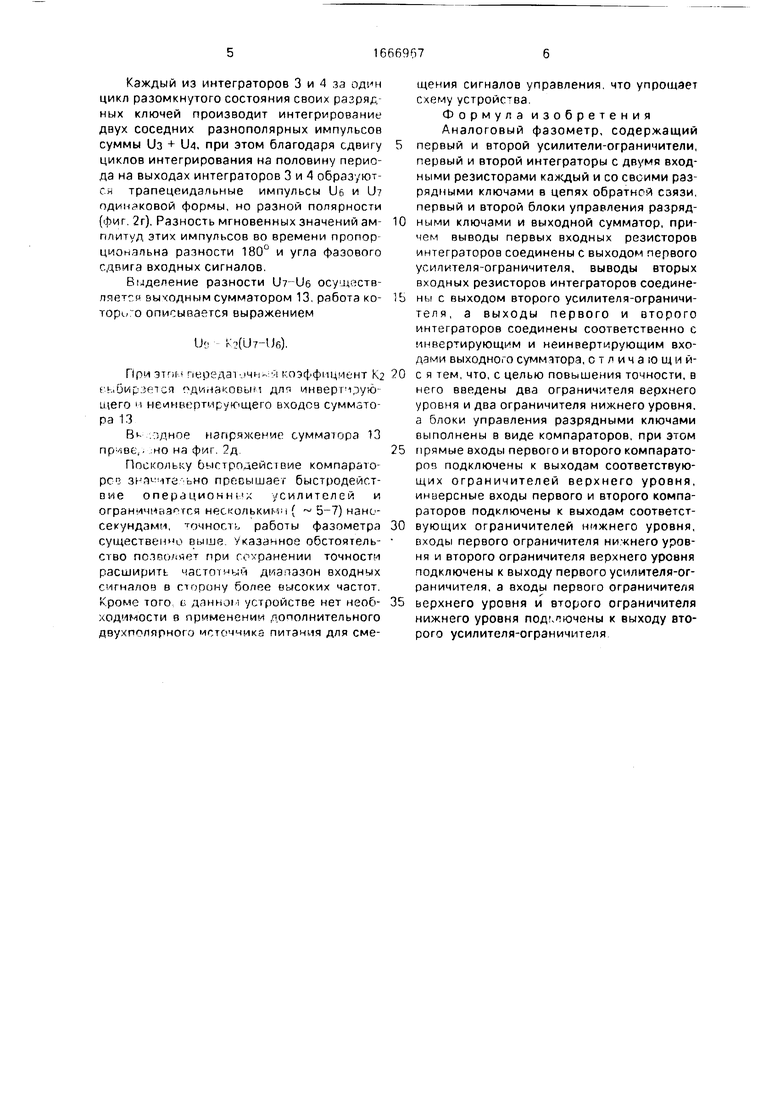

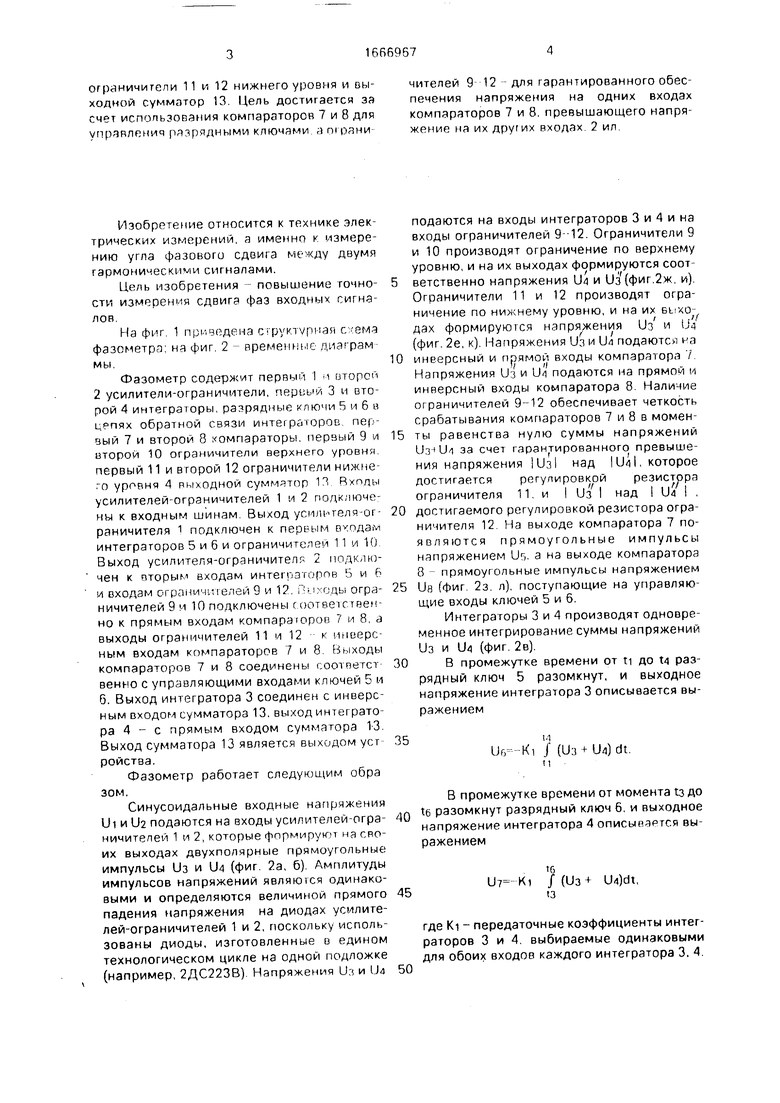

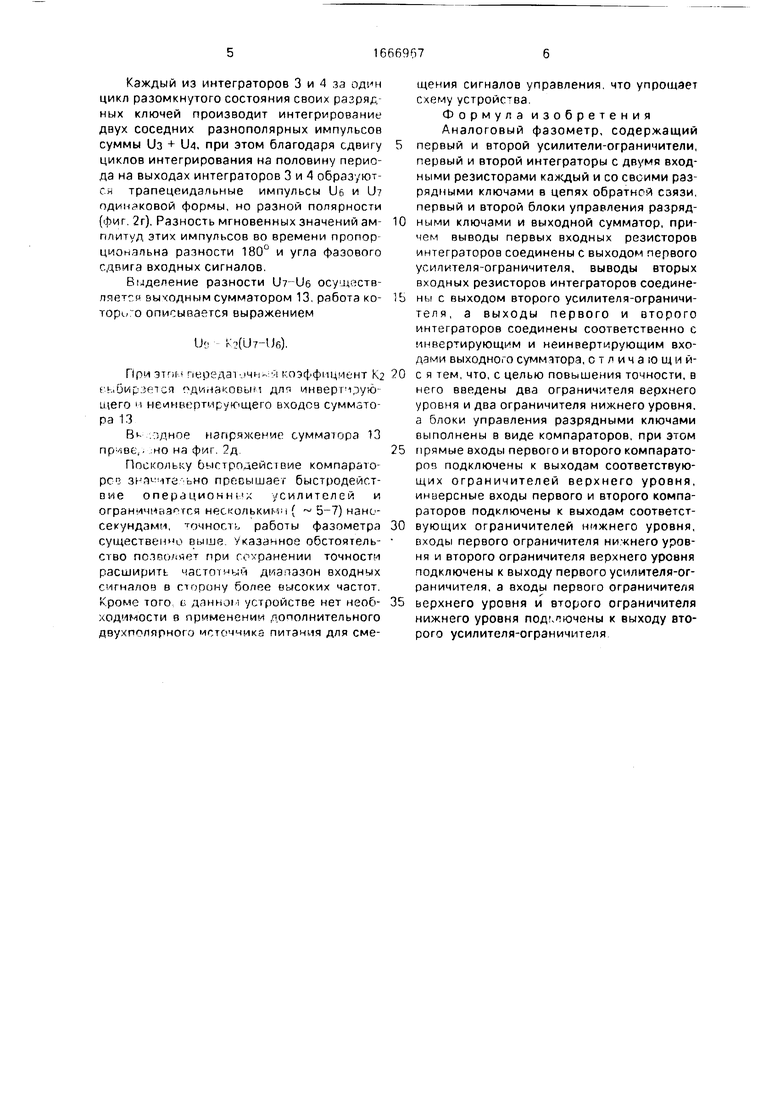

На фиг 1 приведена с румурпая фазометра на фиг 2 - временные дияграм мы.

Фазометр содержит первый I и иторон 2 усилители-ограничители, первый 3 и второй 4 интеграторы, разрядные ключи 5 и 6 в цепях обратной связи интеграторов первый 7 и второй 8 компараторы, первый 9 и второй 10 ограничители верхнего уровня первый 11 и второй 12 ограничители нижнего уровня 4 выходной суммятор П Входы усилителей-ограничителей 1 и 2 подключены к входным шинам Выход усилителя-ог- раничителя 1 подключен к первым обидам интеграторов 5 и 6 и ограничителей 11 и 10 Выход усилителя-ограничителя 2 подключен к вторым входам интегпзгоров 5 и 6 и входам ограничтелей 9 и 1 огра- ничителей 9 и 10 подключены соответственно к прямым входам компараторов 7 и 8, а выходы ограничителей 11 и 12 к инверсным входам компараторов 7 и 8 Выходы компараторов 7 и 8 соединены (.оответст венно с управляющими входами ключей 5 и б. Выход интегратора 3 соединен с инверсным входом сумматора 13. выход интегратора 4 - с прямым входом сумматора 13 Выход сумматора 13 является выходом уст ройства.

Фазометр работает следующим обра зом.

Синусоидальные входные напряжения Ui и U2 подаются на входы усилителей-ограничителей 1 и 2, которые формируют на своих выходах двухполярные прямоугольные импульсы Уз и 1)4 (фиг 2а, б) Амплитуды импульсов напряжений являючся одинаковыми и определяются величиной прямого падения напряжения на диодах усилителей-ограничителей 1 и 2, поскольку использованы диоды, изготовленные в едином технологическом цикле на одной подложке (например, 2ДС223В) Напряжения Уз и LM

чителей 9 12 - для гарантированного обеспечения напряжения на одних входах компараторов 7 и 8. превышающего напряжение на их других входах 2 ил

иУ

подаются на входы интеграторов 3 и 4 и на входы ограничителей 9--12. Ограничители 9 и 10 производят ограничение по верхнему уровню, и на их выходах формируются соответственно напряжения U4 и Уз (фиг.2ж, и) Ограничители 11 и 12 производят ограничение по нижнему уровню, и на их дах формируются напряжения Уз и (фиг. 2е, к). Напряжения Уз и Ш подаются на инверсный и прямой входы компаратора 7 Напряжения Уз и подаются на прямой м инверсный входы компаратора 8 Наличие ограничителей 9-12 обеспечивает четкость срабатывания компараторов 7 и 8 в моменты равенства нулю суммы напряжений Ib-tLM за счет гарантированного превышения напряжения 1Уз над ILUl, которое достигается регулировкой резистора ограничителя 11. и I Уз I над I U4 I , достигаемого регулировкой резистора ограничителя 12 На выходе компаратора 7 появляются прямоугольные импульсы напряжением У,. а на выходе компаратора 8 - прямоугольные импульсы напряжением Ua (фиг 2з, л), поступающие на управляющие входы ключей 5 и б.

Интеграторы 3 и 4 производят одновременное интегрирование суммы напряжений Уз и U4 (фиг, 2в).

В промежутке времени от ti до t4 разрядный ключ 5 разомкнут, и выходное напряжение интегратора 3 описывается выражением

14

Ur,--Ki / (Уз + U4)dt и

В промежутке времени от момента 1з до te разомкнут разрядный ключ 6. и выходное напряжение интегратора 4 ОПИСЫРЗРТСЯ выражением

Ki / (Уз + U4)dt,

13

где Ki - передаточные коэффициенты интеграторов 3 и 4. выбираемые одинаковыми для обоих входов каждого интегратора 3. 4.

Каждый из интеграторов 3 и 4 за один цикл разомкнутого состояния своих разрядных ключей производит интегрирование двух соседних разнополярных импульсов суммы Уз + U4, при этом благодаря сдвигу циклов интегрирования на половину периода на выходах интеграторов 3 и 4 образуются трапецеидальные импульсы Ue и U одинаковой формы, но разной полярности (фиг. 2г). Разность мгновенных значений ам- плитуд этих импульсов во времени пропорциональна разности 180° и угла фазового сдвига входных сигналов.

Выделение разности Uy-Ue осуществляете выходным сумматором 13, работа ко- тори о описывается выражением

Up K:().

При этм-чередат i4H ч коэффициент К.2 ь К|бир) одинаковым дл инвертирующего и неинвертирующего ьходсэ сумматора 13

BI- :дное напряжение сумматора 13 пр /ше,. но на фиг. 2д

Поскольку быстродействие компараторе1 зня - чте-ьно превышает быстродействие операционных усилителей и ограничивается нескольким 5-7) наносекундами, точность работы фазометра существенно выше указанное обстоятель- ство позволяет при сохранении точности расширить частотный диапазон входных сигналов в сторону более высоких частот. К роме того с данном устройстве нет необ- ходимости в применении дополнительного двухполярното источника питания для смещения сигналов управления, что упрощает схему устройства.

Формула изобретения Аналоговый фазометр, содержащий первый и второй усилители-ограничители, первый и второй интеграторы с двумя входными резисторами каждый и со своими разрядными ключами в цепях обратной сзязи, первый и второй блоки управления разрядными ключами и выходной сумматор, причем выводы первых входных резисторов интеграторов соединены с выходом первого усилителя-ограничителя, выводы вторых входных резисторов интеграторов соединены с выходом второго усилителя-ограничителя, а выходы первого и второго интеграторов соединены соответственно с инвертирующим и неинвертирующим входами выходного сумматора, отличающий- с я тем, что, с целью повышения точности, в него введены два ограничителя верхнего уровня и два ограничителя нижнего уровня. а блоки управления разрядными ключами выполнены в виде компараторов, при этом прямые входы первого и второго компараторов подключены к выходам соответствующих ограничителей верхнего уровня, инверсные входы первого и второго компараторов подключены к выходам соответствующих ограничителей нижнего уровня, входы первого ограничителя нижнего уровня и второго ограничителя верхнего уровня подключены к выходу первого усилителя-ограничителя, а входы первого ограничителя верхнего уровня и второго ограничителя нижнего уровня под ючены к выходу второго усилителя-ограничителя

фиг. 2

| Авторское свидетельство СССР N: 1236899, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-07-30—Публикация

1988-11-15—Подача