Для достижения поставленной цели в известное устройство введены дополнительные интеграторы 22-25, вычитаю- лще блоки 26 и 27, суммарно-разностный масштабный усилитель 28. Формирователь 1 (2) состоит из усилителя- ограничителя 29 (30), формирователя 31 (32) логических уровней с парафаз- ныни выходамис Образованы новые свяИзобретение относится к измерительной технике и предназначено для измерения и индикации разности фаз двух синусоидальных сигналов, а также может быть использовано при по- строении преобразователей сдвига фаз сигналов в цифровой код и является усовершенствованием известного фазометра по авт. св. № 1205057,

Цель изобретения - повышение точности измерения разности фаз при малых уровнях входных сигналов и расширение динамического диапазона цифрового фазометра.

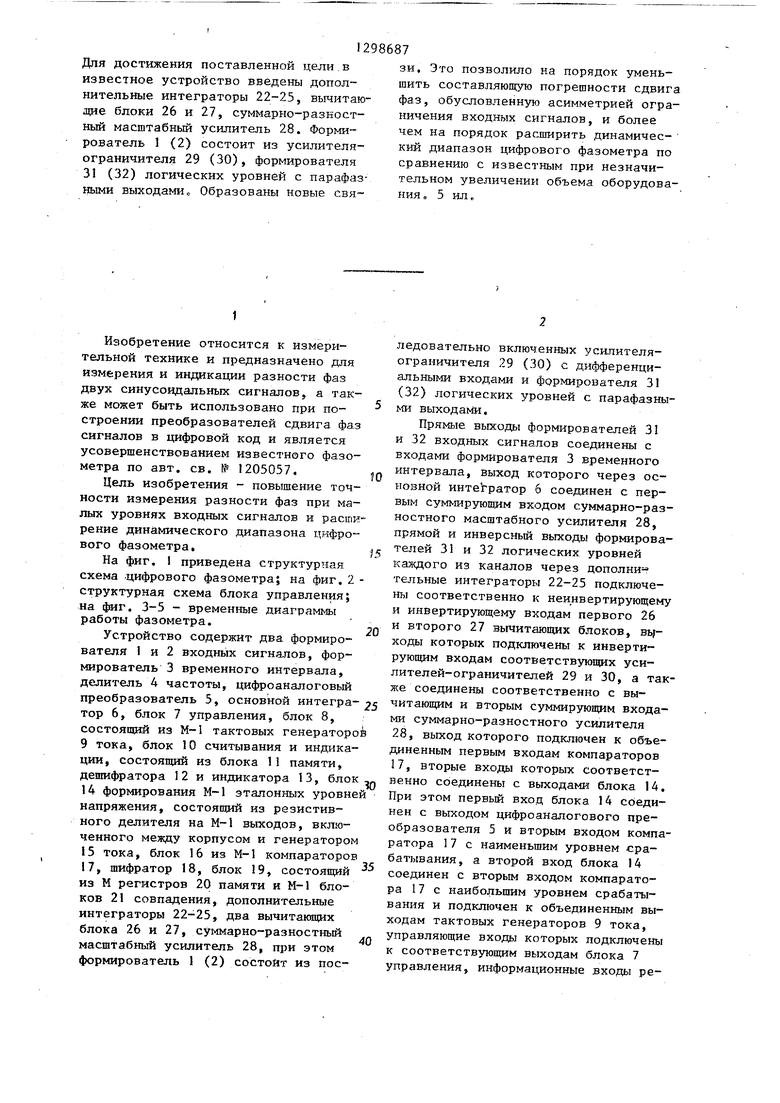

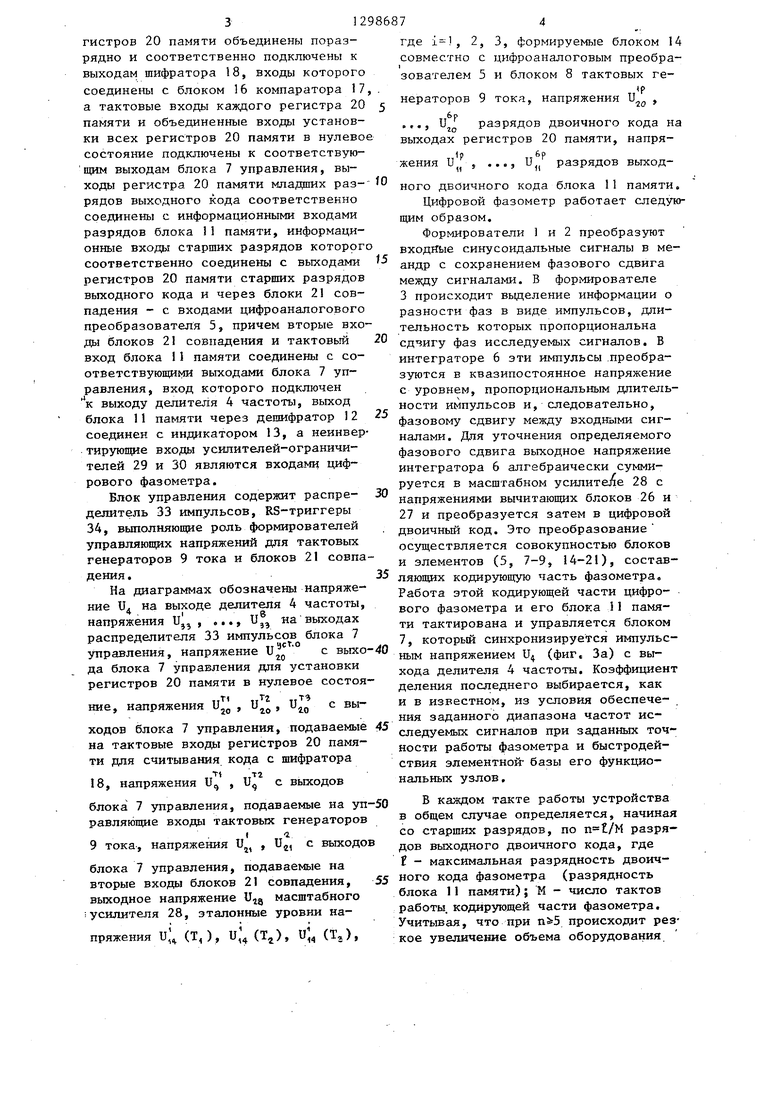

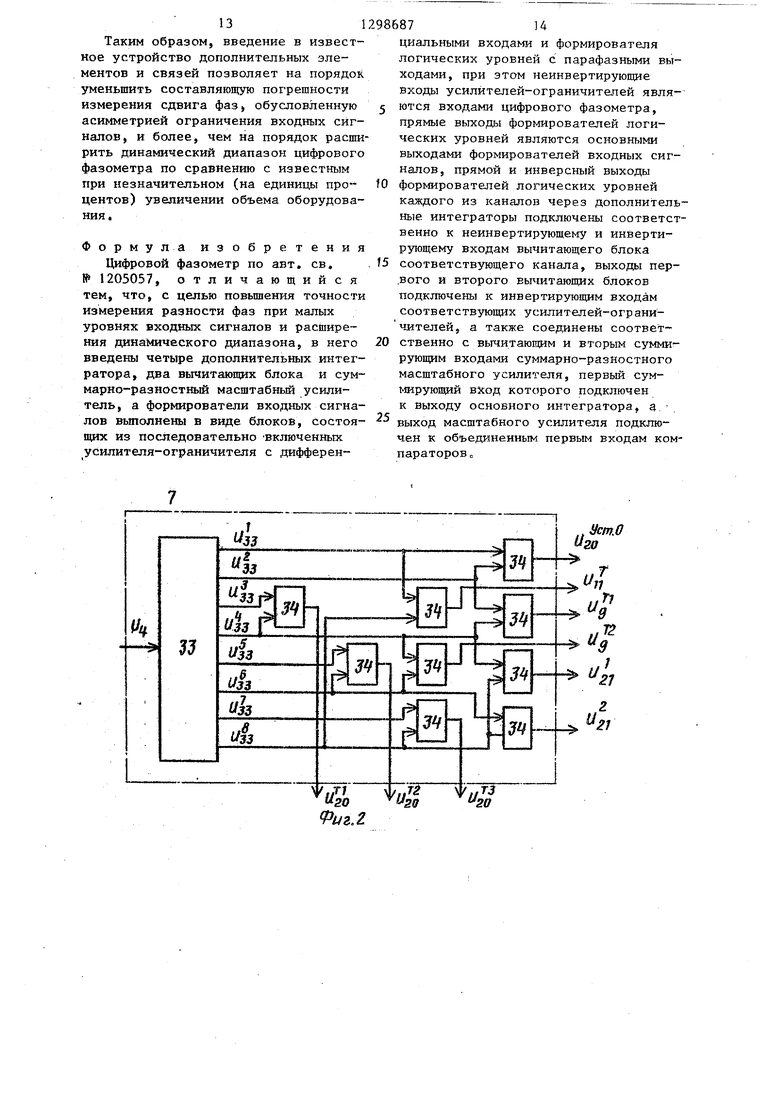

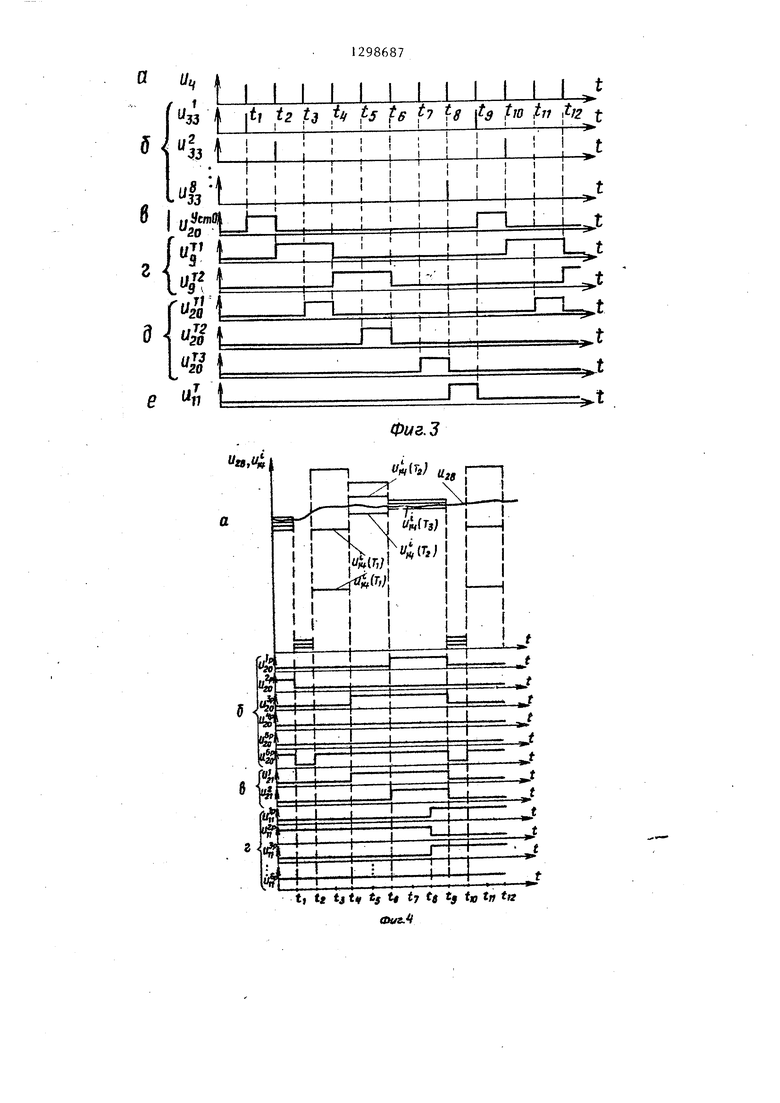

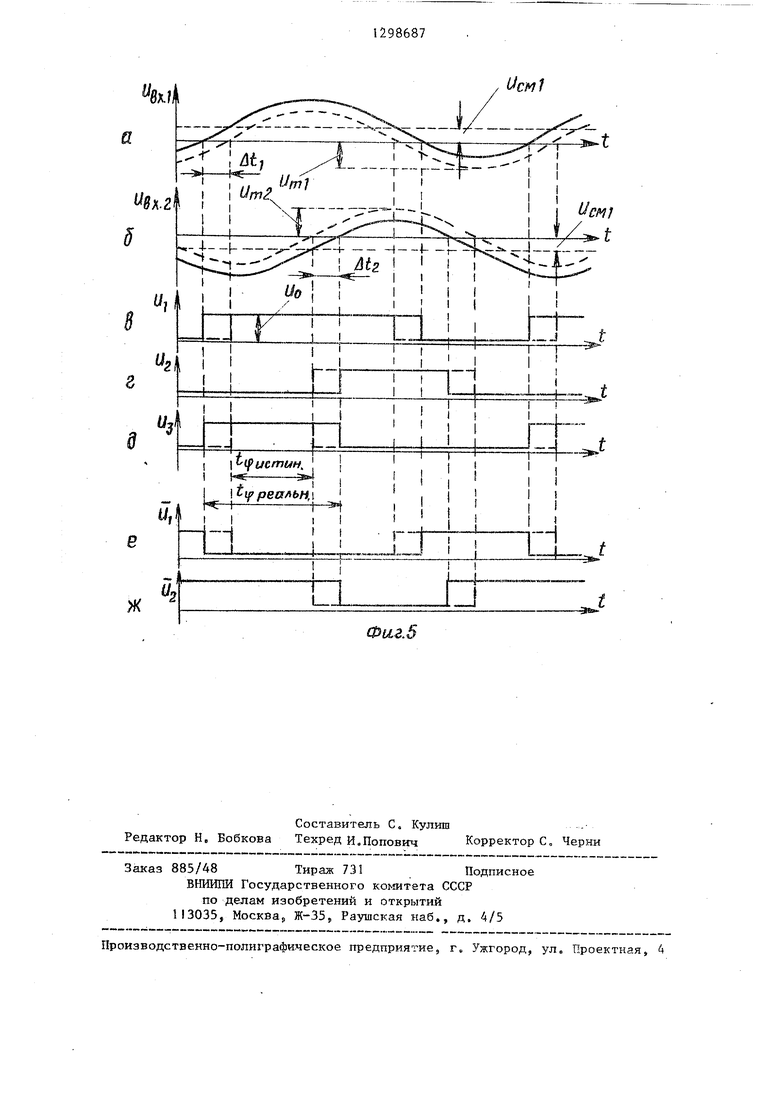

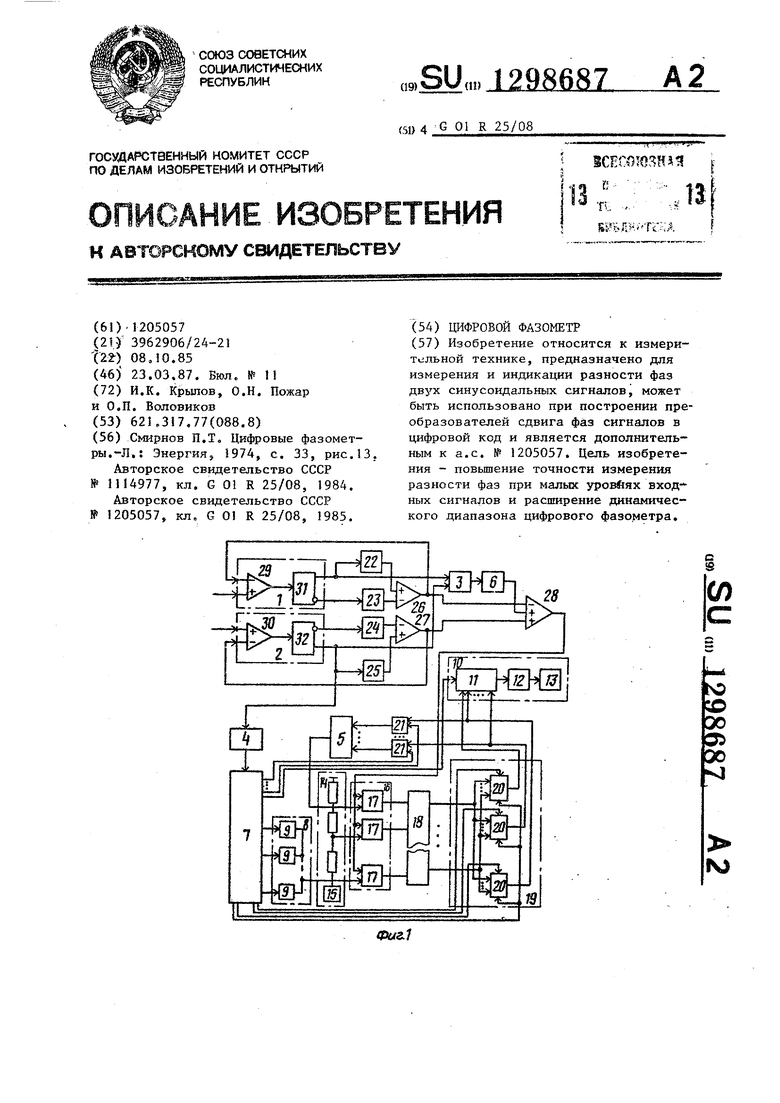

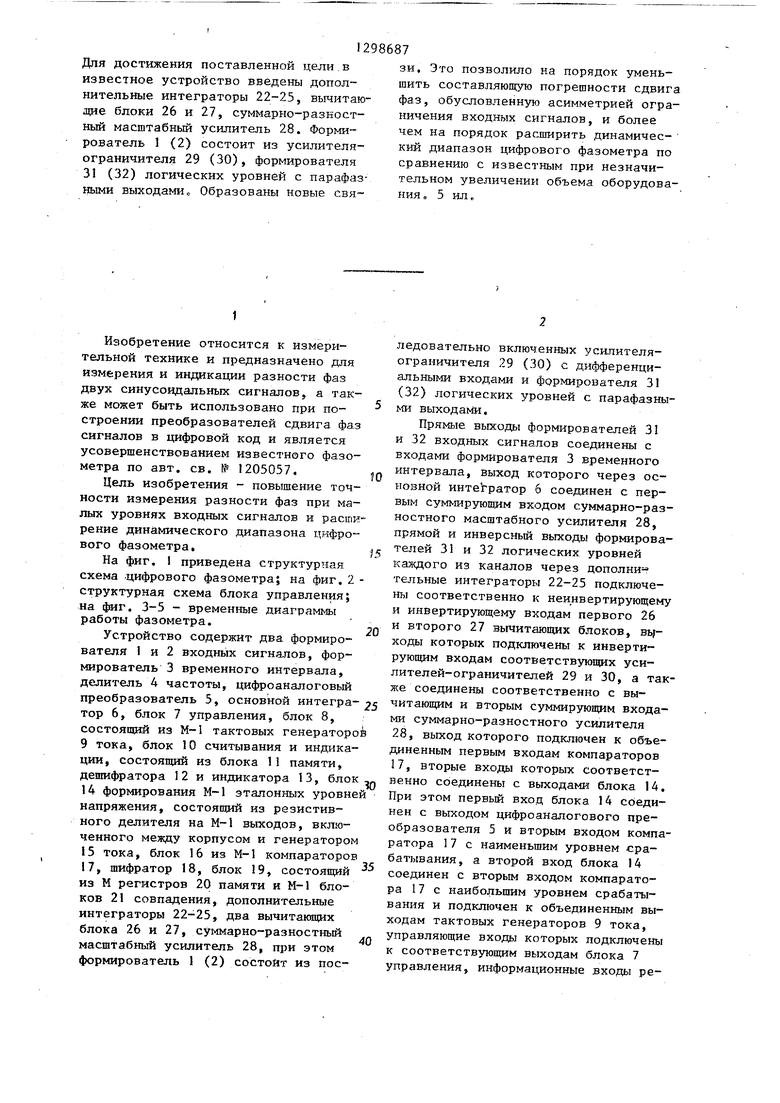

На фиг. приведена структурная схема .цифрового фазометра; на фиг.2 структурная схема блока управления; на фиг. 3-5 - временные диаграммы работы фазометра.

Устройство содержит два формирователя 1 и 2 входных сигналов, формирователь 3 временного интервала, делитель 4 частоты, цифроаналоговый преобразователь 5, основной интегратор 6, блок 7 управления, блок 8, состоящий из М-1 тактовых генераторо 9 тока, блок 10 считывания и индикации, состоящий из блока 1J памяти, дешифратора 12 и индикатора 13, блок

14формирования М-1 зталонных уровне напряжения, состоящий из резистив- ного делителя на М-1 выходов, включенного между корпусом и генератором

15тока, блок 16 из М-1 компараторов 17, шифратор 18, блок 19, состоящий из М регистров 20 памяти и М-1 блоков 21 совпадения, дополнительные интеграторы 22-25, два вычитающих блока 26 и 27, суммарно-разностный масштабный усилитель 28, при этом формирователь 1 (2) состоит из посзи. Это позволило на порядок уменьшить составляющую погрешности сдвига фаз, обусловленную асимметрией ограничения входных сигналов, и более чем на порядок расширить динамичес- кий диапазон цифрового фазометра по сравнению с известным при незначительном увеличении объема оборудования , 5 ил«

ледовательно включенных усилителя- ограничителя 29 (30) с дифференциальными входами и Формирователя 31 (32) логических уровней с парафазны- ми выходами.

Прямые выходы формирователей 31 и 32 входных сигналов соединены с входами формирователя 3 временного интервала, выход которого через основной интегратор б соединен с первым суммирующим входом суммарно-разностного масштабного усилителя 28, прямой и инверсный выходы формирователей 31 и 32 логических уровней каждого из каналов через дополни тельные интеграторы 22-25 подключены соответственно к неинвертирующему и инвертирующему входам первого 26 и второго 27 вычитающих блоков, вц- ходы которых подключены к инвертирующим входам соответствующих усилителей-ограничителей 29 и 30, а также соединены соответственно с вычитающим и вторым суммирующим входами суммарно-разностного усилителя 28, выход которого подключен к объединенным первым входам компараторов 17, вторые входы которых соответственно соединены с выходами блока 14, При этом первый вход блока I4 сЬеди- нен с выходом цифроаналогового преобразователя 5 и вторым входом компаратора 17 с наименьшим уровнем срабатывания, а второй вход блока 14 соединен с вторым входом компаратора 1 7 с наибольшим уровнем срабатывания и подключен к объединенным выходам тактовых генераторов 9 тока, управляющие входы которых подключены к соответствующим выходам блока 7 управления, информационные входы ре312986

гистров 20 памяти объединены поразрядно и соответственно подключены к выходам шифратора 18, входы которого соединены с блоком 16 компаратора 17, а тактовые входы каждого регистра 20 памяти и объединенные входы установки всех регистров 20 памяти в нулевое состояние подключены к соответствую

управления, вы щим выходам блока 7

ходы регистра 20 памяти младашх разрядов выходного кода соответственно соединены с информационными входами разрядов блока 11 памяти, информационные входы старших разрядов которог соответственно соединены с выходами регистров 20 памяти старших разрядов выходного кода и через блоки 21 совпадения - с входами цифроаналогового преобразователя 5, причем вторые входы блоков 21 совпадения и тактовый вход блока 11 памяти соединены с соответствующими выходами блока 7 управления, вход которого подключен к выходу делителя 4 частоты, выход блока 11 памяти через дешифратор 2 соединен с индикатором 13, а неинвер тирующие входы усилителей-ограничителей 29 и 30 являются входами цифрового фазометра.

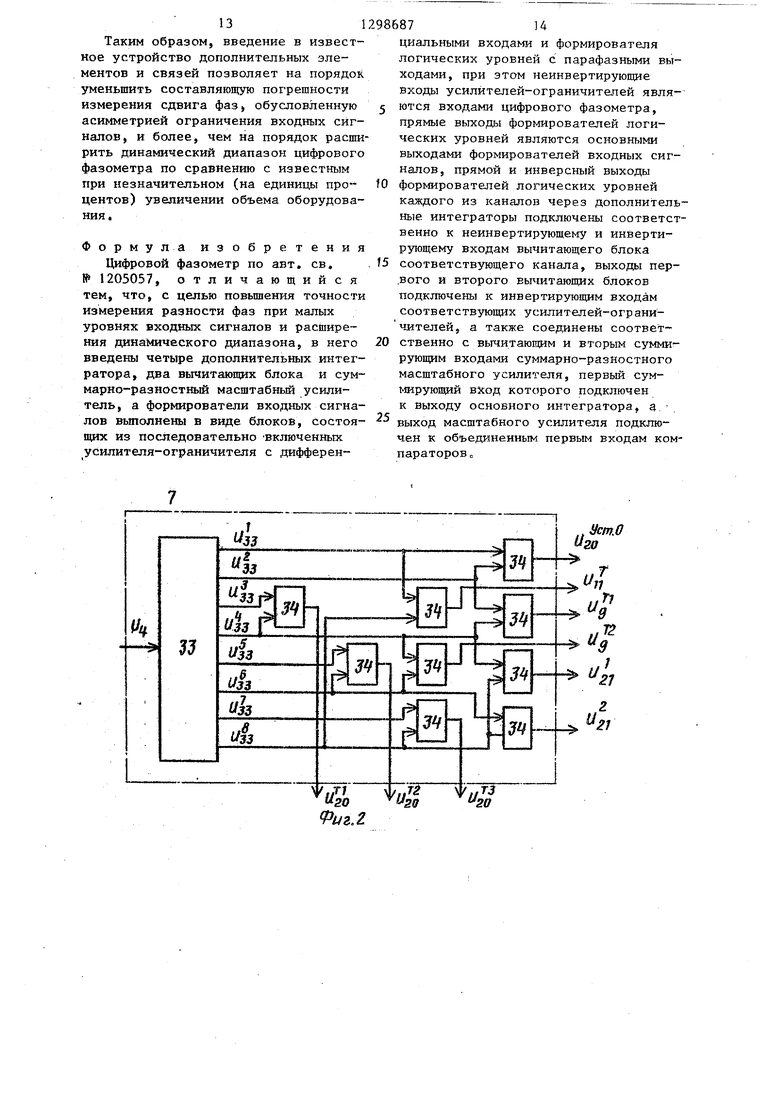

Блок управления содержит распределитель 33 импульсов, RS-триггеры 34, выполняющие роль формирователей управляющих напряжений для тактовых генераторов 9 тока и блоков 21 совпадения.

На диаграммах обозначены напряжение и на выходе делителя 4 частоты,

яа выходах

J. на выходе делителя

1 и

напряжения U, , .,.,11,

распределителя 33 импульсов блока 7

управления, напряжение с вьгхо да блока 7 управления для установки регистров 20 памяти в нулевое состоя

ние,

,.т „тг „тз напряжения и,„ , и,„ , U

с вы 20 iO

ХОДОВ блока 7 управления, подаваемые на тактовые входы регистров 20 памяти для считывания кода с шифратора

18, напряжения U , U

с выходов

9 5

блока 7 управления, подаваемые на уп-50 равляющие входы тактовых генераторов

1-у jno.iit yiyri.tiiruriyi, f

9 тока, напряжения U, , Uj, с выходов

55

блока 7 управления, подаваемые на вторые входы блоков 21 совпадения, выходное напряжение масштабного ;усилителя 28, эталонные уровни напряжения и, (Т,), и,(т), и; (Tj),

где i, 2, 3, формируемые блоком 14 совместно с цифроаналоговым преобратактовых ге- Р

20

зователем 5 9

иГ

и блоком

тока, напряжения U

нераторов

.бр

j разрядов двоичного кода на

выходах регистров 20 памяти, напря

Ю 5 0

5

0

0

1р бр жения и,.и.

разрядов выходИ - - - J - и

ного двоичного кода блока 11 памяти.

Цифровой фазометр работает следующим образом.

Формирователи 1 и 2 преобразуют входные синусоидальные сигналы в меандр с сохранением фазового сдвига между сигналами. В формирователе 3 происходит выделение информации о разности фаз в виде импульсов, длительность которых пропорциональна сд зигу фаз исследуемых сигналов. В интеграторе 6 эти импульсы .преобразуются в квазипостоянное напряжение с уровнем, пропорциональным длительности импульсов и, следовательно, фазовому сдвигу между входными сигналами. Для уточнения определяемого фазового сдвига выходное напряжение интегратора 6 алгебраически суммируется в масштабном ycmiHTej e 28 с напряжениями вычитающих блоков 26 и 27 и преобразуется затем в цифровой двоичный код. Это преобразование осуществляется совокупностью блоков и элементов (5, 7-9, 14-21), состав- 5 ляющих кодирующую часть фазометра. Работа этой кодирующей части цифрового фазометра и его блока I1 памяти тактирована и управляется блоком 7, которьй синхронизируется импульсным напряжением U (фиг. За) с выхода делителя 4 частоты. Коэффициент деления последнего выбирается, как

и в известном, из условия обеспечения заданного диапазона частот исследуемых сигналов при заданных точности работы фазометра и быстродействия элементной- базы его функциональных узлов.

В каждом такте работы устройства в общем случае определяется, начиная со старших разрядов, по разрядов выходного двоичного кода, где t - максимальная разрядность двоич- ного кода фазометра (разрядность блока 11 памяти); М - число тактов работы, кодирующей части фазометра, Учитьшая, что при происходит резкое увеличение объема оборудования

устройства за счет большого количества компараторов 17 (), число (п) разрядов выходного кода, определяемых в каждом такте работы фазометра, целесообразно выбирать не более трех-четырех.

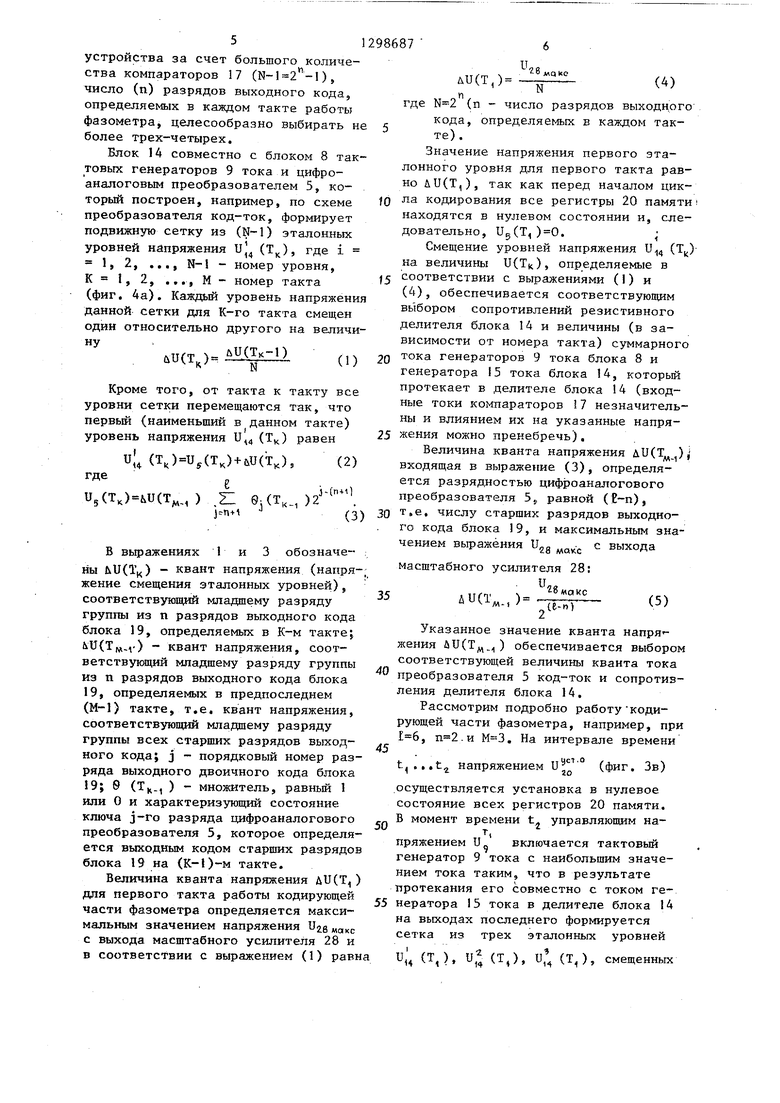

Блок 14 совместно с блоком 8 тактовых генераторов 9 тока и цифро- аналоговым преобразователем 5, который построен, например, по схеме преобразователя код-ток, формирует подвижную сетку из (N-1) эталонных уровней напряжения Uj (Т) где i 1, 2, ..., N-1 - номер уровня, К I, 2, .,., М- номер такта (фиг. 4а). Каждый уровень напряжения данной сетки для К-го такта смещен один относительно другого на величину

(1)

uU(T)

ьи(Тк-1)

N

Кроме того, от такта к такту все уровни сетки перемещаются так, что первый (наименьший в данном такте) уровень напряжения U,4 (Тц) равен

UH (T,)Uj(Tj+uU(T),

где

U5((V, ) .21 ej(T,, )2 (2)

j-(n+il

(3)

В выражениях 1 и 3 обозначе- ны &и(Т,/) - квант напряжения (напряженив смещения эталонных уровней), соответствующий младшему разряду группы из п разрядов выходного кода блока 19, определяемых в К-м тактеj MJ(T;v(,v) квант напряжения, соответствующий младшему разряду группы из п разрядов выходного кода блока 19, определяемых в предпоследнем (М-1) такте, т.е. квант напряжения, соответствующий младшему разряду группы всех старших разрядов выходного кода; j - порядковый номер разряда выходного двоичного кода блока 9; S (Т., ) - множитель, равньй 1 или О и характеризующий состояние

ключа j-ro разряда цифроаналогового ппр.п(1пячояяте.пя 5. котопое опоепеля-

преобразователя 5, которое определяется выходным кодом старших разрядов блока 19 на (К-1)-м такте.

Величина кванта напряжения ди(Т,) для первого такта работы кодирующей части фазометра определяется максимальным значением напряжения макс с выхода масштабного усилителя 28 и в соответствии с выражением (1) равна

ли(т,)

п

28

ArtQkO

N

(4)

где (п - число разрядов выходного кода, определяемых в каждом такте).

Значение напряжения первого эталонного уровня для первого такта равно ди(Т,), так как перед началом цикла кодирования все регистры 20 памятиi находятся в нулевом состоянии и, следовательно, Ug(T, )0.

Смещение уровней напряжения U ( на величины U(T)i;), определяемые в

соответствии с выражениями (I) и (4), обеспечивается соответствующим выбором сопротивлений резистивного делителя блока 14 и величины (в зависимости от номера такта) суммарного тока генераторов 9 тока блока 8 и

генератора 15 тока блока 14, который

протекает в делителе блока 14 (входные токи компараторов 17 незначительны и влиянием их на указанные напря- жения можно пренебречь).

Величина кванта напряжения ди(Т.. .)i

входящая в выражение (3), определяется разрядностью цифроаналогового преобразователя 5,, равной (-п), т.е. числу старших разрядов выходного кода блока )9, и максимальным значением выражения с выхода

масштабного усилителя 28;

и«

iU(V,)

8 такс

де-п)

(5)

40

45

Указанное значение кванта напря-- жения uU(Tj,. ) обеспечивается выбором соответствующей величины кванта тока преобразователя 5 код-ток и сопротивления делителя блока 14.

Рассмотрим подробно работу кодирующей части фазометра, например, при , и . На интервале времени

t..,t

В момент времени t ..i

напряжением U (фиг. Зв)

.осуществляется установка в нулевое состояние всех регистров 20 памяти.

управляющим на В момент времени t ..i

пряжением U- включается тактовый генератор 9 тока с наибольшим значением тока таким, что в результате протекания его совместно с током ге- 55 нератора 15 тока в делителе блока 14 на выходах последнего формируется сетка из трех эталонных уровней

UH ( 14 н (Т,), смещенных

один относительно другого на величину

и

&и(Т,)

Ммакс

и,

2вмаис

, (6)

при ЭТОМ и, (Т, ) и(Т, ) .

Компараторы 17 осушествляют сравнение напряжения с выхода масштабного усилителя 28 с данной сеткой эталонных уровней. По состоянию компараторов 7 в шифраторе 18 формируется двоичный коДу соответствующий первым двум старшим разрядам выходного кода. На интервале времени при подаче высокого уровня

(фиг, Зд) на тактовый

..t

напряжения У

20

вход первого регистра 20 памяти старших разрядов осуществляется запись кода шестого и пятого разрядов в блок 19, являющийся блоком оперативной памяти выходного кода.

В момент времени t заканчивается . первый такт работы устройства и начи- 25 кается второй такт, при этом выключается первый тактовый генератор 9 тока и включается второй тактовый генератор 9 тока, а информация о шестом и пятом разрядах выходного кода с зо блока 19 через соответствующий блок 21 совпадения, управляемый напряжением и,, (фиг, 4в), подается на цифроаналоговый преобразователь 5, Выходной ток последнего совместно с суммарным током второго тактового генератора 9 тока и генератора 5 тока формирует на выходах резистив35

По состоянию компараторов 17 в шифраторе 18 формируется (после ус- танош1ения указанных эталонных уровней на вторых входах компараторов 17 двоичный код, соответствуюш;ий четвертому и третьему разрядам выходного кода. При подаче на интервале вре мени t,,,tg высокого уровня напряже ния (фиг. Зд) на тактовый вход второго регистра 20 памяти старших разрядов происходит запись кода четвертого и третьего разрядов в блоке 19 оперативной памяти,

В момент времени tg заканчивается второй такт работы и начинается третий такт, С этого момента выключается второй тактовый генератор 2Ю тока, а на цифроаналоговый преобразователь 5 через блок 2 совпадения, управляемый напряжением U , подается информация о четвертом и третьем разрядах выходного кода. В результате.за счет совместного протекания в делителе выходного тока цифроаналогового преобразователя 5 и тока генератора 15 формируется сетка эталонных уровней

ного делителя блока 14 другую сетку 0 U, (Т ), , 1(, смещенных

(фиг, 4а) из трех эталонных уровней 1 (Т). 1, (Т,,), и (Т), соответствующих втopo ry такту работы фазометра и смещенных один относительно

один относительно другого на

uU(T,

л ) 28yoj g.,

j г - -л (

;

45„ 1

другого на

AU(T,)

uU(T, ) 58 макс

(7)

Т 16

причем первый уровень U (Tj, ) устанавливается равньм

и, (T)U5(T,j) + uU(T), (8) где для приведенного примера (фиг, 4)

Us(T,,) uU(T) 0j(T, )2

i1Ъ MOitC

(0 2° Ю 2 -2)

28 макс

(9)

С учетом значениг iiU(T) и (1) из выражений (7) и (9) получают уровень напряжения U, (Т), равный

UH (т,)у и,

16 Аймаке

Ш

16 28 макс

(10)

5

0

5 о

5

По состоянию компараторов 17 в шифраторе 18 формируется (после ус- танош1ения указанных эталонных уровней на вторых входах компараторов 17) двоичный код, соответствуюш;ий четвертому и третьему разрядам выходного кода. При подаче на интервале времени t,,,tg высокого уровня напряжения (фиг. Зд) на тактовый вход второго регистра 20 памяти старших разрядов происходит запись кода четвертого и третьего разрядов в блоке 19 оперативной памяти,

В момент времени tg заканчивается второй такт работы и начинается третий такт, С этого момента выключается второй тактовый генератор 2Ю тока, а на цифроаналоговый преобразователь 5 через блок 2 совпадения, управляемый напряжением U , подается информация о четвертом и третьем разрядах выходного кода. В результате.за счет совместного протекания в делителе выходного тока цифроаналогового преобразователя 5 и тока генератора 15 формируется сетка эталонных уровней

один относительно другого на

uU(T,

л ) 28yoj g.,

j г - -л (

;

45„ 1

при этом наименьший уровень становится равным

(12)

I

50

и,4 (T,)U5(Tj)+&U(Tj), где6

и5(Тз)ли(Тг) 11 6j(T,j)2

j-э

и,

24

- Л тт

Тб гвиакс

(l-2%0 2 +0-2%l-2)- 36

-гемакс

36ли(Т,).

(13)

Таким образом,с учетом выражений (12) и (13) для (Tj) получают

37

t- (1 ;() 29 макс

3/ -gTT .(Т,).(14)

Так как квант напряжения ди(Т) соответствует младшему разряду при шестиразрядном кодировании, то на третьем (последнем) такте кодирования в шифраторе 18 формируется код второго и первого разрядов, который при подаче высокого уровня напряжения

и (фиг, Зд) на тактовый вход регистра 20 памяти младших разрядов записывается в блок 19 оперативной памяти, В момент времени tg заканчивается третий такт работы кодирующей части фазометра.

Завершает цикл кодирования напряжения U,jg с выхода масштабного усилителя- 28, пропорционального сдвигу фаз исследуемых сигналов, этап считывания двоичного кода с выхода блока 19 регистров 20 памяти, кото-. рый осуш;ествляется на интервале вреto

1298687 10

Следовательно, для измерения разности фаз с точностью единиц процен- . тов необходимо, чтобы амплитуда входных сигналов была бы примерно на два порядка больше приведенного к входу ОУ напряжения смеш;ения нуля. Учитывая, что для современных гжрокопо- лосных ОУ дрейф напряжения смещения нуля может составлять в рабочем диапазоне температур единицы милливольт, то нижний предел динамического диапазона по входным сигналам в известном цифровом фазометре составляет сотни милливольт при равенстве составляю- t5 щей погрешности измерения, обусловленной асимметрией ограничения, единицам процентов.

В предлагаемом цифровом фазометре повышена точность определения фазового сдвига при значительно меньших уровнях входных сигналов; т„е, расширен динамический ,циапазон фазометра. Это достигнуто за счет введения в известное устройство новых элемен20

мени tg,.,tg подачей на тактовый вход

блока И памяти напряжения U,, (фиГаЗе) тов и связей,, С одной стороны, в

с блока 7 управления,

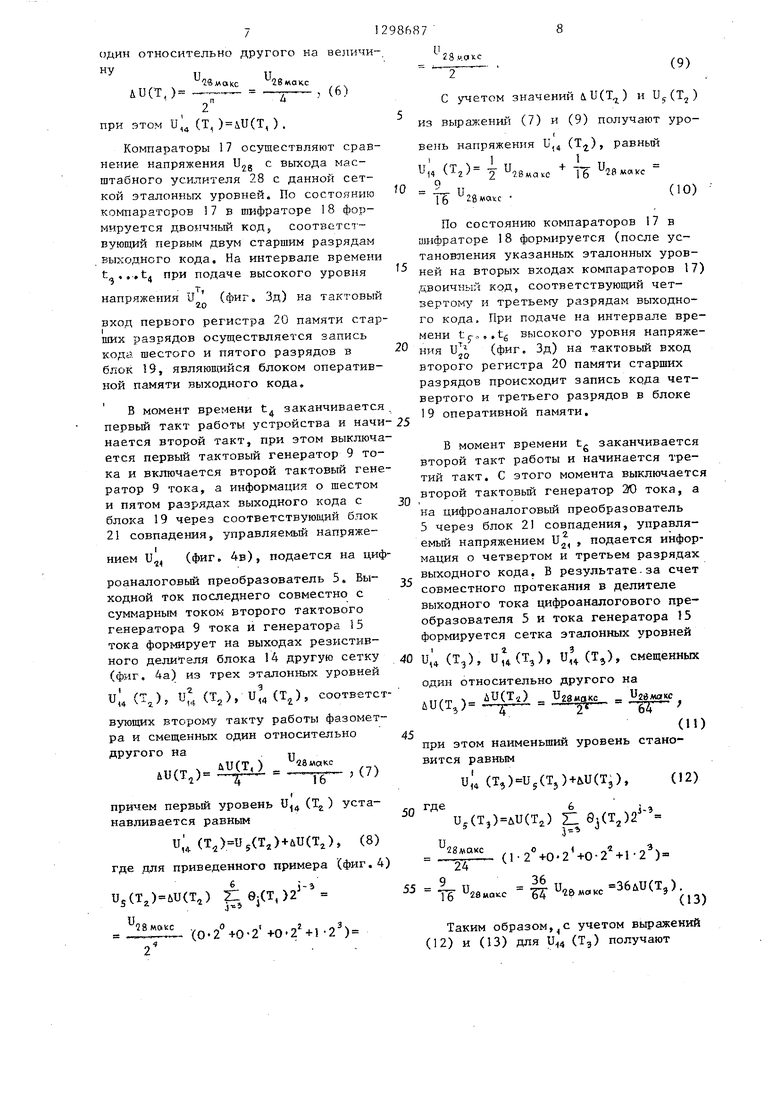

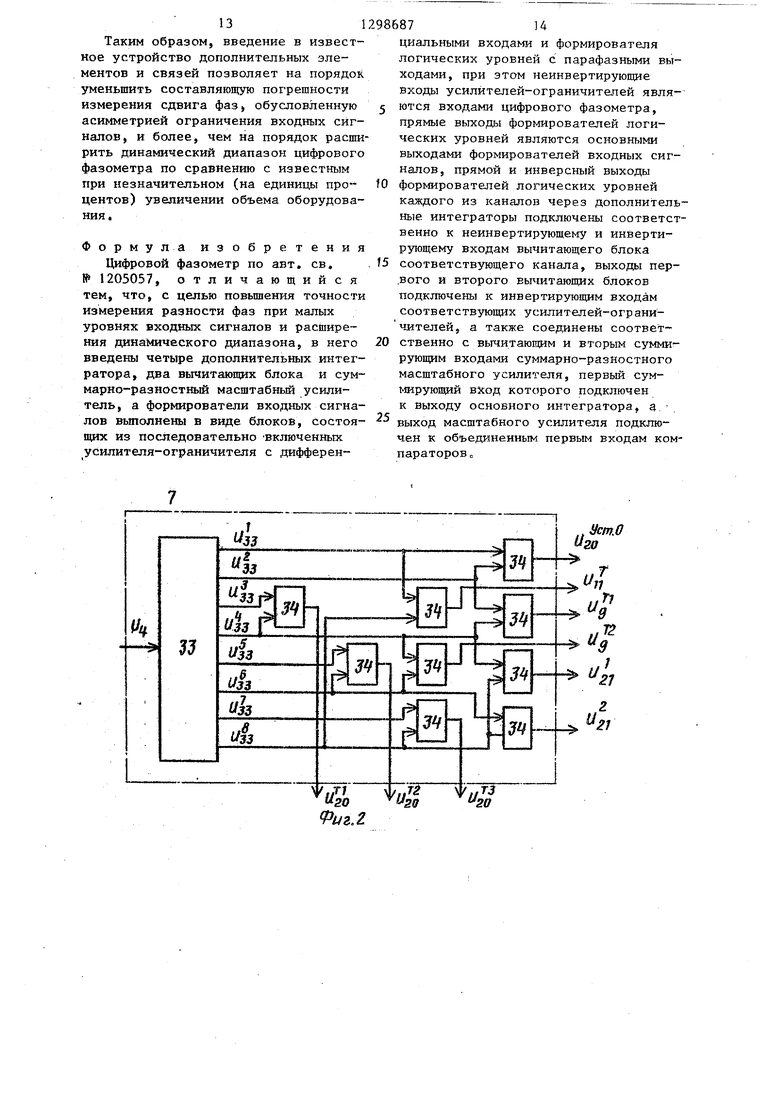

Напряжение на выходе интегратора 6 пропорционально фазовому сдвигу между входными синусоидальными сиг- налами. Однако точность этого соответствия зависит от симметрии огра ничения входных сигналов или от точ-- ности дискриминации нуль-переходов входных сигналов в формирователях 1 и 2, дня построения которых используются широкополосные операционные усилители (ОУ) Наличие у последних напряжения смещения нуля (U.,) и дрейфа этого напряжения приводят к асимметрии ограничения входных сигналов и, следовательно, к появлению ошибки в определении фазового сдви- - га. Как следует из временных диаграмм (фиг. 5) максимальная относительная погрешность в этом схлучае равна (при /A.t,/ /At2/ и

J аьо 1 асим.отр р Т/

UCM

и;г

где Uj - амплитуда входного сигнала, ,М.:0,01 можно практически

предлагаемом устройстве обеспечивается достаточно высокая степень симметрии ограничения за счет охвата формирователей и 2 входных сигна 0 лов отрицательной обратной связью (ООС). Напряжеьше ООС, характеризующее асимметрию ограничения (асимметрию меандра) и формируемое в соответствующих каналах с помош,ью допол35 нительных интеграторов 22-25 (построенных, например, на RC-фильтрах) и вычитающих блоков 26 и 27, смещает пороги срабатывания формирователей 1 и 2 входных сигналов в направлении

обратном дрейфу напряжения смещения нуля, В результате повышается точность дискриминации нуль-переходов и5 следовательно, степень симметрии ограничения входных сигналов.

45

arc sin

50

При

и.

55

с другой стороны, влияние остаточной симметрии ограничения входных сигналов на результат измерения разности фаз практически исключается в суммарно-разностном масштабном усилителе 28, в котором алгебраически суммируются напряжение с интегратора 6, пропорциональное реальному фазовому сдвигу сигналов с выходов формирователей 1 и 2, и напряжения с вычитаю- 1ДИХ блоков 26 и 27, пропорциональное асимметрии меавдров соответствующих каналов. В результате на выходе масштабного усилит 5ля создается напряже

см ffUm

(16)

предлагаемом устройстве обеспечивается достаточно высокая степень симметрии ограничения за счет охвата формирователей и 2 входных сигналов отрицательной обратной связью (ООС). Напряжеьше ООС, характеризующее асимметрию ограничения (асимметрию меандра) и формируемое в соответствующих каналах с помош,ью дополнительных интеграторов 22-25 (построенных, например, на RC-фильтрах) и вычитающих блоков 26 и 27, смещает пороги срабатывания формирователей 1 и 2 входных сигналов в направлении

обратном дрейфу напряжения смещения нуля, В результате повышается точность дискриминации нуль-переходов и5 следовательно, степень симметрии ограничения входных сигналов.

с другой стороны, влияние остаточной симметрии ограничения входных сигналов на результат измерения разности фаз практически исключается в суммарно-разностном масштабном усилителе 28, в котором алгебраически суммируются напряжение с интегратора 6, пропорциональное реальному фазовому сдвигу сигналов с выходов формирователей 1 и 2, и напряжения с вычитаю- 1ДИХ блоков 26 и 27, пропорциональное асимметрии меавдров соответствующих каналов. В результате на выходе масштабного усилит 5ля создается напряжеII

пропорциональное истинному фазние,

вому сдвигу входных сигналов. Поясним сказанное, используя временные диаграммы сигналов на входах и выходах формирователей 1 и 2 входных си налов и формирователя 3 временного интервала при наличии в обоих каналах, например, разной по знаку асимметрии ограничения входных сигналов (фиг, 5), На диаграммах обозначены ио - высота нормированного по амплитуде меандра на прямом и инверсном выходах формирователей I и 2 входных сигналов; it, , At - интервалы, времени, характеризующие асимметрию ограничения; t, , t

tf реальи Чистин.

временные интервалы, характеризующи соответственно реально измеряемый и истинный (без ошибок за счет асимметрии ограничения) фазовый сдвиг входных сигналов; Т - период входных сигналов.

Для представленного на диаграмма случая следует, что на выходе форми рователя 3 временного интервала сфомирован импульс Uj (фиг, 5д) длителностью, характеризующей реальный фазовый сдвиг

.Ч«стии, ,. (П

Следовательно, на выходе интегратора 6 выделится квазипостоянное напряжение, пропорциональное длительности этого импульса

tf реальи. о

tf

и.

+U,

+U,

tf метин,

uti

(18)

ризующему истинный фазовьш сдвиг ме ду входными сигналами фазометра. Сл довательно , составляющая погрещност фазометра, обусловленная асимметрие ограничения входных сигналов, в пре лагаемом устройстве отсутствует, в то время как в известном цифровом фазометре эта составляющая погрещ- ности принимает существенны ния, особенно при малых уровнях входных сигналов, Что касается составляющей погрешности измерения, обусловленной нестабильностью параметров вычитающих блоков 26 и 27 ма 35 штабного усилителя 28, то она яв- :ляется несущественной (не более 0,1% так как для построения указанных бл ков могут быть использованы узкопо- лосные прецизионные операционные уси

At,

TUo -JЭто напряжение, поступая на первый 40 лители, охваченные глубокой отрицасуммирующий вход масштабного усилителя 28, передается с коэффициентом Кц, на его выход,

С помощью интеграторов 22-25 а также вычитающих блоков 26 и 27 на выходах последних формируются квазипостоянные напряжения , , Ujq, , характеризующие асимметрию меандров и, соответственно, погрещности определения фазового сдвига:

лч, Т- f , )- ( I -26t, )

и

и„

(19)

UAC 7 )- ( 5 +2Atj)

-и,

4л t2

(20)

12

Эти напряжения, поступая соответственно на вычитающий и второй суммирующий входы масштабного усилителя

28, передаются с коэффициентом К

1

At,

Kj т- Kcf на его выход, В резуль

тате напряжение на выходе усилителя 28 равно

,

(21)

а с учетом равенств (18) - (20) получают, 4fo

t.

и

28

0

Ч истии

и

Ч истин

.(22)

5

0

5

Таким образом, напряжение на выходе суммарно-разностного масщтабно- го усилителя 28 пропорционально временному интервалу t,. , характе т исти н,

ризующему истинный фазовьш сдвиг между входными сигналами фазометра. Следовательно , составляющая погрещности фазометра, обусловленная асимметрией ограничения входных сигналов, в предлагаемом устройстве отсутствует, в то время как в известном цифровом фазометре эта составляющая погрещ- ности принимает существенны ния, особенно при малых уровнях входных сигналов, Что касается составляющей погрешности измерения, обусловленной нестабильностью параметров вычитающих блоков 26 и 27 мас- 5 штабного усилителя 28, то она яв- :ляется несущественной (не более 0,1%), так как для построения указанных блоков могут быть использованы узкопо- I лосные прецизионные операционные уси0

тельной обратной связью.

Нижняя граница динамического диапазона в предлагаемом цифровом фазометре определяется уже не асимметрией ограничения входных сигналов - фазометра, а искажениями сигналов трапецеидальной формы, т,е, конечной длительностью фронтов меандра на выходах формирователей 1 и 2, Эти искажения зависят от коэффициента усиления и скорости нарастания выходного напряжения операционных усилителей, используемых для построения формирователей 1 и 2, При использовании современных быстродействующих ОУ нижняя граница динамического диапазона в предлагаемом цифровом фазометре может составлять единицы милливольт.

Таким образом, введение в известное устройство дополнительных элементов и связей позволяет на порядок уменьшить составляющую погрешности измерения сдвига фаз обусловленную асимметрией ограничения входных сигналов, и более, чем на порядок расширить динамический диапазон цифрового фазометра по сравнению с известным при незначительном (на единицы процентов) увеличении объема оборудования.

Формула изобретения

Цифровой фазометр по авт. св. № 1205057, отличающийся тем, что, с целью повьщ1ения точности измерения разности фаз при малых уровнях входных сигналов и расширения динамического диапазона, в него введены четыре дополнительных интегратора, два вычитающих блока и суммарно-разностный масштабный усилитель, а формирователи входных сигналов вьшолнены в виде блоков, состоящих из последовательно Включенных усилителя-ограничителя с дифференfPt B,2

циальными входами и формирователя логических уровней с парафазными выходами, при этом неинвертирующие входы усилителей-ограничителей явля-ются входами цифрового фазометра, прямые выходгэ формирователей логических уровней являются основными выходами формирователей входных сигналов, прямой и инверсный выходы

формирователей логических уровней каждого из каналов через дополнительные интеграторы подключены соответственно к неинвертирующему и инвертирующему входам вычитающего блока

соответствующего канала, выходы пер- .вого и второго вычитающих блоков подключены к инвертирующим входам соответствую|цих усилителей-ограни- чителей, а также соединены соответственно с вычитающим и вторым суммирующим входа суммарно-разностного масштабного усилителя, первый суммирующий вход которого подключен к выходу основного интегратора, а ,

выход масштабного усилителя подклю- Ч1ен к объединеннь м первым входам компараторов „

t, tg tj tv tf tt tj tg ty tю tit ta

Фиг.

t/Ш/

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Дельта-кодер | 1987 |

|

SU1441482A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

| ДВУХФАЗНЫЙ ГЕНЕРАТОР ГАРМОНИЧЕСКИХ СИГНАЛОВ | 1990 |

|

RU2033684C1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

Изобретение относится к измерительной технике, предназначено для измерения и индикации разности фаз двз х синусоидальных сигналов может быть использовано при построении преобразователей сдвига фаз сигналов в цифровой код и является дополнительным к а.с. № 1205057. Цель изобретения - повьшение точности измерения разности фаз при малых уровйях вход- ных сигналов и расширение динамического диапазона цифрового фазометра. СО с ю

i неж

Фи,г.5

| Смирнов П.Т | |||

| Цифровые фазометры.-Л.: Энергия, 1974, с | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Цифровой фазометр | 1983 |

|

SU1114977A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой фазометр | 1984 |

|

SU1205057A1 |

Авторы

Даты

1987-03-23—Публикация

1985-10-08—Подача