Изобретение относится к технике циф- роаналогового преобразования с промежуточным преобразованием двоичного кодз во временной интервал и предназначено для использования в системах автоматического регулирования

Целью изобретения является повышение быстродействия и точности преобразования

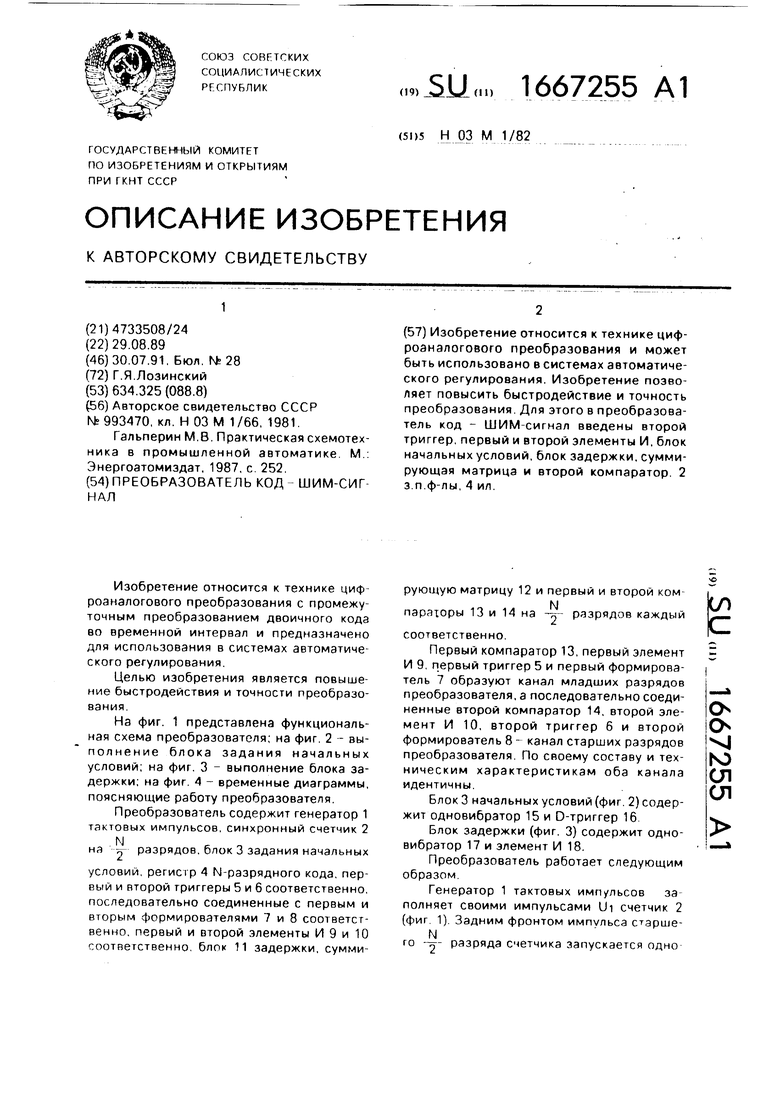

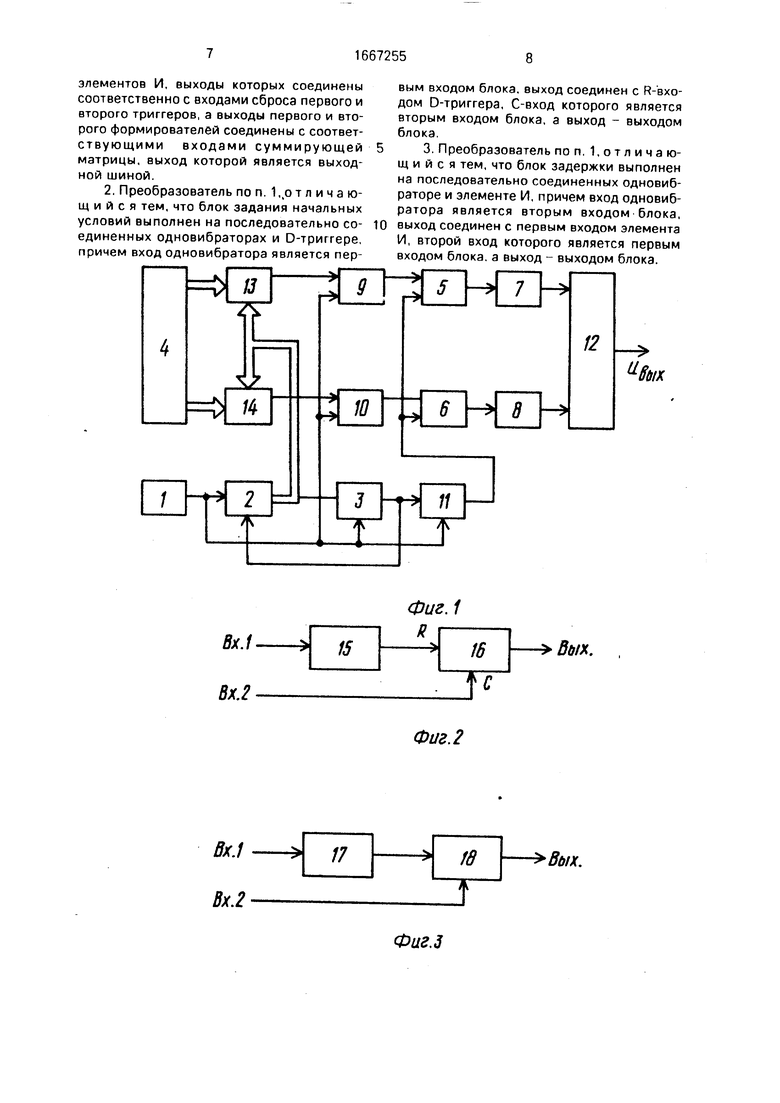

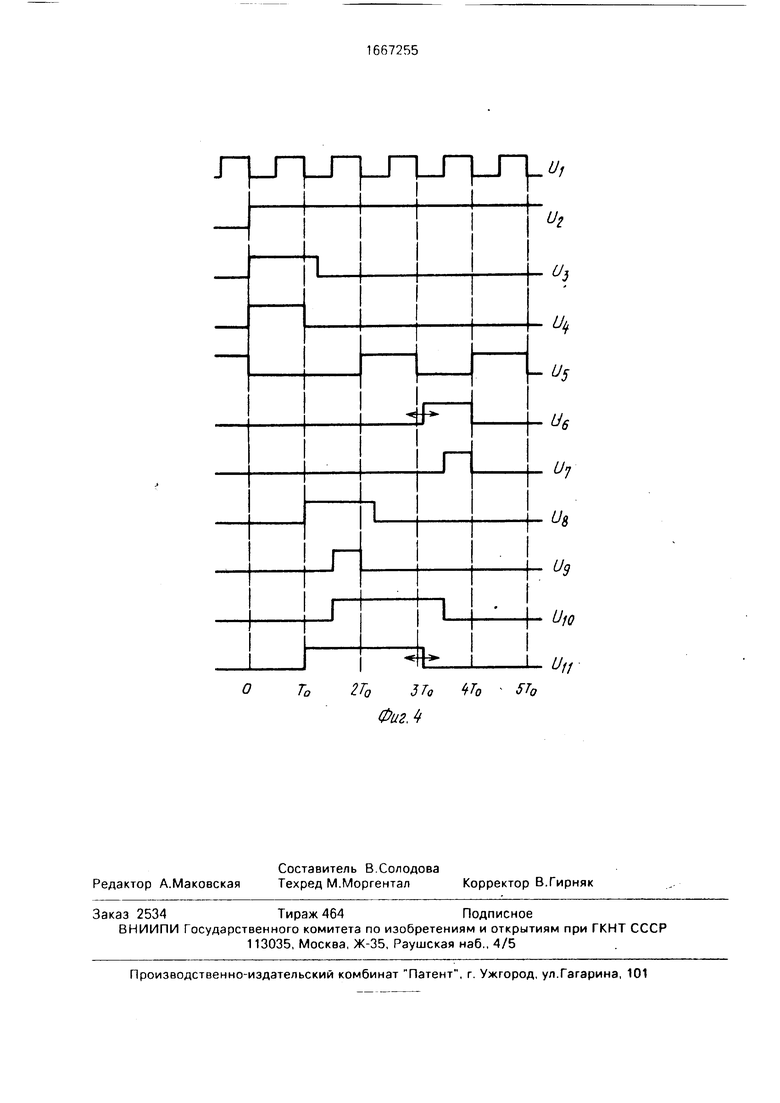

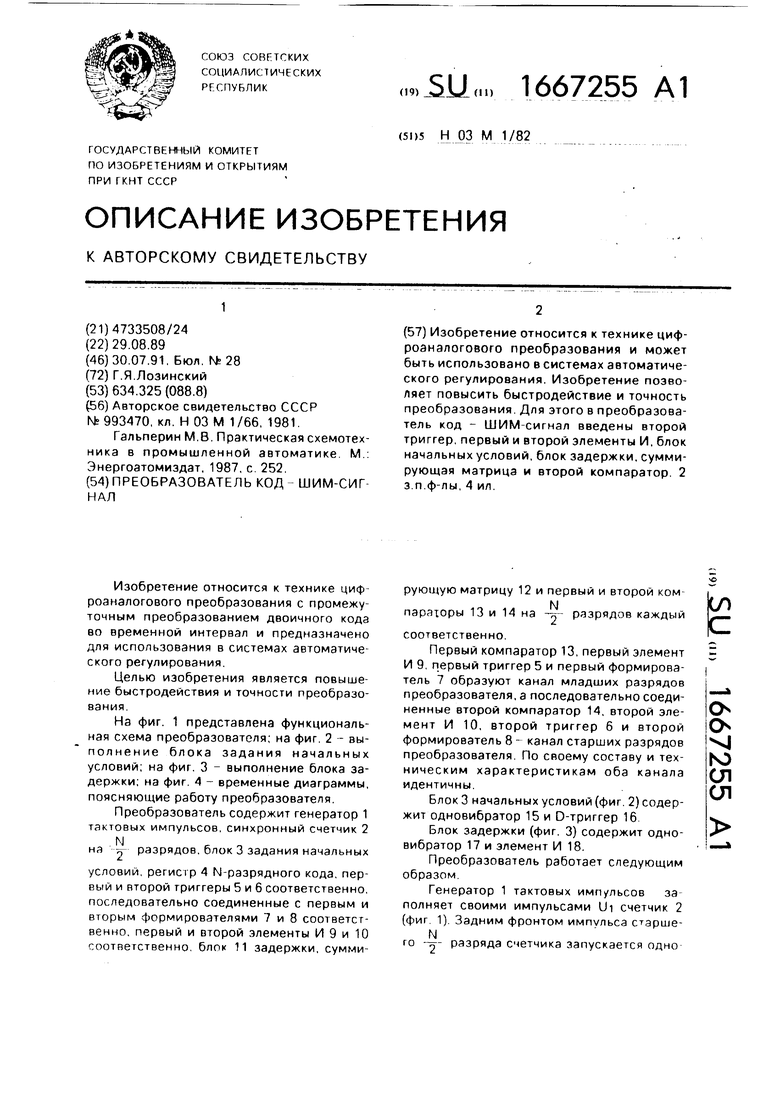

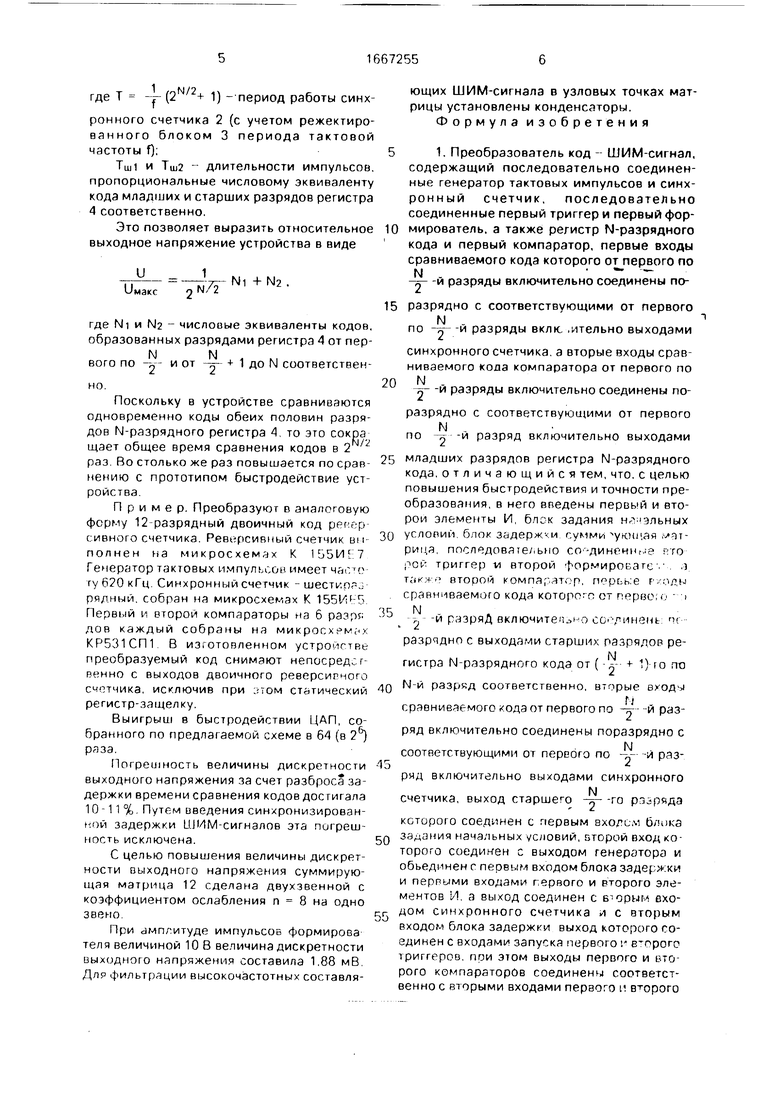

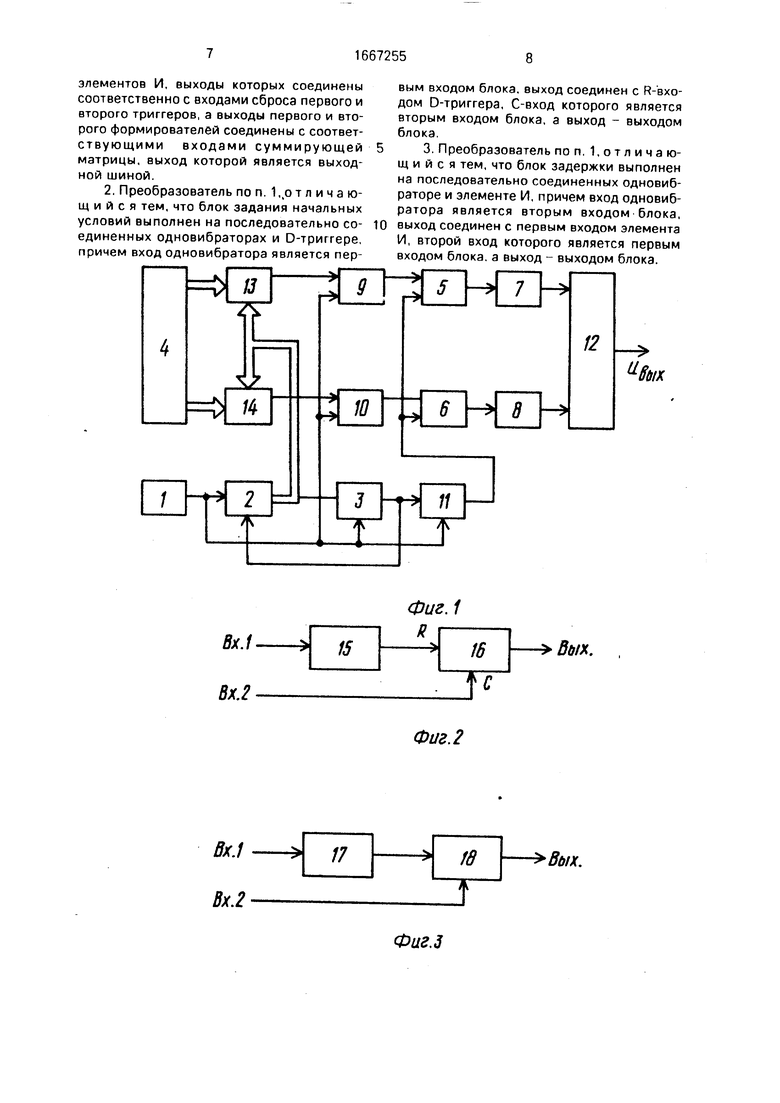

На фиг. 1 представлена функциональная схема преобразователя; на фиг 2 - выполнение блока задания начальных условий, на фиг. 3 - выполнение блока задержки; на фиг 4 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь содержит генератор 1 тактовых импульсов, синхронный счетчик 2

NКо

на - разрядов, блок 3 задания начальных

условий, регистр 4 N-разрядного кода, первый и второй триггеры 5 и 6 соответственно, последовательно соединенные с первым и вторым формирователями 7 и 8 соответственно, первый и второй элементы И 9 и 10 соответственно блок 11 задержки, суммирующую матрицу 12 и первый и второй ком

N параюры 13 и 14 на -к- разрядов каждый

соответственно

Первый компаратор 13, первый элемент И 9 первый триггер 5 и первый формирователь 7 образуют канал младших разрядов преобразователя, а последовательно соединенные второй компаратор 14, второй элемент И 10, второй триггер 6 и второй формирователь 8 - канал старших разрядов преобразователя По своему составу и техническим характеристикам оба канала идентичны

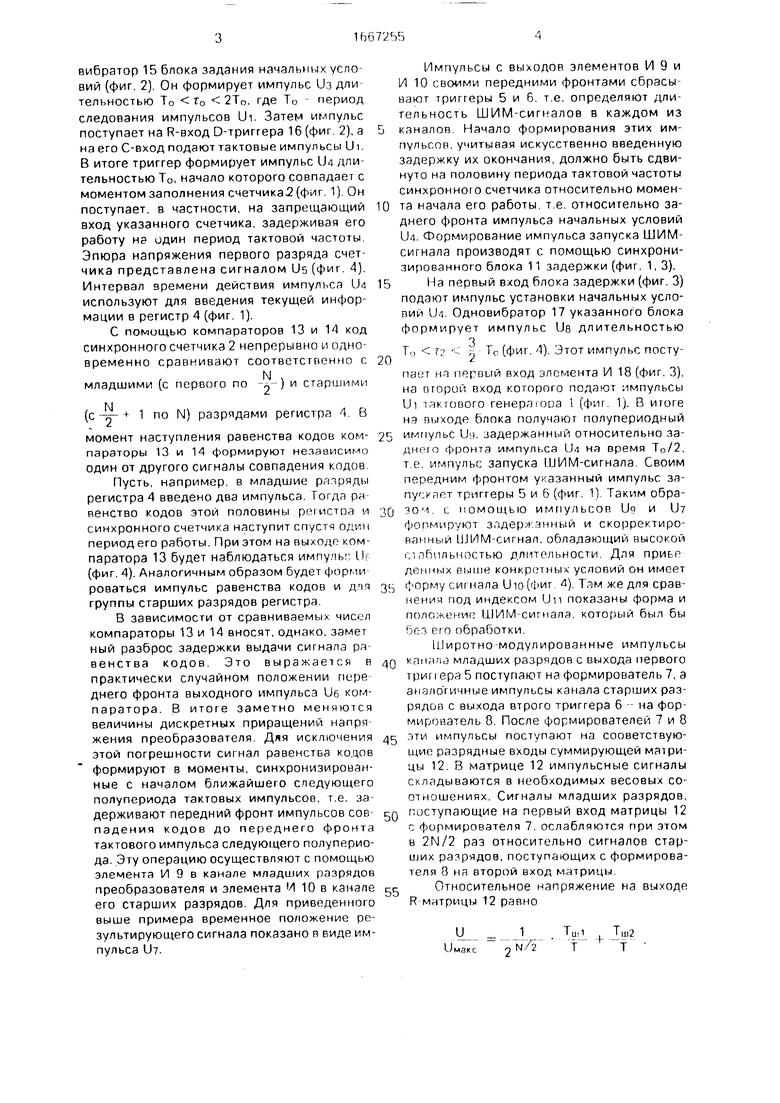

Блок 3 начальных условий (фиг 2) содержит одновибратор 15 и D-триггер 16

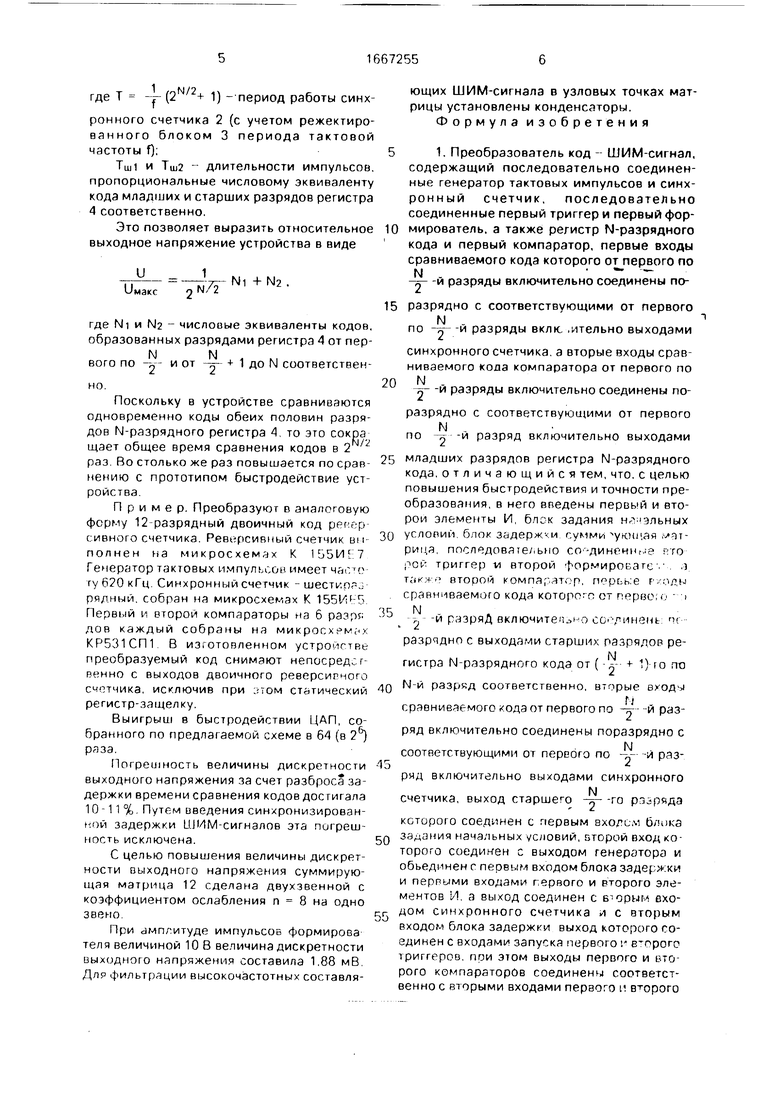

Блок задержки (фиг. 3) содержит одно- вибратор 17 и элемент И 18.

Преобразователь работает следующим образом

Генератор 1 тактовых импульсов за полняет своими импульсами Ui счетчик 2 (фиг 1) Задним фронтом импульса старшеNго разряда счетчика запускается одно

Ј

О

о J ю ел ел

вибратор 15 блока задания начальных условий (фиг. 2). Он формирует импульс Уз длительностью Т0 т0 2Т0, где Т0 - период следования импульсов Ui. Затем импульс поступает на R-вход D-триггера 16 (фиг. 2), а на его С-вход подают тактовые импульсы Ui. В итоге триггер формирует импульс Щ длительностью Т0, начало которого совпадает с моментом заполнения счетчика2 (фиг. 1). Он поступает, в частности, на запрещающий вход указанного счетчика, задерживая его работу на один период тактовой частоты. Эпюра напряжения первого разряда счетчика представлена сигналом Us (фиг. 4). Интервал времени действия импульса 1)4 используют для введения текущей информации в регистр 4 (фиг. 1).

С помощью компараторов 13 и 14 код синхронного счетчика 2 непрерывно и одновременно сравнивают соответственно с

,N

младшими (с первого по ) и старшими

(с -J- + 1 по N) разрядами регистра 4. В

момент наступления равенства кодов компараторы 13 и 14 формируют независимо один от другого сигналы совпадения кодов.

Пусть, например, в младшие разряды регистра 4 введено два импульса. Тогда ря- венство кодов этой половины решстоа и синхронного счетчика наступит спустя один период его работы. При этом на выходе компаратора 13 будет наблюдаться импулы Ur (фиг. 4). Аналогичным образом будет формироваться импульс равенства кодов и дня группы старших разрядов регистра.

В зависимости от сравниваемых чисел компараторы 13 и 14 вносят, однако, замег ный разброс задержки выдачи сигнала равенства кодов. Это выражается в практически случайном положении пере днего фронта выходного импульса Ue компаратора. В итоге заметно меняются величины дискретных приращений напряжения преобразователя. Дяя исключения этой погрешности сигнал равенства кодов формируют в моменты, синхронизированные с началом ближайшего следующего полупериода тактовых импульсов, г.е. задерживают передний фронт импульсов совпадения кодов до переднего фронта тактового импульса следующего полупериода. Эту операцию осуществляют с помощью элемента И 9 в канале младших разрядов преобразователя и элемента И 10 в канале его старших разрядов. Для приведенного выше примера временное положение результирующего сигнала показано в виде импульса и.

Импульсы с выходов элементов И 9 и И 10 своими передними фронтами сбрасывают триггеры 5 и 6. т.е. определяют длительность ШИМ-сигналов в каждом из

каналов. Начало формирования этих импульсов, учитывая искусственно введенную задержку их окончания, должно быть сдвинуто на половину периода тактовой частоты синхронного счетчика относительно момента начала его работы, т.е. относительно заднего фронта импульса начальных условий IJ4. Формирование импульса запуска ШИМ- сигнала производят с помощью синхронизированного блока 11 задержки (фиг. 1,3).

На первый вход блока задержки (фиг. 3)

подают импульс установки начальных условий U/}. Одновибратор 17 указанного блока формирует импульс Us длительностью 3

То

f l г-. Тс (фиг. 4). Этот импульс поступает на первый вход элемента И 18 (фиг. 3), на агорой вход которого подают импульсы Ui тактового генератра 1 (фиг. 1). В итоге на пыходе блока получают полупериодный

импульс U9, задержанный относительно заднего фронта импульса U4 на время Т0/2, т.е. импульс запуска ШИМ-сигнала. Своим передним фронтом указанный импульс запускает триггеры 5 и 6 (фиг. 1). Таким образо 1 - помощью импульсов UQ и U формируют задержанный и скорректированный ШИМ-сигнал, обладающий высокой стабильностью длительности. Для приье денных выше конкретных условий он имеет

форму сигнала ию(Фиг 4). Там же для сравнения под индексом Un показаны форма и положение ШИМ-сигналэ. который был бы без его обработки.

Широт но -модулированные импульсы

канапа младших разрядов с выхода первого трип ера 5 поступают на формирователь 7, а аналогичные импульсы канала старших разрядов с выхода втрого триггера 6 - на формирователь 8. После формирователей 7 и 8

эти импульсы поступают на сооветствую- щие разрядные входы суммирующей матрицы 12. В матрице 12 импульсные сигналы складываются в необходимых весовых соотношениях. Сигналы младших разрядов,

поступающие на первый вход матрицы 12 с формирователя 7, ослабляются при этом в 2N/2 раз относительно сигналов старших разрядов, поступающих с формирователя 8 на второй вход матрицы.

Относительное напряжение на выходе

R-мнтрицы 12 равно

1

N/2

Т

Тш2

т

1

iN/2,

где Т -т- (2 1) - период работы синхронного счетчика 2 (с учетом режектиро- ванного блоком 3 периода тактовой частоты f);

ТШ1 и ТШ2 длительности импульсов, пропорциональные числовому эквиваленту кода младших и старших разрядов регистра 4 соответственно.

Это позволяет выразить относительное выходное напряжение устройства в виде

1

N/2

NI + N2 .

где NI и N2 - числовые эквиваленты кодов, образованных разрядами регистра 4 от перNN...

вого по -х и от -у- + 1 до N соответственно

Поскольку в устройстве сравниваются одновременно коды обеих половин разрядов N-разрядного регистра 4 то это сокра щает общее время сравнения кодов в 2 2 раз Во столько же раз повышается по сравнению с прототипом быстродействие устройства

Пример. Преобразуют в аналоговую форму 12-разрядный двоичный код ррррр сивного счетчика. Реверсивный счетчик вп- полнен на микросхемах К 1 5 5 И 7 Генератор тактовых импульсов имеет часго гу 620 кГц Синхронный счетчик - шестип., пялный, собран на микросхемах К 15511- Первый v второй компараторы из 6 раэрг. дов каждый собраны на микросхемах КР531СП1 В изготовленном устроигтве преобразуемый код снимают непосредственно с выходов двоичного реверсигчого счетчика, исключив при ,;том статический регистр-защелку.

Выигрыш в быстродействии ЦАП, собранного по предлагаемой схеме в 64 (в 2 j раза.

Погрешность величины дискретности выходного напряжения за счет разброса задержки времени сравнения кодов достигала 10 11 % Путем введения синхронизированной задержки ШИМ-сигналов эта погрешность исключена.

С целью повышения величины дискретности выходного напряжения суммирующая матрица 12 сделана двухзвенной с коэффициентом ослабления п 8 на одно звено

При «амплитуде импульсов формирова теля величиной 10 В величина дискретности выходного напряжения составила 1.88 мВ Для фильтрации высокочастотных составля0

5

0

5

0

ющих ШИМ-сигнала в узловых точках матрицы установлены конденсаторы. Формула изобретения

1. Преобразователь код - ШИМ-сигнал, содержащий последовательно соединенные генератор тактовых импульсов и синхронный счетчик, последовательно соединенные первый триггер и первый формирователь, а также регистр N-разрядного кода и первый компаратор, первые входы сравниваемого кода которого от первого по

N

-у- -и разряды включительно соединены поразрядно с соответствующими от первого

N . по -у- -и разряды вклк, .ительно выходами

синхронного счетчика, а вторые входы сравниваемого кода компаратора от первого по

N .

-у- -и разряды включительно соединены поразрядно с соответствующими от первого

N по -п -и разряд включительно выходами

младших разрядов регистра N-разрядного кода, отличающийся тем, что. с целью повышения быстродействия и точности преобразования, в него введены первый и второй элементы И, блек задания н эльных услорий блок задержим сумми ующая , рица последовательно со-диненн е гто рог триггер лл второй формировав .з тйк-)г второй компас-пор, e г.пры сравниваемого кода которого от пррво.с N

2

-и разряд включите - О со уинень Г1

0

разрчдно с выходами старших разрядов регистра N-разрядного кода от ( + 1) го по

N-й разряд соответственно, вторые входы

II .

сравниваемого кода от первого по -у и разряд включительно соединены поразрядно с соответствующими от первого по -„- -и разряд включительно выходами синхронного

N

счетчика, выход старшего -у- -го

которого соединен с первым входим блока задания начальных условий, второй вход которого соединен с выходом генератора и объединен с первым входом блока задери ки и перпыми входами первого и рторого элементов И а выход соединен с вторым входом синхронного счетчика и с вторым входом блока задержки выход которого соединен с входами запуска первого и второго триггеров, пои этом выходы первого и второго компараторов соединены соответственно с вторыми входами первого и второго

элементов И, выходы которых соединены соответственно с входами сброса первого и второго триггеров, а выходы первого и второго формирователей соединены с соответствующими входами суммирующей матрицы, выход которой является выходной шиной.

2. Преобразователь по п. 1 ,.о т л и ч а ю- щ и и с я тем, что блок задания начальных условий выполнен на последовательно соединенных одновибраторах и D-триггере, причем вход одновибратора является пер

вым входом блока, выход соединен с R-вхо- дом D-триггера, С-вход которого является вторым входом блока, а выход - выходом блока.

3. Преобразователь по п. 1, от л и ч а ю- щ и и с я тем, что блок задержки выполнен на последовательно соединенных одновиб- раторе и элементе И, причем вход одновибратора является вторым входом блока, выход соединен с первым входом элемента И, второй вход которого является первым входом блока, а выход - выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода азимута | 1990 |

|

SU1755276A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Управляемая линия задержки | 1988 |

|

SU1647863A1 |

| Преобразователь угол-код | 1988 |

|

SU1596461A1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Формирователь импульсных последовательностей | 1988 |

|

SU1539973A1 |

| Устройство для регистрации аналогового процесса | 1989 |

|

SU1774379A1 |

Изобретение относится к технике цифро-аналогового преобразования и может быть использовано в системах автоматического регулирования. Изобретение позволяет повысить быстродействие и точность преобразования. Для этого в преобразователь код-ШИМ-сигнал введены второй триггер, первый и второй элементы И, блок начальных условий, блок задержки, суммирующая матрица и второй компаратор. 2 з.п. ф-лы, 4 ил.

Фиг. 2

Фиг.З

To 2TQ 3T0 tT0 - srQ ФигЛ

L.UJ и2

3F

-U5 U6

U7

Щ

9 U,o

и и

| Преобразователь "КОД-ШИМ | 1981 |

|

SU993470A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Практическая схемотехника в промышленной автоматике М Энергоатомиздат, 1987, с 252 | |||

Авторы

Даты

1991-07-30—Публикация

1989-08-29—Подача