Изобретение относится к вычислительной технике и предназначено для использования в устройстве отображения информации (УОИ) импульсного метеорадиолокатора (МРЛ) в качестве преобразователя двоичного усеченного кода азимута антенны в число-импульсный код (импульсы нулевого направления и приращения положения антенны МРЛ по азимуту) и азимутальные импульсы 90, 45, 30, 10 и 5°.

В структуре УОИ МРЛ, можно выделить ряд составных частей, в их числе векторный индикатор, имеющий входы управления положением и яркостью луча его электроннолучевой трубки (ЭЛТ), пульт управления, устройство интерфейса, генераторы напряжений разверток для управления положением луча ЭЛТ индикатора, формирователь видеоимпульсов изображения для управления яркостью луча ЭЛТ индикатора, запоминающее устройство оперативной и постоянной информации, микропроцессор для выполнения всех требуемых арифметических и логических операций, преобразователь кода азимута, устройство программного управления, устройство син- хр миоации и временных программ, устройство имитации и контроля и шины данных (ШД), адреса (ША) и управления (ШУ), с помощью которых производится передача информации в процессе функционирования УОИ.

Работа УОИ в МРЛ организована по периодам-циклам То, каждый из которых состоит из периода Тпх прямого и периода Тох обратного ходов таких, что

То , где fo - частота импульсов запуска УОИ.

В течение каждого Т0 осуществляются прием параллельного или последовательного двоичного кода азимута отазимутальиого датчика антенны и соответствующие операции преобразования гринятого кода, причем в течение каждого ТПх происходит отображение первичной информации МРЛ в процессе формирования линии развертки азимут-дальность по текущему коду дальности и по коду азимута, принятому в предыдущем Т0, а в течение Т0х сначала осуществляется отображение вторичной информации МРЛ, а затем производится подготовка УОИ для отображения первичной информации МРЛ в последующем Т0 с помощью кода азимута, поступившего на УОИ в текущем Т0.

Если частота fA изменения кода А азимута А и частота fc связаны соотношением

fA fo(1)

то при вращении антенны код А за период Т0 может измениться более, чем на один

квант. Поэтому для случая (1) без принятия специальных мер линии масштабной азимутальной сетки, видеосигналы которой генерируются формирователем видеосигналов

изображения по азимутальным импульса 30 и 10° (или 5°), будут отображаться нерегулярно на экране индикатора УОИ, что не допускается требованиями, предъявляемыми к информационным моделям, формируемым на экране УОИ.

Известен преобразователь, содержащий датчик прямого и инверсного кода угла, коммутатор кодов, компаратор, элемент ИЛИ-НЕ, блок памяти, болк формирования

признаков меток, блок синхронизации и блок/правления.

Основным недостатком преобразователя является то, что он имеет недостаточные функциональные возможности, поскольку

не вырабатывает число-импульсный код азимута и формирует азимутальные импульсы без учета соотношения (1).

Наиболее близким по технической сущности к предлагаемому является цифровой

преобразователь координат, содержащий регистр, счетчик, коммутатор, блок памяти, элементы 2 И-ИЛИ, регистр меток, генератор серии импульсов, два компаратора, элемент И, ключи, элемент ИЛИ-НЕ, вход

последовательного (2 + п) разрядного двоичного кода азимута, входы синхронизации и выходы число-импульсного кода и азимутальных импульсов 30 и 5°.

Основным недостатком преобразователя является его сложность, обусловленная тем, что он функционирует по содержащемуся в регистре полноразрядному коду азимута, являющегося информационно-избыточным для выполнения преобразователем его функций. Кроме того, частью указанного недостатка преобразователя является наличие в нем блока памяти, имеющего при п 10 четыре адресных входа и девять информационных выходов. Это, например, при реализации блока памяти на интегральных схемах (ИС) 556РТ4, требует для изготовления преобразователя наличия специальной аппаратуры для программирования ИС его блока памяти,

Цель изобретения - упрощение преобразователя и дополнительное формирование им импульсов 90,45 и 10° за счет работы с усеченным (2 + К) - разрядным двоичным

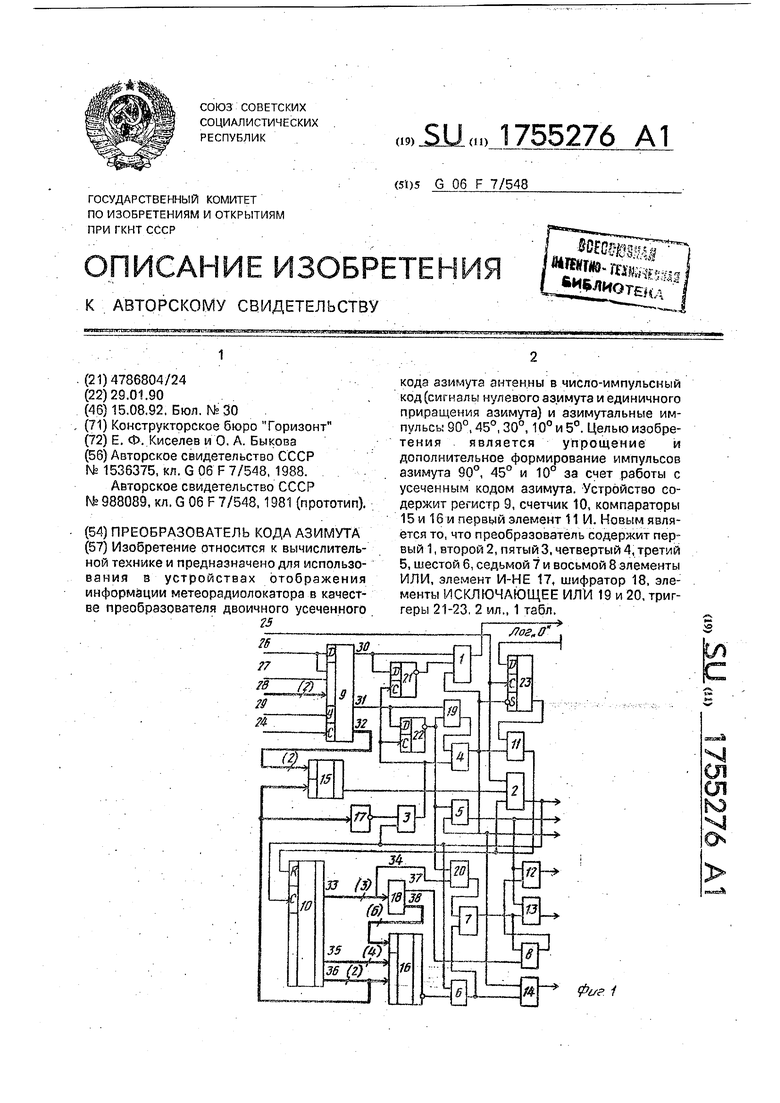

кодом азимута, образованным первым и третьим старшими разрядами и К 2 младшими разрядами (2 + п) разрядного кода А азимута А с весом старшего разряда 180°, На фиг. 1 приведена функциональная

схема преобразователя; на фиг, 2 - функциональная схема шифратора для реализации преобразователя при п 10 и К 2.

Преобразователь (фиг. 1) содержит первый 1, второй 2, пятый 3, четвертый 4,третий 5, шестой 6, седьмой 7и восьмой 8 элементы ИЛИ, четырехразрядный регистр 9, девятиразрядный счетчик 10, первый 11, четвертый 12, третий 13, и второй 14 элементы И, первый 15 и второй 16 компараторы, элементы 17 И-НЕ, шифратор 18, первый 19 и второй 20 элементы ИСКЛЮЧАЮЩЕЕ ИЛ И, три триггера с первого 21 по третий 23 соответственно, первый 24 и второй 25 тактовые входы, вход кода азимута, образованный одноразрядными входами 26 и 27 и двухразрядным входом 28, вход 29 задания режима, выходы 30, 31 и 32 первого старшего, второго старшего и двух младших разрядов регистра 9 соответственно, выходы 33 группы старших разрядов счетчика 10, выход 34 младшего разряда выходов 33, вторую 35 и первую 36 группы выходов младших разрядов счетчика 10, второй 37 и первый 38 выходы шифоатора 18. Причем первый информационный вход 26 соединен с входом последовательного кода и с первым информационным входом регистра 9, у которого управляющий вход и остальные информационные входы соединены с входом 29 и с входами 27, 28 соответственно. Выход 30 регистра 9 соединен с информационным входом первого триггера 21 и с вторым входом первого элемента 1 ИЛИ, первый вход которого соединен с инверсным выходом первого триггера 21. Выход 31 регистра 9 соединен с информационным входом второго триггера 22 и с вторым входом первого элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ. Тактовый вход 24 соединен с синхронизирующим входом регистра 9. Тактовый вход 25 соединен с вторым входом второго элемента 2 ИЛИ и с синхронизирующим входом третьего триггера 23,

информационный вход которого соединен с шиной О преобразователя, а прямой выход соединен с вторым входом первого элемента 11 И, Выход 32 регистра 9 соединен с первым входом первого компаратора 15, прямой выход признака равенства которого соединен с первым входом второго элемента 2 ИЛИ. Второй вход второго компаратора 16 соединен с первым выходом 38 шифратора 18, вход которого соединен с выходами 33 счетчика 10, вторая 35 и первая 36 группы выходов младших разрядов которого соединены с первым входом второго компаратора 16. Группа выходов 36 счетчика 10 соединена с вторым входом первого компаратора 15 и связана через элемент 17 И-НЕ с вторым входом пятого элемента 3

ИЛИ. Первый вход четвертого элемента 4 ИЛИ соединен с выходом первого элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с вторым входом третьего

элемента 5 ИЛИ, с первым входом второго элемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ и с инверсным выходом второго триггера 22. Выход первого элемента 11 И соединен с входом установки з О счетчика Юистреть0 им входом второго элемента 2 ИЛИ, выход которого соединен со счетным входом счетчика 10, с первым входом пятого элемента 3 ИЛИ и с первым входом шестого элемента

6ИЛИ, второй вход которого соединен с 5 инверсным выходом признака равенства

второго компаратора 16. Выход третьего элемента 5 ИЛИ соединен с вторыми входами четвертого 12 и третьего 13 элементов И. Выход четвертого элемента 4 ИЛ И соединен

0 с третьим входом первого элемента 1 ИЛИ, с входом установки в 1 третьего триггера 23, с первым входом второго элемента 14 И и с первыми входами третьего элемента 5 ИЛИ и первого элемента 11 И. Выход 34

5 младшего разряда группы выходов 33 счетчика 10 соединен с вторым входом второго элемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом седьмого элемента 7 ИЛИ, выход которого соеди0 нен с первым входом третьего элемента 13 И и с вторым входом восьмого элемента 8 ИЛИ. Выход шестого элемента 6 ИЛИ соединен с первым входом седьмого элемента

7ИЛИ и с вторым входом второго элемента 5 14 И. Второй выход 37 шифратора 18 соединен с первым входом восьмого элемента 8 ИЛИ, выход которого соединен с первым входом четвертого элемента 12 И. Выход пятого элемента 3 ИЛИ соединен с вторым

0 входом четвертого элемента 4 ИЛИ и с синхронизирующими входами первого 21 и второго 22 триггеров, э выходами с преобразователей импульсов нулевого направления азимута и импульсов единичных

5 приращений двоичного кода азимута и азимутальных импульсов 90, 45, 30, 10 и 5° являются выходы первого 1 и второго 2 элементов ИЛИ и выходы третьего элемента 5 ИЛИ, четвертого элемента 4 ИЛИ, четверто0 го элемента 12 И, третьего элемента 13 И и второго элемента 14 И соответственно.

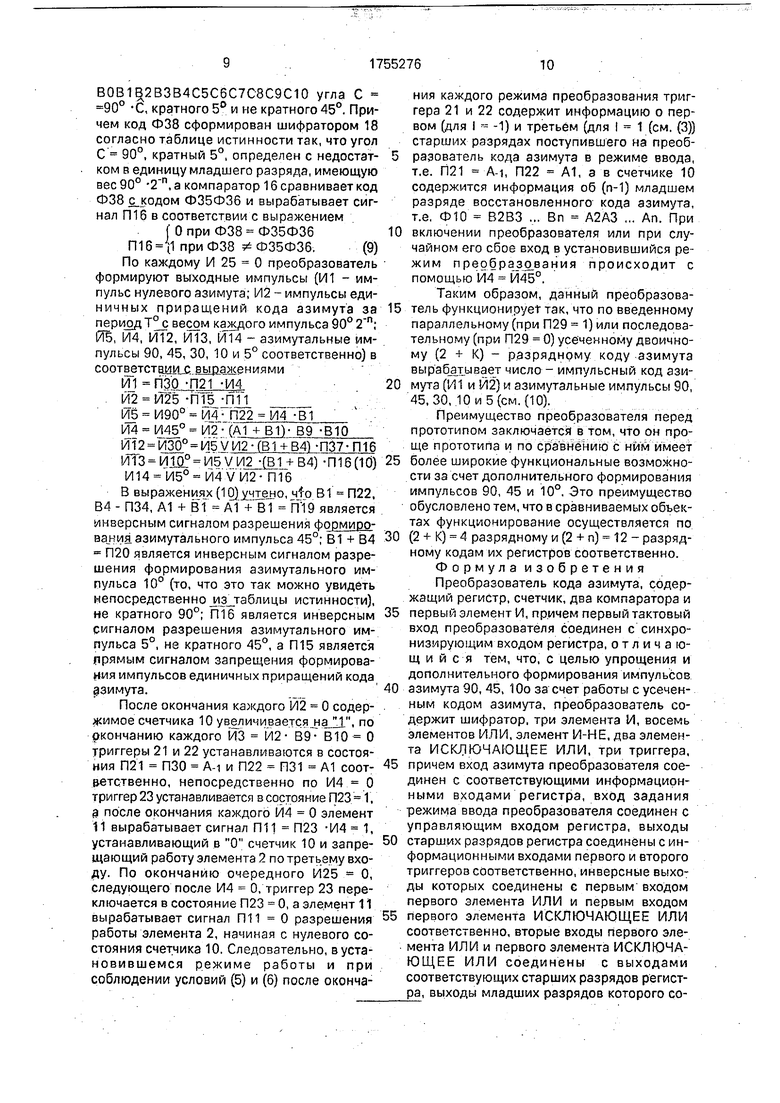

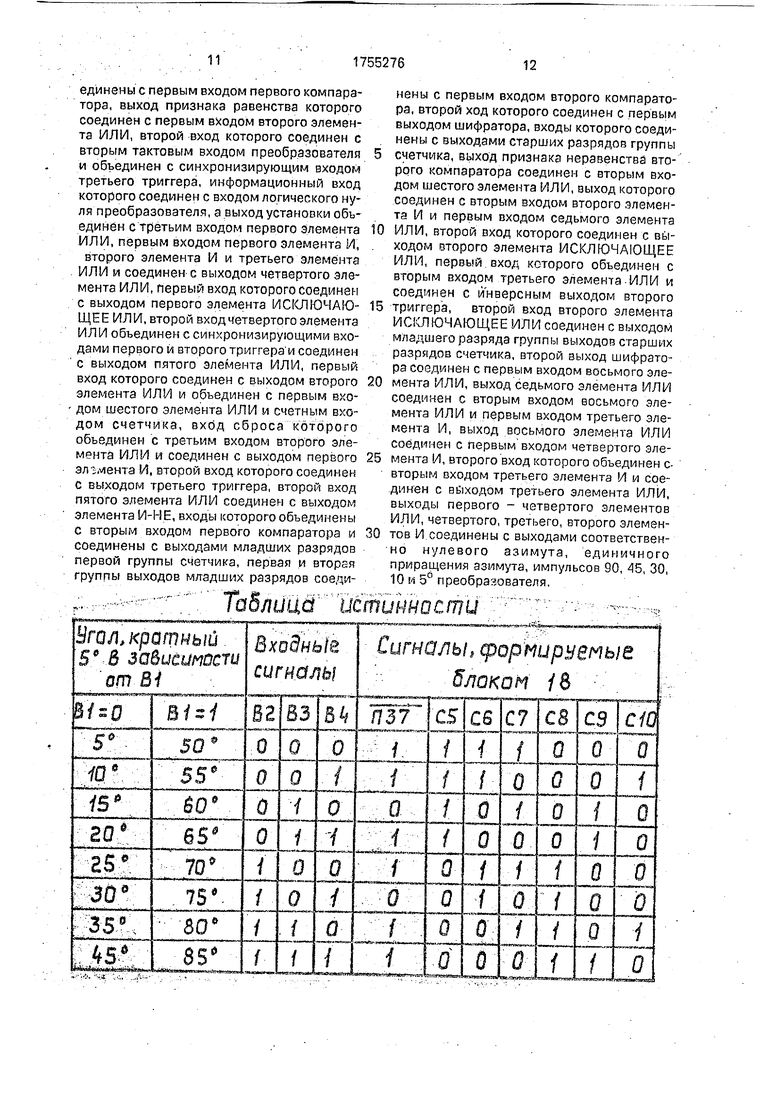

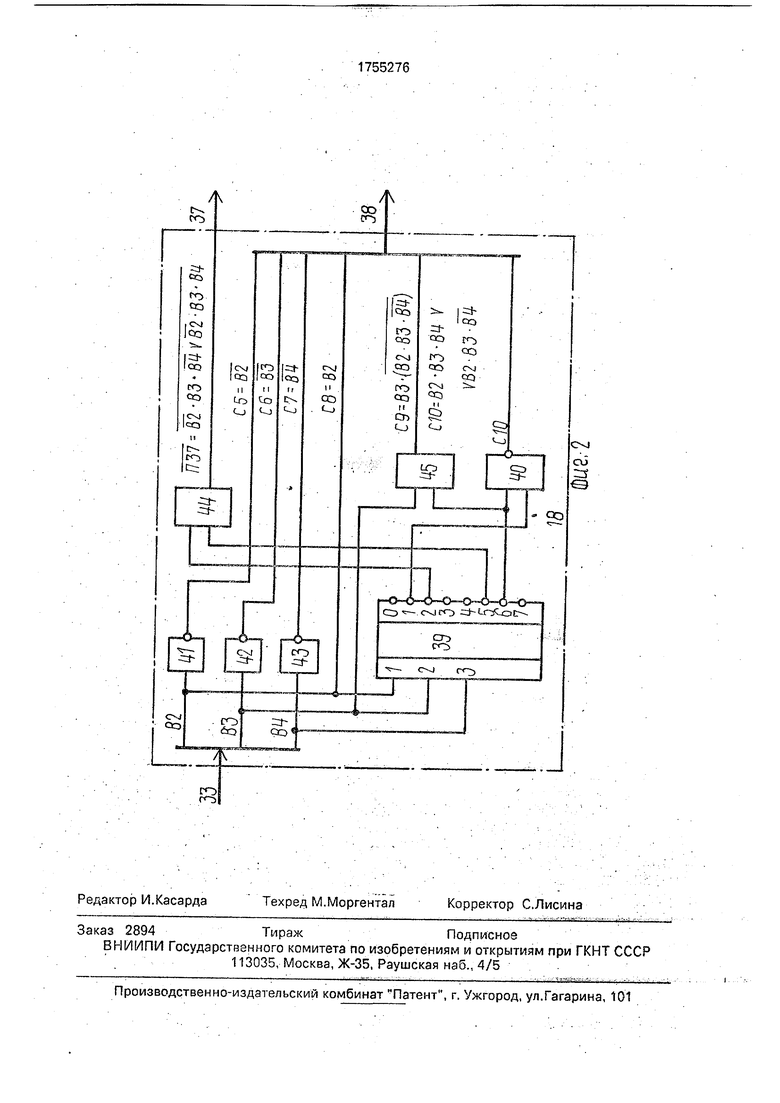

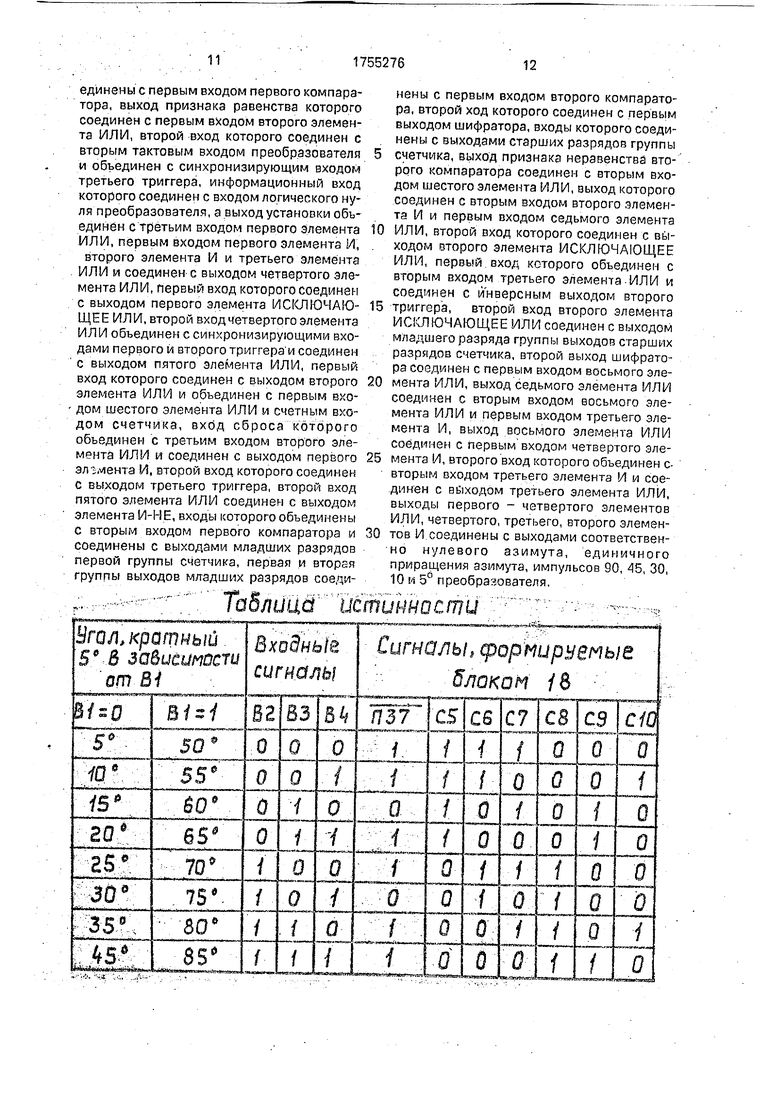

Шифратор 18 (фиг. 2) содержит дешифратор 39, элементно И-НЕ, три элемента 41, 42,43 НЕ, два элемента 44 и 45 И и функци5 онирует согласно таблице истинности.

Преобразователь (фиг. 1, 2} реализован на ИС серии 533 для к 2 и п 10 так, что регистр 9 выполнен в виде ИС 533 ИР11, счетчик 10 содержит две ИС 533 ИЕ5 и D- триггер в качестве младшего разряда счетчика 10, D-триггер счетчика 10 и триггеры 21, 22 и 23 выполнены на двух ИС 533 ТМ2. Компаратор 15 содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИЛИ-НЕ. Компаратор 16 содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ-НЕ, ИС 533 СП1 и элемент НЕ. Дешифратор 39 представляет собой ИС 533 ИД7, а остальные составные части преобразователя, включая комбинационные элементы компараторов 15 и 16 и блока 18, выполнены на соответствующих ИС серии 533.

Обозначим на входах и выходах преобразователя и его узлов через Ф, П , П и И соответственно коды, прямые потенциальные сигналы, инверсные потенциальные сигналы и инверсные импульсы (прямых импульсов в преобразователе не вырабатывается) так, что после каждой из этих букв стоит номер входа преобразователя или выхода его узла, или номер самого узла, например, Ф28, П29, П37 и И24 обозначают код на входе 28, прямой потенциальный сигнал на входе 29, инверсный потенциальный сигнал на выходе 37 и инверсный импульс на входе 2 соответственно.

Кроме того, обозначим ПЗО А-1, П31 А1, Ф32 А910, П21 В-1, П22 В1, Ф10 ФЗЗ Ф35 Ф36 В2ВЗВ4В5В6В7В8В9В10 (где ФЗЗ В2ВЗВ4, Ф35 В5В6В7В8, Ф36 В9В10), П34 В4, Ф38 В5С6С7С8С9СШ (где AJ - разрядная цифра О или 1 I - того разряда кода азимута, содержащегося в регистре 9; В| - разрядная цифра кода В азимута, восстанавливаемого триггерами 21 и 22 и счетчиком 10 в процессе функционирования преобразователя; Ci - разрядная цифра кода С кратного узлу 5° (см. табл. истинности) угла, не совпадающего с углом (азимутом) 45° . N (где N 0, 1, 2,...). Причем на фиг. 1 над наклонной чертой, пересекающей шины кодов Ф28, Ф32, ФЗЗ, Ф35, Ф36, Ф38, в круглых скобках проставлены разрядности этих кодов.

В процессе функционирования преобразователя изменение информации в регистре 9, счетчике 10 и триггерах 21, 22 и 23 производится по положительным фронтам импульсов И24, И2, ИЗ, ИЗ и Й25 соответственно, а установка в 1 триггера 23 и в О счетчика 10 осуществляется непосредственно по И4 0 и П11 1 соответственно.

Временные программы поступления на преобразователь импульсов И 24 и И25, сигналов П26 и П27 и кода Ф 28 определяют его функционирование во времени так, что в его работе можно выделить следующие три режима: режим ожидания; режим ввода; режим преобразования.

Чередование режимов работы преобразователя (т.е. взаимосинхронизация его входных импульсов и сигналов) обеспечивается в УОИ устройством синхронизации и

временных программ и устройством программного управления.

С учетом изложенного работу преобразователя (фиг. 1, 2) можно описать следующим образом.

В режиме ожидания на входах 24 и 25 импульсы тактирования преобразователя отсутствуют, а в его памяти содержится информация, обусловленная предысторией его работы.

В режиме ввода на преобразователь поступает импульс И24 0 записи при ПИ29 1 или четыре импульса И24 0 сдвига при П 29 Ои2 + К 4- разрядный двоичный усеченный код азимута

Аус-П26П27Ф28 А-1А1А9А10 (2)

в виде параллельного кода с входов 26, 27 и 28 при П29 1 или последовательного кода с входа 26 при П29 - 0, соответствующий 2 + п 12 - разрядному полному двоичному коду

А

J А,-2-,

(3)

определяющему азимут (угол) в градусах согласно выражению

А-90°-А,(4)

где AI - разрядная цифра О или 1 i - того 0 -1,0,1,2,..., п) разряда кода А азимута А. В преобразователе соотношение (1) учтено тем, что период Т0 частоты выполнения режима ввода (или режима преобразования, выполняемого в течение каждого Т0 после режима ввода) и скорость изменения кода А таковы, что за время Т0 код (3) может изменится не более,чем на

М 2К - 1 3(5)

квантов, а режим преобразования со- стоит § подаче на преобразователь импульсов И25 0, число которых равно

4.,(6)

В режиме преобразования перед поступлением очередного И25 0 компаратор 15 сравнивает коды Ф32 А9А10 и ФЗб В9В10 и вырабатывает сигнал

О при Ф32 Ф36 П 15 1 при Ф32 Ф36, (7) по коду ФЗЗ В2ВЗВ4 шифратор 18 вырабатывазт сигнал

П 37 В2 ВЗ -В4 V В2 ВЗ В4 (8) разрешения формирования азимутального импульса 30° не кратного 90° и код ФЗЗ С5С6С7С8С9С10, определяющий младшие, разрядыкодаС В-1

BOB1%2B3B4C5C6C7C8C9C10 угла С - 90° -С, кратного 5° и не кратного 45°. Причем код Ф38 сформирован шифратором 18 согласно таблице истинности так, что угол С 90°, кратный 5°, определен с недостатком в единицу младшего разряда, имеющую вес 90° , а компаратор 16 сравнивает код Ф38 с кодом Ф35Ф36 и вырабатывает сигнал П16 в соответствии с выражением

( 0 при Ф38 Ф35Ф36 при Ф38 Ф35Ф36.(9)

По каждому И 25 0 преобразователь формируют выходные импульсы (И1 - импульс нулевого азимута; И2 - импульсы еди- ничных приращений кода азимута за период весом каждого импульса 90° ЙТэ, И4, И12, И13, И14 - азимутальные импульсы 90, 45, 30, 10 и 5° соответственно) в соответствии выражениями ПЗО -П21 -И4.

Й2 И25

И5 И90° И4 П22 И4 -В1

И4 - И45° И2(А1 +В1)- В9 -В10 И12 ИЗО0 И5УЙ2-(В1 + В4)-П37-П16 И13 И10 Й5УИ2 В 1+В4) -П16(10) И14 И5°-Й4УИ2- П16 В выражениях (10)учтено, В1 П22, В4 - П34, А1 + В1 А1 + 81 П 19 является инверсным сигналом разрешения азимутального импульса 45°; В1 + В4 П20 является инверсным сигналом разрешения формирования азимутального импульса 10° (то, что это так можно увидеть непосредственно з таблицы истинности), не кратного 90°; П16 является инверсным сигналом разрешения азимутального импульса 5°, не кратного 45°, а П15 является прямым сигналом запрещения формирования импульсов единичных приращений кода рзимута.

После окончания каждого И2 О содержимое счетчика 10 увеличивается наЛ1, по ркончанию каждого ИЗ Й2 В9- В10 О триггеры 21 и 22 устанавливаются в состояния П21 ПЗО А-1 и П22 П31 А1 соответственно, непосредственно по И4 О триггер 23 устанавливается в состояние П23 1, 9 после окончания каждого Й4 0 элемент 11 вырабатывает сигнал П11 П23 -И4 1, устанавливающий в О счетчик 10 и запрещающий работу элемента 2 по третьему входу. По окончанию очередного И25 О, следующего после И4 0, триггер 23 переключается в состояние П23 0, а элемент 11 вырабатывает сигнал П11 0 разрешения работы элемента 2, начиная с нулевого состояния счетчика 10. Следовательно, в установившемся режиме работы и при соблюдении условий (5) и (6) после окончания каждого режима преобразования триггера 21 и 22 содержит информацию о первом (для I - -1) и третьем (для I 1 (см. (3)) старших разрядах поступившего на преобразователь кода азимута в режиме ввода, т.е. П21 - А-1, П22 А1, а в счетчике 10 содержится информация об (п-1) младшем разряде восстановленного кода азимута, т.е. Ф10 В2ВЗ ... Bn A2A3 ... An. При

0 включении преобразователя или при случайном его сбое вход в установившийся режим преобразования происходит с помощью И4 Й45°.

Таким образом, данный преобразова5 тель функционирует так, что по введенному параллельному (при П29 1) или последовательному (при П29 0) усеченному двоичному (2 + К) - разрядному коду азимута выраб атывае т число - импульсный код ази0 мута (И1 и Й2) и азимутальные импульсы 90, 45,30, 10 и 5 (см. (10).

Преимущество преобразователя перед прототипом заключается в том, что он проще прототипа и по сравнению с ним имеет

5 более широкие функциональные возможности за счет дополнительного формирования импульсов 90, 45 и 10°. Это преимущество обусловлено тем, что в сравниваемых объектах функционирование осуществляется по

0 (2 + К) 4 разрядному и (2 + п) 12 - разрядному кодам их регистров соответственно. Формула изобретения Преобразователь кода азимута, содержащий регистр, счетчик, два компаратора и

5 первый элемент И, причем первый тактовый вход преобразователя соединен с синхронизирующим входом регистра, отличающийся тем, что, с целью упрощения и дополнительного формирования импульсов

0 азимута 90, 45, 10о за счет работы с усеченным кодом азимута, преобразователь содержит шифратор, три элемента И, восемь элементов ИЛИ, элемент И-НЕ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, три триггера,

5 причем вход азимута преобразователя соединен с соответствующими информационными входами регистра, вход задания режима ввода преобразователя соединен с управляющим входом регистра, выходы

0 старших разрядов регистра соединены с информационными входами первого и второго триггеров соответственно, инверсные выходы которых соединены с первым входом первого элемента ИЛИ и первым входом

5 первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, вторые входы первого элемента ИЛИ и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами соответствующих старших разрядов регистра, выходы младших разрядов которого соединены с первым входом первого компаратора, выход признака равенства которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с вторым тактовым входом преобразователя и объединен с синхронизирующим входом третьего триггера, информационный вход которого соединен с входом логического нуля преобразователя, а выход установки объединен с третьим входом первого элемента ИЛИ, первым входом первого элемента И, второго элемента И и третьего элемента ИЛИ и соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход четвертого элемента ИЛИ объединен с синхронизирующими входами первого и второго триггера и соединен с выходом пятого элемента ИЛИ, первый вход которого соединен с выходом второго элемента ИЛИ и объединен с первым входом шестого элемента ИЛИ и счетным входом счетчика, вход сброса которого объединен с третьим входом второго эле- ИЛИ и соединен с выходом первого эл ;,иента И, второй вход которого соединен с выходом третьего триггера, второй вход пятого элемента ИЛИ соединен с выходом элемента И-НЕ, входы которого объединены с вторым входом первого компаратора и соединены с выходами младших разрядов первой группы счетчика, первая и вторая группы выходов мяадших разрядов соединены с первым входом второго компаратора, второй ход которого соединен с первым выходом шифратора, входы которого соединены с выходами старших разрядов группы

счетчика, выход признака неравенства второго компаратора соединен с вторым входом шестого элемента ИЛИ, выход которого соединен с вторым входом второго элемента И и первым входом седьмого элемента

ИЛИ, второй вход которого соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого объединен с вторым входом третьего элемента ИЛИ и соединен с й нверсным выходом второго

триггера, второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом младшего разряда группы выходов старших разрядов счетчика, второй выход шифратора соединен с первым входом восьмого элемента ИЛИ, выход седьмого элемента ИЛИ соединен с вторым входом восьмого элемента ИЛИ и первым входом третьего элемента И, выход восьмого элемента ИЛИ соединен с первым входом четвертого элемента И, второго вход которого объединен с- вторым входом третьего элемента И и соединен с выходом третьего элемента ИЛИ, выходы первого - четвертого элементов ИЛИ, четвертого, третьего, второго элементов И соединены с выходами соответственно нулевого азимута, единичного приращения азимута, импульсов 90, 45, 30, 10 и 5° преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь полярных координат | 1990 |

|

SU1742817A1 |

| Генератор векторов | 1981 |

|

SU993312A1 |

| Генератор напряжений | 1990 |

|

SU1728978A1 |

| Генератор напряжений | 1990 |

|

SU1791956A1 |

| Генератор векторов | 1982 |

|

SU1056256A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

Изобретение относится к вычислительной технике и предназначено для использо- вания в устройствах отображения информации метеорадиолокатора в качестве преобразователя двоичного усеченного 25 кода азимута антенны в число-импульсный код (сигналы нулевого азимута и единичного приращения азимута) и азимутальные импульсы 90°, 45°, 30°, 10° и 5°. Целью изобретения является упрощение и дополнительное формирование импульсов азимута 90°, 45° и 10° за счет работы с усеченным кодом азимута. Устройство содержит регистр 9, счетчик 10, компараторы 15 и 16 и первый элемент 11 И. Новым является то, что преобразователь содержит первый 1, второй 2, пятый 3, четвертый 4, третий 5, шестой б, седьмой 7 и восьмой 8 элементы ИЛИ, элемент И-НЕ 17, шифратор 18, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 19 и 20, триггеры 21-23 2 ил., 1 табл. Лог О pif 1

Втл,кратный 5е В зависимости от ЈН

В/ 0

1:1

5

О

15

о

65

70

1

о

75

30

О /

1

Q

. 45

ЗДи&КвшК&гзШЙя

СВ

С7

сз

сю

6

f

«kcw.

/

Q

Q

i

1

О

Редактор И.Касарда

Техред М.Моргентал

Заказ 2894ТиражПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Корректор С.Лисина

| Цифровой преобразователь координат | 1988 |

|

SU1536375A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР № 988089, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| (Б) ПРЕОБРАЗОВАТЕЛЬ КОДА АЗИМУТА | |||

Авторы

Даты

1992-08-15—Публикация

1990-01-29—Подача