первый и второй выходы арифметического блока являются соответственно первым и вто рым выходами вычислителя.

4.Устройство по п. 1, отличающееся тем, что блок приоритета содержит блок счетчиков, дешифратор, шифратор, триггеры и элементы ИЛИ, выходы дешифратора подключены к первым входам соответствующих элементов ИЛИ, выходы которых подключены к первым входам соответствующих триггеров, выходы которых подключены к соответствующим входам шифратора, выходы блока счетчиков подключены к вторым входам соответствующих элементов ИЛИ, вход дешифратора и объединенные вход блока счетчиков и вторые входы триггеров являются соответственно первым и вторым входами блока приоритета, выход шифратора является выходом блока приоритета.

5.Устройство по п. 1, отличающееся тем, что блок согласования содержит регистр, щифратор, элементы И и элементы ИЛИ, выходы регистра кроме последнего

подключены к первым входам первых элементов И и соответствующим входам шифратора, последний выход регистра подключен к первым входам второго и третьего элементов И и регистра,. вы,ходы первых и второго элементов И подключены к соответствующим входам первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход шифратора - к первому входу второго элемента ИЛИ, выход которого подключен к второму входу первого элемента ИЛИ, выход третьего элемента ИЛИ подключен соответственно к первому и второму входам третьего элемента ИЛИ, выход третьего элемента ИЛИ подключен к второму входу второго элемента ИЛИ, вторые входь первых элементов И, второй вход второго элемента И, второй вход регистра, второй вход третьего элемента И являются соответственно первым, вторым, третьим и четвертым входами блока согласования, выход второго элемента ИЛИ и последний выход регистра являются соответственно первым и вторым выходами блока согласования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

| Тензометрическое устройство | 1986 |

|

SU1427166A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1988 |

|

SU1574152A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Устройство для сопряжения | 1984 |

|

SU1166126A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СОСТОЯНИЯ ОБЪЕКТА, содержащее датчики, выходы которых подключены к первым входам соответствующих первых аналого-цифровых преобразователей и первым входам коммутатора, выход которого подключен к первому входу второго аналого-цифрового преобразователя, генератор, первый выход которого подключен к первому входу блока управления, выход которого подключен к второму входу коммутатора и входу кодера, второй выход генератора подключен к вторым входам первых и второго аналого-цифровых преобразователей, блок буферной памяти, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены блок согласования, вычислитель, блок приоритета, выходы первых аналого-цифровых преобразователей подключены к соответствующим первым входам блока согласования, первый выход которого подключен к .первому входу вычислителя, первый выход которого подключен к входу блока; буферной памяти, выход второго аналого-цифрового преобразователя подключен к второму входу блока согласования, третий выход генератора подключен к третьему входу блока согласования, выход кодера подключен к четвертому входу блока согласования, второй выход-которого подключен к второму входу вычислителя, второй выход которого подключен к первому входу блока приоритета, выход которого подключен к второму входу блока управления, выход блока управления подключен к второму входу блока приоритета, второй выход генератора подключен к третьему входу вычислителя. 2.Устройство но п. 1, отличающееся тем; что блок управления содержит регистр, эле.менты ИЛИ, элементы И, инвертор, выход.первого элемента И подключен к первому входу регистра, первые выходы которого подключены к соответствующим первым входам вторых элементов И, выходы которых подключены к соответствующим первым входам первых элементов ИЛИ, I выход второго элемента ИЛИ через инвертор подключен к вторым объединенным вхо(Л дам вторых элементов И и первому входу первого элемента И, второй выход регистра подключен к его второму входу, вторые входы первых эле.ментов ИЛИ, первый вход первого элемента И и входы второго элемента ИЛИ подключены соответственно к первому и второму входам блока управления, выходы первых элементов ИЛИ подключены к выходу блока управления. со 3.Устройство по п. 1, отличающееся о тем, что вычислитель содержит блок памяти, арифметический блок, дешифратор, СП СЛ блок постоянной памяти, счетчики, выход первого счетчика подключен через блок постоянной памяти к входу дешифратора, первый выход которого подключен к первому входу ариф.метического блока, второй выход дешифратора подключен к первому входу блока памяти, выход которого подключен к второму входу арифметического блока, выход второго счетчика подключен к второ.му входу блока памяти, выход второго счетчика, третий вход блока памяти и вход первого счетчика являются соответственно первым, вторым и третьим входа.ми вычислителя.

1

Изобретение относится к телеизмерениям и может быть использовано при создании автоматических систем контроля состояния чиъекта.

Известна система сбора аналоговых сигналов на БИС, содержащая аналоговые датчики, аналоговый коммутатор, аналогоцифровой преобразователь (АЦП), микропроцессор 1.

Недостатком этой системы является невысокая достоверность информации о состоянии контролируемого объекта из-за частичной потери информации при контроле быстропротекающих процессов, так как подключение каждого аналогового датчика к АЦП производится периодически, т.е. процесс измерения прерывен.

Наиболее близкой по достигаемому эффекту к изобретению является телеметрическая система для передачи информации с контролем информационных каналов, содержащая N измерительных каналов, где N - число контролируемых параметров, и один контрольный канал. Каждый измерительный канал содержит датчик, выход которого подключен к схеме переключения, одним выходом связанной с входом управляемого мультивибратора, уровень сигнала на выходе которого зависит от напряжения на его входе. Выходы АЦП информационных каналов подсоединены к выходной вентильной схеме, выход которой подключен к выходному детектору уровня, выход которого подключен к входу задатчика . программ, один выход которого связан с входом калибратора, а другой - с распределителем.

Недостатком этой системы является

невысокая достоверность информации о

состоянии контролируемого объекта. Это

объясняется тем, что калибровка каждого

канала производится в одной или нескольких точках, заданных жестко, независимо от точки, в которой производится измерение. Например, в этой системе можно контролировать две точки: первая точка - начало диапазона измерения, вторая точка - конец.

Однако если данные контроля будут соответствовать заданным, т.е. канал будет признан исправным, нет полной уверенности в том, что измерения в других точках характеристики канала произведены верно. Например, от воздействия различных дестабилизирующих факторов (старение элементов, температурные и др.) характеристика канала может «прогнуться в середине (или какой-либо другой части), при этом данные, соответствующие точкам на отрезке «прогиба характеристики канала, будут искажены. Попытка проверять как можно большее количество точек в каждом канале существенно увеличивают периодичночть. контроля каждого канала (так как увеличивается время калибровки одного канала), что также снижает достоверность получаемой информации, а в случаях оперативного использования получаемых данных увеличение периодичности контроля может быть вообще недопустимо.

Целью изобретения является повышение достоверности контроля устройства.

Поставленная цель достигается тем, что в устройство, содержащее датчики, выходы которых подключены к первым входам соответствующих первых аналого-цифровых преобразователей и первым входам коммутатора, выход которого подключен к первому входу второго аналого-цифрового преобразователя, генератор, первый выход которого подключен к первому входу блока управления, выход которого подключен к второму входу коммутатора и входу кодера, второй выход генератора подключен к вторым входам первых и второго аналогоцифровых преобразователей, блок буферной памяти, введены .блок согласования, вычислитель, блок приоритета, выходы первых аналого-цифровых преобразователей подключены к соответствующим первым входам блока согласования, первый выход которого подключен к первому входу вычислителя, первый вход которого подключен к входу блока буферной памяти, выход второго аналого-цифрового преобразователя подключен к второму входу блока согласования, третий выход генератора подключен к третьему входу блока согласования, выход кодера подключен к четвертому входу блока согласования, второй выход которого подключен ко второму входу вычислителя, второй выход которого подключен к первому входу блока приоритета, выход которого подключен к второму входу блока управления, выход блока управления подключен к второму входу блока приоритета, второй выход генератора подключен к третьему входу вычислителя.

Блок управления содержит регистр, элементы ИЛИ, элементы И, инвертор, выход первого элемента И подключен к первому входу регистра, первые выходы которого подключены к соответствующим первым входам вторых элементов И, выходы которых подключены к соответствующим первым входам первых элементов ИЛИ, выход второго элемента ИЛИ через инвертор подключен к вторым объединенным входам BTopbix элементов И и первому входу первого элемента И, второй выход регистра подключен к его второму входу, вторые входы первых элементов ИЛИ объединены с соответствующими входами второго элемента ИЛИ, первый вход первого элемента И и входы второго э емента ИЛИ подключены соответственно к первому и второ.му

входам блока управления, выходы первых элементов ИЛИ подключены к выходу блока управления.

В вычислитель введены блок памяти, арифметический блок, дешифратор, блок постоянной памяти, счетчики, выход первого счетчика подключен через блок постоянной памяти к входу дещифратора, первый выход которого подключен к первому входу

арифметического блока, второй выход дещифратора подключен к первому входу блока памяти, выход которого подключен к второму входу арифметического блока, выход второго счетчика подключен к второму

входу блока памяти, выход второго счетчика, третий вход блока памяти и вход первого счетчика являются соответственно первым, вторым и третьим входами вычислителя, первый и второй выходы арифметического блока являются соответственно

первым и вторым выходами вычислителя.

В блок приоритета введены блок счетчиков, дещифратор , шифратор, триггеры, элементы ИЛИ, выходы дешифратора под5 ключены к первым входам соответствующих элементов ИЛИ, выходы которых подключены к первым входам соответствующих триггеров, выходы которых подключены к соответствующим входам шифратора, выходы блока счетчиков подключены к вторым входам соответствующих элементов ИЛИ, вход дещифратора и объединенные вход блока счетчиков и вторые входы триггеров являются соответственно первым и вторым входами блока приоритета, выход шифратора

5 является выходом блока приоритета.

В блок согласования введены регистр, шифратор, элементы И, элементы ИЛИ, выходы регистра кроме последнего подключены к первым входам первых элементов И и соответствующим входам иифратора, последний выход регистра подключен к первым входам второго и третьего элементов И и регистра, выходы первых и второго элементов подключены к соответствующим входам

5 первого элемента ИЛИ, выход которого подключен к первому входу второго элемента ИЛИ, выход щифратора - к первому входу второго элемента ИЛИ, выход которого подключен к второму входу первого элемента ИЛИ, выход третьего элемента ИЛИ подключен соответственно к первому и второму входам третьего элемента ИЛИ, выход третьего элемента ИЛИ подключен к второму входу второго элемента ИЛИ, вторые входы первых элементов И, второй вход

5 второго элемента И, второй вход регистра, второй вход третьего элемента И являются соответственно первым, вторым, третьим и четвертым входами блока согласования.

выход второго элемента ИЛИ н последний выход регистра являются соответственно первым и вторым выходами блока согласования.

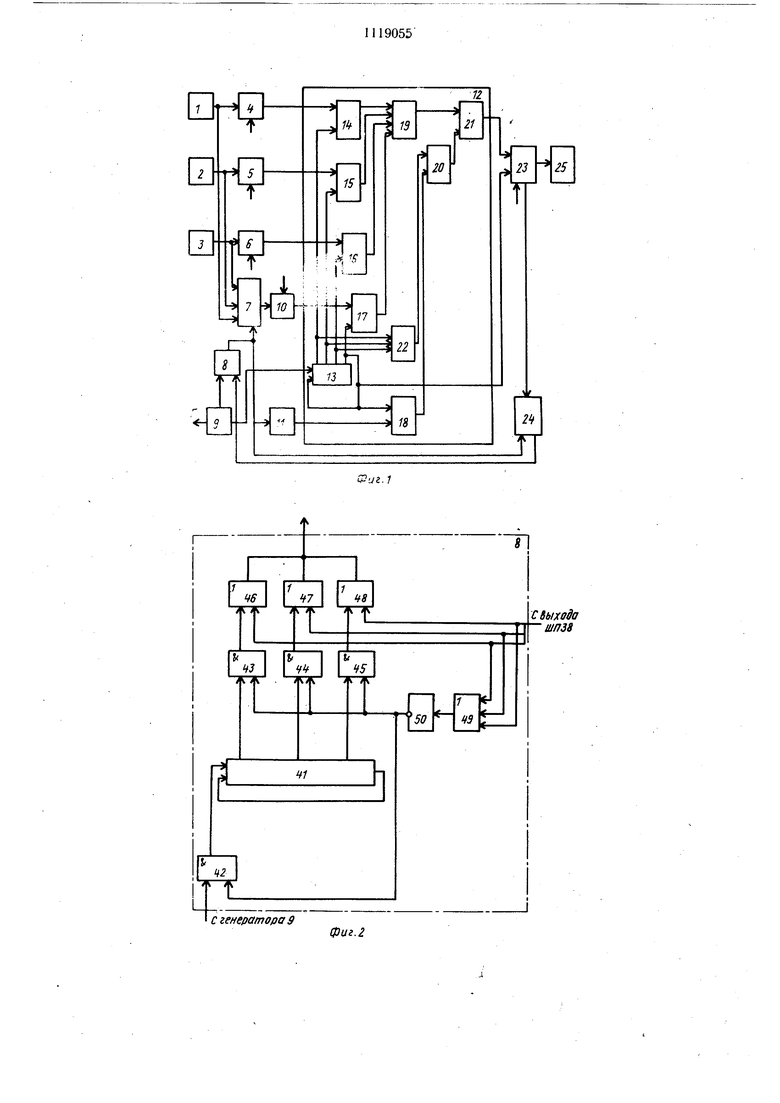

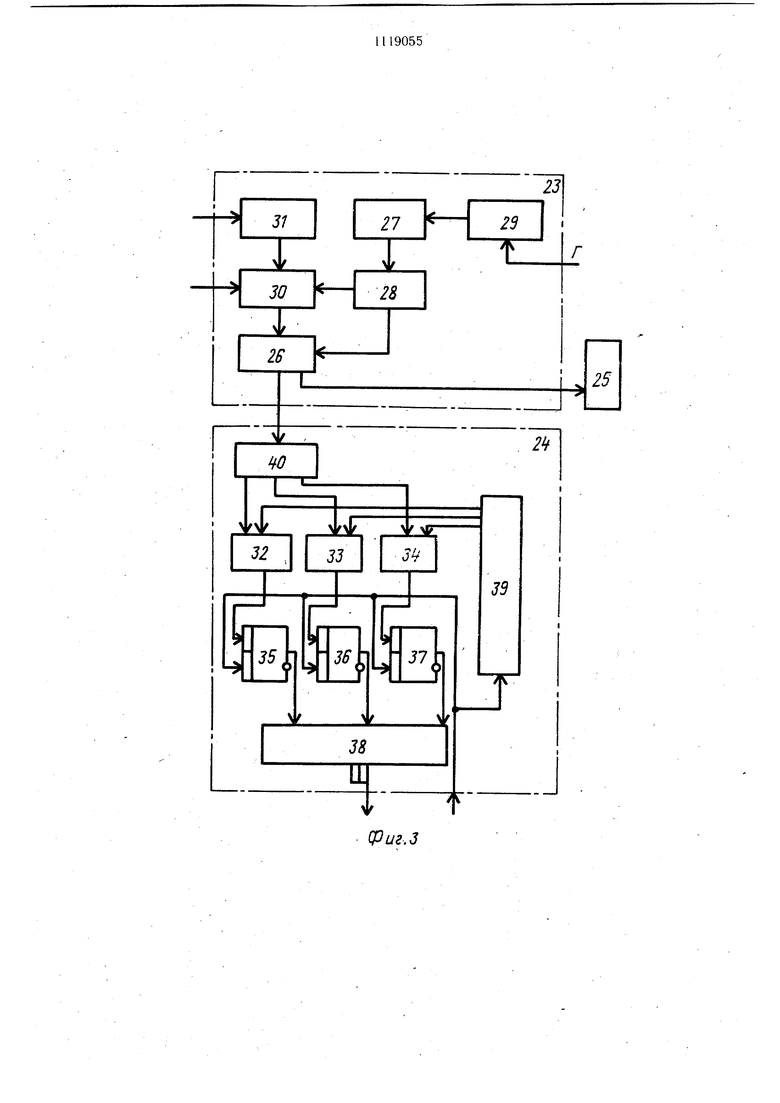

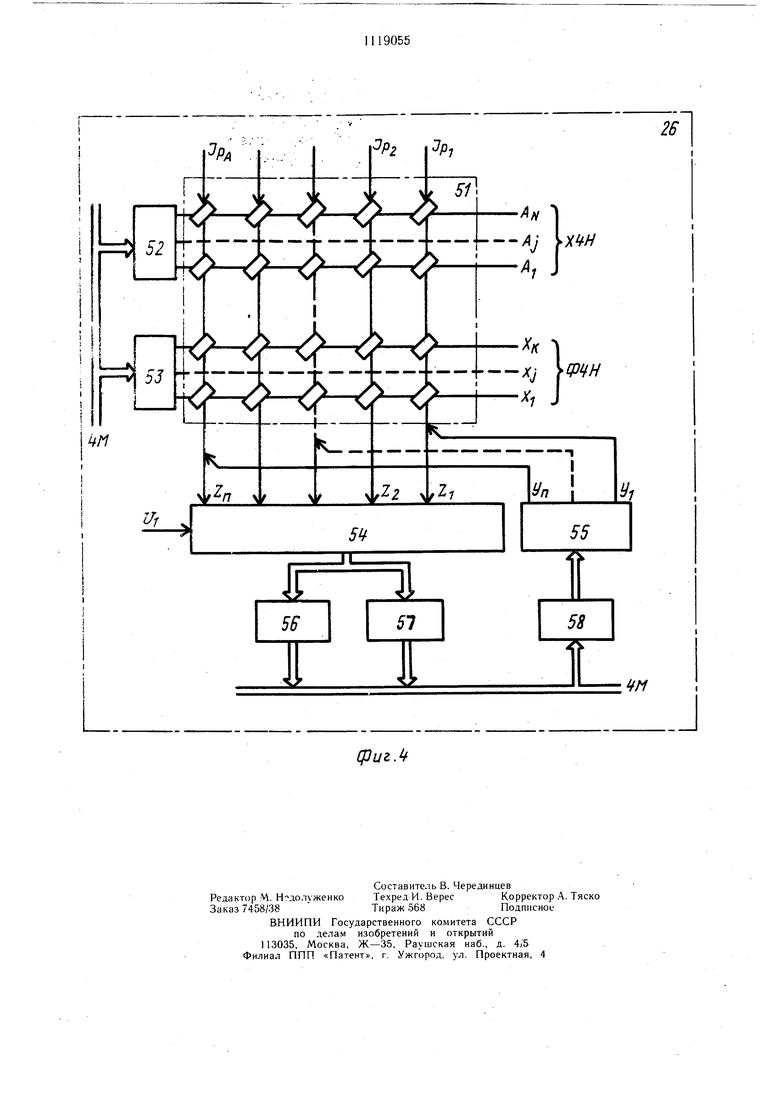

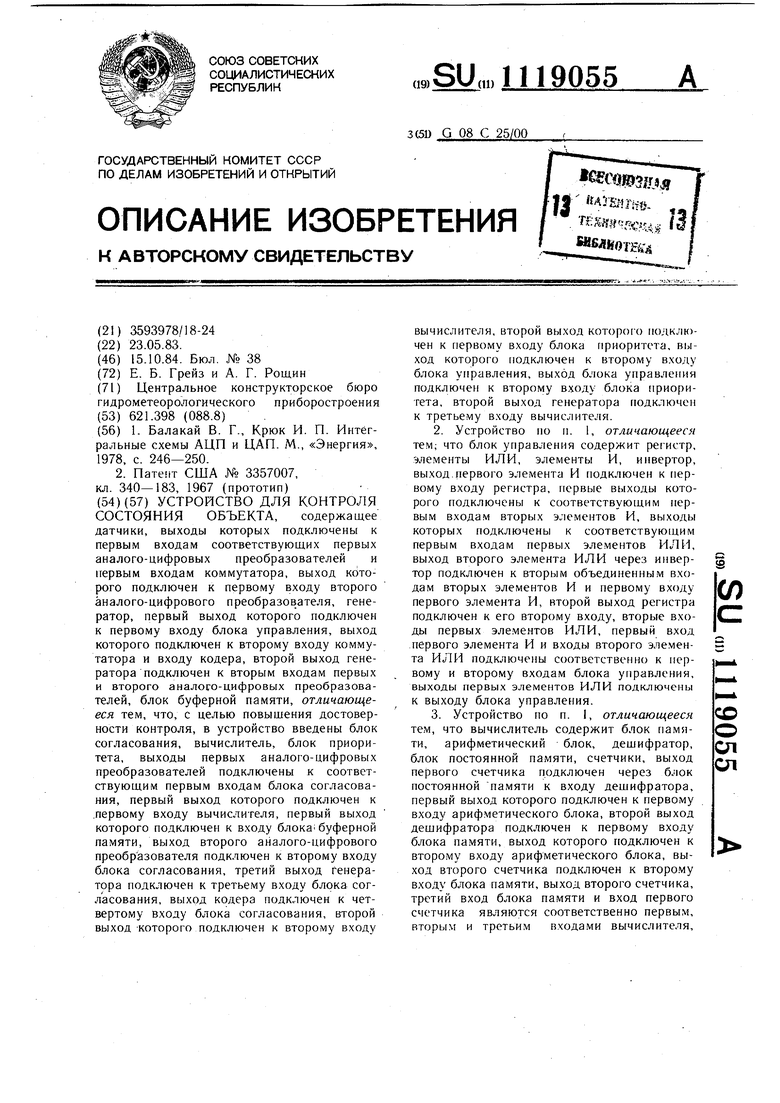

На фиг. 1 представлена структурная схема многоканальной телеметрической системы; на фиг. 2 - пример выполнения блока управления; на фиг. 3 - пример выпол- нения блока вычисления и блока приоритета; на фиг. 4 - пример выполнения арифметического устройства.

Система содержит датчики , АЦП 4-6. коммутатор 7, блок 8 управления, генератор 9, АЦП 10, кодер 11 номера канала, блок 12 согласования, регистр 13, элементы И 14-18, элементы ИЛ И 19-21. шифратор 22 номера канала, вычислитель 23, блок 24 приоритета блок 25 буферной памяти, арифметический блок (АБ) 26, блок постоянной памяти (БПП) 27, дешифратор 28 микрокоманд, счетчик 29, блок 30 памяти, счетчик 31 цикла, элемеиты ИЛИ 32-34, триггеры 35-37, шифратор приоритета (ШП) 38, блок счетчиков времени (БСВ) 39, дешифратор номера канала (ДНК) 40, регистр 41, элементов И 42-45, элементов ИЛИ 46-49, инвертора 50, матричный накопитель 51, дешифратор 52 адреса, блок настройки (БН) 53, усилители 54 воспроизведения (УВ) 54, регистр 55 числа и формирователей записи (РЧ и ФЗ) 55, вентили 56-58.

Система функционирует следующим образом.„.

АЦП 4-6 формирует цифровые коды, соответствующие уровню сигнала из выходе соответствующего датчика. Эти цифровые коды поступают на вычислитель 23. В это же время коммутатор 7, управляемый блоком 8 управления,подключает выходы одного из датчиков 1-3 к входу АЦП 10. Цифровые коды с выхода АЦП 10 через блок 12 согласования также поступают в вычислитель 23. Введем следующие обозначения: Jfl(t)-значение сигнала с выхода i-ro датчика, полученное иа выходе соответствующего датчику АЦП в момент времени t;

Alt -значение сигнала с выхода i-ro датчика, полученное на выходе АЦП 10 в момент времени t, когда этот АЦП 10. был подключен к i-му датчику.

Значения Xi(t) и Ai(i) вводятся в вычислитель 23 через блок 12 согласования, однако с разной частотой. Значения Xt(t) вводятся практически непрерывно (для дискретности времени, принятой в системе), а значения Ai(t) вводятся периодически, причем период ввода А L определяется сигналами с выхода блока 8 управления.

Пусть в некоторый момент времени t АЦП 10 был подключен к i-му датчику

Для момента времени значения Xt(l,) и Ai(t) были введенУ в вычислитель 23. Затем для 1-го датчика в вычислитель 23 вводились значения Xl(j, Xi(y,.., Xi(V,

..., ,Xl(t). Пусть в момент времени tn АЦП 10 вновь подключился к i-му датчику и в вычислитель 23 было введено значение Ai(t. Примем для определенности, что Xt(t|) было минимальным значением ряда

Xi (t), а Х1(1„) - максимальным значением, т.е.

Xi(t,)Xt(tK)AXi(t.)

(1)

При правильном функционировании 15 всех элементов системы должно соблюдаться соотношение Xi(tJ Ai(ti),

(2)

Х{(1„) А1(иУ

При этом (1) запишется как

Aift )Xi(tK)6 Ai(tK). f5) Обозначим Д| At(tn)-Ai(ti). (4

Задавая заранее значение А i для каждого канала, т.е. регулируя величину л i, можно регулировать степень достоверности информации о состоянии контролируемого объекта. При уменьшении значения А i значения Xi (tx) можно получать со сколь-угодно высокой достоверностью, так как при значения Xi()(tn)(tt). С учетом того, что характер нзменеиия измеряемого параметра по каждому каналу неизвестен, в предлагаемой Системе для

каждого канала задается условие

(tK)-Ai(ti),(5)

тем самым задана требуемая достоверность ннформацни о контролируемом параметре. Как только соотйошение (5) нарушается

для какого-либо канала, к выходу датчика этого канала через коммутатор 7 подключается АЦП 10, тем самым определяется значение Ai(tj), где ti - момент времени, перед которым нарушилось соотношение (5).

В блоке вычисления проверяется выполнение соотношения Xi(tj) AL(t) и если соотношение выполняется, то в вычислителе 23 продолжается слежение за выполнениел соотношения (5), в котором значение Ai(ti. заменено значением Ai(tj;.

Для упрощения изложения принципа работы системы рассматривали случаи абсолютного равенства Xt(t) . Ai(t), т.е. получаемые в одни н те же моменты времени значения с выхода АЦП i-ro канала и подключенного к этому кана.лу АЦП 10 совпадают. Однако для этого требуется, чтобы все АЦП 4-6 имели бы такую же точность, .как и АЦП 10. т.о. чтобы ЛЦП « каждом канале имел бы погрешность измерения, не превышающую заданную для соответствующего параметра что экономически нецелесообразно. В предлагаемой системе погрешность измерения АЦП может быть выще, чем требуемая для параметра, т.е. АЦП могут быть неточными, а достоверность информации о состоянии контролируе.мого объекта при этом не снижается. Таким образом в системе допускается частичный отказ АЦП, когда их характеристики изменились вследствие влияния дестабилизирующих факторов (температурных, временных и т.д.) либо из-за отказа одного или нескольких элементов. При таком отказе (т.е. когда произошло изменение характеристики преобразователя - характеристика «сместилась, «выгнулась и т.д.) предлагаемая система позволяет получать данные о соответств юпхем отказавшему АЦП параметру практически с заданной достоверностью. Пусть имеющий низкую (ниже требуемой для параметра) точность АЦП располо жен в i-M канале и пусть вследствие описанных причин характеристика его изменилась. С выхода этого АЦП через блок 12 согласования в вычислитель 23 вводятся значения Xi(t,), Xi(y, Xi(ti), Xi(t). В момент t, к i-му датчику был подключен через коммутатор 7 АЦП 10 и вычислитель 23 введено значение Ai(ti) с выхода .ЛЦП 10 через б,лок 12 согласования. Примем для определенности, что XL(t,) - это минимальное значение гармоничного ряда Xi(ti), Xt(t2), Xt(tb), Xi(t/i), a Xi{U) - максимальное значение этого ряда. Если разность Д Xi Xi(U) -Xl(tt) достаточно мала по отношению ко всему диапазону характеристики АЦП, а промежуток времени t t - t также мал настолько, что параметры элементов АЦП за это время практически постоянны, то можно считать, на участке от Xt(ti) до Xi(t.,) характеристика АЦП имеет вид Y BXi(t) +С, у -выходной сигнал датчика 1; В -const; С -const; Li -значение, принадлежащее ряду Xi(tt),.., Xi(t). Если в момент вторично подключить АЦП 10 к выходу первого датчика (а это осуществляется выбором требуемой величины и - см. (5) и получить значение можно записать Y. At(t,)-BXi(t,) +С, {6} 4 AL(t) BXl(t) + С Значения y и y, получены с требуемой достоверностью, так как сняты с выхода калибратора. В момент t АЦП И) к выходу i-ro датчика не подключался, и известно только что Y BXKta) + С, причем точные значения В и С неизвестны. Из (6) следует AifU) -Ai(tO - (tA) -Xi(tj),(r) B- 4 ta Тогда из первого уравнения (6) Ai(t.),(t.)-fC С А (t)(tx). следовательно, ) + Aid.) (Xi(i,)-Xi( t,i : : |j+Ai(t,i (&) Из (8) вытекает, что значение у. получено практически с такой же достоверностью, что и калиброванные значения YI и у, так как в выражении (8) нет неопределенных величин. Аналогично можи получить и значение YJ по имеющему я жачснмю Xt(t5). Корректировка по.i чаемых значений по формуле „ | ,,. I Y.it Al(in}-Ai(i {п} YK- 1 -S ) - ,)| tg; производится в Р ычислителе 23. Пусть цифровые коды с выходов АЦП 4-6 поступают на вход блока 12 согласования. Коммутатор 7 подключает выходы одного из датчиков 1- 3 к входу АЦП 10. Работой коммутатора 7 управляет блок 8 управления, который работает следующим образом. По начальной установке в первый разряд сдвигающего регистра 41 записывается «1, в остальные разряды этого регистра 41 записан «О. Если с выходов ШП 38 нет ни одного сигнала «1, то на выходе инвертора 50 будет разрешающий сигнал «I, поэтому «1 с первого разряда сдвигающего регистра 41 через элемент И 43 и через элемент ИЛИ 46 поступает на коммутатор 7, на первый ключ этого коммутатора. При поступлении с -генератора 9 и.мпульса на тактирующий (сдвигающий) вход сдвигающего регистра 41 «1 из первого разряда этого регистра сдвигается во второй разряд, а в первом разряде регистра 41 оказывается «О, так как регистр собран по кольцевой схеме, т.е. его вход связан с выходом. При этом «I через элемент И 44 и элемент ИЛИ 47 поступает на коммутатор 7, на второй ключ этого коммутатора и т.д.

Если же на одном из выходов ШП 38 1ЮЯВНТСЯ «1, например, на третьем, свяэанном с элементом ИЛИ 48, то этот снгнал «I, через элемент ИЛИ 48 поступит на коммутатор 7 на его третнй ключ. Одновременно на выходе инвертора 50 появится сигнал «0, запрещающий прохождение сигналов с выходов сдвигающего регистра 41 через элементы И 43-45. Одновременно запрещается прохождение сигналов с генератора 9 через элемент И 42 на сдвигающий вход регистра 41. Поэтому, когда сигнал «1 любого из выходов ШП 38 исчезнет, сдвигающий регистр 41 продолжит работу с прерванного положения.

Следовательно, на элементы И 14-17 поступают параллельные цифровые коды с АЦП 4-6 и АЦП 10, На другие входы этих элементов поступают сигналы с разрядных выходов сдвигающего регистра 13. При этом сигнал «1, т.е. разрещающий {ютенциал записан только в одном разряде сдвигающего регистра 13, в остальных разрядах этого сдвигающего регистра записан «О. Регистр 13 построен по кольцевой схеме, т.е. при сдвиге «1 из последнего разряда она(«1) попадает в первый разряд, так как выход сдвигающего регистра 13 связан с его входом. Поэтому 13 работает циклично. Начало каждого цикла - это появление сигнала « в первой ячейке регистра 13. Конец каждого цикла - это сдвиг «1 из последнего разряда регистра 13 в первый разряд этого регистра. Начало последующего цикла совпадает по времени с концом предыдущего цикла.

Сдвиг «1 по ячейкам сдвигающего регистра 13 производится импульсами, поступающими на тактирующий (сдвигающий) вход сдвигающего регистра 13 с выхода генератора 9. Таким образом, на разрешающих входах элементов И 14-17 поочередно поступает разрешающая «1 и соответствующие коды АЦП и АЦП О через элемент ИЛИ 19 поступают на вход элемента ИЛИ 21. Одновременно «1 с выходов сдвигающего регистра 13 поступает на щнфра-. тор 22 номерй канала, тем самым на выходе шифратора 22 формируется код номера соответствующего канала. С выхода триггера последнего разряда сдвигающего ре1истра 13 сигнал «1 дает разрешение на прохождение кода через элемент И 18.., На другой вход элемента И 18 поступает снгнал с выхода кодера 11 адреса, этот сигнал содержит код номера канала, к которому подключен АЦП 10. Коды с выходов щифратора 22 и элемента И 18 поступают через : лемент ИЛИ 20 на вход элемента ИЛИ 2L Таким образом, на выходе элемента ИЛИ 21 появляется параллельный код, содержащий одновременно кодовое значение величины

измерйемого параметра, а также код номера канала, В котором находнтся параметр. Например, если имеется 22 разряда выхода элемента ИЛИ 21, то 18 первых разрядов используются для передачи величину параметра, а 4 оставшихся разряда - для передачи кода номера параметра.

В принятых обозначеннях на выходе блока согласования 12 циклично появляются коды (1 раз в цикл):

Xl(t ) + адрес i, (Ю)

где- последовательно равно 1,2,3,...; адрес 1- код номера канала.

5A(t) .-f адрес А,

где А Г это значение, измеренное

АЦП 10,

адрес А - код номера параметра, которому. это измеренное значение соответствует.

° Длительность каждого цикла определя..ется быстродействием АЦП (относительно низкое) и частотой, с которой можно производить смену кодов на входе вычислителя 23 (относительно высокая). Поэтому

5 частота, поступающая на тактирующий вход сдвигающего регистра 1 с выхода генератора 9 выбирается максимально возможной с учетом приведенных выше ограничений.,,

. Итак, на вход вычислителя 23 поступают сигналы согласно выражений (Ю). В вычислитель 23 эти сигналы поступают на вход блока 30 памяти оперативной (БОП). С выхода последнего разряда сдвигающего регистра 13 на вход счетчика цикла 31 в

5 конце каждого цикла поступает сигнал «1. В счетчике 31 цикла производится суммирование этих единиц, т.е. с выхода счетчика 31 цикла иа вход ВЬП 30 поступает код номера цикла.

БОП 30 разбит на зоны памяти, коли0 чество которых равно количеству каналов измерения плюс одна зона для калибратора, т.е. каждому каналу измерения соответствует определенная, навсегда за ним закрепленная зона БОП. Номер этой зоны

5 соответствует коду адреса, поступающему на вход БОП вместе с кодовым значением по каналу величины. Таким образом, измеренное значение записывается в определенную зону БОП 30, а очередность записи значений в эту зону (номер по порядку из0 мерения) определяется номером цикла, поступившим в БОП с выхода счегжка 31 цикла.

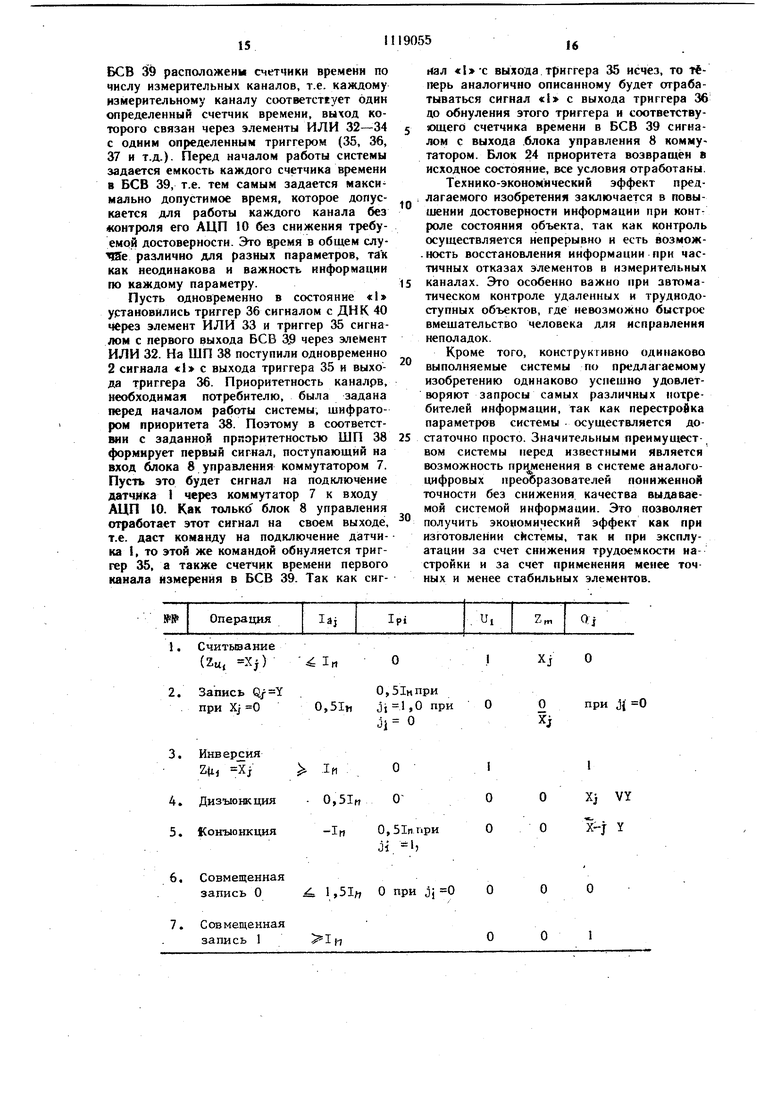

Значения, плученные с выхода АЦП 10, записываются. в свою зону вместе с соответствующими этим значениям , номер измерения соответствует номеру цикла, поступающему с выхода счетчика 31 Ш(кла на вход БОП 30. Базой для выполнения БОП 30 целесообразно принять МОП БИС К535РУ2- и К 535РУЗ .. Информация из блока БОП 30 при поступлении команд с дешифратора 28 поступает в АБ 26. АБ 26 выполняет 4 арифметических действия над числами, представленными параллельными кодами: сложение, вычитание, умножение и деление, и одну логическую операцию: сравнение (больше-меньшеравно). Комаидь на выполнение этих операций поступают в АБ 26 с выхоДа дешифратора 28 микрокоманд. Последовательность этих команд такова, что в АБ 26 производится решение двух основных задач: вычисление значения ( Х(1к) - At{tic)l по формуле (5) и сравнение полученной разности с величиной д i; корректировка получаемых значений X(t) по формуле (9). Коды чисел, иад которыми выполняются арифметические и одно, логическое действия, поступают в АБ 26 из БОП 30. Результаты решения двух основных задач из АБ 26 поступают в блок 25 буферной памяти и на вход блока 24 приоритета. Элементной базой для изготовления АБ 26 наиболее целесообразно принять МОП БИС К 536 ИК9. Возможно также изготовление АБ 26 и на другой элемент ной базе. В основу предлагаемой структуры АБ 26 положен принцип организации арифметического устройства иа едином однородном оборудовании иакопителя ОЗУ (оперативного запоминающего устройства). Ввиду высокой однородности и экономичности накопителя ОЗУ такое направление приводит к резкому сокращению аппаратурных затрат, уменьшению числа соединений, повышению технологичности вычислительных блоков. Поэтому структурное проектирование АБ 26 и БОП 30 должно производиться совместно. На фиг. 3 приведен фрагмент блока 30 памяти БОП, функционирующий совместно с АБ 26. На фиг. 3 представлена структура АБ 26 иа едином однородном оборудовании накопителя МОЗУ системы 2D, 2W с коэффициентом селекции КС 2. Здесь матричный накопитель 51 простейшей конструкции условно разбит на две части: хранящую часть накопителя (ХЧН) и функциональную часть иакопителя (ФЧН). Устройство содержит также дешифратор адреса (ДА) 52, блок настройки (БН) 53, усилители 54 воспроизведения (УВ) 54, регистр числа и формирователей записи (РЧ и ФЗ) 55, вентили 56- 58. Управление АБ 26 и вывод информации осуществляется через числовую магистраль ЧМ. 1 55 Адресные шины ХЧН обычным образом подключены к ДА 52 ХЧН используется как обычное ОЗУ для пассивного хранения п-разрядных чисел. Код адреса выбираемой ячейки поступает из числовой магистрали ЧМ. Адресные шины ФЧН подключены к БН 53. В БН 53 содержится К формирователей адресных токов lai:IaK Ток laj может изменять свое значение и полярность в зависимости от входных команд из числовой магистрали ЧМ. Особенность БН 53 состоит в том, что возможно возбуждение произвольного сочетания токов Ш: 1ак одиовременио. Именно этой особеииостью определяется возможность выполнения за одно обращение к накопителю 51 до К двухместных логических операций в ФЧН. Операции выполняются над словами Xi-Хк и общим п-разрядным аргументом У. Вектор У физически представлен разрядными токами записи 1р.-1рп из регистра числа и формирователей записи РЧ и ФЗ 55. Вектор Xj представлен состоянием намагниченности сердечников в ячейке ФЧН с . Результат логического преобразования может быть получен в виде вектора (q,j,ij;,.., %j), определяемого состоянием намагниченности сердечников в J-й ячейки ФЧН после выполненной операции, либо при чтении ячеек в виде п-разрядного вектора Z (2, Za,..., Zn), представленного иа разрядных шинах электродвижущими силами перемагничивания. Сигналы Z поступают иа вход УВ 54, которые формируют выходной сигнал вне зависимости от полярности входных сигналов. Поэтому Zt I при единицы//, а Z( О при /ei/ е /нуля/. Ув 54 срабатывает при Zi I лишь при условии Hi I (стробирующий сигнал в такте чтения). Выходы УВ 54 и входы РЧ и ФЗ 55 подсоединены через вентили 56- 58 к числовой магистрали ЧМ. Вентили 56 соединяют выходы УВ 54 с ЧМ в соответствии с номером разряда, а вентили 57 в соответствии со сдвигом на один разряд влево (i-й разряд ЧМ соединяют с (i-H)-M разрядом УВ 54. Выполняемые в ФНЧ операции представлены в таблице. Рассмотрение таблицы следует проводить с привлечением таблиц истинности реализуемых логических операций. В таблице In - ток полного перемагничивания по предельной петле гистерезиса. Таким образом, ФЧН следует рассматривать как поле многофункциональных, натраиваемых адресным током регистров. ногофункциональность обусловлена пороговыми с&ойствами сердечников. Операции 1,3 выполняются в такте счиывания, остальные опсряиии -- в такте аписи. Операции 1.2 .хярпкторны для обычого ОЗУ. ПриЕ еденмыо в тп6.чиг1е о(терации обеспечивают избыточный иабор логических и установочных операций.

В такте записи (2,4-7 операции) возможно одновременно выполнение в общем случае различных двухместных (X и У) операций в ФЧН при одновременной записи слова Y в ХЧН. Избыточный набор логических операций (сдвиг влево через вентиль 57) позволяет алгоритмически (реализуя последовательно во времени соответствующую микропрограмму) выполнить любую логическую или вычислительную операцию, в том числе и указанные операции, для которых и предназначено АБ 26.

Принцип работы многоканальной телеметрической системы заключается в следующем.

Как указано выще АБ 26 управляется микрокомандами, поступающими на АБ 26 с выхода дешифратора 28 микрокоманд. Эти микрокоманды обеспечивают выполнение операций «Сложение, «Вычитание, «Умножение, «Деление, «Сравнение, «Ввод числа в АБ, «Вывод числа из АБ, причем каждой операции соответствует определенный набор микрокоманд. Этот набор (или коды) микрокоманд определяется конкретным исполнением АБ 26.

Задав последовательность операций «Сложение, «Вычитание и т.д. для решения двух основных задач в АБ 26, тем самым задают и последовательность микрокоманд, т.е. в какой последовательности нужно формировать микрокоманды на входе АБ 26, связанном с выходом дешифратора 28 микрокоманд.

Формирование такой последовательности микрокоманд обеспечивается следующим образом. До начала работы системы коды микрокоманд записываются в БПП 27 так, что адреса последовательно расположенных команд отличаются на «1. С выхода генератора 9 на вход суммирующего счетчика 29 поступает частота, которая выбирает| я максимально возможной для принятой элементной базы. Выходы разрядных триггеров суммирующего счетчика 29 связаны с адресными входами БПП 27. Поэтому при заполнении частотой суммирующего счетчика 29 на выходе БПП 27 последовательно появляются коды требуемых для управления АБ 26 и БОП 30 микрокоманд, которые поступают на указанные блоки через дешифратор 28 микрокоманд.

Элементной базой для изготовления БПП 27 наиболее целесообразно принять БИС ПЗУ К535РЕ2.

Как указывалось выше, второй основной задачей, решаемой в АБ 26, является кор;чкт11ровка получаемых значений X(t) : о формуле (9). Данные для проведения угих корректировок поступают в АБ 26 из ГОП 30 из соответствуюши.х зон этого блока.

После проведения корректировки знамени. X(t) в соответствующей зоне, т.е. после загрузки этого значения из БОП 30 в АБ 26 для проведения корректировки, это значе5 ние X(t) в БОП 30 стирается. Аналогично стираются из своей зоны в блоке БОП значения АЦП 10, которые использовались для калибровки, и больще не потребуются для дальнейших вычислений.

Откорректированные в АБ 26 значения X(t) поступают из АБ 26 в буфер 25 и, в конечном счете, поступают потребителю информации.

Рассмотрим результаты решения первой основной задачи в АБ 26, т.е. вычисление

5 значения Xi (tx) - Ai (to) и сравнение полученной разности с величиной л 1(5). Эта операция производится в АБ 26 непрерывно по ере поступления новь1х значений X(t) на вход БОП 30 и оттуда - в АБ 26. Если соотношение (5) выполняется, то из АБ 26 на вход блока 24 приоритета сигнал не поступает. Если для како(;-либо канала соотношение (5) не выполняется, то из АБ 26 на вход буфера 24 поступает адрес номера канала, для которого соотношение (5)

5 перестало вы.юлняться . Это означает, что к датчику, расположенному в этом канале, нужно подключить АЦП 10 через коммутатор 7. Это требование реализуется следующим образом. Сигнал с АБ 26 поступает на расположенный в блоке 24 приоритета

ДНК 40 У ДНК 40 количество выходов равно количествуканалов измерения и каждому каналу измерения соответствует свой выход ДНК 40. Примем, что на вход ДНК поступил код номера второго канала измерения, в котором расположен датчик 2. На выходе ДНК 40, связанном с первым входом элемента ИЛИ 33, появляется сигнал srf. Этот сигнал проходит через элемент ИЛИ 33 на установочный вход триггера 36, устанавливая этот триггер в «I. Сигнал

0 с этого триггера 36 поступает на вход ШП 38. На втрром выходе ШП 38 также появляется сигнал «1, который поступает с выхода ШП 38, являющимся выходом блока 24 приоритета, на вход блока 8 управ5 ления коммутатором 7. Тем самым блок 8 управления дает сигнал коммутатору 7 на внеочередное подключение AU,n 10 через коммутатор 7 к выходу датчика 2.

Этот же сигнал с выхода блока 8 управления поступает на триггер 36 и обнуляет

0 его. Схема блока 24 приоритета возвращена в исходное состояние.

Возможен случай когда два триггера одновременно (или почти одновременно) устанавливаются в «1. Это возможно как

2 по подряд двум поступившим адресам номеров двух различных каналов из АУ 26 на ДНК 40 (может быть и больше), так и по сигналам, поступающим из БСВ 39. В БСВ 39 расположеин счетчики времеии по числу измерительных каналов, т.е. каждому измерительному каиалу соответстгует один определенный счетчик времени, выход которого связан через элементы ИЛИ с одним определенным триггером (35, 36, 37 и т.д.). Перед началом работы системы задается емкость каждого счетчика времени в БСВ 39, т.е. тем самым задается максимальио допустимое время, которое допускается для работы каждого канала без «оитроля его АЦП 10 без снижения требуемой достоверности. Это время в общем различно для разных параметров, так как неодинакова и важность информации по каждому параметру. Пусть одновременно в состояние «1 уртановились триггер 36 сигналом с ДНК 40 через элемент ИЛИ 33 и триггер 35 снгналом с первого выхода БСВ 35 через элемент ИЛИ 32. На ШП 38 поступили одновременно 2 сигнала «1 с выхода триггера 35 и выхода триггера 36. Приоритетность каналрв, необходимая потребителю, была задана перед началом работы системы, шифратором приоритета 38. Поэтому в соответствии с заданной приоритетностью ШП 38 формирует первый сигнал, поступающий на вход блока 8 управления коммутатором 7. Пусть это будет сигнал на подключение датчика 1 через коммутатор 7 к входу АЦП 10. Как толькб блок 8 управления отработает этот сигнал на своем выходе, т.е. даст команду на подключение датчика 1, то этой же командой обнуляется триггер 35, а также счетчик времени первого канала измерения в БСВ 39. Так как сиг1, Считьюание (Zuj Xj) 1« 2. Запись .0,51ипри . при Xj 00,51ц Ji,0 при 3. Инвер ия 2,(11 Xj 1и 0,51„ 04.Дизъюнкция -If, 0,51ппри 5.Конъюнкция 6.Совмещенная запись Оj4 ,51ц О при 7.Совмещенная запись и I О 1 о о Ji -Ь О нал выхода триггера 35 исчез, то теперь аналогично описанному будет отрабатываться сигнал «1 с выхода триггера 36 до обнуления этого триггера н соответствующего счетчика времени в БСВ 39 сигналом с выхода .блока управления 8 коммутатором. Блок 24 прнорнтета возвращён в исходное состояние, все условия отработаны. Технико-экономический эффект предлагаемого изобретения заключается в повыщенни достоверности информации при контроле состояния объекта, так как контроль осуществляется непрерывно и есть возможность восстановления информации-при частичных отказах элементов в измерительных каналах. Это особенно важно при эвтоматическом контроле удаленных и труднодоступных объектов, где невозможно быстрое вмешательство человека для исправления неполадок. Кроме того, конструктивно одинаково выполняемые системы по предлагаемому изобретению одинаково успешно удовлетворяют запросы самых различных потребителей информации, так как перестройка параметров системы осуществляется достаточно просто. Значительным преимуществом системы перед известнымн является возможность применения в системе аналогоцифровых преобразователей пониженной точности без снижения качества выа ваемой системой информации. Это позволяет получить экономический эффект как при изготовлении системы, так и при эксплуатации за счет снижения трудоемкости настройки и за счет применения менее точных и менее стабнльных элементов. XjО опри Ji 0 Xj 1 оXj VY оX-J Y 00

I С генератора 9

фиг. 2

L.,

W

J

(puiM

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Балакай В | |||

| Г., Крюк И | |||

| П | |||

| Интегральные схемы АЦП и ЦАП | |||

| М., «Энергия, 1978, с | |||

| Котел | 1921 |

|

SU246A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| США № 3357007, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1984-10-15—Публикация

1983-05-23—Подача