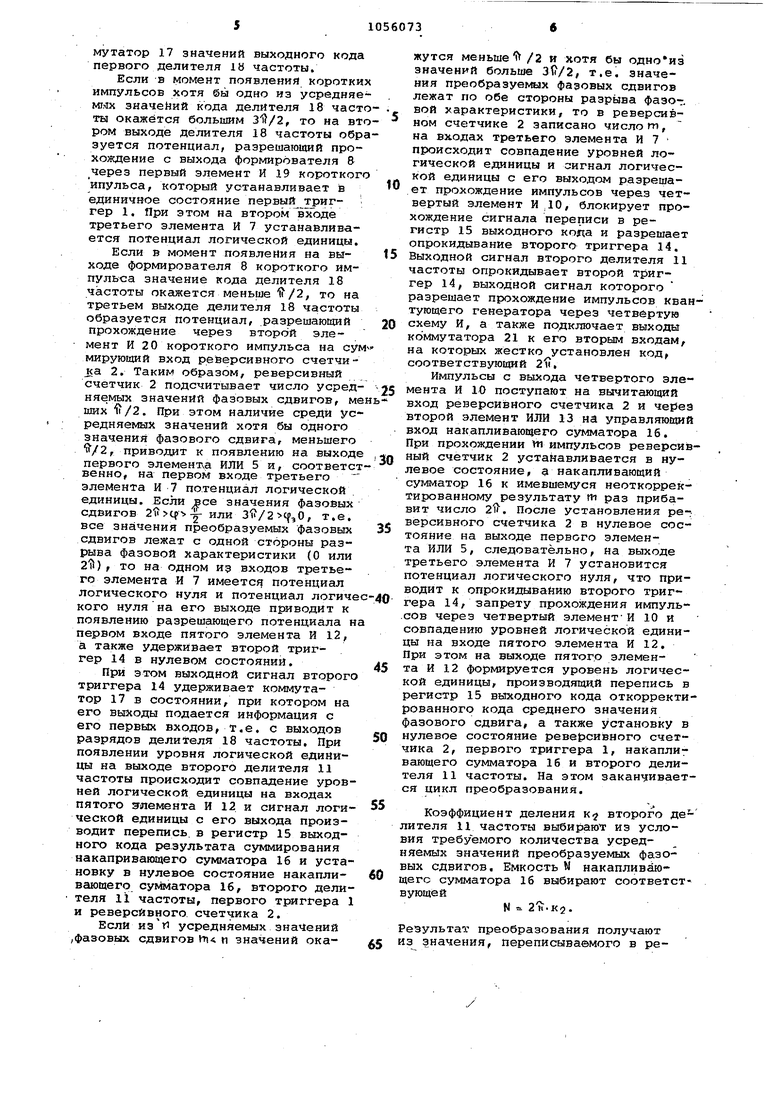

Изобретение относится к измерительной технике и может быть исполь зовано для измерения фазового сдвига непрерывных и радиоимпульсных квазисинусоидальных сигналов. Известен преобразователь фазовых сдвигов в цифровой код на основе триггерных схем и схем с элементами перекрытия (элементами совпадени с промежуточным преобразованием фазового сдвига во временной интервал и последующим времяимпульсным кодированием l . Недостатками триггерных преоб разователей и Преобразователей с элементами перекрытия являются нали чие мертвых зон и значительных погрешностей, обусловленных уходом нулевой линии усилителей-ограничите лей при формировании временного ин-г тервала, пропорционального фазовому сдвигу, а также погрешности из-за нелинейних искажений входных напряжений. Наиболее близким к изобретению по технической сущности является устройство по способу преобразовани фазового сдвига в цифровой код, содержащее регистр выходного кода, а также соединенные последовательно квантующий генератор, делитель част ты, однополюсный преобразователь частоты, перемножитель, фильтр, фор мирователь,, элементы совпадений, пр этом вторые входы однополюсного преобразователя частоты и перемножи теля соединены с соответствующими входами устройства, выходы разрядов делителя частоты соединены с сигнал ными входами элементов совпадений, выходы которых подключены к входам регистра выходного кода . Недостатком устройства являемся недостаточно высокая точность преоб разования фазового сдвига в цифровой код. Это объясняется тем, что содержащиеся во входных сигналах . шумы, а-также собственные аппаратур ные шумы преобразователя смещают моменты перехода входного сигнала формирователя через нулевое значение и приводят к значительным norpem ноетям преобразования. Цель изобретения - повышение точности П1 еобразования среднего значения фазового сдвига сигналов в цифровой код путем усреднения зна чений фазового сдвига к исключения погрешности от разрыва фазовой характеристики. Поставленная цел,ъ достигается те что в преобразователь фазового сдви та в цифровой код, содержащий регис выходного кода, а также соединенные последовательно квантующий генерато первый делитель частоты, однополюсный преобразователь частоты, перемн житель, фильтр, формирователь, элементы совпадения, при этом вторые входы перемножителя и однополюсного преобразователя частоты соединены с соответствующими входами устройства, а выход одного из элементов совпадения соединен с входом регистра выходного кода, введены первый и второй элементы ИЛИ, инвертор, первый и второй триггеры, реверсивный счетчик, второй делитель частоты, накапливающий сумматор и коммутатор, причем выход формирователя соединен с входом второго делителя частоты, первым входом второго элемента ИЛИ и первыми входами первого и второго &лемента И, вторые входы которых подключены соответственно к второму и третьему выходам первого делителя частоты, выход первого элемента И соединен с входом установки в i первого триггера, вход установки в О которого подключен к выходу пятого элемента И, к управляющему входу регистра выходного кода и к входам установки в О реверсивного счетчика, накапливающего сумматора и второго делителя частоты, выход второго элемента И соединен с суммирующим входом реверсивного счетчика, вычитающий вход которого подключен к выходу четвертого элемента И и к второму входу второго элемента ИЛИ, выход которого соединен с управляющим входом накапливающего сумматора, выходы разрядов реверсивного счетчика подключены к входам первого элемента ИЛИ, выход которого соединен с первьэл входом третьего элемента И и с входом установки в второго триггера, выход первого триггера подключен к второму входу третьего элемента И, выход которого соединен с первым входом четвертого элемента И, и через инвертор с первым входом пятого элемента И, выход квантующего генератора подключен к второму входу четвертого элемента И, третий вход которого соединен с выходом второго триггера и управляющим входом коммутатора, выход второго делителя частоты подключен к второму входу пятого элемента Кик счетному входу второго триггера, сигнальные входы регистра выходного кода соединены с выходами накапливающего сумматора, входы которого подключены к выходам коммутатора, первые входы коммутатора соединенЬ с выходами всех разрядов первого делителя частоты, а вторые входы - с входом установки кода числа 21. На чертеже приведена структурная схема предлагаемого преобразователя. Устройство содержит первый триггер 1, реверсивный счетчик 2, перемножитель 3, однополюсный преобразователь 4 частоты, первый эле- . мент ИЛИ 5, фильтр б,, третий элемент И 7, формирователь 8, инэертор 9, четвертый элемент И 10, второй делитель 11 частоты, пятый элемент И 12, второй элемент ИЛИ 13, второй триггер 14, регистр 15 выходного кода, накапливающий сумматор 16, коммутатор 17, первый делитель 18 частоты, первый элемент И 19, второй элемент И 29, квантующий генера- О тор 21, причем выход квантующего генератрг 21 соединен с вторым входом четвертого о элемента Икс входом делителя 18 частоты, выходы всех разрядов которого соедине- 15 ны с первыми входами коммутатора 17, а выход старшего разряда подключен к первому входу однополюсного преобразователя 4 частоты, второй вход которого соединен с первым входом 20 устройства, а выход - с первьм входом перемножителя 3, вход устройства соединен с вторым входом перемножителя 3, выход которого подключен к входу фильтра 6, выход 25 фильтра 6 соединен с входом формирователя 8, выход которого подключен к первому входу второго элемента ИЛИ 13, к первым входам первого и второго элементов 19 и 20 И и к ,« входу второго делителя 11 частоты, выход второго делителя 11 частоты соединен с вторым входом пятого элемента И 12 и счетным входом второго триггера 14, выход которого подключен X управляющему входу коммутатора 17 и третьему входу четвертого элемента И 10, второй и третий выхоы первого делителя 18 частоты соединены соответственно с вторьвли входами первого и второго элементов И 1940 и 20, выход первого элемента И 19 подключен к входу установки в i«« первого триггера I, выход которого соединен с вторым входом третьего элемента И 7/ выход второго элемен- 45 та И 20 подключен к суммирукяцему входу реверсивного счетчика 2, выходы разрядов которого соединены с входами первого элемента ИЛИ 5, выход первого элемента ИЛИ 5 подключен к JQ первому входу третьего элемента И 7, выход которого соединен с входом установки в О второго триггера 14 с первьял входом четвертого элемент та И 10 и через инвертор 9 с первым ее входом пятого элемента И 12, выход пятого элемента И 12 подключен к управляющему входу регистра 15 выходнО7 го кода и к входам установки в О реверсивного счетчика 2 первого триггера 1, накапливающего сумматора 16 ° и второго делителя 11 частоты, выход четвертого элемента И соединен с вычитаю1№м входом реверсивного счетчика 2 и вторым входом второго элеменяа ИЛИ 13, выход которого подключен 65

к входу суммирования накапливающего сумматора 16, сигнальные входы регистрй 15 выходного кода соединены с выходами накапливающего сумматора 16, входы которого подключены к выходам коммутатора 17, а вторые входы - с входом установки кода числа 2fi.

Устройство работает следующим образом.

На выходе старшего разряда первого делителя 18 частоты, заполняемого импульсами квантующего генератора 21, образуется меандр, напряжение первой гармоники которого можно записать в виде

COk ..

.Q

где 63(4 -.частота выходного сигнала

квантующего генератора; К коэффициент деления первбго

дели теля ч а сто ты.

Полученный меандр поступает на один вход однополюсного преобразователя 4 частоты, на другой вход которого подается входной сигнал устройства

1 (ntot.

На выходе однополюсного преобразователя 4 частоты Формируется сигнал суммарной частоты

Ui, U,SAnicAJ QH,

поступающий на один вход перемножителя 3, на другой вход которого подается второй входной сигнал устройства

(.)Из выходного сигнала перемножителя 3 с помощью фильтра 6 выделяется сигнал разностной частоты

Ug UfngSinlClivt).

Таким образом, выходное напряжение фильтра 6 сдвинуто по Фазе относительно первой гармоники выходного напряжения старшего разряда первого делителя 18 частоты на угол, равный преобразуемому фазовому сдвигу. Поэтому в момент равенства нулю фазы выходного сигнала фильтра 6 значение кода первого делителя 18 частоты соответствует преобразуемому фазовому сдвигу.

Формирователь 8 производит короткие импульсы в моменты перехода выходного сигнала фильтра 6 через нулевое значение, например, из области отрицательных значений в область положительных. Сформированные короткие импульсы проходят через второй элемент ИЛИ 13 на управляющий вход,на- капливающего сумматора 16, который при этом осуществляет суммирование поступающих на его входы через ком- мутатор 17 значений выходного кода первого делителя 1Ь частоты. Если в момент появления коротки импульсов хотя бы одно из усредняе мглх значейий кода делителя 18 част ты окажется большим 3iJ/2, то на вт ром выходе делителя 18 частоты обр зуется потенциал, разрешающий прохождение с выхода формирователя 8 через первый элемент И 19 коротког ипульса, который устанавливает is единичное состояние первый триг- гер 1. При этом на второмвходе третьего элемента И 7 устанавливается потенциал логической единицы. Если в момент появления на выходе формирователя 8 короткого импульса значение кода делителя 18 частоты окажется меньше t/2, то на третьем выходе делителя 18 частоты образуется потенциал, разрешающий прохождение через второй элемент И 20 короткого импульса на сум мирующий вход реверсивного счетчика 2. Таким образом, реверсивный счетчик 2 подсчитывает число усредняемых значений фазовых сдвигов, ме ших 11/2. При этом наличие среди усредняемых значений хотя бы одного значения фазового сдвига, меньшего ff/2, приводит к появлению на выходе первого элемент а ИЛИ 5 и, соответст венно, на первом входе третьего элемента И 7 потенциал логической . единицы. Если се значения фазовых сдвигов или , т.е. все значения преобразуемых фазовых сдвигов лежат с одной стороны разрыва фазовой характеристики (О или 21) , то на одном из входов третьего элемента И 7 имеется потенциал логического нуля и потенциал логиче кого нуляна его выходе приводит к появлению разрешающего потенциала н первом входе пятого элемента И 12, а также удерживает второй триггер 14 в нулевом СОСТОЯНИЙ. При этом выходной сигнал второго триггера 14 удерживает коммутатор 17 в состоянии, при котором на его выходы подается информация с его первых входов, т.е. с выходов разрядов делителя 18 частоты. При появлении уровня логической единицы на выходе второго делителя 11 частоты происходит совпадение уровней логической единицы на входах пятого элемента И 12 и сигнал логической единицы с его выхода производит перепись в регистр 15 выходного кода результата суммирования накапривакадего сумматора 16 и установку в нулевое состояние накапливеющего сумматора 16, второго делителя 11 частоты, первого триггера 1 и реверсивного счетчика 2. Если ИЗУ усредняемых значений (фазовых сдвигов п значений окажутся меньше f /2 и хотя бы одноиз значений больше , т.е. значения преобразуемых фазовых сдвигов лежат по обе стороны разрыва фазовой характеристики, то в реверсивном счетчике 2 записано число fn, на входах третьего элемента И 7 происходит совпадение уровней логической единицы и сигнал логической единицы с его выходом разрешает прохождение импульсов через четвертый элемент И, 10, блокирует прохождение сигнала переписи в регистр 15 выходного кода и разрешает опрокидывание второго триггера 14. Выходной сигнал второго делителя 11 частоты опрокидывает второй триггер 14, выходной сигнал которого разрешает прохождение импульсов квантующего генератора через четвёртую схему И, а также подключает выходы коммутатора 21 к его вторым входам, на которых жестко установлен код, соответствующий 21. Импульсы с выхода четвертого элемента И 10 поступают на вычитающий вход ре}зерсивиого счетчика 2 и через второй элемент ИЛИ 13 на управляющий вход накапливающего сумматора 16. При прохождении ш импульсов реверсивный счетчик 2 устанавливается в нулевое состояние, а накапливающий сумматор 16 к имевшемуся неоткорректированному результату tti раз прибавит число 21. После установления ре-, версивного счетчика 2 в нулевое состояние на выходе первого элемента ИЛИ 5, следовательно, на выходе третьего элемента И 7 установится потенциал логического нуля, что приводит к опрокидывайию второго триггера 14, запрету прохождения импуль.сов через четвертый элементИ 10 и совпадению уровней логической единицы на входе пятого элемента И 12. При этом на выходе пятого элемента И 12 формируется уровень логической единицы, производящий перепись в регистр 15 выходного кода откорректированного кода среднего значения фазового сдвига, а также установку в нулевое состояние ревеб)сивного счетчика 2, первого триггера 1, накапливающего сумматора 16 и второго делителя 11 частоты. На этом заканЧ:Ивается цикл преобразования. Коэффициент деления к второго делителя 11 частоты выбирают из условия требуемого количества усредняемых значений преобразуемых фазовых сдвигов. Емкость N накапливающегс сумматора 16 выбирают соответствующейN 2п.К2. Результат преобразования получают из значения, переписываемого в регистр 15 выходного кода, после переноса запятой влево на число разрядов, равное числу разрядов второго делителя 11 частоты, что эквивалентно делению результата суьфшрования значений фазовых, сдвигов на число к.

Эффективность описанной коррекции при усреднении значений фазовых сдвигов можно пояснить следующим примером. Пусть из десяти усредняемых значений фазовых сдвигов, имеющих некоторый 10 разброс вследствие влияния шумов,четыре окажутся равными , а шесть - . При этом неоткорректированиое среднее арифметическое значение равно 15 .

ч;, 144.2°.

10

Результат измерения предлагаемьом устройством равен

359 . б+ЗбО 620

г ЗбО,2,0,,

10

ак как емкость накалливакицего сумматсфа Н 360. к,, а к 10. В пред- 25 ложемном примере устройством устраняется составлякндая погрешности, рав

наяо я

fcil OVZ®- 144,2 «144°.

Таким образом, в устройстве в Р5 зультате усреднения к значений

преобразуемых фазовых сдвигов в Гку раз уменьшается случайная составляющая погрешности, обусловленная шумами , приводящими к разбросу значений усредняемых фазовых сдвигов, не пр ёвышающих . При этом благодаря предлагаемой коррекций результата преобразования устраняется погрешность преобразования, обусловленная

разрывностью фазовой характеристики Предлагаемое устройство не имеет зон неустойчивой работы (мертвых

зон), а также имеет высокое быстродействие, определяемое коэффициентом

.деления второго делителя 11 частоты. Благодаря использованию двойного преобразования частоты и фильтрации выходного сигнала перемножйтеля 3, имеющего фиксированное значение частоты, в преобразователе фазового сдвига в цифровой код исключена погрешность от нелинейных искажений. Преобразователь фазового сдвига в цифровой код может быть использован в радиолокации, радионавигации, дефектоскопии, при исследовании фазовых характеристик .четырехполюсников и в других областях.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1982 |

|

SU1075187A1 |

| Измеритель сдвига фаз (его варианты) | 1982 |

|

SU1040432A1 |

| Цифровой фазометр и его варианты | 1982 |

|

SU1020781A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099721C1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Цифровой компенсатор | 1972 |

|

SU439915A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Устройство для цифровой корреляционнойфильТРАции | 1978 |

|

SU799108A1 |

ПРРОБРАЗРВАТЕЛЬ ФАЗОВОГО СДВИГА В ЦИФРОВОЙ КОД, содержащий регистр выходного кода, а также соединенные последовательно квантующий генератор, первый делитель частоты, однополюсный преобразователь частоты, перемножитель, фильтр, формирователь, элементы совпадения при этом вторые входы перемножителя и однополюсного преобразователя частоты соединены с соответствующими входами устройства,-а выход одного из элементов совпадения соединен с входом регистра выходного кода, отличают и. йся тем, что, с целью повышения точности преобразования среднего значения фазового сдвига сигналов в цифровой код путем усреднения значений фазового сдвига и исключения погрешности от разрыва фазовой характеристики, в него введены первый и второй элементы ИЛИ, инвертор, первый и второй триггеры, реверсивный счетчик, второй делитель частоты, накапливающий cjT-iMaTop и коммутатор, рричем выход формирователя соединен с входом второго делителя частоты, первым зходом второго элемента ИЛИ и входами первого и второго эле-. ментов И, вторые входы которых подключены соответственно к второму и третьему выходам .первого делителя частоты, выход первого элемента И соединен с входом установки в i первого тригге;ра, вход установки в О t In I которого подключен к выходу пятого элемента И, к управляю1аему входу регистра выходного кода и к О входам установки в реверсивного счетчика, накапливающего сумматора и второго делителя частоты, выход второго элемента И соединен.с суммирующим входом реверсивного счетчика, вычитающий вход которого подключен к выходу четвертого элемента Ник второмувходу второгоэлемента ИЛИ, выход которого собда нен с управляющим входом накапливающего сумматора, выходы разрядов, реверсивного счетчика подключены к входам первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, и с входом второго триггера. установки в выход первого триггера подключен к второму входу третьего элемента И, ,выход которого соединен с первым входом четвертого элемента И, и через инвертор с первым входом пятого элемента И, выход квантующего генератора подключен к второму входу четвертого элемента И, третий вход которого соединен с выходом второго триггера и управляющим входом коммутатора, выход второго делителя частоты подключен к второму входу пртого элемента Ник счетному входу второго триггера,.сигнальные входы регистра выходного кода соединены с выходами накапливающего сумматора, входы К9ТОРОГО подключены к выходам коммутатора, первые входы коммутатора соединены с выходами всех ра рядов первого делителя частоты,, а вторые входы - с входом установки кода числа 2ii.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вишенчук И..М | |||

| и др | |||

| Электромеханические и электронные фазометры | |||

| М.-Л.,Госэнергоиздат, 1962 | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 779906, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-11-23—Публикация

1982-04-30—Подача