Изобретение относится к области вычислительной техники и предназначено для приема и преобразования цифрового дифференциального (разностного) сигнала

U = Ua - Ub (1)

любого трехуровневого самосинхронизирующегося последовательного двоичного кода (биполярного импульсного, манчестерского, кода NRZ при передаче информации избыточным кодом типа 4В/5В и т. п., [1]) в сложной помеховой обстановке при значительных величинах синфазной помехи в линии связи

Uc = (Ua + Ub)/2 (2)

в выходные цифровые сигналы транзисторно-транзисторной логики приема "1", "0" и "1" или "0" цифрового дифференциального сигнала с формированием импульсного и потенциального сигналов паузы с программируемым положением во времени относительно начала паузы.

Наличие в линии связи помехи Uc (2) искажает обе компоненты

Ua = Uc + U/2, (3)

Ub = Uc - U/2 (4)

дифференциального сигнала U (1) на входах устройства, которое характеризуется показателем помехоустойчивости

K = {M(Uc/U)}max, (5)

где Ua (3) и Ub (4) - соответственно первая и вторая компонента дифференциального сигнала U (1), измеряемая на входе устройства относительно общей шины (корпуса) устройства;

М(Х) - здесь и далее оператор выделения модуля величины X, заключенной в круглые скобки, т.е. в (5) величины Х = Uc/U;

{Y}max - здесь и далее оператор выделения максимального значения величины Y, содержащейся в фигурных скобках, т.е. в (5) величины Y = M(Uc/U);

/ - здесь и далее знак оператора арифметической операции деления.

Изобретение может использоваться, например, при построении устройств для ввода последовательной информации в самосинхронизирующемся последовательном двоичном коде RZ с возвратом к нулю по протоколам на основе ГОСТ 18977-79 и РТМ 1495-75, имеющих широкое применение в системах управления авиационной, судовой и прочей техники, расположенной, как правило, на подвижных объектах [2, с. 57-64], в частности при построении устройств для ввода информации типа [3].

Следует заметить, что при обмене информацией по проводным линиям связи (одноканальным или мультиплексным) именно передача дифференциальным сигналом U (1) может обеспечить наибольшую помехоустойчивость в современных цифровых системах передачи, обработки информации и управления [4, с.22-24].

Согласно ГОСТ 18977-79 (см., например, [2, с.57-64]) в коде RZ каждый бит информации передается дифференциальным сигналом U (1) в течение битового периода Т = Т1 + Т2 при Т1 = Т2 так, что в активной части Т1 = Т/2 периода Т битовой синхронизации на входах устройства

U = (10±3) В при приеме"1" кода RZ, (6)

U = -(10±3) В при приеме "0" кода RZ (7)

а в течение времени Т2 = Т/2 возврата к нулю или в течение паузы

Тп = (от 4 до 40)хТ (8)

определяется величиной

U = ±1B, (9)

где Т - период частоты следования импульсов битовой синхронизации передачи сообщения;

х - здесь и далее оператор арифметической операции умножения.

В реальных условиях передача информации в бортовой аппаратуре происходит в сложной помеховой обстановке при синфазной помехе Uc (2), могущей превышать полезный сигнал U (1) в несколько раз. Это обусловило создание специализированной микросборки АП. 004 Т53.430.006 ТУ для приема и декодирования "Кода последовательного 48 кГц" по двум каналам при высоком уровне синфазной помехи {M(Uc)}max = 15 В, т.е. при реальном показателе помехоустойчивости

Кр = 15/7>2. (10)

Однако устройство на основе микросборки АП.004 Т53.430.006 ТУ имеет низкое быстродействие (1/Т<61 кГц) и ограниченные функциональные возможности (отсутствует функция формирования сигналов паузы) и его использование, например, в устройстве [3] в качестве демодулятора требует включения в это устройство генератора одиночных импульсов для формирования импульсов битовой синхронизации и сложного специализированного счетчика для обнаружения середины четвертого периода Т в каждой паузе Тп (8).

В этой связи создание простого устройства для приема и преобразования цифрового дифференциального сигнала с формированием сигналов паузы и показателе помехоустойчивости (5), удовлетворяющем с запасом ограничению (10), представляет, на наш взгляд, актуальную техническую задачу, разрешение которой позволит повысить качество разрабатываемых устройств для ввода информации в бортовой аппаратуре.

Известно устройство для приема и преобразования цифрового дифференциального сигнала, являющегося первым преобразователем уровней устройства [5] и содержащем мультиплексор-демультиплексор с входными ограничительными резисторами и два детектора допусковых зон [6], каждый из которых выполнен на двух компараторах (микросхеме 521СА1 с двумя ограничительными резисторами) с объединенными по ИЛИ выходами, причем выход мультиплексора-демультиплексора соединен с пороговыми входами обоих детекторов допусковых зон, выход приема "1" кода соединен с выходом первого детектора допусковой зоны, инвертирующий вход которого соединен с неинвертирующим входом второго детектора допусковой зоны и с входом первой компоненты дифференциального сигнала, вход второй компоненты дифференциального сигнала соединен с неинвертирующим входом первого детектора допусковой зоны и инвертирующим входом второго детектора допусковой зоны, выход которого является выходом приема "0" кода.

В процессе функционирования устройства [5] первый детектор допусковой зоны вырабатывает единичный сигнал на выходе приема" 1" кода при величине сигнала Ua (или Ub), соответствующей (6) (или (7)), а второй детектор допусковой зоны вырабатывает единичный сигнал на выходе приема "0" кода при величине сигнала Ub (или Ua), соответствующей (7) (или (6)). Таким образом, в данном устройстве детектирование кода RZ производится непосредственно по сигналу Ua (3) (или Ub (4)), содержащего помеху Uc (2). Следовательно, устройство [5] работоспособно только при ограничении

M(U/2)>M(Uc), (11)

т.е. характеризуется показателем помехоустойчивости

Кп = {M(Uc/U)}max<0,5, (12)

в несколько раз меньшим по сравнению с значением (10), требуемым для бортовой аппаратуры.

Основным недостатком устройства [5] является низкая помехоустойчивость, что обусловлено организацией функционирования его детекторов допусковых зон только по одной из компонент дифференциального сигнала U(1).

Известно устройство для приема и преобразования биполярного манчестерского сигнала согласно ГОСТ 26765.52-87 (зарубежные стандарты MIL-STD-1533В и MIL-STD-1773), являющегося частью аналогового блока приема/передачи МК [7, с. 206, рис.5.1а], и содержащего усилитель-ограничитель с ограничительным резистором и резистором и двумя конденсаторами частотной коррекции ([7, с. 206, рис.5.1б], первый и второй компаратор, два элемента И, первые входы которых соединены с выходами первого и второго компараторов соответственно, входы источников отрицательного и положительного напряжений смещения, соединенные с неинвертирующим и инвертирующим входами первого и второго компараторов соответственно, вход биполярного манчестерского сигнала, связанный через усилитель-ограничитель соответственно с инвертирующим и неинвертирующим входами первого и второго компараторов, стробирующий вход разрешения приема, соединенный с вторыми входами элементов И, и цифровые выходы приема "0" и "1" манчестерского кода, являющиеся выходами первого и второго элементов И соответственно.

В процессе функционирования устройства [7] усилитель-ограничитель формирует на выходе биполярный манчестерский сигнал с уровнем в пределах ±0,75 В, по которому, при единичном стробирующем входном сигнале, первый (или второй) компаратор через первый (или второй) элемент И выдает единичный сигнал на выход приема "0" (или "1") манчестерского кода.

Основным недостатком устройства [7] является низкая помехоустойчивость, характеризуемая величиной (12) показателя (5), поскольку сигнальный вход усилителя-ограничителя недифференциальный.

Из известных технических решений наиболее близким по технической сущности к предлагаемому является устройство [8], содержащее два компаратора, триггер, элемент И, вход первой компоненты дифференциального сигнала кода RZ, соединенный с инвертирующим и неинвертирующим входами соответственно первого и второго компараторов, входы положительного и отрицательного напряжений смещения (порога), соединенные соответственно с неинвертирующим и инвертирующим входами первого и второго компараторов, выход последовательного двоичного кода, являющийся выходом триггера, инверсный выход приема "1" кода RZ, соединенный с выходом первого компаратора, асинхронным инверсным входом установки триггера и первым входом элемента И, инверсный выход приема "0" кода RZ, соединенный с выходом второго компаратора, асинхронным инверсным входом сброса второго триггера и вторым входом элемента И, и инверсный выход приема "1" или "0" кода RZ, являющийся выходом элемента И.

В процессе функционирования на вход устройства (согласно (2), (3), (6), (7) и (9)) поступает сигнал

Ua = Uс + (5 ± 1,5) в течение Т1 при приеме "1" кода RZ, (13)

Ua = Uс - (5 ± 1,5) в течение Т1 при приеме "0" кода RZ, (14)

Ua = Uс ± 0,5 В в течение Т2 или Тп, (15)

по которому, при выполнении ограничения (11), при поступлении на устройство [8] сигнала Ua (3) в течение Т1 при M{Ua)>Еc (где Еc и - Еc - величины положительного и отрицательного напряжений смещения на неинвертирующем и инвертирующем входах первого и второго компараторов соответственно) первый (или второй) компаратор вырабатывает инверсный сигнал NK1 = 0 (или NK2 = 0) приема "1" (или "0") при Ua (13) (или Ua (14)), по которому триггер устанавливается (или сбрасывается) и вырабатывает в течение каждого битового интервала Т единичный (или нулевой) сигнал D = 1 (или D = 0) последовательного двоичного кода принимаемой информации. Кроме того, элемент И вырабатывает инверсный сигнал NC = NK1 & NK2 (где & - знак логической операции И в языке ABEL) битовой синхронизации, по фронту которого последовательный код D может приниматься, например, в регистр сдвига устройства [3].

Из (11), (13) и (14) легко видеть, что устройство характеризуется низкой величиной показателя помехоустойчивости (12), т.е. это устройство практически нельзя использовать при построении бортовой аппаратуры.

Основным недостатком устройства [8] является ограниченность области использования, обусловленная низкой величиной (12) показателя помехоустойчивости и ограниченностью его функциональных возможностей, поскольку оно ориентировано для работы с одной компонентой Ua (2) сигнала U (1) и только кода RZ без формирования сигналов паузы.

Предлагаемым изобретением решается задача расширения области использования устройства путем повышения его помехоустойчивости и расширения его функциональных возможностей за счет обеспечения работы с цифровым трехуровневым дифференциальным сигналом любого самосинхронизирующегося кода с формированием импульсного и потенциального сигналов паузы с программируемым положением во времени относительно начала паузы.

Для достижения этого технического результата в устройство для приема и преобразования цифрового дифференциального сигнала, содержащее два компаратора, элемент И, вход первой компоненты цифрового дифференциального сигнала, вход отрицательного напряжения смещения, инверсные выходы приема "1" и "0" цифрового дифференциального сигнала, соединенные соответственно с выходами первого и второго компараторов и входами элемента И, и инверсный выход приема "0" или "1" цифрового дифференциального сигнала, являющийся выходом элемента И, введены вход второй компоненты цифрового дифференциального сигнала, счетчик, три элемента ИЛИ, элемент И-НЕ, два ограничителя и четыре делителя напряжений, вход начального сброса, тактовый вход, инверсные выходы импульсного и потенциального сигналов паузы и программируемый кодовый вход положения во времени импульсного и потенциального сигналов паузы относительно начала паузы, соединенный с информационным параллельным входом счетчика, выходы старших разрядов которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, выход элемента И соединен с асинхронным инверсным входом записи счетчика, асинхронный вход сброса которого соединен с входом начального сброса устройства, тактовый вход которого соединен с первым входом элемента И-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ и счетным вычитающим входом счетчика, выход младшего разряда которого соединен с вторым входом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с инверсным выходом импульсного сигнала паузы устройства, инверсный выход потенциального сигнала паузы которого соединен с выходом третьего элемента ИЛИ и вторым входом элемента И-НЕ, инвертирующий и неинвертирующий входы первого компаратора соединены соответственно с первым и вторым входами первого ограничителя напряжения и выходами первого и второго делителей напряжений, инвертирующий и неинвертирующий входы второго компаратора соединены соответственно с первым и вторым входами второго ограничителя напряжения и выходами третьего и четвертого делителей напряжений, первые входы первого и четвертого делителей напряжений соединены с входом первой компоненты цифрового дифференциального сигнала устройства, вход второй компоненты дифференциального сигнала соединен с первыми входами второго и третьего делителей напряжений, вход отрицательного напряжения смещения устройства соединен с вторыми входами первого и третьего делителей напряжений, вторые входы второго и четвертого делителей напряжений соединены с общей шиной устройства, при этом каждый ограничитель напряжения содержит два диода, первый вход, соединенный с анодом первого диода и катодом второго диода, и второй вход, соединенный с катодом первого диода и анодом второго диода, а каждый делитель напряжения содержит два резистора, первый вход, соединенный с первым выводом первого резистора, выход, соединенный с вторым выводом первого резистора и первым выводом второго резистора, и второй вход, соединенный с вторым выводом второго резистора.

Авторам не известны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение счетчика, трех элементов ИЛИ, элемента И-НЕ, двух ограничителей и четырех делителей напряжений, входа второй компоненты цифрового дифференциального сигнала, входа начального сброса, тактового входа, инверсных выходов импульсного и потенциального сигналов паузы и программируемого кодового входа положения во времени импульсного и потенциального сигналов паузы относительно начала паузы) предлагаемого устройства, которые позволяют (по сравнению с прототипом) расширить область его использования путем существенного повышения его помехоустойчивости и расширения его функциональных возможностей за счет работы с цифровым дифференциальным сигналом любого трехуровневого самосинхронизирующегося кода с формированием импульсного и потенциального сигналов паузы с программируемым положением относительно начала паузы.

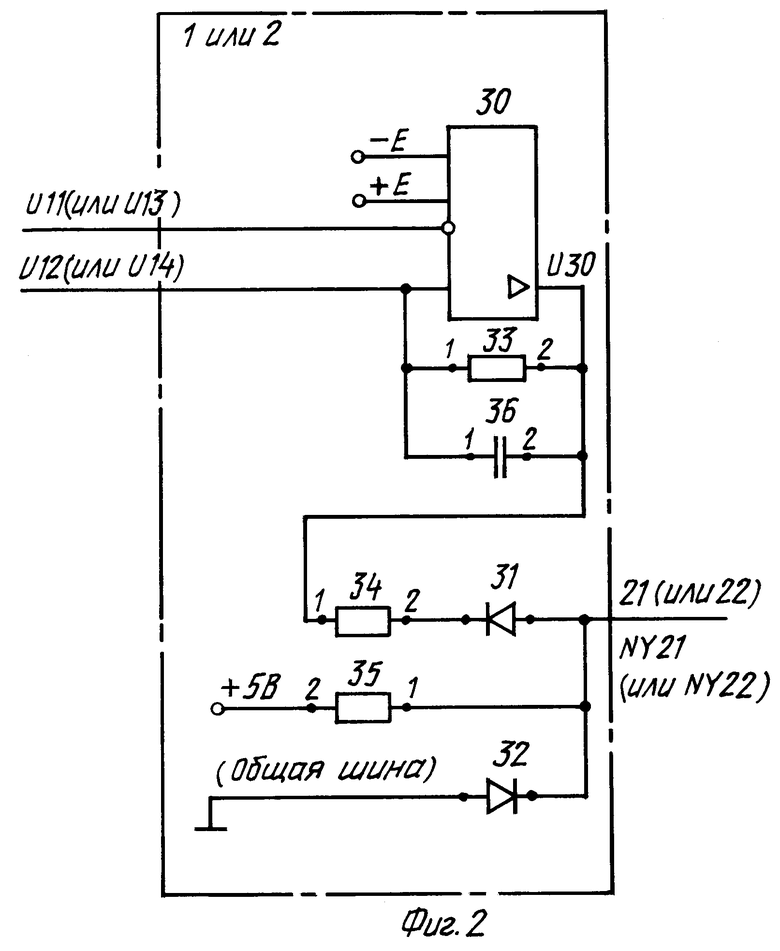

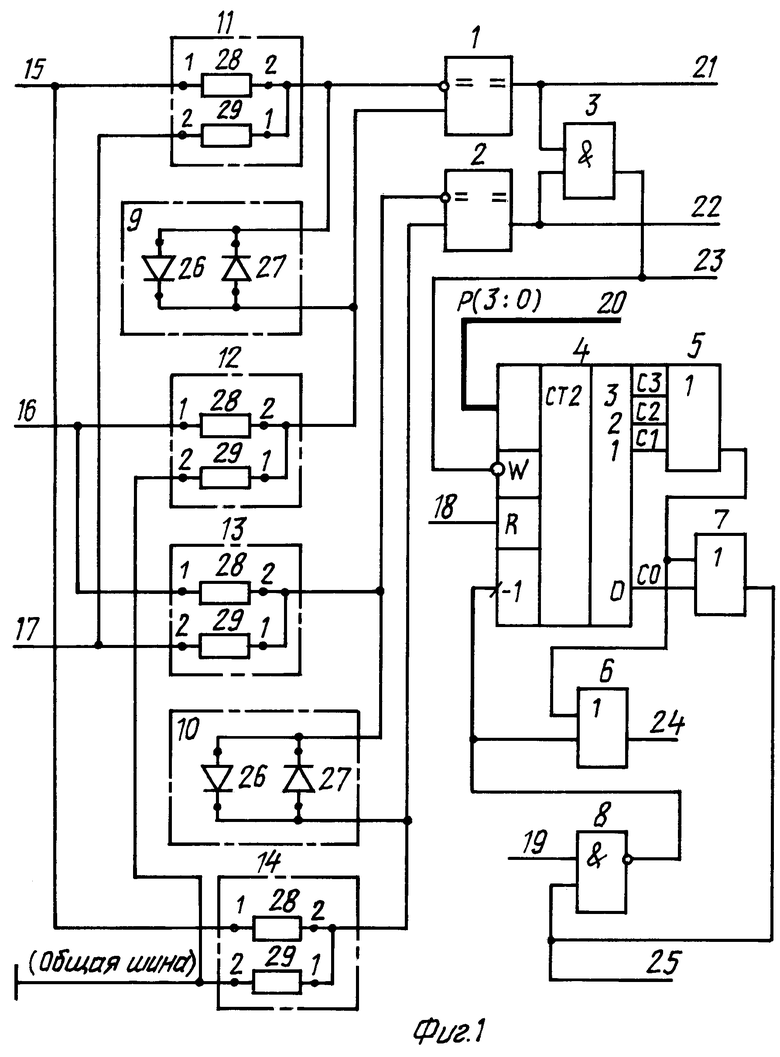

На фиг. 1 приведена функциональная схема устройства для приема и преобразования цифрового дифференциального сигнала с использованием библиотеки элементов интегральных схем (ИС) серии 1533, а на фиг. 2 - вариант реализации его первого (или второго) компаратора на основе операционного усилителя.

Устройство для приема и преобразования цифрового дифференциального сигнала (фиг. 1) содержит первый 1 и второй 2 компараторы, элемент 3 И, четырехразрядный счетчик 4, первый 5, второй 6 и третий 7 элементы ИЛИ, элемент 8 И-НЕ, первый 9 и второй 10 ограничители напряжений, первый 11, второй 12, третий 13 и четвертый 14 делители напряжений, входы 15 и 16 первой и второй компонент цифрового дифференциального сигнала соответственно, вход 17 отрицательного напряжения смещения, вход 18 начального сброса, тактовый вход 19, программируемый кодовый вход 20 положения во времени импульсного и потенциального сигналов паузы относительно начала паузы, инверсные выходы 21 и 22 приема "1" и "0" цифрового дифференциального сигнала, соединенные соответственно с выходами компараторов 1 и 2 и входами элемента 3, инверсный выход 23 приема "0" или " 1" цифрового дифференциального сигнала, соединенный с выходом элемента 3 и асинхронным инверсным входом записи счетчика 4, и инверсные выходы 24 и 25 импульсного и потенциального сигналов паузы, причем программируемый кодовый вход 20 соединен с информационным параллельным входом счетчика 4, выходы старших разрядов которого соединены с входами элемента 5, выход которого соединен с первыми входами элементов 6 и 7, вход 18 соединен с асинхронным входом сброса счетчика 5, вход 19 соединен с первым входом элемента 8, выход которого соединен с вторым входом элемента 6 и счетным вычитающим входом счетчика 5, выход младшего разряда которого соединен с вторым входом элемента 7, выход элемента 6 соединен с инверсным выходом 24, инверсный выход 25 соединен с выходом элемента 7 и вторым входом элемента 8, инвертирующий и неинвертирующий входы компаратора 1 соединены соответственно с первым и вторым входами ограничителя 9 и выходами делителей 11 и 12, инвертирующий и неинвертирующий входы компаратора 2 соединены соответственно с первым и вторым входами ограничителя 10 и выходами делителей 13 и 14, вход 15 соединен с первыми входами делителей 11 и 14, вход 16 соединен с первыми входами делителей 12 и 13, вход 17 соединен с вторыми входами делителей 11 и 13, вторые входы делителей 12 и 14 соединены с общей шиной устройства, каждый ограничитель 9 или 10 которого содержит два диода 26 и 27, первый вход, соединенный с анодом диода 26 и катодом диода 27, и второй вход, соединенный с катодом диода 26 и анодом диода 27, а каждый делитель 11-14 содержит два резистора 28 и 29, первый вход, соединенный с первым выводом резистора 28, выход, соединенный с вторым выводом резистора 28 и первым выводом резистора 29, и второй вход, соединенный с вторым выводом резистора 29.

Компаратор 1 (или 2) с делителем 12 (или 14) образует схему триггера Шмитта (см., например, в [9] рис.3.54 б на с. 215) и содержит выход 21 (или 22), операционный усилитель 30, два диода 31 и 32, три резистора 33 - 35, ускоряющий конденсатор 36, инвертирующий вход, являющийся инвертирующим входом усилителя 30, и неинвертирующий вход, соединенный с неинвертирующим входом усилителя 30 и первыми выводами резистора 33 и конденсатора 36, вторые выводы которых соединены с выходом усилителя 30 и первым выводом резистора 34, второй вывод которого соединен с катодом диода 31, анод которого соединен с выходом 21 (или 22), катодом диода 32 и первым выводом резистора 35, второй вывод которого соединен с шиной питания +5В устройства, общая шина которого соединена с анодом диода 32.

При условиях (6) - (10), напряжении смещения - Ec = U17 = -0,6В на входе 17 (фиг. 1) и питания - Е = -15В и Е = +15В усилителя 30 (фиг.2) составные части устройства (фиг.1 и 2) реализованы так, что: счетчик 4 выполнен на ИС 1533ИЕ7 - реверсивном четырехразрядном счетчике с асинхронным входом сброса и асинхронным инверсным входом загрузки кода с параллельного информационного входа и вычитающим (-1) и суммирующим (+1) счетными входами, обеспечивающих функционирование по фронтам действующих на них счетных импульсов, причем у счетчика 4 вход (+1) соединен с шиной ЛОГИЧЕСКОЙ 1 устройства (на фиг.1 это не показано); элементы 3,5-8 выполнены на комбинационных элементах соответствующих ИС серии 1533; усилители 30 компараторов 1 и 2 реализованы на двух операционных усилителях (ОУ) микросхемы 1401УД1 (содержит четыре ОУ); диоды 26, 27 и 31, 32 ограничителей 9 и 10 и компараторов 1 и 2 реализованы на одной диодной матрице 2ДС627А (содержит восемь диодов); в качестве резисторов 28 и 29 делителей 11-14 и резисторов 33-35 компараторов 1 и 2 использованы миниатюрные (безвыводные) резисторы типа Р1-12-0,25 с допуском 2% с номиналами R28 = 10 кОм, R29 = 2 кОм, R33 = 200 кОм, R34 = 4,7 кОм, R35 = 4,7 кОм; в качестве конденсатора 36 компаратора 1 (или 2) использован конденсатор типа К10-17а-М47-51пФ±20%.

Согласно, например, [10] каждый из четырех ОУ микросхемы 140УД1 имеет при Е = 15В, - Е = -15В полосу пропускания 2,5 МГц, модуль выходного напряжения M(U30) = 12,5В, максимальное напряжение синфазного сигнала U30c = 13В.

Описание функционирования устройства осуществляется с помощью системы положений и обозначений, определенных в следующих пяти пунктах.

1. Аналоговые сигналы на входах и выходах соответствующих составных частей устройства обозначим через Ui, где i - номер входа устройства или номер его составной части:

U11, U12, U13, U14, U15 = Ua, U16 = Ub, U17 = -Еc, U30.

При условии

[(R28хR29)/(R28+R29)]=R<<R33 (16)

и определении ширины петли гистерезиса триггера Шмитта величиной

Up = [(U30хR)/(R+R33)]х2 (17)

непосредственно по фиг. 1 и 2 в режиме малых напряжений между входами компараторов 1 и 2 (т.е. при отсутствии взаимовлияния напряжений на входе компаратора 1 (или 2) через ограничитель 9 (или 10)) методом наложения [11] получаем следующие расчетные выражения напряжений U11-U14

U11 = [(UaхR29)/(R28+R29)] - [(ЕcхR28)/(R28+R29)], (18)

U12 = [(UbхR29)/(R28+R29)] + Up/2, (19)

U13 = [(UbхR29)/(R28+R29)] - [(ЕcхR28)/(R28+R29)], (20)

U14 = [(UaхR29)/(R28+R29)] + Up/2. (21)

На основе выражений (18)-(21) определяем следующие результирующие выражения для расчета дифференциальных U1d = U11-U12 и U2d = U13-U14 и синфазных Ujc = U1c = U2c = [(U11+U12)/2] = [(U13+U14)/2] напряжений на входах компараторов 1 и 2

U1d = [(UхR29)/(R28+R29)] - [(ЕcхR28)/(R28+R29)]-Up/2, (22)

U2d = [(-UхR29)/(R28+R29)] -[(ЕcхR28)/(R28+R29)]-Up/2, (23)

Ujc = [(UcхR29)/(R28+R29)] - [(ЕcхR28)/(R28+R29)]/2+Up/4, (24)

где U и Uc - определены выражениями (1) и (2) соответственно.

Обозначив допустимое значение модуля синфазного напряжения на входах усилителя 30 через U30c (для каждого ОУ микросхемы 140УД1 синфазного напряжения U30c = Е - 2В = 13В) при ограничении

U30c > Ujc (25)

определяем максимальное значение синфазной помехи Uc (2)

M{Uc}max = [U30cх(R28+R29)]/R29 (26)

и оценку показателя (5) устройства согласно выражению

Ку = {[U30cх(R28+R29)]/R29}/{M(U)}min, (27)

где {M(U)}min - минимальное значение модуля дифференциального сигнала U (1).

Выражения (22) и (23) справедливы при напряжениях U1d и U2d небольших по модулю, не превышающих примерно 0,5В, а при больших напряжениях M(Ua - Ub) напряжения U1d и U2d ограничиваются соответственно ограничителями 9 и 10 по модулю до величины примерно 1В.

2. Обозначим цифровые сигналы на входах 18 и 19 через X18 и X19, а на инверсных выходах 21, 22, 23, 24, 25 соответственно через NY21, NY22, NY23, NY24, NY25. Кроме того, код на программируемом кодовом входе 20 временного положения импульсного NY24 и потенциального NY25 сигналов паузы относительно начала паузы обозначим через Р(3:0) = Р3 Р2 Р1 Р0, на выходе счетчика 4 - через С(3:0) = С3 С2 С1 С0, где Р0 и С0 младшие, а Р3 и С3 старшие разрядные цифры (т.е. 0 или 1) этих кодов.

3. Используется модифицированный язык описания логических функций ABEL, в котором логические операторы И, ИЛИ и НЕ имеют обозначения "&", "#" и "!" соответственно. Например, элемент 8 формирует инверсную переменную NY8 = !Y8 (т.е. знак N в левой части эквивалентен знаку ! в правой части) по формуле

NY8 = !(X19 & NY25). (28)

4. В процессе функционирования в установившемся режиме при отрицательном или положительном напряжении U1d (или U2d) компаратор 1 (или 2) вырабатывает соответственно цифровой сигнал NY21 = 1 или NY21 = 0 (или NY22 = 1 или NY22 = 0); в динамике компаратор 1 (или 2) при изменении напряжения U1d (или U2d) < 0В на напряжение U1d (или U2d) > 0В переключает сигнал NY21 (или NY22) из "1" в "0" с форсированным изменением U1d (или U2d) на положительную величину Up (17), а при изменении напряжения U1d (или U2d) > 0В на напряжение U1d (или U2d) < 0В переключает сигнал NY21 (или NY22) из "0" в "1" с форсированным изменением U1d (или U2d) на отрицательную величину Up (17) ширины петли гистерезиса триггера Шмитта.

Из фиг. 2 видно что компаратором 1 (или 2) цифровой сигнал NY21 (или NY22) формируется из напряжения U30 (в установившемся режиме M(U30) = 12,5В) с помощью напряжения +5В двухсторонним диодным ограничителем, образованным диодами 31 и 32 и резисторами 34 и 35.

5. Под фронтом или спадом любого цифрового сигнала (прямого или инверсного) понимается смена логического значения этого сигнала из "1" в "0" или из "0" в "1" соответственно.

На основании изложенного выше опишем формирование в устройстве его выходных инверсных сигналов NY21, NY22, NY23, NY24, NY25 в процессе поступления на устройство трехуровневого цифрового сигнала U (1), например, кода RZ, описанного во времени множеством

{U(6),U(7),(U9)}. (29)

В процессе функционирования на устройство поступает цифровой дифференциальный сигнал U(1) = Ua - Ub = U15 - U16, установившийся уровень которого принадлежит множеству (29). По каждому уровню сигнала U (1) компараторы 1 и 2 вырабатывают выходные сигнала NY21 и NY22 согласно следующим соотношениям

При U (1) = U (6) NY21 = 0, NY22 = 1, (30)

При U (1) = U (7) NY21 = 1, NY22 = 0, (31)

При U (1) = U (9) NY21 = 1, NY22 = 1 (33)

элемент 3 (фиг.1) формирует выходной сигнал NY23 по формуле

NY23 = NY21 & NY22, (34)

а по сигналу X18 начального сброса, тактовым импульсам X19, программируемому коду Р(3:0) и инверсным импульсам NY23 (34) вырабатываются сигналы NY24 и NY25

NY24 = С3 # С2 # С1 # [!(Х19 & С0)], (35)

NY25 = С3 # С2 # С1 # С0, (36)

так, что при NY25 = 0 устройство находится в состоянии паузы, а при NY25 = 1 в режиме приема и преобразования, который заканчивается формированием импульса NY24 = 0, по окончании которого устройство переходит в состояние паузы. Из фиг.1 и (35) следует, что инверсный импульс NY24 вырабатывается по тактовому импульсу X19 при нахождении счетчика 4 в состоянии С(3:0) = (0001), а инверсный сигнал NY25 = 0 вырабатывается при нахождении счетчика 4 в состоянии С(3: 0) = (0000), в котором счетчик 4 может быть зафиксирован сигналом X18 = 1 начального сброса. При X18 = 0 счетчик 4 по коду Р(3:0) на входе 20 и инверсным импульсам NY8(28) и NY23(34) функционирует следующим образом. Каждым импульсом NY23 = 0 счетчик 4 фиксируется в состоянии С(3:0) = Р(3:0), которое определяет числовой порог

Р = Р0 + (2хР1) + (4хР2) + (8хР3) (37)

формирования сигналов NY24 и NY25 во времени относительно начала паузы.

При наступлении паузы формирование импульсов NY23 (34) прекращается и элемент 8 формирует ровно Р (37) импульсов NY8 (28) (отсчитываются от последнего сигнала NY23 = 0), по фронту каждого из которых содержимое счетчика 4 уменьшается на единицу, а по импульсу Р последовательности импульсов NY8 (28) формируется инверсный импульсный сигнал NY24 (35) паузы, по окончании которого счетчик 4 переходит в состояние С(3:0) = (0000) и вырабатывается инверсный потенциальный сигнал NY25 = 0 паузы, который блокирует работу элемента 8. В состоянии паузы устройство остается до формирования инверсного сигнала NY23 = 0, который формируется с поступлением на входы 15 и 16 цифрового дифференциального сигнала сообщения, описанного, например, для кода RZ множеством (29) с периодом Т передачи сообщения. В этой связи задержки Т24 и Т25 формирования соответственно сигналов NY24 и NY25 относительно начала паузы можно оценить выражениями

Т24 = Рх(1/f19) = Рх(Т/к), (38)

Т25 = (Р + 0,5)((1/f19)=(Р + 0,5)((T/k), (39)

где k - коэффициент пропорциональности больший единицы;

1/Т - частота передачи сообщения дифференциальным сигналом U(1);

f19 = k/T - частота следования тактовых импульсов X19 на входе 19.

На основании формулы (27) оценим показатель помехоустойчивости устройства при максимальном синфазном сигнале U30c = Е - 2В = 13В операционного усилителя 30, R28 = 10 кОм, R29 = 2 кОм, {M(U)}min = 7В

Ку = {[13х(10+2)]/2}/7>11. (40)

Сравнивая (35) с (12), получаем

Ку/Кп>22. (41)

Из (41) и (40) получаем, что предлагаемое устройство имеет во много раз более высокую помехоустойчивость по сравнению с прототипом [8] и с большим запасом удовлетворяет ограничению (10).

Таким образом, по сравнению с прототипом [8] предлагаемое устройство, благодаря его существенным признакам, имеет более широкую область использования путем значительного повышения помехоустойчивости с удовлетворением ограничению (10) с большим запасом за счет работы с трехуровневым цифровым дифференциальным сигналом, например, кода RZ, описанного множеством (29), с формированием импульсного NY24 (35) и NY25 (36) потенциального сигналов паузы с программируемым положением во времени относительно начала паузы согласно задержками Т24 (38) и Т25 (39).

Использование данного устройства при построении устройства типа [3] или [5] позволит как упростить, так и повысить их помехоустойчивость за счет удовлетворения ограничению (10) с большим запасом. В частности, при построении устройства типа [3] с использованием, например, интегральных микросхем (ИС) серии 1533 оно будет содержать данное устройство, RS триггер с инверсными входами установки и сброса для формирования последовательного двоичного кода D принимаемой информации по инверсным сигналам NY21 и NY22 (как в прототипе [8] ), 33-разрядный регистр сдвига (D триггер в качестве старшего разряда - 0,5 ИС ТМ2 с асинхронными инверсными входами установки и четыре ИС ИР8 - четыре байтовых регистра сдвига с асинхронным инверсным сбросом, последовательным вводом и параллельным выводом) с установкой в начальное состояние (10. . . 0) по сигналу NY25 = 0 и сдвигом (при NY25 = 1) вправо последовательного кода D по фронтам импульсов NY23 и дешифратор 8-разрядной адресной группы выходов регистра сдвига, выход младшего разряда которого соединен с стробирующим входом дешифратора. В этом устройстве [3] при k = 16 и Р = 12 после окончания каждой последовательности из 32 сдвиговых импульсов NY23 регистр сдвига заполняется и выставляет через дешифратор адресный сигнал готовности информации, которая снимается с информационной группы выходов регистра соответствующим приемником в течение времени (Тх3). После этого вырабатывается сигнал NY25 = 0, по которому регистр сдвига фиксируется в исходном состоянии (10. . . 0) до поступления на него очередной последовательности 32 сдвиговых импульсов NY23.

Литература

1. "2.2. Методы передачи дискретных данных на физическом уровне" - с. 132-144 в книге: Компьютерные сети. Принципы, технологии, протоколы / В.Г. Олифер, Н.А. Олифер - СПб.: Питер, 2001. - 672 с.: ил.

2. Хвощ С.Т. и др. Организация последовательных мультиплексных каналов систем автоматического управления. С.Т. Хвощ, В.В. Дорошенко, В.В. Горовой. Под общ. ред. С.Т. Хвоща. - Машиностроение. Ленингр. отд-ние, 1989. - 271 с. , ил.

3. А.с. 1068927, М. кл. G 06 F 3/04, СССР. Устройство для ввода информации. Л.П. Горохов, Р.Ю. Хальфан и В.А. Генина. Опубл. 23.01.1984. Бюл. 3.

4. "Линии передачи сигналов" - с. 22-24 в книге: Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ - Петербург, 2001. - 528 с.: ил.

5. А.с. 1786491, М. кл. G 06 F 13/00, СССР. Устройство для ввода информации. Д.Ю. Гусев и Ю.В. Крюков. Опубл. 07.01.1993. Бюл. 1.

6. "Детектор допусковой зоны для сигнала Uc" - с.229, рис.5.8д в книге: Шило В. Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. 2-е изд., перераб. и доп. М: Сов. радио, 1979. - 368 с., ил.

7. "Аналоговый блок приема/передачи МК" - с.206, рис.5.1а, рис.5.16 в книге: Хвощ С.Т. и др. Организация последовательных мультиплексных каналов систем автоматического управления. С.Т. Хвощ, В.В. Дорошенко, В.В. Горовой. Под общ.ред. С.Т. Хвоща. - Машиностроение. Ленингр. отд-ние, 1989. - 271 с., ил.

8. Прототип. "Пример схемы дешифрации кода RZ" - с.102, рис. 2.25 в книге: Ю. В. Новиков, Д.Г. Карпенко. Аппаратура локальных сетей: функции, выбор, разработка. Под общей редакцией Ю.В. Новикова. - М., Издательство ЭКОМ, 1998. - 288 с., ил.

9. Хоровиц П., Хилл У. Искусство схемотехники: в 2-х томах. Т1. Пер. с англ. - изд. 3-е, стереотип. М.: Мир, 1986. - 598 с., ил.

10. "5.2.7. Многоканальные операционные усилители" - с.356-360 в книге: Цифровые и аналоговые интегральные микросхемы: Справочник/ С.В. Якубовский, Л. И. Ниссельсон, В. И. Кулешова и др.; Под. ред. С.В. Якубовского. - М.: Радио и связь, 1989. - 496 с: ил.

11. "Принцип наложения и метод наложения" - с.44-45 в книге: Бессонов Л. А. Теоретические основы электротехники (электрические цепи). - Издание девятое переработанное и дополненное. - М.: Высшая школа, 1996. - 638 с: ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2003 |

|

RU2257005C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2000 |

|

RU2190927C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

Устройство для приема и преобразования цифрового дифференциального сигнала относится к области вычислительной техники и предназначено для приема и преобразования цифрового дифференциального сигнала. Техническим результатом является расширение области использования устройства путем повышения его помехоустойчивости и расширение его функциональных возможностей за счет обеспечения работы с цифровым дифференциальным трехуровневым сигналом любого самосинхронизирующегося кода с формированием импульсного и потенциального сигналов паузы с программируемым положением во времени относительно начала паузы. Для этого устройство содержит компараторы, элемент И, счетчик, элементы ИЛИ, элемент И-НЕ, ограничители и делители напряжений. 2 ил.

Устройство для приема и преобразования цифрового дифференциального сигнала, содержащее два компаратора, элемент И, вход первой компоненты цифрового дифференциального сигнала, вход отрицательного напряжения смещения, инверсные выходы приема "1" и "0" цифрового дифференциального сигнала, соединенные соответственно с выходами первого и второго компараторов и входами элемента И, и инверсный выход приема "1" или "0" цифрового дифференциального сигнала, являющийся выходом элемента И, отличающееся тем, что оно дополнительно содержит вход второй компоненты цифрового дифференциального сигнала, счетчик, три элемента ИЛИ, элемент И-НЕ, два ограничителя и четыре делителя напряжений, вход начального сброса, тактовый вход, инверсные выходы импульсного и потенциального сигналов паузы и программируемый кодовый вход положения во времени импульсного и потенциального сигналов паузы относительно начала паузы, соединенный с информационным параллельным входом счетчика, выходы старших разрядов которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, выход элемента И соединен с асинхронным инверсным входом записи счетчика, асинхронный вход сброса которого соединен с входом начального сброса устройства, тактовый вход которого соединен с первым входом элемента И-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ и счетным вычитающим входом счетчика, выход младшего разряда которого соединен с вторым входом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с инверсным выходом импульсного сигнала паузы устройства, выход третьего элемента ИЛИ соединен с вторым входом элемента И-НЕ и инверсным выходом потенциального сигнала паузы устройства, инвертирующий и неинвертирующий входы первого компаратора соответственно соединены с первым и вторым входами первого ограничителя напряжения и выходами первого и второго делителей напряжений, инвертирующий и неинвертирующий входы второго компаратора соответственно соединены с первым и вторым входами второго ограничителя напряжения и выходами третьего и четвертого делителей напряжений, вход первой компоненты цифрового дифференциального сигнала соединен с первыми входами первого и четвертого делителей напряжений, вход второй компоненты цифрового дифференциального сигнала соединен с первыми входами второго и третьего делителей напряжений, вход отрицательного напряжения смещения соединен с вторыми входами первого и третьего делителей напряжений, вторые входы второго и четвертого делителей напряжений соединены с общей шиной устройства.

| 0 |

|

SU159993A1 | |

| НОВИКОВ Ю.В., КАРПЕНКО Д.Г | |||

| Аппаратура локальных сетей: функции, выбор, разработка | |||

| - М.: ЭКОМ, 1998, с.102, рис.2.25 | |||

| Преобразователь биполярного кода в однополярный | 1988 |

|

SU1552378A1 |

| RU 94037470 A1, 10.09.1996 | |||

| ФОРМИРОВАТЕЛЬ БИПОЛЯРНЫХ ИМПУЛЬСОВ | 1988 |

|

SU1515993A2 |

| US 4758821 A, 19.06.1998. | |||

Авторы

Даты

2003-04-27—Публикация

2001-05-22—Подача