срабатывание его при появлении сдвоенных импульсов Импульс, образованный сумматором 9 по отриц. фронту первого импульса ВПИС, проходит через ЭЗ 5 на счетный вход триггера 1, переводя его в противоположное состояние. Далее импульсы выходной последовательности формируются с помощью сигналов с интеграторов 6, 7.

1

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной инфорг а- ции с использованием сигналов с расщепленной фазой для тактовой синхро- низации.

Целью изобретения является увеличение помехоустойчивости.

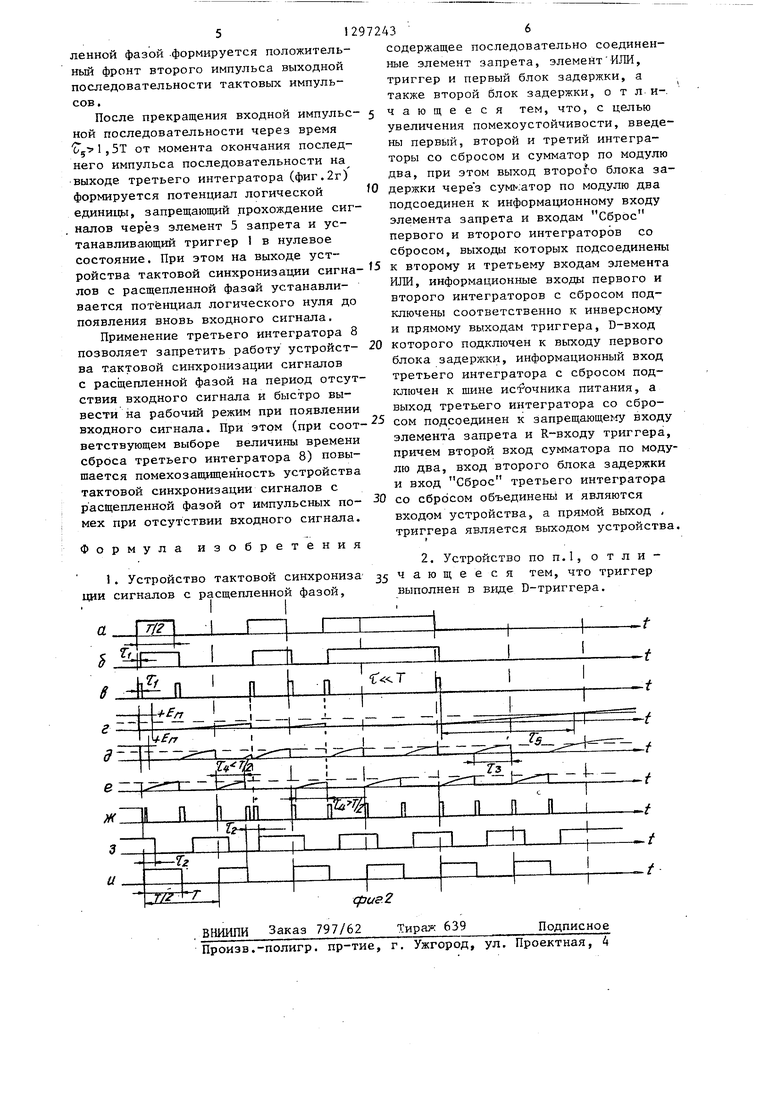

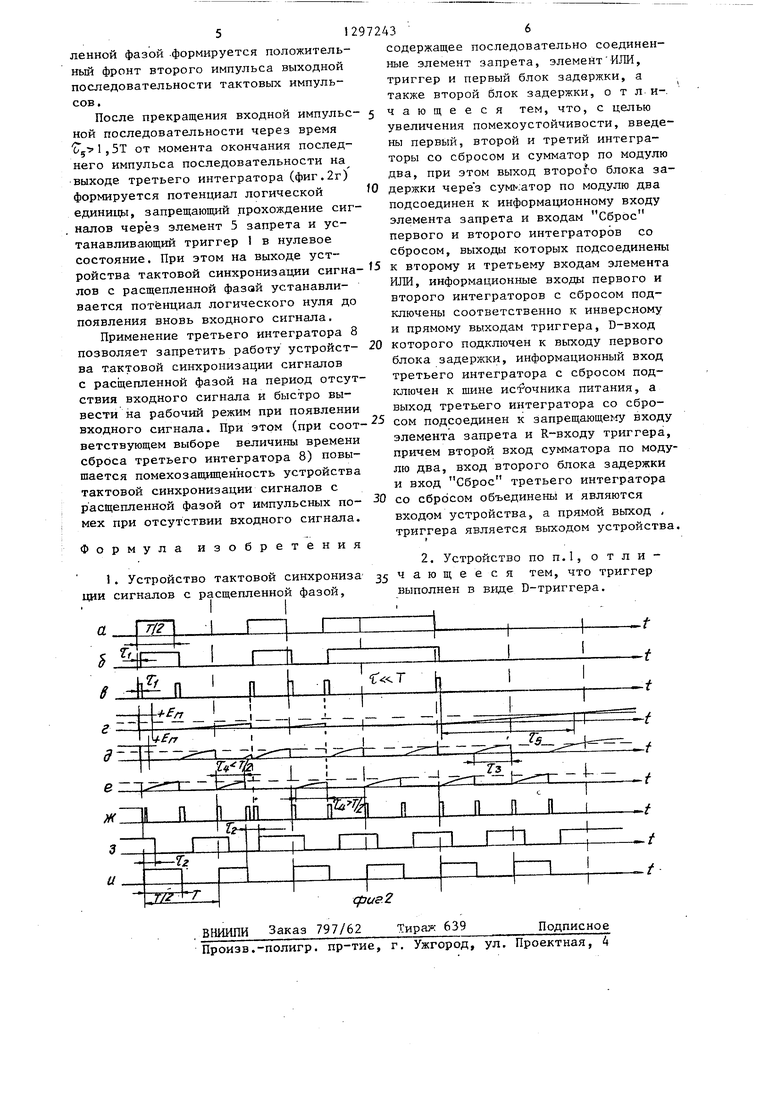

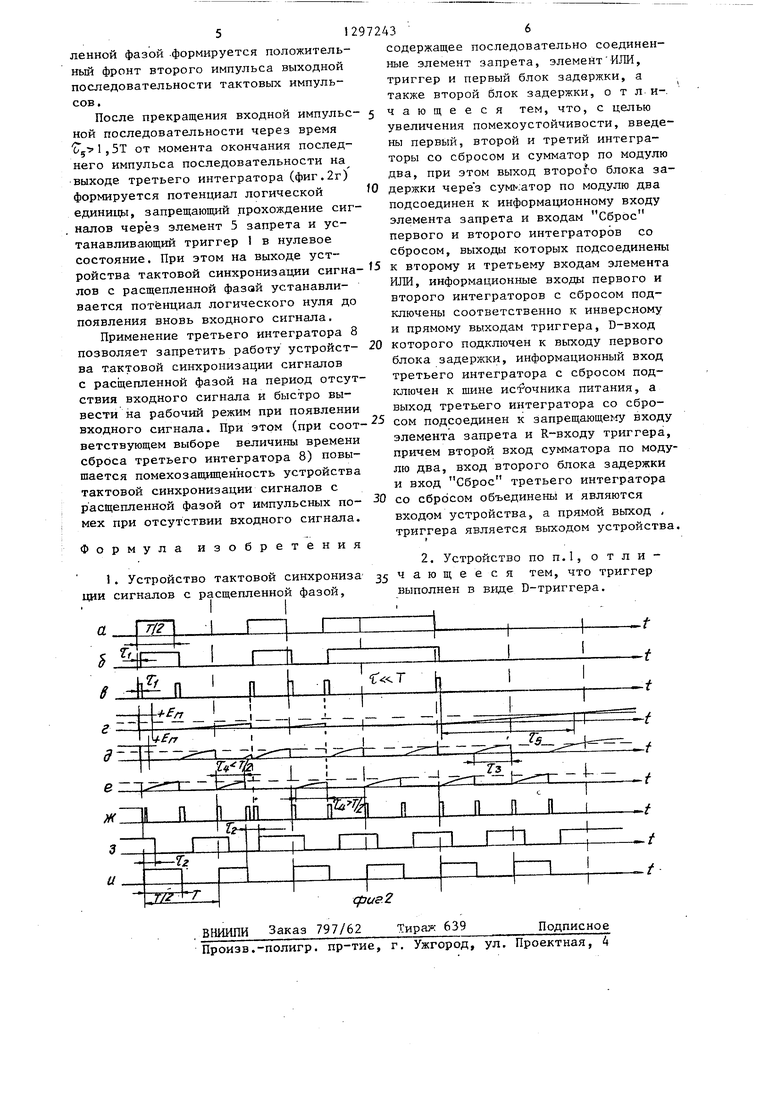

На фиг.1 представлена структурная электрическая схема устройства тактовой синхронизации сигналов с расщепленной фазой; на фиг.2 - временные диаграммы сигналов, поясняющие рабо

ту устройства тактовой синхронизации

сигналов с расщепленной фазой.

Устройство тактовой синхронизации сигналов с расщепленной фазой содержит триггер 1, элемент ИЛИ 2, первый 3 и второй 4 блоки задержки, элемент запрета 5, первый, второй и третий интеграторы 6-8 со сбросом, сумматор 9 по модулю два.

Первый, второй и третий интеграторы 6-8 со сбросом содержат ключ 10 диод 11, резистор I2 и конденсатор 13.

Устройство тактовой синхронизации сигналов с расщепленной фазой работает следующим образом.

В исходном состоянии при отсутствии сигнала на входе устройства тактовой синхронизации сигналов с расщепленной фазой (фиг.2а) оно находится в ждущем режиме. Потенциал логи- ческого нуля с прямого выхода (фиг.2и) триг1 ера 1, выполненного в виде D-триггера, находящегося в нулевом состоянии, подан на информационный - вход второго интегратора 7 (фиг.1). Ключ 10 второго интегратора 7 закрыт потенциалом логического

Через время, большее 1,5 Т, после окончания последнего импульса ВПИС интегратор 8 формирует потенциал i, который запрещает прохождение сигналов через ЭЗ 5 и устанавливает триггер 1 в состояние О . Это позволяет запретить работу устр-ва на период отсутствия ВПИС . 1 э.п. ф-лы , 2 ил.

5

JO

15

25

30

35

40

нуля с выхода сумматора 9 (фиг.2в). Конденсатор 13 второго интегратора 7 разряжен и его потенциал через парал лельно включенные резистор I2 и диод 1I (прямое сопротивление) привязан к потенциалу логического нуля прямого выхода триггера 1. С выхода второго интегратора 7 (фиг.2е) потенциал логического нуля подается на третий вход элемента ИЛИ 2, а с инверсного выхода триггера 1 потенциал логической единицы - на информационный вход первого интегратора 6, на вход Сброс которого поступает потенциал логического нуля. При этом на выходе первого интегратора 6 (фиг.2д) установлен потенциал логической единицы, который через элемент ИЛИ 2 поступает на счетный вход триггера 1 (фиг.2ж), а наD-вход триггера 1 (фиг.2з) поступает потенциал логической единицы с инверсного выхода триггера 1 через первый блок 3 задержки.

На информационный вход третьего интегратора 8 подается постоянно потенциал логической единищ) от источника питания (-fEpi). На вход Сброс третьего интегратора 8 подается потенциал логического нуля, который устанавливает на выходе третьего интегратора 8 (фиг.2г) потенциал логической единицы, удерживающий триггер 1 в нулевом состоянии, что определяет потенциал логической единицы на выходе устройства тактовой синхронизации сигн;злов с расщепленной фазой (фиг.2и). Потенциал логического нуля подается на второй вход сумматора 9 и через второй блок задержки 4 (фиг.2б) - на первый вход сумматора 9, выходной сигнал которого (фиг.2в)

поступает на входы Сброс первого и второго интеграторов 6 и 7.

При поступлении входной последовательности импульсных сигналов с расщепленной фазой, случайные временные интервалы между импульсами которой соответствуют нулевым символам с длительностью Т/2 и Т, а передние фронты импульсов, длительность которых внутри тактового интервала Т соответствует значениям Т и Т/2, совпадают с началом и серединой тактового интервала Т (фиг.2а), на выходе сумматора 9 (фиг.2в)образуются короткие импульсы длительностью €, , соответствующей задержке во втором блоке задержки 4. Величина €, выбирается из условия f, .

Сигнал с выхода сумматора 9 поступает на входы Сброс второго и третьего интеграторов 6 и 7. При этом ключ 10 второго интегратора 7 открывается на время сГ, , подтверждая разряженное состояние конденсатора 13 (фиг.. 2д) и потенциал логического нуля на выходе второго интегратора 7. Первый интегратор 6 также сбрасывается, в результате чего на его выходе формируется потенциал логического нуля.

Входная последовательность импульсных сигналов одновременно поступает на вход Сброс третьего интегратора 8, устанавливая на его выходе потенциал логического нуля, причем за счет выбора времязадающих параметров третьего интегратора его сброс осуществляется с некоторой задержкой по сравнению с моментом сброса первого интегратора 6. В результате на счетный вход триггера 1 (фиг.2ж) поступает импульс, устанавливая его в единичное состояние. На выходе устройства тактовой синхронизации сигналов с расщепленной фазой (фиг.2и) формируется положительный фронт первого импульса выходной последовательности тактовых импульсов, причем с инверсного выхода триггера 1 потен- |циал логического нуля поступает на D-вход триггера 1 (фиг.2з) только через время , равное по длительности времени задержки первого блока 3 задержки, в результате чего триггер 1 на время t Т/2 становится нечувствительным к воздействию по счетному входу. При этом устраняется ложное срабатывание триггера 1 при появле5

0

5

0

0

НИИ сдвоенных импульсов на его счет-, ном входе.

С прямого выхода триггера 1 (фиг.2и) потенциал логической едини- цы поступает на информационный вход второго интегратора 7. Ключ 10 второго интегратора 7, открытый на время б, длительности импульса с выхода сумматора 9, по окончании его закры0 вается и конденсатор 13 начинает заряжаться через параллельно включенные обратное сопротивление диода I1 и резистор 12. Через ремя с Т/2 от момента поступления первого импульса входной последовательности конденсатор 13 (фиг.2е) заряжается до напряжения заданной величины. Одновременно с этим с вьгхода сумматора 9 через элемент 5 запрета и элемент ИЛИ 2 на счетный вход триггера 1 поступает импульс (образованный по отрицательному фронту первого импульса входного сигнала), передним фронтом которого триггер 1 переводится в противоположное состояние. При этом на выходе устройства тактовой синхронизации сигналов с расщепленной фазой формируется отрицательный фронт первого импульса выходной последовательности тактовых импульсов, после чего через время Г потенциал логической единицы с инверсного выхода триггера 1 поступает на D-вход триггера I. Первьй и второй интеграторы 6 и

5 7 сбрасываются сигналом с выхода сумматора 9. Потенциал логической единицы с инверсного выхода триггера I поступает на информационный вход первого интегратора 6, который начинает его интегрирование после окончания импульса, поступившего на вход Сброс. На информационный вход второго интегратора 7 поступает сигнал с прямого выхода триггера 1. При

5 этом на выходе второго интегратора 7 в течение времени Т/2 от момента поступления импульса длительностью Т на вход Сброс второго интегратора 7 устанавливается потенциал ло0 гического нуля (фиг.2и).

Через время Т/2 на выходе первого интегратора 6 (фиг.2д) формируется потенциал логической едини- цы, устанавливающий триггер 1 на D-вход которого поступает потенциал логической единицы) в единичное состояние. При этом на выходе устройства тактовой синхронизации с расщепленной фазой .формируется положительный фронт второго импульса выходной последовательности тактовых импульсов.

После прекращения входной импульс- ной последовательности через время

,5Т от момента окончания последнего импульса последовательности на выходе третьего интегратора (фиг.2г) формируется потенциал логической единицы, запрещающий прохождение сигналов через элемент 5 запрета и устанавливающий триггер 1 в нулевое состояние. При этом на выходе уст

ройства тактовой синхронизации сигна- лов с расщепленной фазой устанавливается потенциал логического нуля до появления вновь входного сигнала.

Применение третьего интегратора 8 позволяет запретить работу устройст- ва тактовой синхронизации сигналов с расщепленной фазой на период отсутствия входного сигнала и быстро вывести на рабочий режим при появлении входного сигнала. При этом (при соответствующем выборе величины времени сброса третьего интегратора 8) повышается помехозащищенность устройства тактовой синхронизации сигналов с расщепленной фазой от импульсных помех при отсутствии входного сигнала.

Формула изобретения

1. Устройство тактовой синхрониза ции сигналов с расщепленной фазой.

и

содержащее последовательно соединенные элемент запрета, элемейт -ИЛИ, триггер и первый блок задержки, а также второй блок задержки, о т л и-, чающееся тем, что, с целью увеличения помехоустойчивости, введены первый, второй и третий интеграторы со сбросом и сумматор по модулю два, при этом выход второго блока задержки чере з cyMN.aTop по модулю два подсоединен к информационному входу элемента запрета и входам Сброс первого и второго интеграторов со сбросом, выходы которых подсоединены к второму и третьему входам элемента ИЛИ, информационные входа первого и второго интеграторов с сбросом подключены соответственно к инверсному и прямому Бы.ходам триггера, В-вход которого подключен к выходу первого блока задержки, информационный вход третьего интегратора с сбросом под- ютючен к шине истРочника питания, а выход третьего интегратора со сбросом подсоединен к запрещающе -1у входу элемента запрета и R-входу триггера, причем второй вход сумматора по модулю два, вход второго блока задержки и вход Сброс третьего интегратора со сбросом объединень и являются входом устройства, а прямой выход , триггера является выходом устройства.

2. Устройство по П.1, о т л и - 35 ч а го щ е е с я тем, что триггер выполнен в Е1зде D-триггера.

срие.2

ВНИИПИ Заказ 797/62

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Тираж 639

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации М-последовательности по задержке | 1986 |

|

SU1398106A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для обработки сообщений | 1990 |

|

SU1803919A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1774497A1 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

| Устройство для настройки и поверки импульсной электроразведочной аппаратуры | 1988 |

|

SU1679444A2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВОГО ПРИЕМНИКА | 1996 |

|

RU2138907C1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

Изобретение относится к электросвязи и обеспечивает увеличение помехоустойчивости. Устр-во содержит триггер 1, элемент ИЛИ 2, блоки задержки (БЗ) 3, 4, элемент запрета (ЭЭ) 5, интеграторы 6-8 со сбросом и сумматор 9 по модулю два. При поступлении входной последовательности импульсных сигналов (ВПИС) с расщепленной фазой на выходе сумматора 9 образуются короткие импульсы длительностью .-u.I, соотв. задержке в БЗ 4. Сигнал с сумматора 9 сбрасывает интеграторы 6, 7. ВПИС устанавливает на выходе интегратора 8 потенциал 1, который устанавливает триггер 1 в состояние 1. При этом на выходе устр-ва формируется положит, фронт первого импульса выходной последовательности тактовых импульсов. За счет подачи потенциала О с инверсного выхода триггера 1 на его D-вход через время , обусловленное БЗ 3, триггер 1 становится нечувствительным к воздействию по счетному входу. При этом устраняется ложное с сл с

| Устройство выделения сигналов тактовой частоты | 1975 |

|

SU557501A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для выделения сигналов тактовой частоты из импульсной последовательности с переменными параметрами | 1981 |

|

SU1003374A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-03-15—Публикация

1985-05-28—Подача