Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении преобразователей аналоговых сигналов, а также функциональных звеньев систем автоматического управления,

Цель изобретения - расширение области применения за счет квантования по уровню пропорционально скорости изменения входного сигнала при повышении точности квантования,

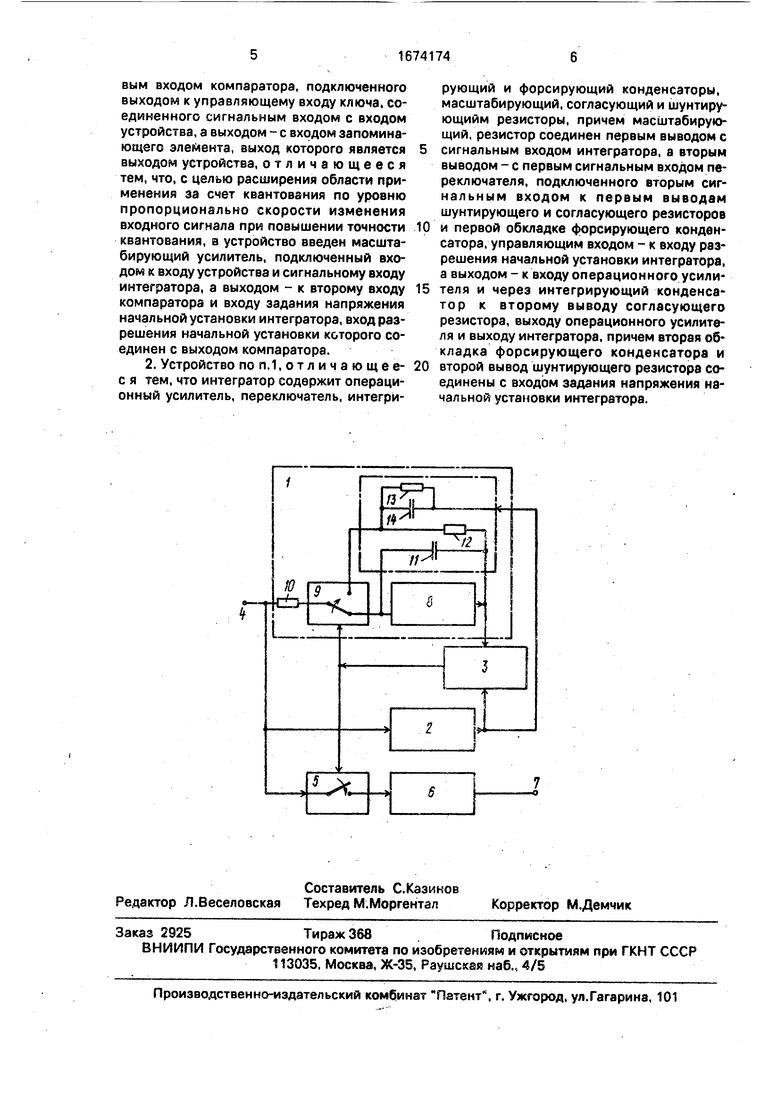

На чертеже изображена блок-схема устройства для квантования непрерывного сигнала по уровню.

Устройство содержит интегратор 1, масштабирующий усилитель 2, компаратор . вход 4 устройства, ключ 5, запоминающий элемент 6 и выход 7 устройства.

Интегратор 1 выполнен ка операционном усилителе 8, переключателе 9, масштабирующем регистре 10 интегрирующем конденсаторе 11, согласующем 12 и шунти- руощем 13 резисторах и форсирующем кон денсаторе 14,

Устройство для квантования непрерывного сигнала по уровню работает следующим образом.

О vj

VJ

к

Входной гигнал с вход 4 устройства для квантования непрерывного сигнала по уровню поступает одновременно на входы масштабирующего усилителя 2, ключа 5 и через масштабирующий резистор 10 на первый сигнальный вход переключателя 9 интегратора 1.

В нормальном рабочем положении при отсутствии управляющего сигнала на выходе компаратора 3 первый вход переключателя 9 скоммутирован на его выход, а сигнальный вход ключа 5 отключен от его выхода. Следовательно, с вь-хода масштабирующего резистора 10 через переключатель 9 входной сигнал поступает на вход операционного усилителя 8. который работает в режиме интегрирования, так как в нормальном режиме (при отсутствии управляющего сигнала на входе разрешения начальной установки интегратора 1) в цепи обратной связи операционного усилителя 8 между его собственным входом и выходом включен интегрирующий конденсатор 11, а во входной цепи - масштабирующий резистор 10. С выхода операционного усилителя 8, являющегося выходом интегратора 1, проинтегрированный входной сигнал поступает одновременно на первые входы компаратора 3 и резистора 12. С выхода масштабирующего усилителя 2 измененный по амплитуде входной сигнал поступает на второй вход компаратора 3 и на вход задания напряжения начальной установки интегратора 1. Компаратор 3 осуществляет сравнение текущих значений сигналов, поступающих на его первый и второй входы, и в момент их равенства вырабатывает управляющий сигнал в виде короткого импульсз, который поступает одновременно на управляющие входы интегратора 1, переключателя 9 и ключа 5. Под воздействием управляющего сигнала выход переключателя 9 отключается от его первого входа и подключается к его второму входу, который соединен с выводами резисторов 12 и 13 и конденсатора 14, при этом выход операционного усилителя 8 через частотно-независимую цепь, образованную параллельно соединенными резистором 13 и конденсатором 14, а также резистором 12 и конденсатором 11, соединяется с выходом и собственным входом операционного усилителя 8. На время действия управляющего импульса интегратор 1 за счет описанной выше коммутации переводится из режима интегрирования в режим установки начальных условий, которые в данном случае определяются мгновенным значением сигнала, действующим на выходе масштабирующего усилителя 2. в оезультзте чего

интегрирующий конденсатор 11 заряжается до напряжения, пропорционального действующему значению сигнала на выходе усилителя 2. Одновременно под действием

управляющего сигнала кратковременно срабатывает ключ 5, соединяя вход устройства 4 с входом запоминающего элемента 6, в результате чего на выходе запоминающего элемента 6 запоминается мгновенное

0 значение входного сигнала, которое поступает на выход 7 устройства. По окончании действия управляющего сигнала устройство переходит в исходное рабочее состояние, при котором вход 4 устройства через масш5 табирующий резистсф 10 и переключатель 9 соединен с собственным входом операционного усилителя 3, который вновь переведен в режим интегрирования, ключ 5 - разомкнут и вход запоминающего элемента

0 б отключен от входа 4 устройства. При этом на выходе запоминающего элемента 6 фиксируется и удерживается до выработки очередного управляющего импульса мгновенное значение входного сигнала, за5 фиксированное при выработке управляющего сигнала.

В дальнейшем циклы работы устройства для квантования непрерывного сигнала по уровню повторяются с той лишь разни0 цей, что интегратор 1 при переводе в режим интегрирования начинает свою работу - интегрирование входного сигнала - каждый раз с новых начальных условий, пропорциональных мгновенному значению сигнала на

5 выходе масштабирующего усилителя 2 на момент выработки на выходе компаратора 3 управляющего сигнала.

В процессе работы устройства для квантования непрерывного сигнала по уровню

0 длительность интервалов квантования входного сигнала определяется моментами сравнения текущих значений входного сигнала и его интеграла, что эквивалентно сравнению текущих значений входного сиг5 нала и его первой производной, Такое техническое решение позволяет осуществить квантование входного сигнала по уровню в функции скорости его изменения, т.е. пропорционально его производной, не прибе0 гая к нахождению самой производной входного сигнала, т.е. исключая операцию дифференцирования, точность определения которой в большой степени зависит от характера изменения входного сигнала и

5 наличия аддитивных помех, особенно в виде шумового сигнала.

Формула изобретения 1. Устройство для квантования непрерывного сигнала по уровню, содержащее интегратор, выход которого соединен с пер

вым входом компаратора, подключенного выходом к управляющему входу ключа, соединенного сигнальным входом с входом устройства, а выходом - с входом запоминающего элемента, выход которого является выходом устройства, отличающееся тем, что, с целью расширения области применения за счет квантования по уровню пропорционально скорости изменения входного сигнала при повышении точности квантования, в устройство введен масштабирующий усилитель, подключенный входом к входу устройства и сигнальному входу интегратора, а выходом - к второму входу компаратора и входу задания напряжения начальной установки интегратора, вход разрешения начальной установки которого соединен с выходом компаратора.

2. Устройство поп.1,отличающее- с я тем, что интегратор содержит операционный усилитель, переключатель, интегрирующий и форсирующий конденсаторы, масштабирующий, согласующий и шунтиру- ющийм резисторы, причем масштабирующий, резистор соединен первым выводом с

сигнальным входом интегратора, а вторым выводом - с первым сигнальным входом переключателя, подключенного вторым сигнальным входом к первым выводам шунтирующего и согласующего резисторов

и первой обкладке форсирующего конденсатора, управляющим входом - к входу разрешения начальной установки интегратора, а выходом - к входу операционного усилителя и через интегрирующий конденсатор к второму выводу согласующего резистора, выходу операционного усилителя и выходу интегратора, причем вторая обкладка форсирующего конденсатора и

второй вывод шунтирующего резистора соединены с входом задания напряжения начальной установки интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1986 |

|

SU1401485A2 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1337784A1 |

| Устройство для оценки работы операторов | 1987 |

|

SU1441442A1 |

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Интегратор | 1988 |

|

SU1728871A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| ВИХРЕТОКОВЫЙ ДЕФЕКТОСКОП | 1995 |

|

RU2085932C1 |

| Импульсный фазовый детектор | 1977 |

|

SU748854A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в преобразователях аналоговых сигналов и функциональных звеньях систем автоматического управления. Целью изобретения является расширение области применения за счет квантования по уровню пропорционально скорости изменения входного сигнала при повышении точности квантования. Устройство содержит интегратор 1, масштабирующий усилитель 2, компаратор 3, ключ 5 и запоминающий элемент 6. Интегратор 1 выполнен на операционном усилителе 8, переключателе 9, резисторах 10, 12 и 13, конденсаторах 11 и 14. Поставленная цель достигается за счет организации замкнутого операционного контура, обеспечивающего квантование по уровню пропорционально производной входного сигнала обращенным методом, что позволяет исключить влияние характера изменения входного сигнала и наличия аддитивного шума на точность формирования управляющего сигнала, причем периодический перевод интегратора 1 из режима интегрирования в режим установки начальных условий позволяет исключить влияние дрейфа нуля и накопленных методической и инструментальных ошибок на точность квантования. 1 ил.

ЙЭ

12

LO±Z3J

| 0 |

|

SU335699A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Нелинейный преобразователь | 1981 |

|

SU1051549A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПЕРИОДИЧЕСКИЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 0 |

|

SU351222A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1989-02-24—Подача