со

с

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА РАДИОВЕЩАНИЯ | 2008 |

|

RU2383103C1 |

| Преобразователь информации | 1986 |

|

SU1322476A1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2011 |

|

RU2462828C1 |

| Измерительная система с автоматическим контролем аналого-цифрового преобразования и блок задания нечувствительности | 1991 |

|

SU1837261A1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1996 |

|

RU2128890C1 |

| Устройство для аналого-цифрового преобразователя | 1988 |

|

SU1594687A1 |

| Устройство для приема и передачи телеметрической информации | 1986 |

|

SU1427403A1 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2011 |

|

RU2479926C1 |

| Устройство для ввода аналоговой информации | 1988 |

|

SU1501026A1 |

Изобретение относится к импульсной и электроизмерительной технике, а именно к устройствам аналого-цифрового преобразования быстро изменяющихся сигналов. Предложенное техническое решение позволяет расширить область применения за счет возможности преобразования двухполярных сигналов. Аналого-цифровой преобразователь содержит N последовательно соединенных усилителей 1 и АЦП 2, при этом выходы N - 1 АЦП 2 соединены поразрядно с входами соответствующих коммутаторов 3 и дешифраторов 4, причем выход каждого дешифратора 4 соединен с управляющим входом соответствующего коммутатора 3. Выходы регистра 5 являются выходами устройства. Источник опорных напряжений 6 соединен с дополнительными входами АЦП 2, выход его соединен с дополнительными входами усилителей 1. 1 з.п. ф., 5 ил.

1

°Ci

Ǥ

сэ

ч

- 4

«о

Os

VI N

со о VI

Изобретение относится к импульсной и электроизмерительной технике, а именно к устройствам аналого-цифрового преобразователя быстроизменяющихся сигналов, и может быть использовано в автоматических устройствах контроля.

Целью изобретения является расширение области применения путем обеспечения возможности преобразования двухполярных напряжений.

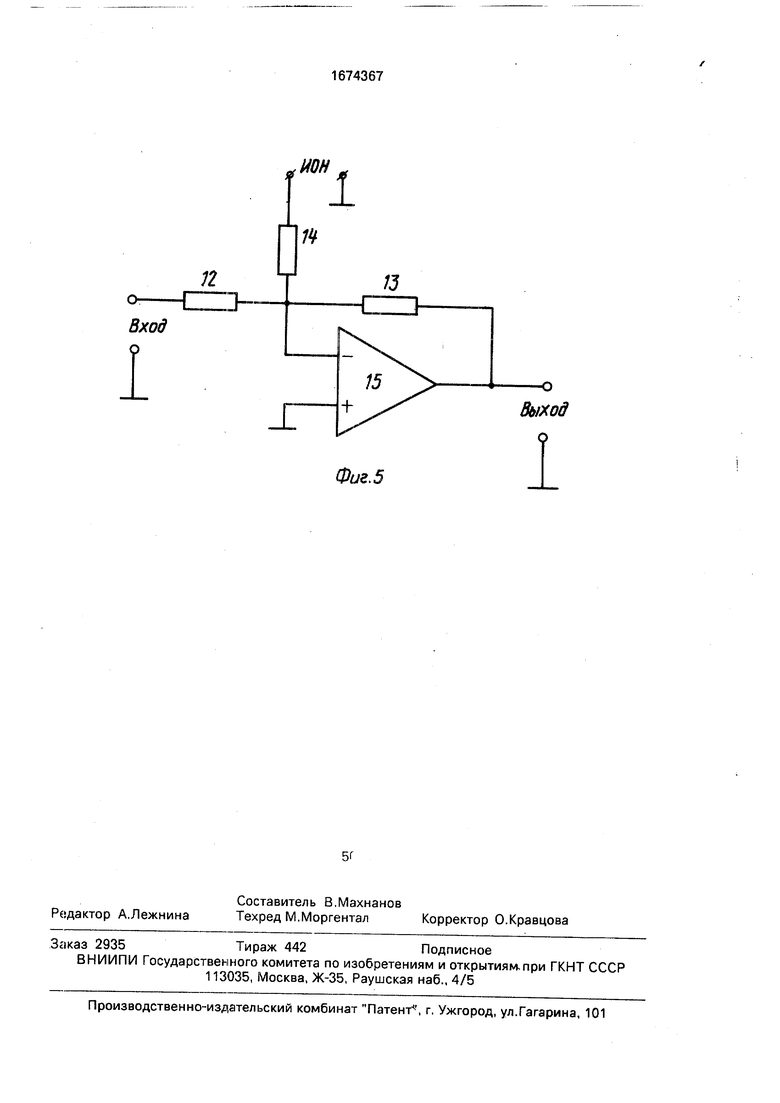

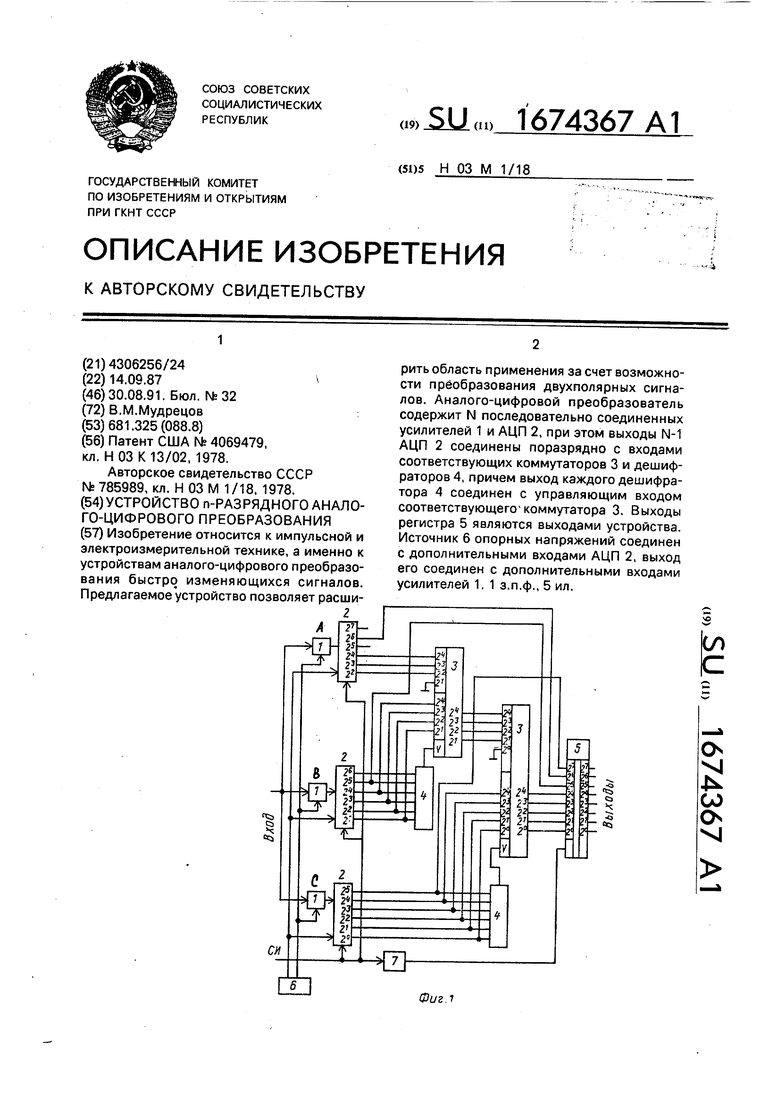

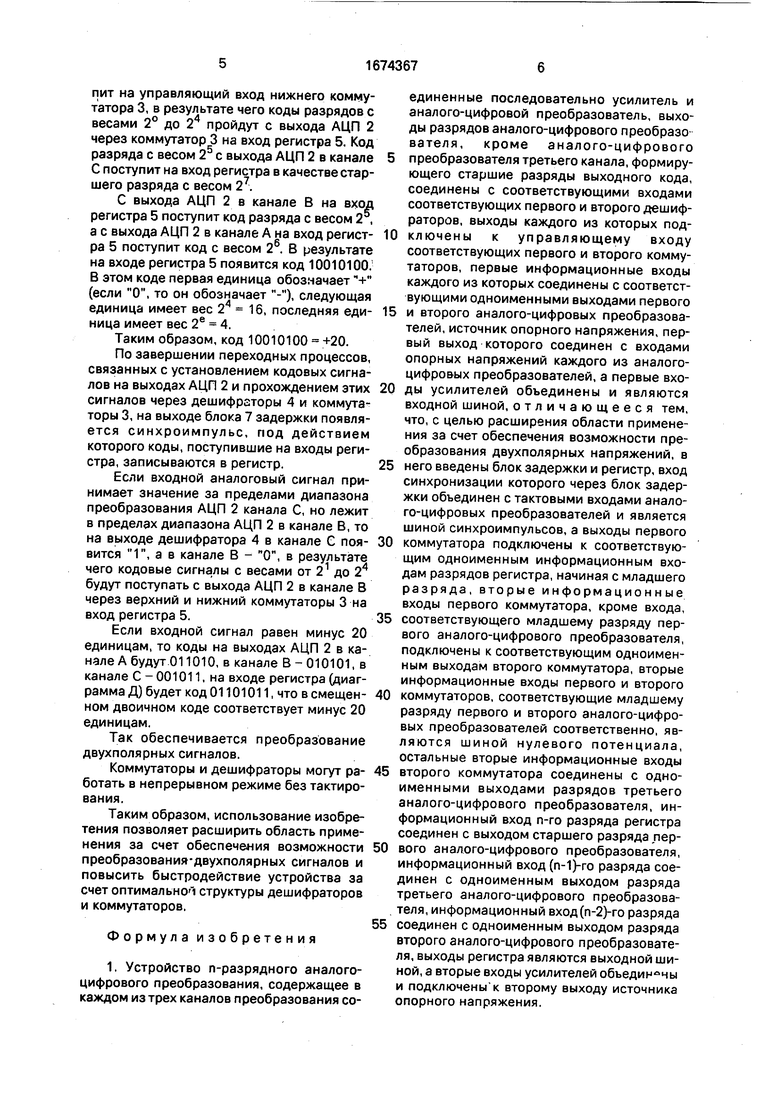

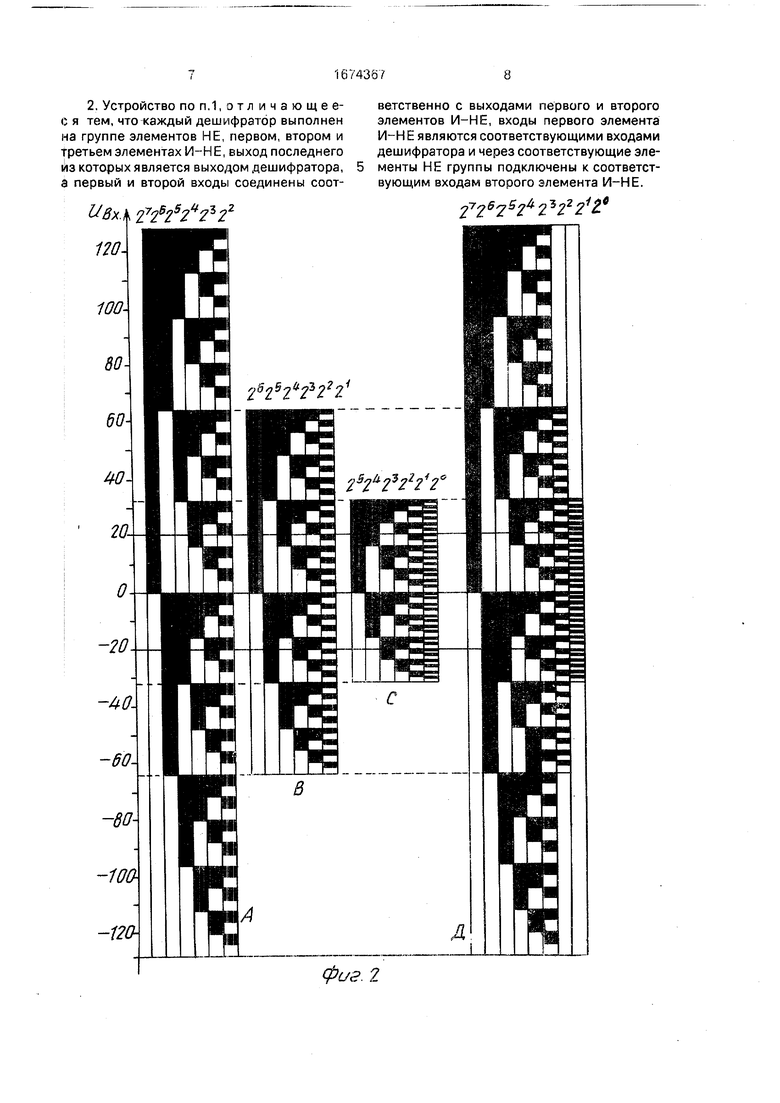

На фиг. 1 представлена функциональная схема устройства n-разрядного аналого-цифрового преобразователя; на фиг. 2 - диаграммы кодов, иллюстрирующие процесс формирования выходных кодов; на фиг. 3 - принципиальная схема и таблица истинности дешифратора; на фиг. 4 - принципиальная схема коммутатора; на фиг. 5 - принципиальная схема усилителя.

Устройство содержит (фиг. 1) усилитель 1, аналого-цифровой преобразователь (АЦП) 2, коммутатор 3, дешифратор 4, регистр 5, источник 6 опорных напряжений, блок 7 задержки. Усилитель вместе с последовательно сопряженным АЦП образуют канал преобразования.

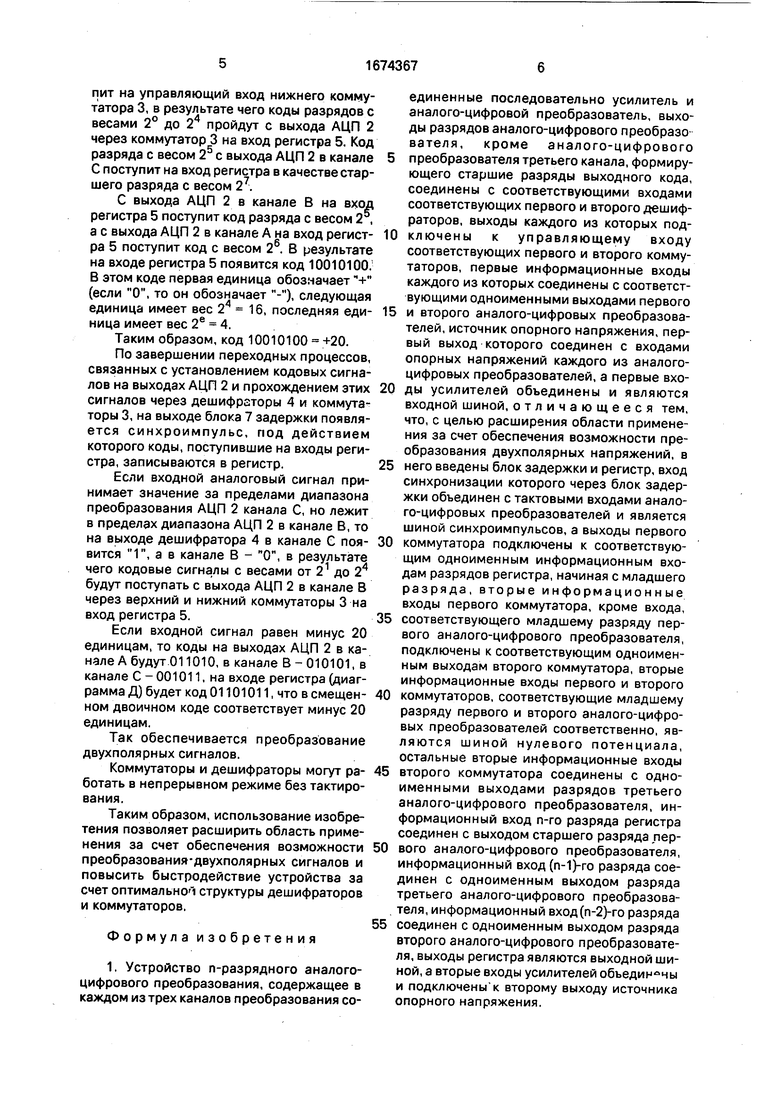

Дешифратор выполнен (фиг. 3) на элементе НЕ 8 и элементе И-НЕ 9.

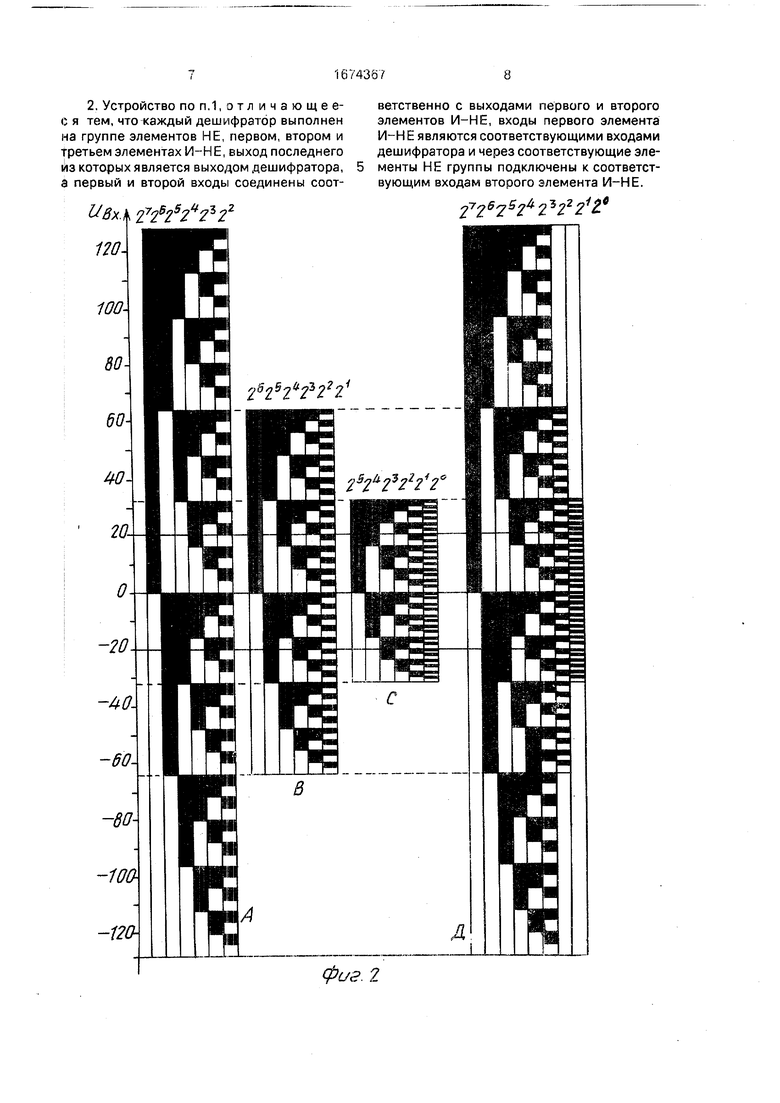

Коммутатор включает (фиг. 4) элемент И-НЕ 10 и элемент НЕ 11.

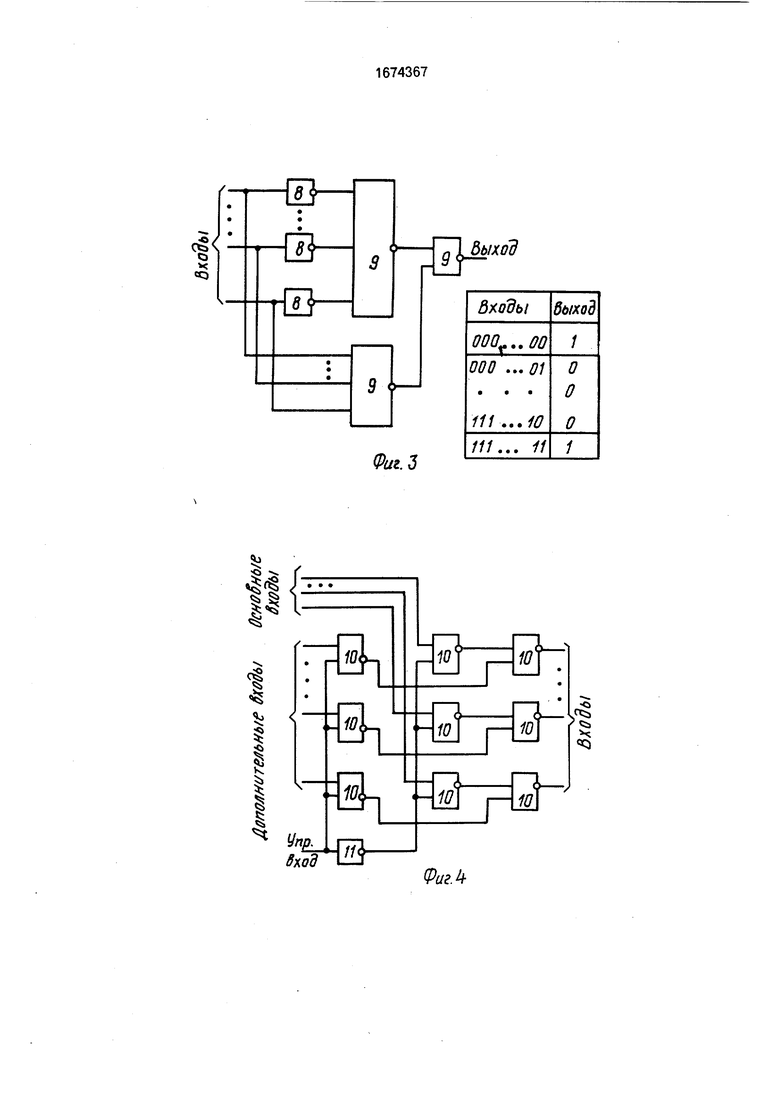

Усилитель выполнен (фиг. 5) на резисторах 12-14 и операционном усилителе 15.

Устройство работает следующим образом.

Подлежащий преобразованию аналоговый электрический сигнал поступает одновременно на входы всех усилителей 1 Каждый усилитель имеет свой коэффициент усиления. Отношение коэффициентов усиления усилителей 1 кратно степени 2, например 1:2:4 и т.д.

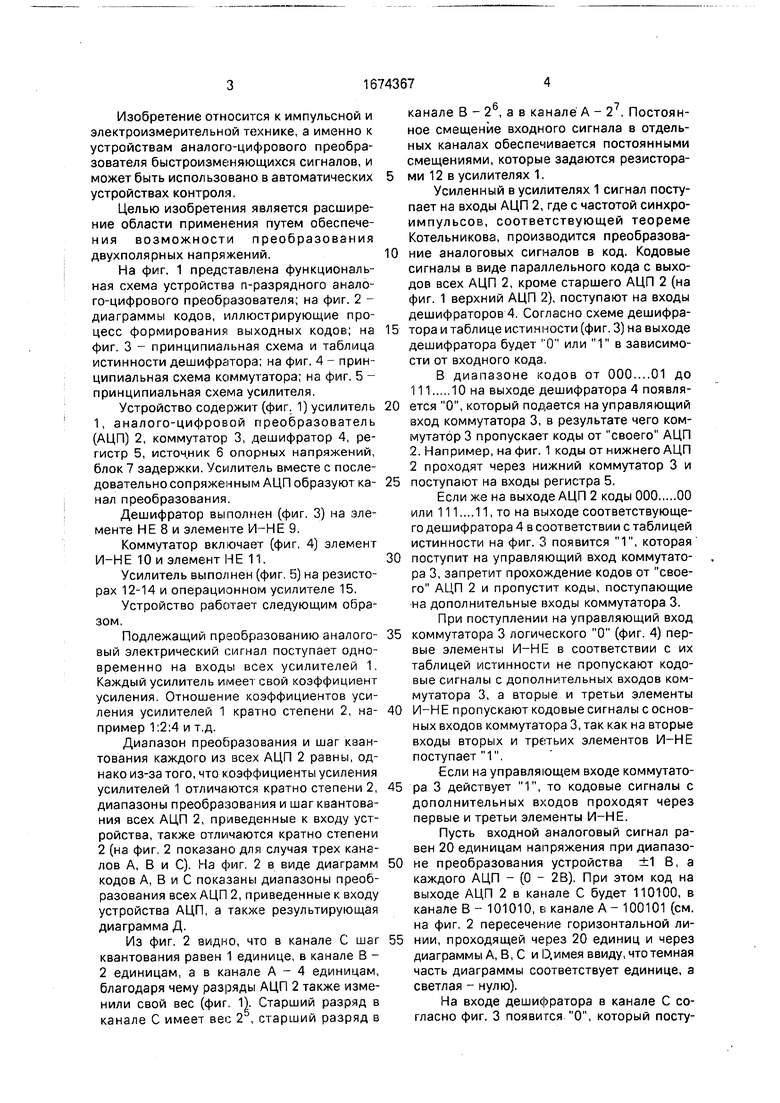

Диапазон преобразования и шаг квантования каждого из всех АЦП 2 равны, однако из-за того, что коэффициенты усиления усилителей 1 отличаются кратно степени 2, диапазоны преобразования и шаг квантования всех АЦП 2, приведенные к входу устройства, также отличаются кратно степени 2 (на фиг. 2 показано для случая трех каналов А, В и С). На фиг. 2 в виде диаграмм кодов А, В и С показаны диапазоны преобразования всех АЦП 2, приведенные к входу устройства АЦП, а также результирующая диаграмма Д.

Из фиг. 2 видно, что в канале С шаг квантования равен 1 единице, в канале В - 2 единицам, а в канале А - 4 единицам, благодаря чему разряды АЦП 2 также изменили свой вес (фиг. 1V Старший разряд в канале С имеет вес 2 , старший разряд в

канале В - 2 , а в канале А - 27. Постоянное смещение входного сигнала в отдельных каналах обеспечивается постоянными смещениями, которые задаются резисторами 12 в усилителях 1.

Усиленный в усилителях 1 сигнал поступает на входы АЦП 2, где с частотой синхроимпульсов, соответствующей теореме Котельникова, производится преобразова0 ние аналоговых сигналов в код. Кодовые сигналы в виде параллельного кода с выходов всех АЦП 2, кроме старшего АЦП 2 (на фиг. 1 верхний АЦП 2), поступают на входы дешифраторов 4. Согласно схеме дешифра5 тора и таблице истинности (фиг. 3) на выходе дешифратора будет О или 1 в зависимости от входного кода

В диапазоне кодов от 000....01 до 11110 на выходе дешифратора 4 появля0 ется О, который подается на управляющий вход коммутатора 3, в результате чего коммутатор 3 пропускает коды от своего АЦП 2. Например, на фиг. 1 коды от нижнего АЦП 2 проходят через нижний коммутатор 3 и

5 поступают на входы регистра 5.

Если же на выходе АЦП 2 коды 00000

или 111 ....11, то на выходе соответствующего дешифратора 4 в соответствии с таблицей истинности на фиг. 3 появится 1, которая

0 поступит на управляющий вход коммутатора 3, запретит прохождение кодов от своего АЦП 2 и пропустит коды, поступающие на дополнительные входы коммутатора 3. При поступлении на управляющий вход

5 коммутатора 3 логического О (фиг. 4) первые элементы И-НЕ в соответствии с их таблицей истинности не пропускают кодовые сигналы с дополнительных входов коммутатора 3, а вторые и третьи элементы

0 И-НЕ пропускают кодовые сигналы с основных входов коммутатора 3, так как на вторые входы вторых и третьих элементов И-НЕ поступает 1.

Если на управляющем входе коммутато5 ра 3 действует 1, то кодовые сигналы с дополнительных входов проходят через первые и третьи элементы И-НЕ.

Пусть входной аналоговый сигнал равен 20 единицам напряжения при диапазо0 не преобразования устройства ±1 В, а каждого АЦП - (0 - 2В). При этом код на выходе АЦП 2 в канале С будет 110100, в канале В - 101010, в канале А - 100101 (см. на фиг. 2 пересечение горизонтальной ли5 нии, проходящей через 20 единиц и через диаграммы А, В, С и Цимея ввиду, что темная часть диаграммы соответствует единице, а светлая - нулю).

На входе дешифратора в канале С согласно фиг. 3 появится О, который поступит на управляющий вход нижнего коммутатора 3, в результате чего коды разрядов с весами 2° до 2 пройдут с выхода АЦП 2 через коммутатор 3 на вход регистра 5. Код разряда с весом 25 с выхода АЦП 2 в канале С поступит на вход регистра в качестве старшего разряда с весом 27,

С выхода АЦП 2 в канале В на вход регистра 5 поступит код разряда с весом 2 , а с выхода АЦП 2 в канале А на вход регистра 5 поступит код с весом 2 . В результате на входе регистра 5 появится код 10010100. В этом коде первая единица обозначает + (если О, то он обозначает -), следующая единица имеет вес 24 16, последняя единица имеет вес 2е 4.

Таким образом, код 10010100 +20.

По завершении переходных процессов, связанных с установлением кодовых сигналов на выходах АЦП 2 и прохождением этих сигналов через дешифраторы 4 и коммутаторы 3, на выходе блока 7 задержки появляется синхроимпульс, под действием которого коды, поступившие на входы регистра, записываются в регистр.

Если входной аналоговый сигнал принимает значение за пределами диапазона преобразования АЦП 2 канала С, но лежит в пределах диапазона АЦП 2 в канале В, то на выходе дешифратора 4 в канале С появится 1, а в канале В - О, в результате чего кодовые сигналы с весами от 21 до 24 будут поступать с выхода АЦП 2 в канале В через верхний и нижний коммутаторы 3 на вход регистра 5.

Если входной сигнал равен минус 20 единицам, то коды на выходах АЦП 2 в канале А будут 011010, в канале В - 010101, в канале С - 001011, на входе регистра (диаграмма Д) будет код 01101011, что в смещенном двоичном коде соответствует минус 20 единицам.

Так обеспечивается преобразование двухполярных сигналов.

Коммутаторы и дешифраторы могут работать в непрерывном режиме без тактирования.

Таким образом, использование изобретения позволяет расширить область применения за счет обеспечения возможности преобразования-двухполярных сигналов и повысить быстродействие устройства за счетоптимально 1 структуры дешифраторов и коммутаторов.

Формула изобретения

преобразователя третьего канала, формирующего старшие разряды выходного кода, соединены с соответствующими входами соответствующих первого и второго дешифраторов, выходы каждого из которых под0 ключены к управляющему входу соответствующих первого и второго коммутаторов, первые информационные входы каждого из которых соединены с соответствующими одноименными выходами первого

5 и второго аналого-цифровых преобразователей, источник опорного напряжения, первый выход которого соединен с входами опорных напряжений каждого из аналого- цифровых преобразователей, а первые вхо0 ды усилителей объединены и являются входной шиной, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности преобразования двухполярных напряжений, в

5 него введены блок задержки и регистр, вход синхронизации которого через блок задержки объединен с тактовыми входами аналого-цифровых преобразователей и является шиной синхроимпульсов, а выходы первого

0 коммутатора подключены к соответствующим одноименным информационным входам разрядов регистра, начиная с младшего разряда, вторые информационные входы первого коммутатора, кроме входа,

5 соответствующего младшему разряду первого аналого-цифрового преобразователя, подключены к соответствующим одноименным выходам второго коммутатора, вторые информационные входы первого и второго

0 коммутаторов, соответствующие младшему разряду первого и второго аналого-цифровых преобразователей соответственно, являются шиной нулевого потенциала, остальные вторые информационные входы

5 второго коммутатора соединены с одноименными выходами разрядов третьего аналого-цифрового преобразователя, информационный вход n-го разряда регистра соединен с выходом старшего разряда пер0 вого аналого-цифрового преобразователя, информационный вход (п-1)-го разряда соединен с одноименным выходом разряда третьего аналого-цифрового преобразователя, информационный вход(п-2)-го разряда

5 соединен с одноименным выходом разряда второго аналого-цифрового преобразователя, выходы регистра являются выходной шиной, а вторые входы усилителей объединены и подключены к второму выходу источника опорного напряжения.

ветственно с выходами первого и второго элементов И-НЕ, входы первого элемента И-НЕ являются соответствующими входами дешифратора и через соответствующие элементы НЕ группы подключены к соответствующим входам второго элемента И-НЕ.

ч

п

О

#

оL

Вход

1

L

.5

/j

Выход

1

| Патент США № 4069479, кл | |||

| Насос | 1917 |

|

SU13A1 |

| Многопредельный аналого-цифровой преобразователь | 1978 |

|

SU785989A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-08-30—Публикация

1987-09-14—Подача