ел

со

4;:

О5 00

Изобретение относится к вычислительной технике и может быть использовано для преобразования аналоговьпс величин в цифровые, а также для цифровой обработки сигналов, кроме того, дня получения цифровой информации о расположении объекта в двухмерной системе координат.

Цель изобретения - расширение функ циональных возможностей посредством преобразования аналогового сигнала в код с основанием 2 и контроля пра вильности преобразования.

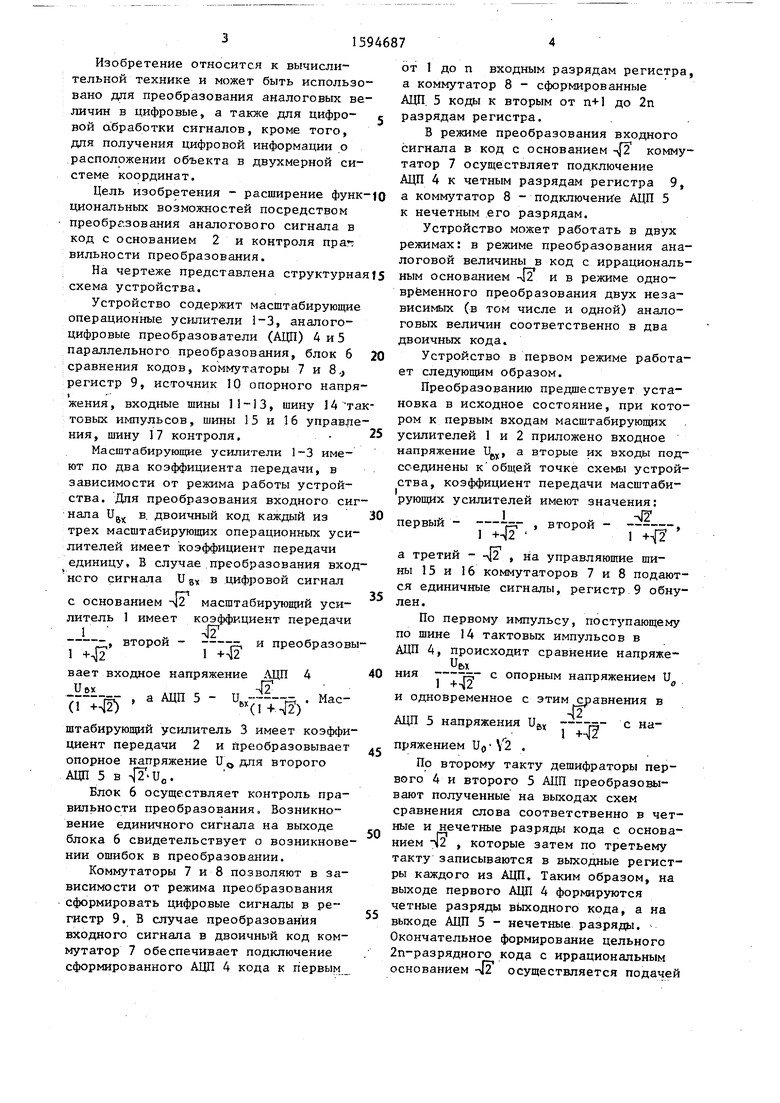

На чертеже представлена структурна схема устройства.

Устройство содержит масштабирующие операционные усилители 1-3, аналого- цифровые преобразователи (АЦП) 4и5 параллельного преобразования, блок 6 сравнения кодов, коммутаторы 7 и 8.

регистр 9, источник 10 опорного напря I

жения, входные шины 1-13, шину 14 татовых импульсов, шины 15 и 16 управления, шину 17 контроля.

Масштабирующие усилители 1-3 имеют по два коэффициента передачи, в зависимости от режима работы устройства. Для преобразования входного сигнала и в. двоичный код каждый из трех масштабируюш 1х операционных усилителей имеет коэффициент передачи единицу, В случае преобразования входного сигнала U вк в цифровой сигнал

с основанием 42 масштабирующий уси- литель 1 имеет коэффициент передачи

Г „

второй - - и преобразовы1 +л121 +

вает входное напряжение АЦП 4 -..1. , , д„П 3 - D..--C.Ma штабирующий усилитель 3 имеет коэф(})и- циент передачи 2 и преобразовывает опорное напряжение U для второго АЦП 5 в U.

Блок 6 осуществляет контроль правильности преобразования,, Возникновение единичного сигнала на выходе блока 6 свидетельствует о возникновении ошибок в преобразовании.

Коммутаторы 7 и 8 позволяют в зависимости от режима преобразования сформировать цифровые сигналы в регистр 9. В случае преобразования входного сигнала в двоичный код коммутатор 7 обеспечивает подключение сформированного АЦП 4 кода к первым

ю

5

20

25

30

40

дс

5

от 1 до п входным разрядам регистра, а коммутатор 8 - сформированные АЦП 5 коды к вторым от п+ до 2п разрядам регистра.

В режиме преобразования входного сигнала в код с основанием - коммутатор 7 осуществляет подключение АЦП 4 к четным разрядам регистра 9, а коммутатор 8 - подключение АЦП 5 к нечетным его разрядам.

Устройство может работать в двух режимах: в режиме преобразования аналоговой величины в код с иррациональным основанием 4 и в режиме одновременного преобразования двух независимых (в том числе и одной) аналоговых величин соответственно в два двоичных кода.

Устройство в первом режиме работает следующим образом.

Преобразованию предшествует установка в исходное состояние, при котором к первым входам масштабирующих усилителей 1 и 2 приложено входное напряжение U, а вторые их входы подсоединены к общей точке схемы устройства, коэффициент передачи масштаби- усилителей имеют значения:

первый - рг , второй - ,

1 +42 +{1

а третий - nfi , на управляющие шины 15 и 16 коммутаторов 7 и 8 подаются единичные сигналы, регистр 9 обнулен.

По первому импульсу, поступающему по шине 14 тактовых импульсов в АЦП 4, происходит сравнение напряжеUfcx

ния --- с опорным напряжением U I +s2о

и одновременное с этим сравнения в

-|2 АЦП 5 напряжения UB, -.- с на.г 1 Н2 пряжением Uo 2 .

По второму такту дешифраторы первого 4 и второго 5 АЦП преобразовывают полученные на выходах схем сравнения слова соответственно в четные и нечетные разряды кода с основанием -ч2 , которые затем по третьему такту записываются в выходные регистры каждого из АЦП. Таким образом, на выходе первого АЦП 4 формируются четные разряды вькодного кода, а на выходе АЦП 5 - нечетные разряды. Окончательное формирование цельного 2п-разрядного кода с иррациональным основанием -Jz осуществляется подачей

10

нулевого сигнала в шину 15 коммута торов 7 и 8, которые организовывают подключение четных и нечетных п-раз- рядов кода 2 с выходов АЦП на соответствующие входы регистра 9 с последующей записью.

Блок 6 осуществляет контроль правильности преобразования - единица на выходе схемы сигнализирует об ошибке в преобразовании.

Второй режим работы устройства для аналого-ц 1фрового преобразования отличается тем, что в исходном состоянии первые входы первого I и второго 2 масштабирующих усилителей подсоединены к общей точке схемы, а на вторые их входы поданы независимые входные напряжения соответственно U.,,

чВЛ

и коэффициенты передачи каждого из трех масштабирующих усилителей равны единице, на управляющую шину 15 подан нулевой сигнал.

По первому тактовому импульсу вход-, ..., „ ..,.„

ные напряжения Ug,, и Ug. сравниваются 25 масштабирующие операционные усилите- г. г,,л.„„„.. тт „ jjjj ВЫХОДЫ которых подключены соотобразования в процессе работы устро ства, т.е. осуществляет контроль.

5 Формула изобретени

Устройство для аналого-цифрового преобразования, содержащее первый аналого-цифровой преобразователь и источник опорного напряжения, выход которого соединен с первым входом первого аналого-цифрового преобразов теля, второй вход которого является шиной тактовых импульсов, отличающееся тем, что, с целью расширения функциональных возможностей путем создания дополнительной во можности преобразования аналоговой в личины в код с иррациональным основа нием /2 и контроля правильности пре образования, в него введены блок сра нения кодов, регистр, два коммутатора, второй аналого-цифровой преобразователь, первый, второй и третий

15

20

с напряжением U„ в схемах сравнения соответственно первого 4 и второго 5

АЦП.

Во время второго такта в каждом АЦП происходит дещифрация слова, полученного на выходах схем сравнения, а затем в третьем такте осуществляется запись в выходные регистры АЦП N1- и N2 п-разрядных двоичных кодов: в первом АЦП 4-кода, соответст- взпощего первому входному напряжению Ug, во втором АЦП 5 - кода, соответствующего напряжению Ug, .

Вследствие приложения нулевого сигнала к щине 15 с помощью коммутаторов 7 и 8 осуществляется запись выходного кода N1 в младшие от единицы до п разрядов, а кода V 2 - в старшие от п+1 до 2п разрядов регистра 9 устройства для аналого-цифрового преобразования.

По сравнению с известным предлагаемое устройство обладает более широкими функциональными возможностями в связи с тем, что устройство способно преобразовывать напряжение в цифровую величину, представленную кгк двоичным п-разрядным кодом, так и 2п-разрядным кодом с основанием V2, а также преобраз.овывать одновременно два независимых напряжения Ug, и 8xz два N1- и N2 п-разрядных двоичных кода, кроме того, обладает способностью обнаружения ошибки пре35

40

ветственно к третьему входу первого аналого-цифрового преобразователя, jc первому и второму входам второго ана- 30 лого-цифрового преобразователя, третий вход которого является шиной тактовых импульсов, выходы первого анало го-цифрового преобразователя соединены с соответствующими первыми информационными входами первого и второ го коммутаторов и блока сравнения кодов, выходы второго аналого-цифрового преобразователя соединены с соответствующими вторыми информационными входами первого и второго коммутаторов и блока сравнения кодов, а первый и второй управляющие входы первого и второго коммутаторов соответственно объединены и являются соответственно д5 первой и второй управляющими шинами, выходы первого и второго коммутаторов соединены соответственно с пер- вым и вторым входами регистра, первые входы первого и второго масштабирующих операционных усилителей объединены и являются первой входной шиной, вторые входы являются соответственно второй и третьей входными шинами, вход третьего масштабирующего операционного усилителя подключен к выходу

50

55

источника опорного напряжения, выходы блока сравнения кодов являются шиной контроля, выходы регистра являются выходной шиной.

1594687

0

, ..., „ ..,.„

5 масштабирующие операционные усилите- jjjj ВЫХОДЫ которых подключены соотобразования в процессе работы устройства, т.е. осуществляет контроль.

5 Формула изобретения

Устройство для аналого-цифрового преобразования, содержащее первый аналого-цифровой преобразователь и источник опорного напряжения, выход которого соединен с первым входом первого аналого-цифрового преобразователя, второй вход которого является шиной тактовых импульсов, отличающееся тем, что, с целью расширения функциональных возможностей путем создания дополнительной возможности преобразования аналоговой величины в код с иррациональным основанием /2 и контроля правильности преобразования, в него введены блок сравнения кодов, регистр, два коммутатора, второй аналого-цифровой преобразователь, первый, второй и третий

5

0

35

0

ветственно к третьему входу первого аналого-цифрового преобразователя, jc первому и второму входам второго ана- 30 лого-цифрового преобразователя, третий вход которого является шиной тактовых импульсов, выходы первого аналого-цифрового преобразователя соединены с соответствующими первыми информационными входами первого и второ- го коммутаторов и блока сравнения кодов, выходы второго аналого-цифрового преобразователя соединены с соответствующими вторыми информационными входами первого и второго коммутаторов и блока сравнения кодов, а первый и второй управляющие входы первого и второго коммутаторов соответственно объединены и являются соответственно 5 первой и второй управляющими шинами, выходы первого и второго коммутаторов соединены соответственно с пер- вым и вторым входами регистра, первые входы первого и второго масштабирующих операционных усилителей объединены и являются первой входной шиной, вторые входы являются соответственно второй и третьей входными шинами, вход третьего масштабирующего операционного усилителя подключен к выходу

0

5

источника опорного напряжения, выходы блока сравнения кодов являются шиной контроля, выходы регистра являются выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Преобразователь напряжение-код | 1988 |

|

SU1508343A1 |

| Устройство для цифроаналогового преобразования | 1987 |

|

SU1411978A1 |

| МОДУЛЬ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЙ ПОСТОЯННОГО ТОКА В КОД | 2007 |

|

RU2365033C2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1095389A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1547059A1 |

| Цифроаналоговый преобразователь | 1982 |

|

SU1051701A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1251326A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

Изобретение относится к вычислительной технике и может быть использовано для преобразования аналоговых величин в цифровые, а также при цифровой обработке сигналов и, кроме того, для получения цифровой информации о расположении объекта в двумерной системе координат. Изобретение позволяет расширить функциональные возможности посредством преобразования аналогового сигнала в код с основанием √2 и контроля правильности преобразования. Это достигается тем, что в устройство, содержащее источник 10 опорного напряжения, аналого-цифровой преобразователь 4, введены масштабирующие операционные усилители 1, 2, 3, аналого-цифровой преобразователь 5, коммутаторы 7, 8, регистр 9, блок 6 сравнения кодов. 1 ил.

| Гитис Э.И | |||

| Аналого-цифровые преобразователи | |||

| - М.: Энергоиздат, 1981, с.241 | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналоговые и цифровые интегральные схемы./Под ред.С.В.Якубовского.- М.: Радио и связь, 1984, с.366, рис.6.92. | |||

Авторы

Даты

1990-09-23—Публикация

1988-04-01—Подача