N4

Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

Изобретение относится к вычислительной технике. Цель изобретения состоит в повышении быстродействия устройства. Устройство состоит из генератора тактовых импульсов, генератора псевдослучайных чисел, блока синхронизации, счетчика длины т.еста, блока задания исходных данных, трёх регистров сдвига, двух счетчиков, мультиплексора, элемента И, группы элементов И, группы триггеров, блока памяти и узла коммутации. Устройство позволяет проводить в автокатическом режиме синтез и генерацию тестовых последовательностей. 7 ил. да

Ю

|шв

Изобретение относится к автомати- ре и вычислительной технике и может ыть использовано при производствен- юм контроле интегральных схем, а

также узлов и блоков на основе этих схем,

Цель .изобретения - повышение быстродействия.

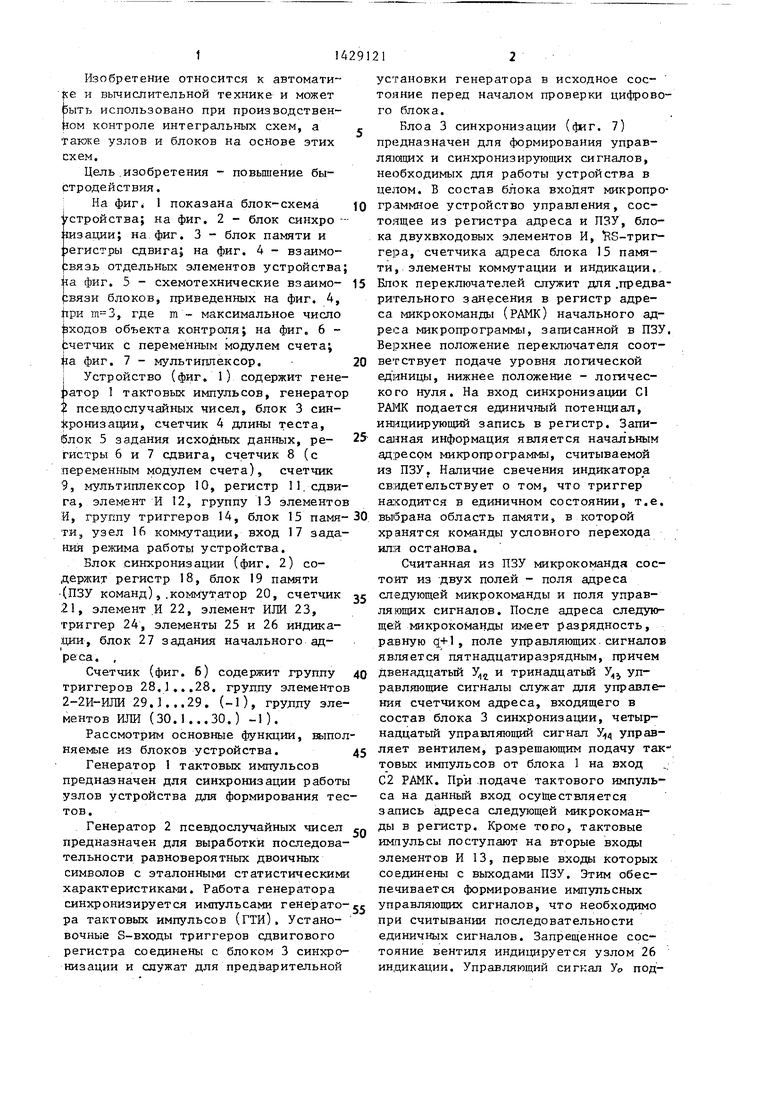

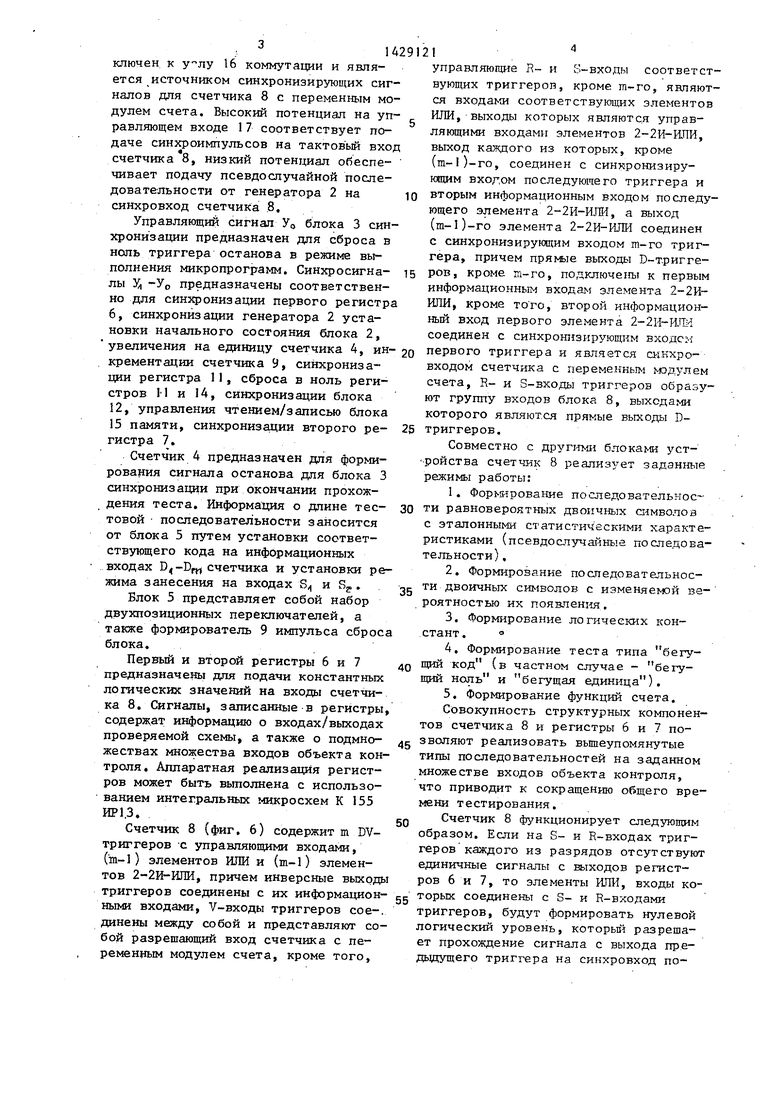

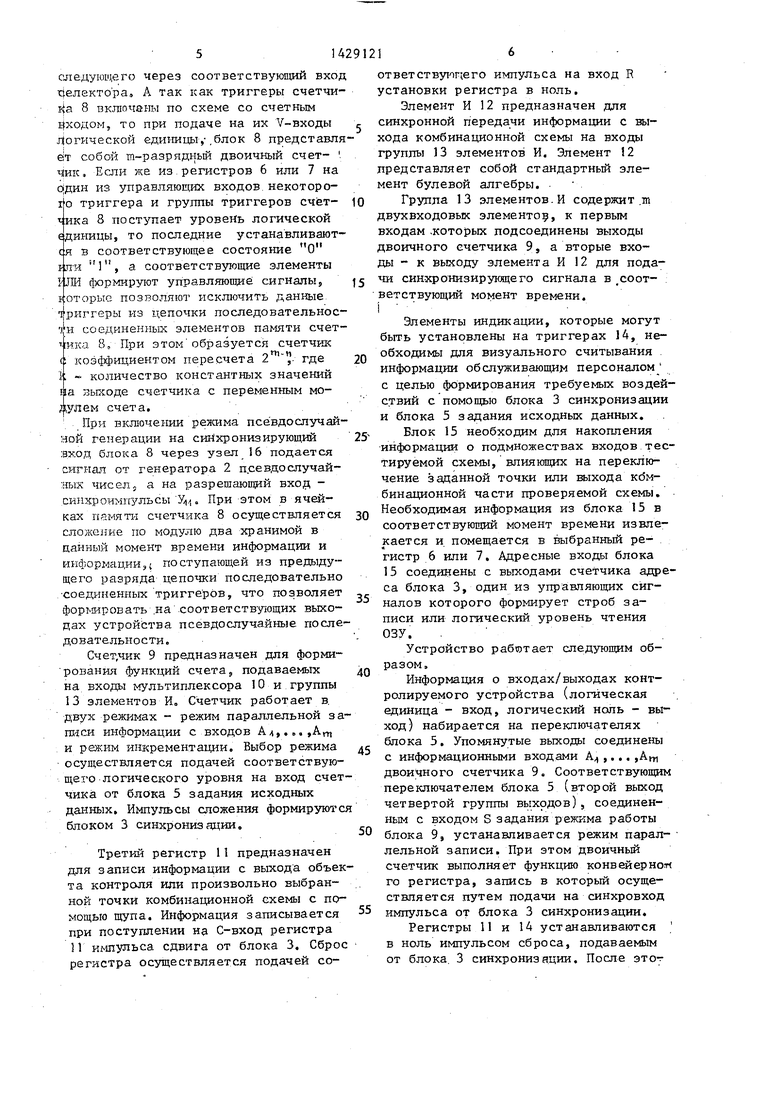

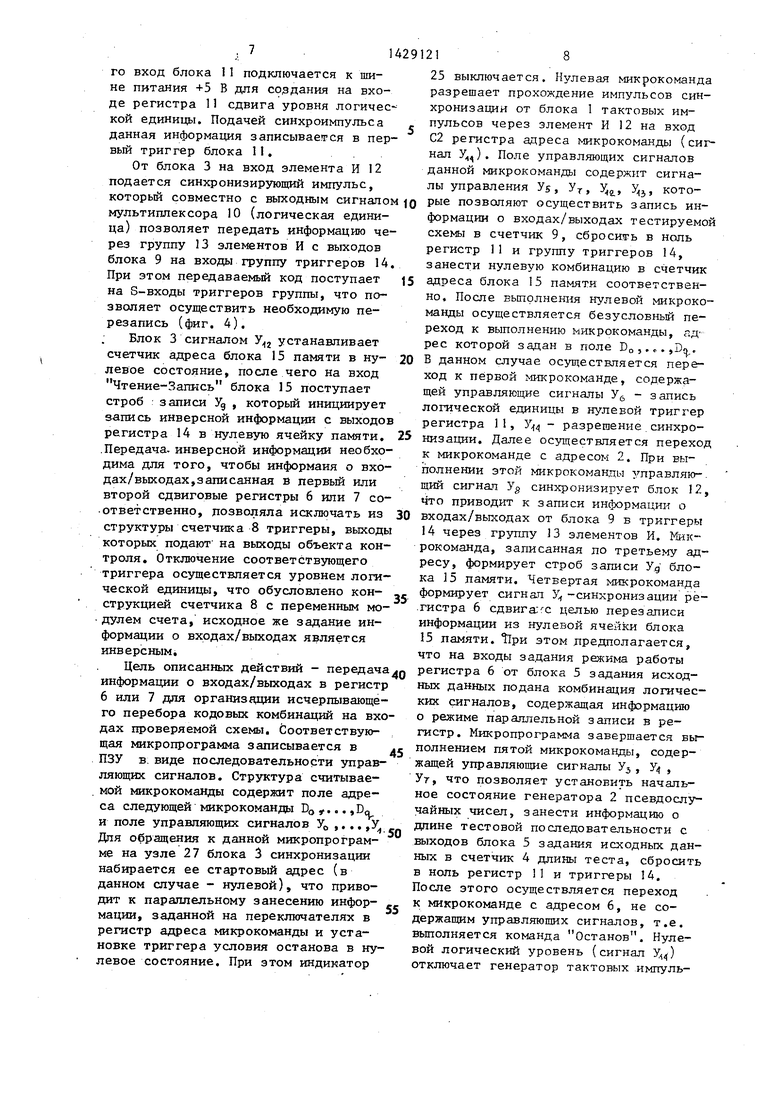

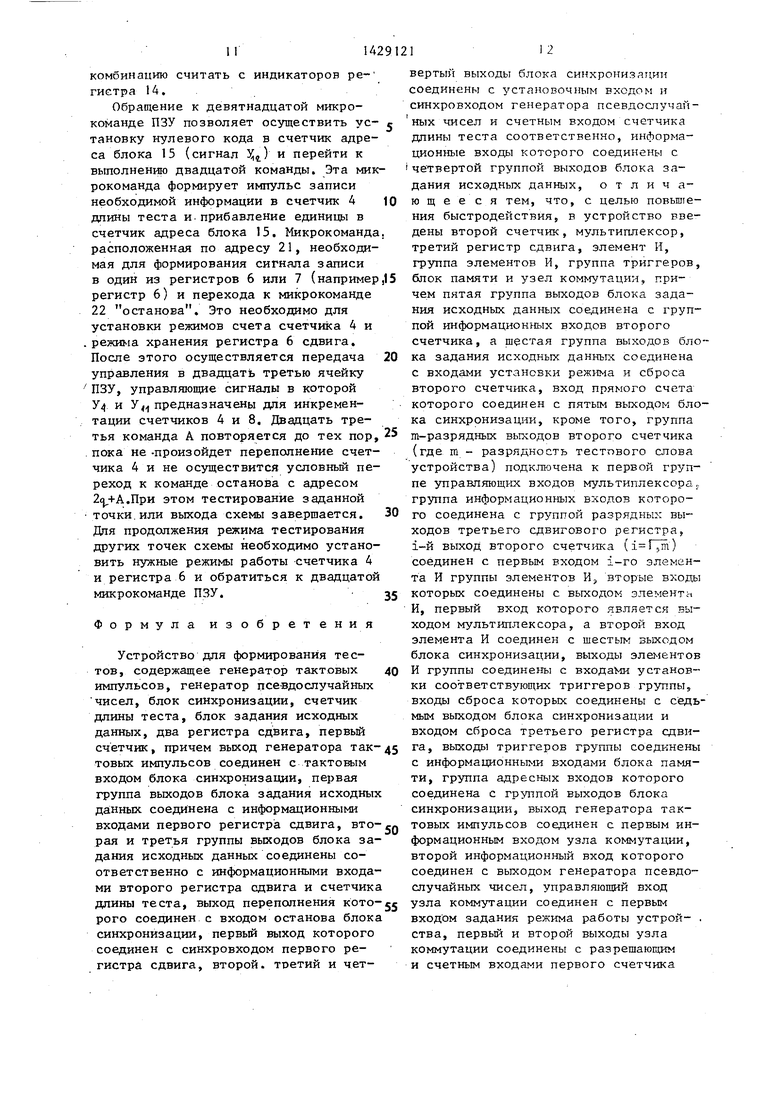

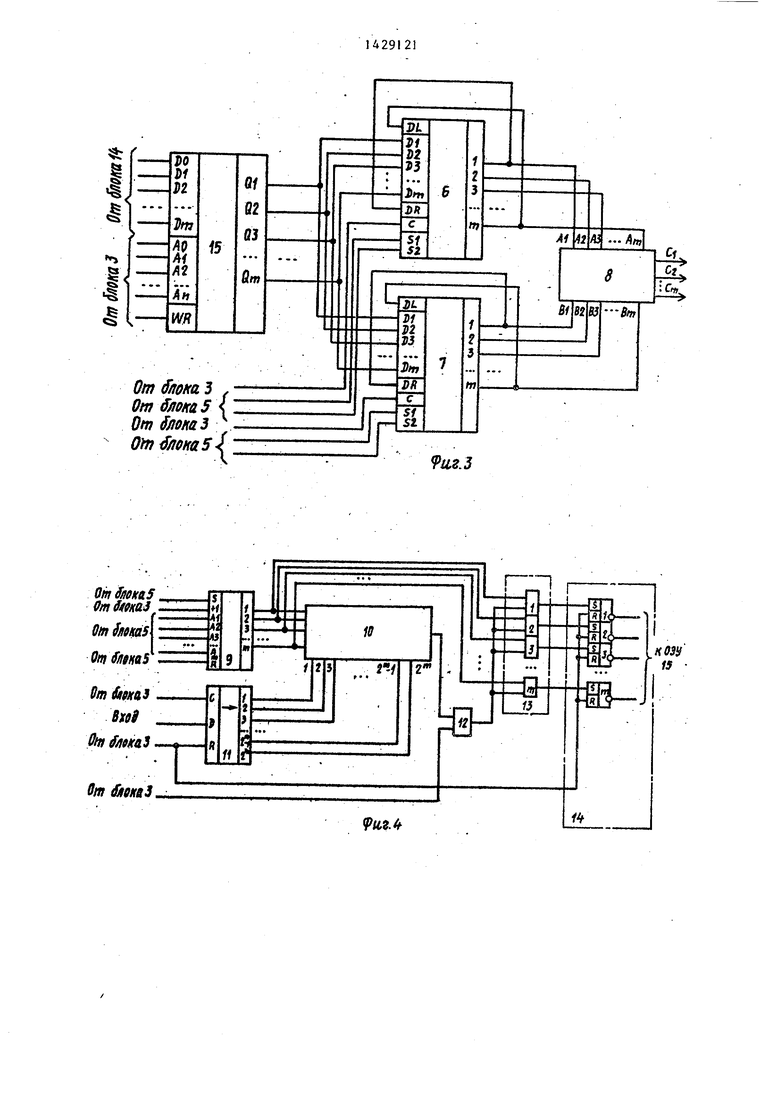

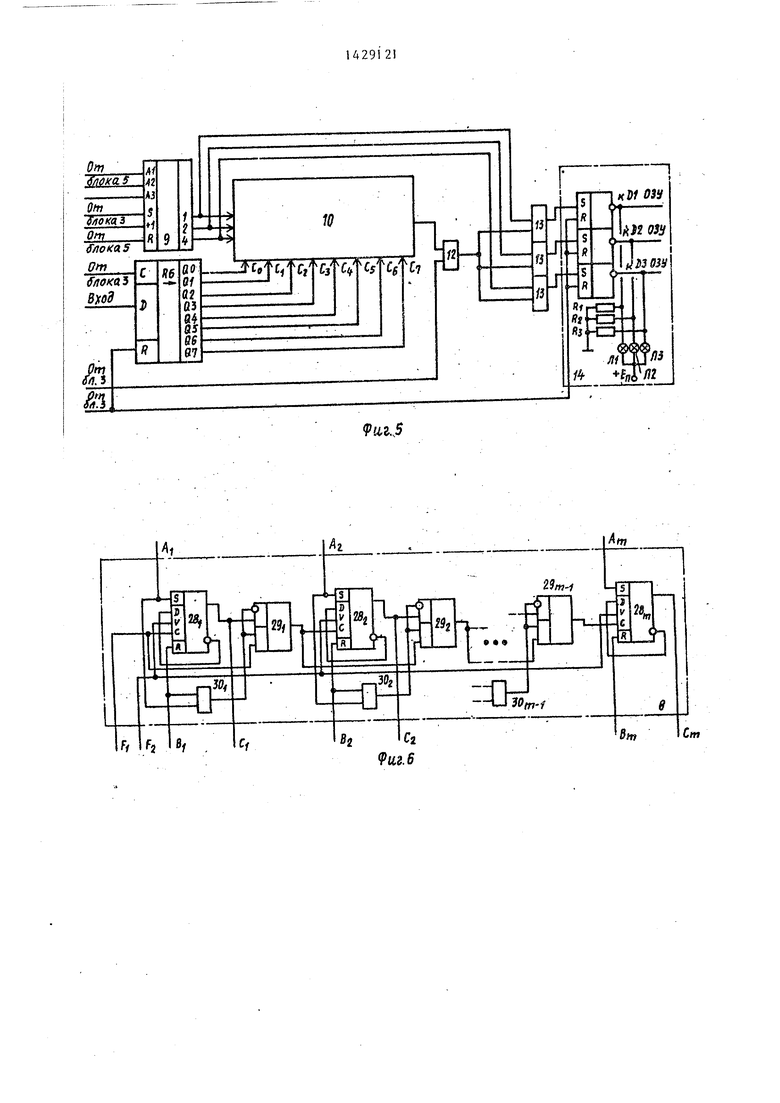

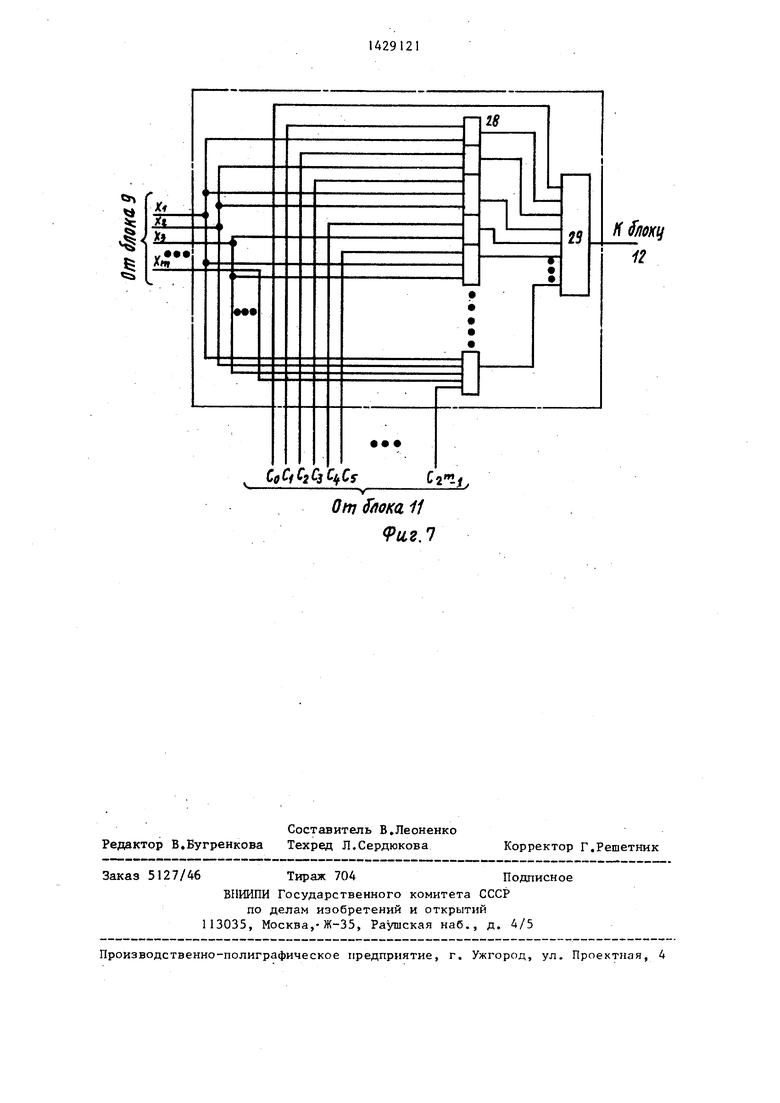

: На фиг 1 показана блок-схема стройства; на фиг, 2 - блок синхро - : 1зации; на фиг, 3 - блок памяти и ;зегистры сдвига на фиг, 4 - взаимо- ;вязь отдельных элементов устройства; йа фиг, 5 - схемотехнические взаимо- :вязи блоков, приведенных на фиг, 4, IIPH , где m - максимальное число ходов объекта контроля; на фиг, 6 - Ьчетчик с переменным модулем счета; jia фиг, 7 - мультиплексор,

I Устройство (фиг. 1) содержит гене- jjaTOp 1 тактовых импульсов, генератор t псевдослучайных чисел, блок 3 син- сронизации, счетчик 4 длины теста, блок 5 задания исходных данных, ре- гистры 6 и 7 сдвига, счетчик 8 (с переменным модулем счета), счетчик 9, мультиплексор 10, регистр П. сдвига, элемент И 12, группу 13 элементов И, группу триггеров 14, блок 15 памяти, узел 16 коммутации, вход 17 зада- ккя режима работы устройства,

Блок синхронизации (фиг, 2) содержит регистр 18, блок 19 памяти (ПЗУ команд),.коммутатор 20, счетчик 21, элемент ,И 22, элемент ИЛИ 23, триггер 24, элементы 25 и 26 индикации, блок 27 задания начального адреса, ,

Счетчик (фиг. 6) содержит группу триггеров 28,,,,28, группу элементов 2-2И-ИЛИ 29,,,,29. (-1), грулду элементов ИЛИ (30,1,,,30,) -1).

Рассмотрим основные функции, няемые из блоков устройства,

Генератор 1 тактовых импульсов предназначен для синхронизации работы узлов устройства для формирования тестов.

Генератор 2 псевдослучайных чисел предназначен для выработки последовательности равновероятных двоичных символов с эталонными статистическими характеристиками. Работа генератора синхронизируется импульсами генератора тактовых импульсов (ГТИ), Устано- вочные S-входы триггеров сдвигового регистра соединены с блоком 3 синхронизации и служат для предварительной

установки генератора в исходное состояние перед началом проверки цифрового блока,

Блоа 3 синхронизации (фиг. 7) предназначен для формирования управ- ЛЯ1СЩИХ и синхронизирующих сигналов, необходимых дпя работы устройства в целом, В состав блока входят микропрограммное устройство управления, состоящее из регистра адреса и ПЗУ, блока двухвходовых элементов И, КБ-триг- гера, счетчика адреса блока 15 памяти , элементы коммутации и индикации, переключателей служит для .предварительного занесения в регистр адреса микрокоманды (РАМК) начального адреса микропрограммы, записанной в ПЗУ Верхнее положение переключателя соответствует подаче уровня логической единицы, нижнее положение - логического нуля. На вход синхронизации С1 РА1ЧК подается единичный потенциал, ин дциирующнй запись в регистр. Записанная информация является начальным адресом микропрограммы, считываемой из ПЗУ. Наличие свечения индикатора сведетельствует о том, что триггер на:кодится в единичном состоянии, т,е, выбрана область памяти, в которой хранятся команды условного перехода ил:я останова.

Считанная из ПЗУ микрокоманда сос- то:ит из двух полей - поля адреса следующей микрокоманды и поля управляющих сигналов. После адреса следующей микрокоманды имеет разрядность, равную 3.+ 1 , поле управляющих, сигналов яв.цяется пятнадцатиразрядным, причем двенадцатый У;, и тринадцатый У,, управляющие сигналы служат для управления счетчиком адреса, входящего в состав блока 3 синхронизации, четыр- надцатьй управляющий сигнал У управляет вентилем, разрешающим подачу так товых импульсов от блока 1 на вход С2 РМК. При .подаче тактового импульса на данный вход осуществляется запись адреса следующей микрокоманды в регистр. Кроме того, тактовые импульсы поступают на вторые входы элементов И 13, первые входы которых соединены с выходами ПЗУ, Этим обеспечивается формирование импульсных управляющих сигналов, что необходимо при считывании последовательности единичных сигналов. Запрещенное состояние вентиля индицируется узлом 26 индикации. Управляющий сигнал Уо подключей к 16 коммутации и является источником синхронизирующих сигналов для счетчика 8 с переменным модулем счета. Высокий потенциал на управляющем входе 17 соответствует подаче синхроимпульсов на тактов ьй вход счетчика 8, низкий потенциал обеспечивает подачу псевдослучайной последовательности от генератора 2 на синхровход счетчика 8,

Управляющий сигнал УО блока 3 синхронизации предназначен для сброса в ноль триггера останова в режиме выполнения микропрограмм. Синхросигналы У) -УО предназначены соответственно для синхронизации первого регистра 6, синхронизации генератора 2 установки начального состояния блока 2,

увеличения на единицу счетчика 4, ин- 2о первого триггера и является синхро25

30

35

крементации счетчика 9, синхронизации регистра 11, сброса в ноль регистров М и 14, синхронизации блока 12, управления чтением/записью блока 15 памяти, синхронизации второго регистра 7,

Счетчик 4 предназначен для формирования сигнала останова для блока 3 синхронизации при окончании прохождения теста. Информация о длине тестовой последовательности заносится от блока 5 путем установки соответствующего кода на информационных входах счетчика и установки режима занесения на входах S и Sj..

Влок 5 представляет собой набор двухпозиционных переключателей, а также формирователь 9 импульса сброса блока.

Первый и второй регистры 6 и 7 предназначены длл подачи константных логических значений на входы счетчика 8. Сигналы, записанные в регистры, содержат информацию о входах/выходах проверяемой схемы, а также о подмножествах множества входов объекта контроля. Аппаратная реализация регистров может быть вьтолнена с использованием интегральных микросхем К 155 ИР1.3.

Счетчик 8 (фиг. 6) содержит m DV- триггеров -с управляющими входами, (ia-l ) элементов ИЛИ и (m-l) элементов 2-2И-И11И, причем инверсные выходы триггеров соединены с их информацион- gg ными входами, V-входы триггеров сое-, динены между собой и представляют собой разрешающий вход счетчика с переменным модулем счета, кроме того.

40

45

50

входом счетчика с переменным мэдулем счета, R- и З-входы триггеров образу ют группу входов блока 8, выходами которого являются прямые выходы D- триггеров.

Совместно с друп-гми блоками уст- -ройства счетчкк 8 реализует заданные режимы работы:

с эталонными статистическими характе ристиками (псевдослучайные последова тельности) .

Совокупность структурных компонен тов счетчика 8 и регистры 6 и 7 позволяют реализовать вьшеупомянутые типы последовательностей на заданном множестве входов объекта контроля, что приводит к сокращению общего вре мени тестирования.

Счетчик 8 функционирует следующим образом. Если на S- и R-входах триггеров каждого из разрядов отсутствую единичные сигналы с выходов регистров 6 и 7, то элементы ИЛИ, входы ко торых соединены с S- и R-входами триггеров, будут формировать нулевой логический уровень, который разрешает прохождение сигнала с выхода пре- дьиущего триггера на сикхровход поуправляющие R- и S-входы соответствующих триггеров, кроме т-го, являются вxoдa соответствующих элементов ИЛИ, выходы которых являются управляющими входами элементов 2-2И-КПИ, выход каж,цого из которых, кроме (m-l)-ro, соединен с синкронизиру- кяцим входом последующего триггера и

вторым информационным входом последующего элемента 2-2И-ИЛИ, а выход (m-l)-ro элемента 2-2И-ИЛИ соединен с синхронизирующим входом т-го триггера, причем пря1-ые выходы D-т.риггеров, кроме и-го, подключены к первым информационным входам элемента 2-2И- ИШ, кроме того, второй информационный вход первого элемента 2-2И-Р1ТТИ соединен с синхронизирующим входе:.

5

0

5

g

0

5

0

входом счетчика с переменным мэдулем счета, R- и З-входы триггеров образуют группу входов блока 8, выходами которого являются прямые выходы D- триггеров.

Совместно с друп-гми блоками уст- -ройства счетчкк 8 реализует заданные режимы работы:

с эталонными статистическими характеристиками (псевдослучайные последовательности) .

Совокупность структурных компонентов счетчика 8 и регистры 6 и 7 позволяют реализовать вьшеупомянутые типы последовательностей на заданном множестве входов объекта контроля, что приводит к сокращению общего времени тестирования.

Счетчик 8 функционирует следующим образом. Если на S- и R-входах триггеров каждого из разрядов отсутствуют единичные сигналы с выходов регистров 6 и 7, то элементы ИЛИ, входы которых соединены с S- и R-входами триггеров, будут формировать нулевой логический уровень, который разрешает прохождение сигнала с выхода пре- дьиущего триггера на сикхровход последук)1цего через соответствующий вход г|електо ра, А так как триггеры счетчи- |а 8 вкгаочаьм по схеме со счетным уходом, то при подаче на их V-входы логической единицы,-.блок 8 представля eiT собой га-разрядный двоичный счет- Чик. Еа1И же из,регистров 6 или 7 на с|дин из управляющих входов, некоторого триггера и гру1шы триггеров счет- икa 8 поступает уровень логической единицы, то последние устанавливаются в соответствующее состояние О рл И 1, а соответствующие элементы 1Ш (}юрмиру1от управляющие сигналы, 1 :оторые позволяют исключить данные 1|риггеры из цепочки последовательнос- ifH соединенных элементов памяти счет- 8, При этом образуется счетчик (1 коэффициентом пересчета . где 1. - количество константных значений на гзыходе счетчика с переменным модулем счета.

При включении режима псевдослучайной генерации на синхронизирующий вход блока 8 через узел 16 подается сигнал от генератора 2 псевдослучайных чисел, а на разрешающий вход - синхроимпульсы У,{. При этом в ячейках памяти счетчика 8 осуществляется сложение по модулю два хранимой в цанный момент времени информации и информацииj{ поступающей из предыдущего разряда цепочки последовательно .-соединенных триггеров, что позволяет фop иpoвaть .на .соответствующих выходах устройства псевдослучайные последовательности.

Счет,чик 9 предназначен для форми- рованш функций счетаj подаваемых

на входы мультиплексора 10 и.группы 13 элементов И, Счетчик работает в. двух режимах - режим параллельной записи информации с входов A/i,,.,,Ant . и режим инкрементагщи. Выбор режима осуществляется подачей соответствующего логического уровня на вход счетчика от блока 5 задания исходных данных. Импульсы сложения формируютс блоком 3 синхроннаадиио

Третий регистр I1 предназначен для записи информации с выхода объекта контрсщя или произвольно выбран- ной точки комбинационной схемы с помощью щупа. Информация записывается при поступлении на С-вход регистра 11 и fflyльca сдвига от блока 3. Сброс регистра осуществляется подачей со

О

О

5

0

5

ответствуюпего импульса на вход R установки регистра в ноль.

Элемент И 12 предназначен для синхронной передачи информации с выхода комбинационной схемы на входы группы 13 элементов И. Элемент 12 представляет собой стандартный элемент булевой алгебры. .

Группа 13 элементов.И содержит .т двухвходовьк элементов, к первым входам .которых подсоединены выходы двоичного счетчика 9, а вторые входы - к выходу элемента И 12 для подачи синхронизиругацего сигнала в ,соответствующий момент времени. i

Элементы индикации, которые могут быть установлены на триггерах 14, необходимы для визуального считывания информации обслуживающим персоналом с целью формирования требуемых воздействий с помощью блока 3 синхронизации и блока 5 задания исходных данных.

Блок 15 необходим для накопления информации о подмножествах входов тестируемой схемы, влияющих на переключение заданной точки или выхода кбм- бинационной части проверяемой схемы. Необходимая информация из блока 15 в соответствующий момент времени извлекается и помещается в выбранный регистр 6 или 7. Адресные входы блока 15 соединены с выходами счетчика адреса блока 3, один из управляющих сигналов которого формирует строб записи или логический уровень чтения ОЗУ.

Устройство работает следующим образом.

Информация о входах/выходах контролируемого устройства (логическая единица - вход, логический ноль - выход) набирается на переключателях блока 5. Упомянутые выходы соединены

с информационными входами

двоичного счетчика 9, Соответствующим переключателем блока 5 (второй выход четвертой группы выходов), соединенным с входом S задания режима работы блока 9, устанавливается режим параллельной записи. При этом двоичный счетчик выполняет функцию конвейерное го регистра, запись в который осуществляется путем подачи на синхровход импульса от блока 3 синхронизации.

Регистры 11 и 14 устанавливаются в ноль импульсом сброса, подаваемым от блока. 3 синхронизации. После этот

го вход блока 11 подключается к шине питания +5 В для создания на вхое регистра П сдвига уровня логичес кой единицы. Подачей синхроимпульса . данная информация записывается в первый триггер блока 11..

От блока 3 на вход элемента И 12 подается синхронизирзтощий импульс, которьй совместно с выходным сигналом Q мультиплексора Ю (логическая единица) позволяет передать информацию через группу 13 элементов И с выходов блока 9 на входы группу триггеров 14. При этом передаваемьй код поступает tS на S-входы триггеров группы, что позволяет осуществить необходимую перезапись (фиг. 4).

Блок 3 сигналом У устанавливает счетчик адреса блока 15 памяти в ну- 20 евое состояние, после чего на вход Чтение-Запись блока 15 поступает строб записи Уд , который инициирует запись инверсной информации с выходов регистра 14 в нулевую ячейку памяти. 25 Передача, инверсной информации необхоима для того, чтобы информаия о вхоах/выходах,записанная в первый или второй сдвиговые регистры 6 или 7 со- тветственно, дозволяла исключать из 30 структуры счетчика 8 триггеры, выходы которых подают на выходы объекта контроля. Отключение соответствующего триггера осуществляется уровнем логической единицы, что обусловлено кон- „ струкцией счетчика 8 с переменным мо- дулем счета, исходное же задание информации о входах/выходах является инверсным.

Цель описанных действий - передача Q информации о входах/выходах в регистр 6 или 7 для организядии исчерпывающего перебора кодовых комбинаций на вхоах проверяемой схемы. Соответствую- щая микропрограмма записывается в д ЗУ в: виде последовательности управляющих сигналов. Структура считываемой микрокоманды содержит поле адреса следующей микрокоманды DO ...,DQ и поле управляющих сигналов о Х,.еп Для обращения к данной микропрограмме на узле 27 блока 3 синхронизации набирается ее стартовый адрес (в данном случае - нулевой), что приводит к параллельному занесению инфор- мации, заданной на переключателях в регистр адреса микрокоманды и установке триггера условия останова в нулевое состояние. При этом индикатор

25 выключается. Нулевая микрокоманда разрешает прохождение импульсов синхронизации от блока 1 тактовых импульсов через элемент И 12 на вход С2 регистра адреса микрокоманды (сигнал У,) . Поле управляющих сигналов данной микрокоманды содержит сигналы управления УБ, УГ, а. У, которые позволяют осуществить запись информации о входах/выходах тестируемой схемы в счетчик 9, сбросить в ноль регистр 11 и группу триггеров 14, занести нулевую комбинацию в счетчик адреса блока 15 памяти соответственно. После выполнения нулевой микрокоманды осуществляется безусловный переход к выполнению микрокоманды, адрес которой задан в поле DO ,. „. ,D-, В данном случае осуществляется переход к первой микрокоманде, содержащей управляющие сигналы У - з апись логической единицы в нулевой триггер регистра 1 1, У - разрешение синхронизации. Далее осуществляется переход к микрокоманде с адресом 2. При выполнении этой микрокоманды управляющий сигнал У синхронизирует блок 12 fтo приводит К записи информации о входах/выходах от блока 9 в триггеры

14через группу 13 элементов И. Микрокоманда, записанная по третьему адресу, формирует строб записи блока 15 памяти. Четвертая микрокоманда формирует сигнал У -синхронизации рё- .гистра 6 сдвига с целью перезалиси информации из нулевой ячейки блока

15памяти. ТГри этом лредполагается, что на входы задания режима работы регистра 6 от блока 5 задания исходных данных подана комбинация логических сигналов, содержащая информацию

о режиме параллельной записи в регистр. Микропрограмма завершается выполнением пятой микрокоманды, содержащей управляющие сигналы У , У4 , УГ, что позволяет установить начальное состояние генератора 2 псевдослу чайных чисел, занести информацию о длине тестовой последовательности с выходов блока 5 задания исходных данных в счетчик 4 длины теста, сбросить в ноль регистр 11 и триггеры 14. После этого осуществляется переход к микрокоманде с адресом 6, не содержащим управляющих сигналов, т.е. вьптолняется команда Останов. Нулевой логический уровень (сигнал У,) отключает генератор тактовых импуль

фон и работа устройства прекращается, 1)авертение выполнения микропрограммы фоировождается В1шючением индикато- lU 26.

: Кроме описанной выше микропрограм- №1 в ПЗУ содержится другая микропро- рамна, позволяющий подобным образом -Мнести необходимую информацию во 1зторой регистр 7 сдвига. Выполнение микропрограммы предполагается сразу же после выполнения первой мик- (Юпрограммы, Останов после выполнения йервой микропрограммы обусловлен не- Ьбходимостью смены исходных данных, Йредиазначенных для записи в регистр J7 сдвига. Данная микропрограмма рас- |1олагается с седьмого по одиннадца- fbm адреса ПЯУ. Двенадцатая ячейка |ТЗУ содержит команду Останов, ана- |1огичную рассмотренной, : После выполнения указанных мик- 1опрогр.амм переключениями блока 5 устанавливается режим хранения реги- тров 6 и 7 сдвига,-режим счета счет ика 9. Уровень на управляющем вхо- |де узла 16 устанавливается в единичное значениеJ что соответствует заданию режима счета счетчика, 8 с переменным модулем счета. Вход третье- то регистра i1 сдвига .соединяется с заданной точкой объекта контроля, ютносительно которой необходимо по- Устроить вектор-строку двоичных цифр, ;единичные сигналы в которой будут ;соответствовать входам схемы, влия- :ющим на переключение данной точки. Микропрограмма перебора кодовых комбинаций на входах объекта контроля начинается с гтринадцатого адреса. По этому адресу считьшаются управляющие сигналы ., Уб, V 1- По сигналу У осуществляется инкремен- тация счетчика 4, сигнал У является сигналом записи выходной информа- ции объекта контроля в регистр 11, По сигналу Ун1 осуществляется добавление, единицы в счетчик 8 с перем енным модулем счета, Поле адреса следующей микрокоманды содержит адрес текущей микрокоманды, что обуславливает выполнение перечисленных операций в течение времени, необходимого для перебора всех- комбинаций на входах схемы. При переполнении счетчика 4 длин теста сигнал Останов поступает на 5--.вход триггера останова и устанавливает его в единичное состояние. При этом очередная команда считывается и

0

5

0

121

25 дд 55

30

35

40

50

10

ячейки ПЗУ с адресом + В (В - тринадцатая ячейка). Эта команда позволяет осуществить условный переход к микрокоманде с адресом 14, и, кроме того, сигналом УО установить триггер останова в нулевое состояние. Микрокоманда с адресом 14 служит для увеличения на единицу содержимого счетчика 9 (сигнал ) и осуществления перехода к микрокоманде с адресом 15, Последняя, сигналами У/) и У осуществляет инкрементацию счетчика 4 и синхронизацию блока 12 с целью формирования разрещающего импульса для передачи содержимого блока 9 в регги стр 14, после чего осуществляется переход к четырнадцатой микрокоманде. Эти две микрокоманды повторяются в цикле до тех пор, пока счетчик 4 длины теста не переполнится, после чего происходит установка триггера останова блока 3 синхронизации в единичное состояние сигналом переполнения и переход к микрокоманде; с адресом (С - пятнадцатая ячейка). Данная микрокоманда сбрасывает триггер останова в ноль и осуществляет условный переход к микрокоманде с адресом 16, которая необходима для наращивания содержимого регистра адреса блока 15 (55г УЧЬ) с целью записи сформированной вектор-строки в последующую свободную ячейку памяти блока 15. Семнадцатая микрокоманда формирует строб записи ОЗУ и осуществляет переход к микрокоманде останова 18.

При н еобходимости сформировать другие векторы (для других точек схемы) необходимо осуществить nepeKOi iy- тацию входа третьего регистра 11 сдвига и повторно обратиться к микропрограмме, расположенной начиная с тринадцатого адреса ПЗУ.

После окончания формирования всех заданных строк можно перейти к режиму тестирования объектов контроля. Микропрограмма тестирования расположена, начиная с девятнадцатого адреса ПЗУ, Предварительно устанавливается режим параллельной записи регистра 6, информация о длине теста заносится в блок 4, Информация о длине теста для выбранной точки (или выхода схемы) может быть определена оператором при построении соответствующей вектор- строки. При этом необходимо двоичную

комбинацию считать с индикаторов ре- гистра 14.

Обращение к девятнадцатой микрокоманде ПЗУ позволяет осуществить ус- с тановку нулевого кода в счетчик адреса блока 15 (сигнал Хг. перейти к выполнению двадцатой команды. Эта микрокоманда формирует импульс записи необходимой информации в счетчик 4 10 длины теста и.прибавление единицы в счетчик адреса блока 15. Микрокоманда, расположенная по адресу 21, необходимая для формирования сигнала записи в один из регистров 6 или 7 (например,15 регистр 6) и перехода к микрокоманде 22 останова. Это необходимо для установки режимов счета счетчизка 4 и

режима хранения регистра 6 сдвига. После этого осуществляется передача 20 управления в двадцать третью ячейку

ПЗУ, управляющие сигналы в которой У4 и У предназначены для инкремен- тации счетчиков 4 и 8. Двадцать третья команда А повторяется до тех пор, 25

пока не -произойдет переполнение счетчика 4 и не осуществится условный переход к команде останова с адресом 2({,+А.При этом тестирование заданной

точки, или выхода схемы завершается. 30 Для продолжения режима тестирования других точек схемы необходимо установить нужные режимы работы счетчика 4 и регистра 6 и обратиться к двадцатой микрокоманде ПЗУ. 35

Формула изобретения

Устройство для формирования тестов, содержащее генератор тактовых 40 импульсов, генератор псе-вдослучайных чисел, блок синхронизации, счетчик длины теста, блок задания исходных данных, два регистра сдвига, первьй счетчик, причем выход генератора так-45 товых импульсов соединен с тактовым входом блока синхронизации, первая группа вьпсодов блока задания исходных данных соединена с информационными входами первого регистра сдвига, рая и третья группы выходов блока задания исходных данных соединены соответственно с информационными входами второго регистра сдвига и счетчика длины теста, выход переполнения кото- рого соединен с входом останова блока синхронизации, первый выход которого соединен с синхровходом первого ре- гистрй сдвига, второй, третий и четвертый выходы блока синхронизации соединены с установочным Влодом н синхровходом генератора псевдослучайных чисел и счетным входом счетчика дпины теста соответственно, информационные входы которого соединены с

четвертой группой выходов блока задания исходных данных, отличающее с я тем, что, с целью повьшуе- ния быстродействия, в устройство введены второй счетчик, мультиплексор, третий регистр сдвига, элемент И, группа элементов И, группа триггеров, блок памяти и узел коммутации, причем пятая группа выходов блока задания исходных данных соединена с группой информационных входов второго счетчика, а шестая группа выходов блока задания исходных данных соединена с входами установки режима и сброса второго счетчика, вход прямого счета которого соединен с пятым выходом блока синхронизации, кроме того, группа т-разрядных выходов второго счетчика (где m - разрядность тестового слова устройства) подключена к первой группе управляющих входов мультиплексора, группа информационных входов которого соединена с группой разрядных выходов третьего сдвигового регистра, выход второго счетчгжа () соединен с первым входом i-ro элемента И группы элементов И, вторые входы которых соединены с выходом элемента

И, первый вход которого является выходом мультиплексора, а второй вход элемента И соединен с шестым выходом блока синхронизации, выходы эле ментов И группы соединены с входаКи установки соответствующих триггеров группы, входы сброса которых соединены с седьмым выходом блока синхронизации и входом сброса третьего регистра сдвига, выходы триггеров группы соединены с информационными входами блока памяти, группа адресных входов которого соединена с группой выходов блока синхронизации, выход генератора тактовых импульсов соединен с первым информационным входом узла коммутации, второй информационный вход которого соединен с выходом генератора псевдослучайных чисел, управляющий вход уэла коммутации соединен с первым вход ом задания режима работы устрой- . ства, первый и второй выходы узла коммутации соединены с разрешающим и счетным входами первого счетчика

соответственно, а выходы блока памя- ти соединень: с информационными входами первого и второго регистров сдвига, кроме того, восьмой выход блока синхронизации соединен с синхровходом второго регистра сдвига, девятьй выход блока синхронизации соединен с синхровходом третьего регистра сдвига, информационный вход третьего сдвигового регистра является вторым входом задания режима работы устрой OcmaH0S-. от d/rof a

JH от SnoKu 1

ства, а разрядные выходы первого счетчика являются выходами устройства, разрядные выходы первого регистра сдвига соединены с входами установки в нулевое состояние соответствующих разрядов первого счетчика, входы установки в единичное состояни которых соединены с соответствующими разрядными выходами второго регистра сдвига.

1г}раВдтщие CUZHQ/IH

К адресном шинам локй ч5

fuz.2

От SaoKtLS

OHI /Moisl OmfmaS

Urn iff КПЗ Bxoi

0Ht //iei(u3

От йомЗ

:m-j

От

и,г.5

«

1

I

Jff

7Г

X

.. Дн|

CpCiC CjCifCs

От ffloKa i1

9ll2,l

IB

KfflOKij 2

т

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования тестов | 1985 |

|

SU1297059A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-07—Публикация

1987-02-19—Подача