Изобретение относится к области цифровой магнитной записи.

Цель изобретения - упрощение устройства и расширение его функциональных возможностей за счет введения функции выделения данных.

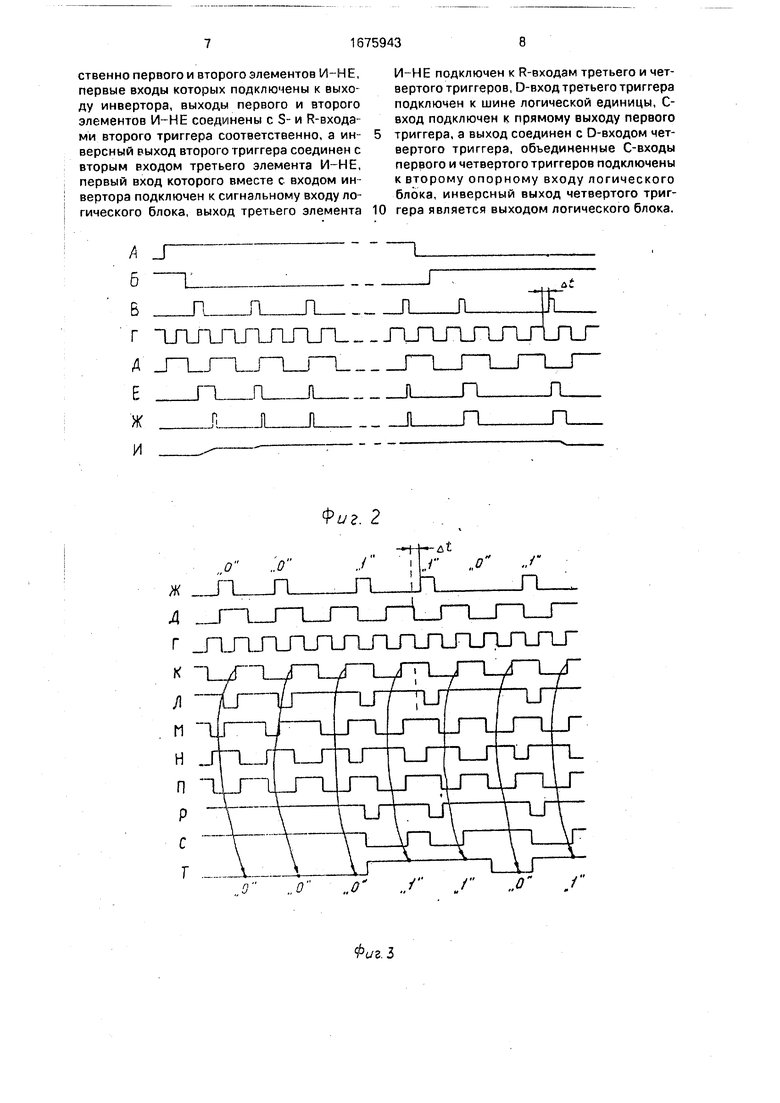

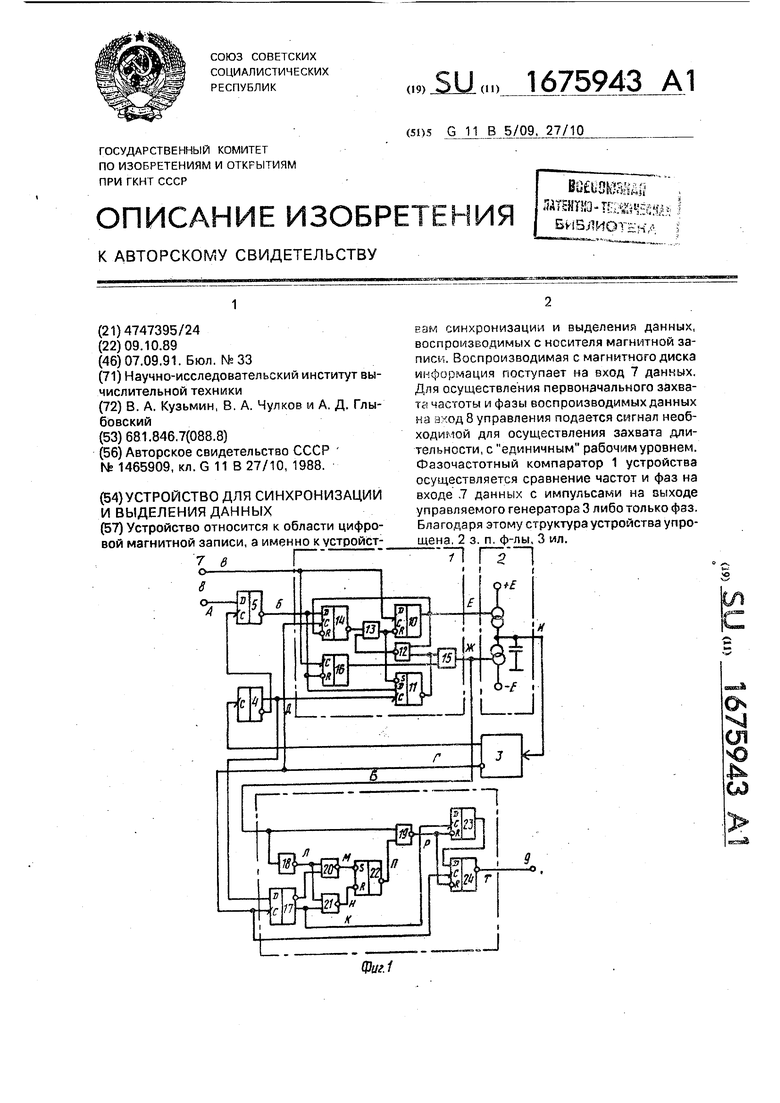

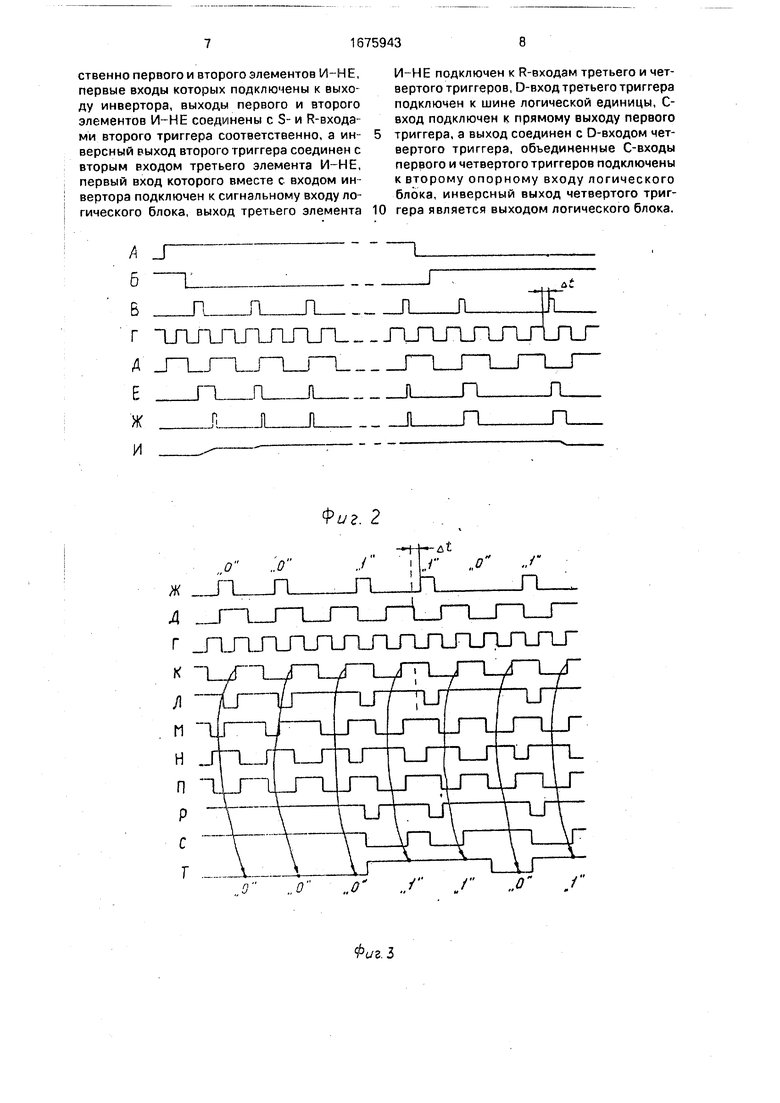

На фиг. 1 представлена схема устройства синхронизации и выделения данных; на фиг. 2 - временные диаграммы его работы; на фиг. 3 - временные диаграммы работы логического блока.

Для удобства описания линии связи на фиг. 1 и соответствующие им временные диаграммы на фиг. 2 и 3 обозначены одноименными буквами А...Т.

Устройство содержит фазочастотный компаратор 1, блок 2 интегрирования,управляемый генератор 3, делитель 4 частоты, триггер 5, логический блок 6. Имеются вход 7 данных, вход 8 управления и выход 9 данных,

Фазочастотный компаратор 1 содержит триггеры 10 и 11 с общим сбросом через элемент И-НЕ 12 и элемент И 13, триггер 14, элемент ИЛИ 15, и одновибратор 16, формирующий импульс с высоким рабочим уровнем. Длительность импульса одно- вибратора выбирается равной половине периода сигналов управляемого генератора.

Логический блок состоит из триггера 17, D- и С-входы которого являются соответственно первым и вторым опорными входами логического блока, инвертора 18, вход которого вместе с первым входом элемента И-НЕ 19 подключен к сигнальному входу логического блока, элементов И-НЕ 20 и 21 итриггеров 22-24, причем инеерсный выход триггера 24 является выходом логического блока.

Начальное установление синхронизма в устройстве осуществляется в поле синхронизации воспроизводимого массива данных, которое представляет собой последовательность нулей, т. е. регулярных импульсов с периодом, в два раза большим периода синхросигналов с выхода управляемого генератора 3. Для осуществления захвата на вход 8 управления подается сигнал необходимой длительности с единичным рабочим уровнем (фиг. 2,а).

При поступлении фронта очередного импульса с инверсного выхода делителя 4 частоты триггер 5 взводится и запрещает работу одновибратора 16, удерживает в сброшенном состоянии триггер 14. Триггер 10 взводится каждым импульсом сигнала (В) данных, а триггер 11 каждым импульсом сигнала (Д) с выхода делителя 4 частоты. Сброс обоих триггеров происходит через элементы И-НЕ 12 и И 13 после того, как они оба окажутся взведенными.

В этом режиме фазочастотный компаратор осуществляет частотное и фазовое

сравнение. В зависимости от разности фаз сравниваемых сигналов (В и Д на фиг. 2) он формирует либо на выходе триггера 10, либо на выходе триггера 11 импульсы длительностью, равной задержке между срав0 ниваемыми сигналами. Импул ьсы с выхода триггера 11 проходят через элемент ИЛИ 15 на выход фазочастотного компаратора. Импульсы (Е и Ж на фиг. 2) с выхода фазочастотного компаратора проводят к соот5 ветствующему приращению выходного напряжения (И) блока 2 интегрирования и коррекции частоты управляемого генератора 3 в направлении компенсации разности фаз, К моменту окончания сигнала А на

0 входе 8 управления в устройстве устанавливается синфазное состояние, при котором фронты сигналов (Д) обратной связи с выхода делителя частоты и входного сигнала (В) совпадают по времени.

5В режим слежения устройство переходит после окончания сигнала управления (А) и переключения триггера 5 в единичное состояние (фиг. 2,6), разрешая работу триггера 14, рдновибратора 16 и удерживает во

0 взведенном состоянии триггер 11. В этом режиме сигналы фазовой ошибки появляются на выходе фазочастотного компаратора только по приходу каждого входного импульса, благодаря этому он не реагирует

5 на частоту входных сигналов и способен работать с кодированным сигналом данных. Автоподстройка фазы сигналов генератора 3 осуществляется на основании сравнения длительностей импульсов заряда и разряда

0 с выхода фазочастотного компаратора 1. Длительность импульса заряда равна задержке между фронтом входного сигнала и фронтом синхросигнала с инверсного выхода управляемого генератора 3, а длитель5 ность импульса разряда фиксирована одновибратором и равна половине периода сигналов управляемого генератора 3. Если, например, очередной входной сиг-/ нал данных опаздывает на время At относи0 тельносвоей номинальной позиции (обозначенной пунктиром) позиции (фиг. 2,в), то на выходе одновибратора 16 появляется импульс фиксированной длительности, а на выходе триггера 10 - импульс меньшей

5 длительности (фиг. 2,е, ж). Эта пара импульсов, воздействуя на входы блока 2 интегрирования, приводит к понижению его выходного напряжения (фиг. 2и) и, следовательно, к понижению частоты выходных синхросигналов.

На фиг.З показаны временные диаграммы работы логического блока. На его сигнальный вход поступают импульсы (Ж) с второго выхода фазочастотного компаратора, равные по длительности половине периода сигналов управляемого генератора 3. На D-вход триггера 17, являющегося первым опорным входом логического блока, подаются импульсы (Д) с выхода делителя частоты. На С-вход этого триггера, являющийся вторым опорным входом логического блока, поступают импульсы с инверсного выхода управляемого генератора 3. Триггер 17 сдвигает импульсы с делителя 4 частоты на 1/4 периода, образуя так называемые окна данных (К), расположенные симметрично относительно номинальных позиций сигналов данных (их фронтов)(Ж). В отсутствии сигналов данных оба вентиля И-НЕ 20 и 21 открыты, поэтому выходной сигнал (П) триггера 22 повторяет сигнал (К) с выхода триггера 17.

Значение цифрового символа данных, переносимого поступившим на сигнальный вход логического блока импульсов МФМ-ко- да, зависит от того, на какую полочку: низкого или высокого напряжения сигнала. окна данных приходится фронт этого импульса. Вентили И-НЕ 20 и 21 и инвертор 18 служат для того, чтобы при выделении символа учитывался только фронт сигнала, а его длительность не играла роли. Это достигается за счет того, что во время действия импульса данных состояние триггера 22 (П) не может измениться. Таким образом, если фронт импульса данных пришелся на низкую нулевую полочку сигнала окна (П), то на выходе элемента ИНЕ 19 импульс не появится, т. е. фиксируется нулевой символ. Если же фронт импульса данных (Ж) приходится на высокую единичную полочку сигнала окна (К и П), то на выходе элемента И-НЕ 19 формируется нулевой импульс (Р) с длительностью, равной длительности импульса данных (Ж). Этот импульс сбрасывает оба триггера 23 и 24, т, е. на выходе данных начинает формироваться импульс с высоким единичным уровнем. Фронт очередного сигнала окна (К) вновь взводит триггер 23, и если в следующем окна не появится импульс данных, то по его окончании (по прошествии периода синхросигнала Г) вернется в исходное состояние и триггер 24.

Если же идут сплошные две, как показано на фиг. 3, или более единицы, то на выходе 9 данных удерживается уровень логической 1. Таким образом входные МФМ данные логического блока .преобразуются в БВН данные.

Формула изобретения

1.Устройство для синхронизации и выделения данных, содержащее последовательно соединенные фазочастотный

компаратор, блок интегрирования, управляемый генератор и делитель частоты,прямым выходом подключенный к первому опорному входу фазочастотного компаратора, а также триггер, у которого D-вход сое0 динен с шиной управляющего сигнала, при этом сигнальный вход фазочастотного компаратора соединен с входной шиной данных, отличающееся тем, что, с целью упрощения устройства и расширения функ5 циональных возможностей за счет введения функции выделения данных, в него введен логический блок, первый опорный вход которого подключен к выходу делителя частоты, второй опорный вход - с опор0 мым входом фазочастотного компаратора и с инверсным выходом управляемого генера- тора, сигнальный вход - к второму выходу фазочастотного компаратора, а выход - к выходной шине выделения данных, при

5 этом С-вход триггера подключен к инверсному выходу делителя частоты, а выход - к управляющему входу, фазочастотного компаратора.

2.Устройство поп. 1,отличающее- 0 с я тем. что фазочастотный компаратор выполнен в виде первого и второго триггеров, D-входы которых вместе с входом сброса одновибратора подключены к управляющему входу, а С-входы служат соответственно

5 вторым и первым опорными входами фазочастотного компаратора, а также третьего триггера, С-вход которого соединен с входом запуска одновибратора и сигнальным входом фазочастотного компаратора, эле0 ментов И, И-НЕ, ИЛИ, причем инверсный выход первого триггера через элемент VI, другой вход которого соединен с выходом элемента И-НЕ, подключен к S-входу второго триггера R-входу третьего триггера, у

5 которого D-вход присоединен к шине логической единицы, а выход к первому выходу фазочастотного компаратора, R-входу первого триггера и первому входу элемента И-НЕ, первый вход элемента ИЛИ подключен

0 к выходу одновибратора, его второй вход вместе с вторым входом элемента И-НЕ подключен к инверсному выходу второго триггера, а выход присоединен к второму выходу фазочастотного компаратора.

53. Устройство поп. 1,отличающеес я тем. что логический блок состоит из первого триггера, D-вход которого является первым опорным входом логического блока, инверсный и прямой выходы первого триггера соединены с вторыми входами соответственно первого и второго элементов И-НЕ, первые входы которых подключены к выходу инвертора, выходы первого и второго элементов И-НЕ соединены с S- и R-входа- ми второго триггера соответственно, а инверсный выход второго триггера соединен с вторым входом третьего элемента И-НЕ, первый вход которого вместе с входом инвертора подключен к сигнальному входу логического блока, выход третьего элемента

0

И-НЕ подключен к R-входам третьего и четвертого триггеров, D-вход третьего триггера подключен к шине логической единицы, С- вход подключен к прямому выходу первого триггера, а выход соединен с D-входом четвертого триггера, объединенные С-входы первого и четвертого триггеров подключены к второму опорному входу логического блока, инверсный выход четвертого триггера является выходом логического блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой синхронизации для дискового накопителя цифровых данных | 1988 |

|

SU1615799A1 |

| Устройство для измерения индикатрис рассеяния света | 1990 |

|

SU1723456A1 |

| Устройство для определения триботехнологических свойств материалов | 1990 |

|

SU1795351A1 |

| Устройство для контроля фазочастотных характеристик четырехполюсников | 1989 |

|

SU1758600A1 |

| Устройство для учета объектов | 1990 |

|

SU1815662A1 |

| УРОВНЕМЕР | 2004 |

|

RU2256158C1 |

| Дуплексная система передачи данных с временным разделением сигналов | 1990 |

|

SU1782336A3 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Устройство для измерения индикатрис рассеяния света | 1986 |

|

SU1402862A1 |

Устройство относится к области цифровой магнитной записи, а именно к устройст7 вГ рам синхронизации и выделений данных, воспроизводимых с носителя магнитной записи. Воспроизводимая с магнитного диска информация поступает на вход 7 данных. Для осуществления первоначального захвата частоты и фазы воспроизводимых данных на вход 8 управления подается сигнал необходимой для осуществления захвата длительности, с единичным рабочим уровнем, Фазочастотный компаратор 1 устройства осуществляется сравнение частот и фаз на входе .7 данных с импульсами на выходе управляемого генератора 3 либо только фаз. Благодаря этому структура устройства упрощена. 2 з. п. ф-лы, 3 ил. Л ГТП ЕЕГ75&. J

$иг. 2

о

.о

г jnjiJiJi-rLrmjiJT

к /| и 11Г

..о „о Ж J f

JlJ4Jnjnj Lrl n r

П

П

| Устройство для синхронизации воспроизведения информации | 1987 |

|

SU1465909A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-09-07—Публикация

1989-10-09—Подача