Изобретение относится к технике накопления цифровых данных, в частности к устройствам для синхронизации при записи и воспроизведении данных в накопителях на магнитных дисках.

Цель изобретения- - повышение быстродействия за счет уменьшения времени установления синхронизма.

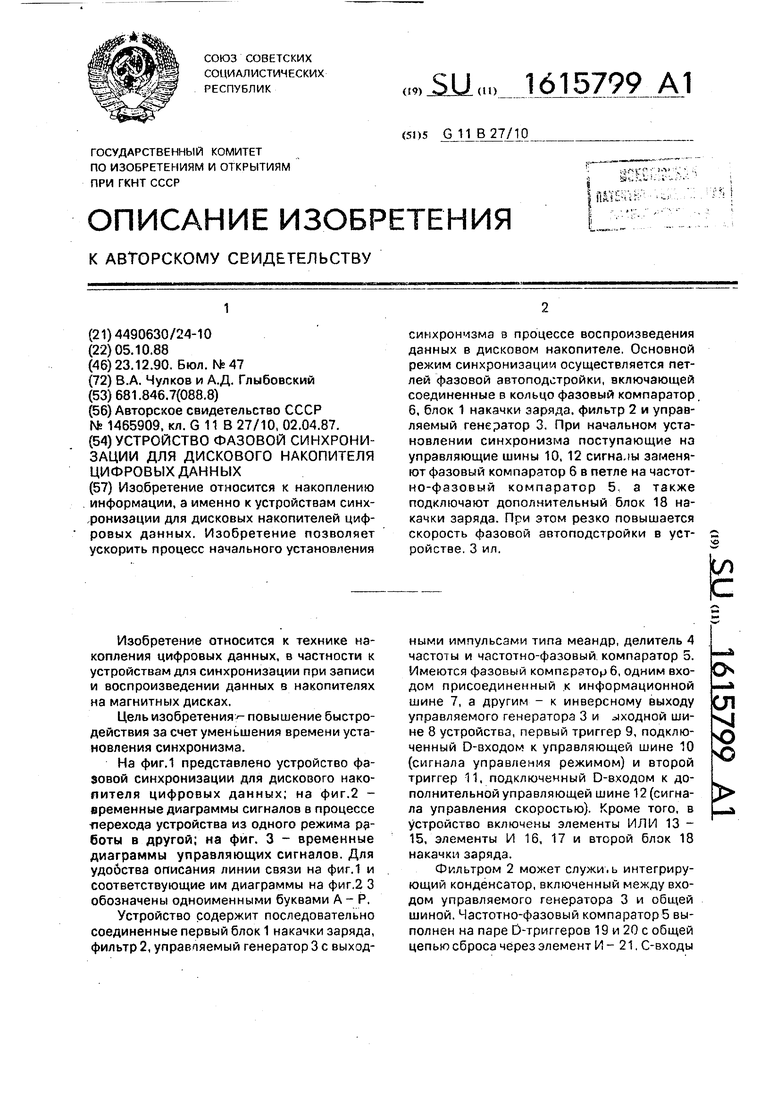

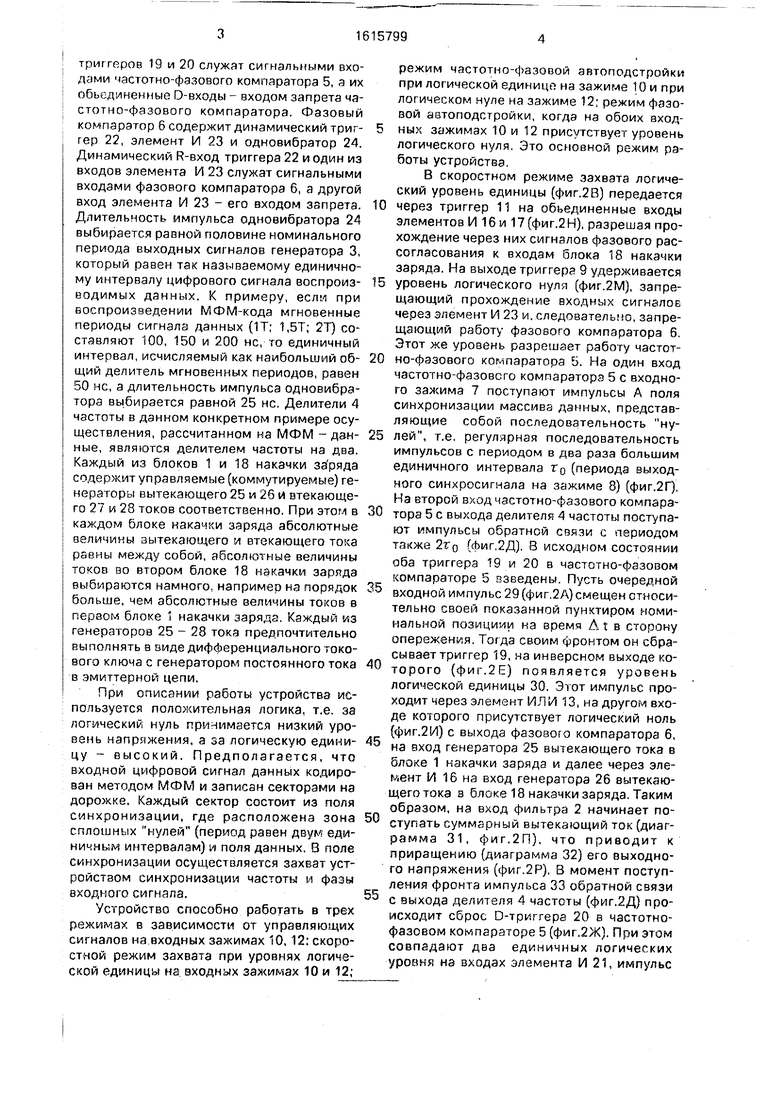

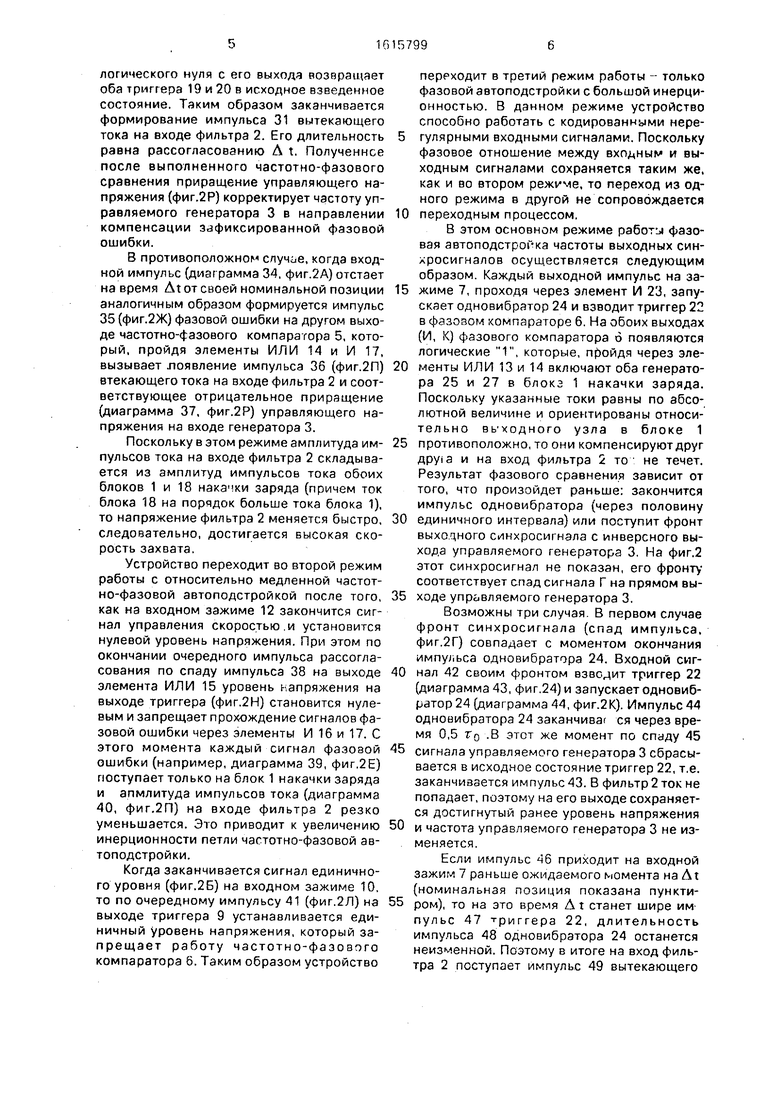

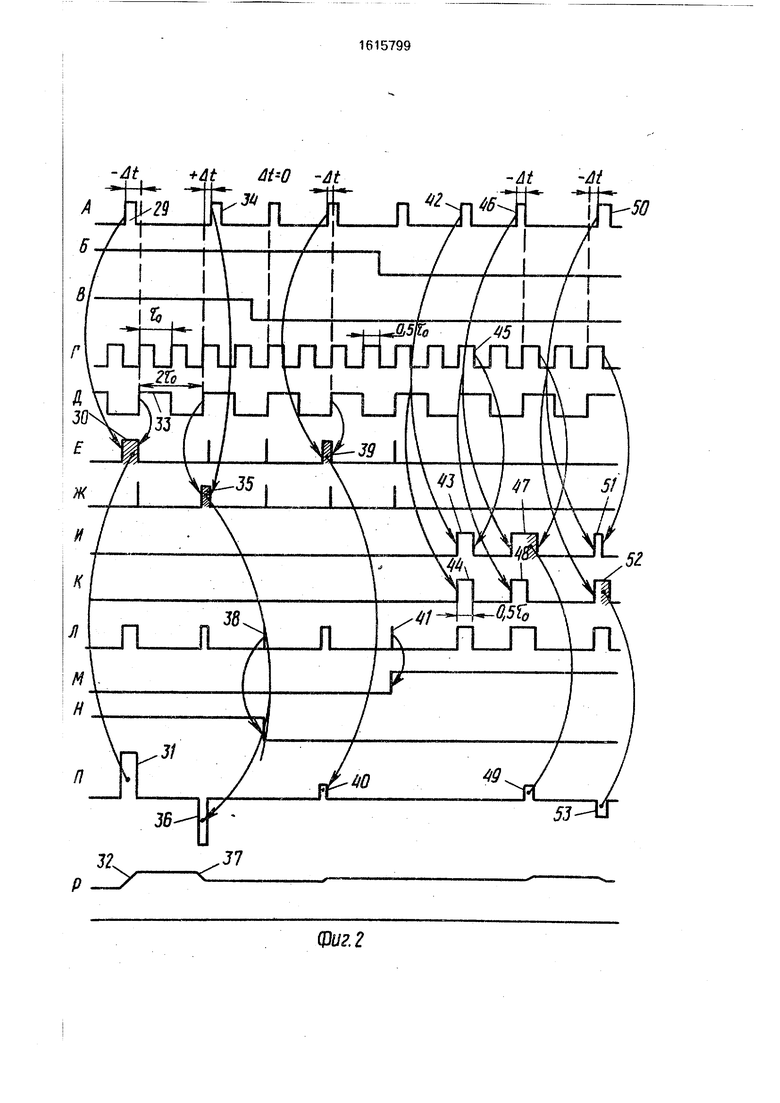

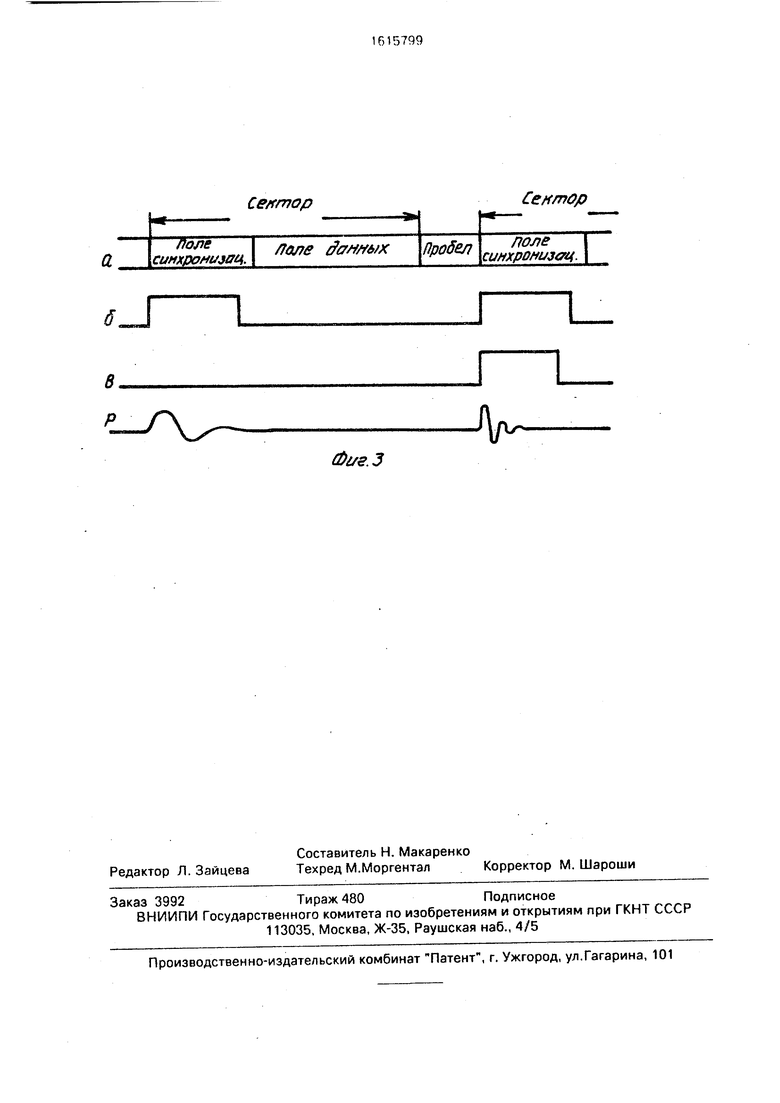

На фиг.1 представлено устройство фазовой синхронизации для дискового накопителя цифровых данных; на фиг.2 - временные диаграммы сигналов в процессе f epexoдa устройства из одного режима боты в другой; на фиг. 3 - временные диаграммы управляющих сигналов. Для удобства описания линии связи на фиг.1 и соответствующие им диаграммы на фиг.2 3 обозначены одноименными буквами А- Р.

Устройство содержит последовательно соединенные первый блок 1 накачки заряда, фильтр 2, управляемый генератор 3 с выходными импульсами типа меандр, делитель 4 частоты и частотно-фазовый, компаратор 5. Имеются фазовый компгрзтор 6, одним входом присоединенный .к информационной шине 7, а другим - к инверсному выходу управляемого генератора 3 и .(ходной шине 8 устройства, первый триггер 9, подключенный D-входом к управляющей шине 10 (сигнала управления режимом) и второй триггер 11, подключенный D-входом к дополнительной управляющей шине 12 (сигнала управления скоростью). Кроме того, в устройство включены элементы ИЛИ 13 - 15, элементы И 16, 17 и второй блок 18 накачки заряда.

Фильтром 2 может служи,ь интегрирующий конденсатор, включенный между входом управляемого генератора 3 и общей шиной. Частотно-фазовый компаратор 5 выполнен на паре D-триггеров 19 и 20 с общей цепью сброса через элемент И - 21. С-входы

О

сл VI ю

ю

триггеров 19 и 20 служат сигнальными входами частотно-фазового компаратора 5, а их обьединенные D-входы - входом запрета частотно-фазового компаратора. Фазовый компаратор 6 содержит динамический триггер 22, элемент И 23 и одновибратор 24. Динамический R-вход триггера 22 и один из входов элемента И 23 служат сигнальными входами фазового компаратора б, а другой вход элемента И 23 - его входом запрета. Длительность импульса одновибратора 2-4 выбирается равной половине номинального периода выходных сигналов генератора 3, который равен так называемому единичному интервалу цифрового сигнала воспроизводимых данных. К примеру, если при воспроизведении МФМ-кода мгновенные периоды сигнала данных (IT; 1,5Т; 2Т) составляют 100, 150 и 200 НС, то единичный интервал, исчисляемый как наибольший общий делитель мгновенных периодов, равен 50 НС, а длительность импульса одновибратора вы,бирается равной 25 не. Делители 4 частоты в данном конкретном примере осуществления, рассчитанном на МФМ -данные, являются делителем частоты на два. Каждый из блоков 1 и 18 накачки за ряда содержит управляемые (коммутируемые) генераторы вытекающего 25 и 26 и втекающего 27 и 28 токов соответственно. При этом в каждом блоке накачки заряда абсолютные величины вытекающего и втекающего тока равны между собой, абсолютные величины токов во втором блоке 18 накачки заркда выбираются намного, например на порядок больше, чем абсолютные величины токов в первом блоке 1 накачки заряда. Каждый из генераторов 25 - 28 тока предпочтительно выполнять в виде дифференциального токового ключа с генератором постоянного тока в эмиттерной цепи.

При описании работы устройства используется положительная логика, т.е. за логг/ ческий нуль принимается низкий уровень напряжения, а за логическую единицу - высокий. Предполагается, что входной цифровой сигнал данных кодирован методом МФМ и записан секторами на дорожке. Каждый сектор состоит из поля синхронизации, где расположена зона сплошных нулей (период равен двум единичным интервалам) и поля данных. В поле синхронизации осуществляется захват устройством синхронизации частоты и фазы входного сигнала.

Устройство способно работать в трех режимах в зависимости от управляющих сигналов на входных зажимах 10, 12: скоростной режим захвата при уровнях логической единицы на эходных зажимах 10 и 12;

режим частотно-фазовой автоподстройки при логической единице на зажиме 10 и при логическом нуле на зажиме 12; режим фазовой автоподстройки, когда на обоих вход- 5 ных зажимах 10 и 12 присутствует уровень логического нуля, Это основной режим работы устройства,

В скоростном режиме захвата логический уровень единицы (фиг.2В) передается 10 через триггер 11 на обьединенные входы элементов И 16 и 17 (фиг.2Н), разрешая прохождение через них сигналов фазового рассогласования к входам блока 18 накачки заряда. На выходе триггера 9 удерживается 15 уровень логического нуля (фиг.2М), запре- а(ающий прохождение входных сигналов через элемент И 23 и. следовательно, запрещающий работу фазового компаратора 6. Этот же уровень разрешает работу частот- 0 НС-фазового компаратора 5. На один вход частотно-фазового компараторз 5 с входного зажима 7 поступают импульсы А поля синхронизации массива данных, представляющие собой последовательность ну- 5 лей, т.е. регулярная последовательность импульсов с периодом в два раза большим единичного интервала TQ (периода выходного синхросигнала на зажиме 8) (фиг.2Г). На второй вход частотно-фазового компара- 0 тора 5 с выхода делителя 4 частоты поступают импульсы обратной связи с периодом также 2го (фиг,2Д). 8 исходном состоянии оба триггера 19 и 20 в частотно-фазовом компараторе 5 взведены. Пусть очередной входной импульс 29 (фиг.2А) смещен относительно своей показанной пунктиром номинальной позициии на время At в сторону опережения. Тогда своим фронтом он сбра- П триггер 19, на инверсном выходе ко- торого (фиг.2Е) появляется уровень логической единицы 30. Этот импульс проходит через элемент ИЛИ 13, на другом входе которого присутствует логический ноль (фиг.2И) с выхода фазового компаратора 6, на вход генератора 25 вытекающего тока в блоке 1 накачки заряда и далее через элемент И 16 на вход генератора 26 вытекающего тока в блоке 18 накачки заряда. Таким образом, на вход фильтра 2 начинает поступать суммарный вытекающий ток (диаграмма 31, фит.2П), что приводит к приращению (диаграмма 32) его выходного напряжения (фиг.2Р), В момент поступления фронта импульса 33 обратной связи с выхода делителя 4 частоты (фиг.2Д) происходит сброс D-триггера 20 в частотно- фазовом компараторе 5 (фиг.2Ж). При этом совпадают два единичных логических уровня на входах элемента И 21, импульс

логического нуля с его выхода возвращает оба триггера 19 и 20 в исходное взведенное состояние. Таким образом заканчивается формирование импульса 31 вытекающего тока на входе фильтра 2. Его длительность равна рассогласованию Д t. Полученное после выполненного частотно-фазового сравнения приращение управляющего напряжения (фиг.2Р) корректирует частоту управляемого генератора 3 в направлении компенсации зафиксированной фазовой ошибки.

В противоположном случае, когда входной импульс (диаграмма 34, фиг.2А) отстает на время At от своей номинальной позиции аналогичным образом формируется импульс 35 (фиг.2Ж) фазовой ошибки на другом выходе частотно-фазового компаратора 5, который, пройдя элементы ИЛИ 14 и И 17, вызывает лоявление импульса 36 (фиг.2П) втекающего тока на входе фильтра 2 и соответствующее отрицательное приращение (диаграмма 37, фиг.2Р) управляющего напряжения на входе генератора 3.

Поскольку в зтом режиме амплитуда импульсов тока на входе фильтра 2 складывается из амплитуд импульсов тока обоих блоков 1 и 18 накачки заряда (причем ток блока 18 на порядок больше тока блока 1), то напряжение фильтра 2 меняется быстро, следовательно, достигается высокая скорость захвата.

Устройство переходит во второй режим работы с относительно медленной частотно-фазовой автоподстройкой после того, как на входном зажиме 12 закончится сигнал управления скоростью.и установится нулевой уровень напряжения. При этом по окончании очередного импульса рассогласования по спаду импульса 38 на выходе элемента ИЛИ 15 уровень напряжения на выходе триггера (фиг.2Н) становится нулевым и запрещает )ждение сигналов фазовой ошибки через элементы И 16 и 17. С этого момента каждый сигнал фазовой ошибки (например, диаграмма 39, фиг.2Е) поступает только на блок 1 накачки заряда и апмлитуда импульсов тока (диаграмма 40, фиг.2П) на входе фильтра 2 резко уменьшается. Это приводит к увеличению инерционности петли частотно-фазовой автоподстройки.

Когда заканчивается сигнал единичного уровня (фиг.2Б) на входном зажиме 10, то по очередному импульсу 41 (фиг.2Л) на выходе триггера 9 устанавливается единичный уровень напряжения, который запрещает работу частотно-фазового компаратора б. Таким образом устройство

переходит в третий режим работы - только фазовой автоподстройки с большой инерционностью. В данном режиме устройство способно работать с кодированными нере- 5 гулярными входными сигналами. Поскольку фазовое отношение между входным и выходным сигналами сохраняется таким же. как и во втором режиме, то переход из одного режима в другой не сопровождается

10 переходным процессом.

В этом основном режиме работы фазовая автоподстройка частоты выходных синхросигналов осуществляется следующим образом. Каждый выходной импульс на за15 жиме 7, проходя через элемент И 23, запускает одновибратор 24 и взводит триггер 22 в фазовом компараторе 6. На обоих выходах (И, К) фазового компаратора 6 появляются логические 1, которые, пройдя через эле0 менты ИЛИ 13 и 14 включают оба генератора 25 и 27 в блокэ 1 накачки заряда. Поскольку указанные токи равны по абсолютной величине и ориентированы относительно выходного узла в блоке 1

5 противоположно, то они компенсируют друг дру1а и на вход фильтра 2 то; не течет. Результат фазового сравнения зависит от того, что произойдет раньше: закончится импульс одновибратора (через половину

0 единичного интервала) или поступит фронт выходного синхросигнала с инверсного выхода управляемого генератора 3. На фиг.2 этот синхросигнал не показан, его фронту соответствует спад сигнала Г на прямом вы5 ходе упрг вляемого генератора 3.

Возможны три случая. В первом случае фронт синхросигнала (спад импульса, фиг.2Г) совпадает с моментом окончания импульса одновибратора 24. Входной сиг0 нал 42 своим фронтом взводит триггер 22 (диаграмма 43, фиг.24) и запускает одновибратор 24 (диаграмма 44, фиг.2К). Импульс44 одноеибратора 24 заканчиваг ся через время 0,5 Го .В этот же момент по спаду 45

5 сигнала управляемого генератора 3 сбрасывается в исходное состояние триггер 22, т.е. заканчивается импульс 43. В фильтр2 ток не попадает, поэтому на его выходе сохраняется достигнутый ранее уровень напряжения

0 и частота управляемого генератора 3 не изменяется.

Если импульс ч6 приходит на входной зажим 7 раньше ожидаемого момента на At (номинальная позиция показана пункти5 ром), то на это время А t станет шире им- пульс 47 триггера 22, длительность импульса 48 одновибратора 24 останется неизменной. Поэтому в итоге на вход фильтра 2 поступает импульс 49 вытекающего

тока из блока 1 накачки заряда. Напряжение {фиг,2Р) на выходе фильтра 2 получает приращение и частота управляемого генератора 3 корректируется в направлении компенсации фазового рассогласования.

Совершенно аналогично работает устройство и в противоположном случае, когда очередной входной импульс 50 запаздывает относительно своей номинальной позиции на Д t. При этом импульс 51 триггера 22 оказывается по длительности меньшим, чем импульс 52 одновибратора 24, что приводит к появлению импульса 53 тока (фиг.2П) на входе фильтра 2. Напряжение на его выходе получает отрицательное приращение (фиг.2Р), частота управляемого генератора 3 корректируется в необходимом направлении.

Временные диаграммы (фиг.З) иллюстрируют эффект ускоренного установления синхронизма в устройстве за счет подключения второго блока 18 накачки заряда при поступлении сигнала управления сигнала управления скоростью (В) на входной зажим 12. В поле синхронизации сектора данных (фиг.ЗА) по сигналу Б управления режимом на входном зажиме 10 устройство переходит в режим частотно-фазового сравнения. при котором полоса захвата равна полосе удержания. Если сигнала управления скоро- стью при этом не поступает, то переходной процесс захвата,.о котором судят по напряжению на выходе фильтра 2 (фиг.ЗР), будет продолжительным. Если же сигнал В управления скорости поступил, то время переход- ного процесса резко сокращается.

Формула изобретения

Устройство фазовой синхронизации для дискового накопителя цифровых данных, содержащее последовательно соединенные первый блок накачки заряда, фильтр, управляемый генератор, делитель частоты и частотно-фазовый компаратор, а также фазовый компаратор, первый триггер, соединенный D-входом с управляющей шиной, второй триггер, информационную шину и

выходную шину, при этом фазовый компаратор выполнен в виде динамического триггера и одновибратора, выходы ко торых являются соответствующими выходами фазового компаратора, вход одновибратора соединен с одним входом динамического триггера, другой вход которого является одним входом фазового компаратора и подключен к выходной шине, отличающее- с я тем, что, с целью повышения быстродействия за счет уменьшения времени установления синхронизма, введены второй блок накачки заряда, подключенный выходом к выходу первого блока накачки заряда, три элемента ИЛИ, первый и второй элементы И, дополнительный элемент И в фазовом компараторе, соединенный выходом с одним входом динамического триггера, дополнительная управляющая шина, соединенная с D-входом второго триггера, при этом первый и второй элементы ИЛИ подключены одними входами к соответствующим выходам фазового компаратора, другими входами - к соответствующим выходам частотно-фазового компаратора, выход первого и выход второго элементов ИЛИ соединены с соответствующими входами первого блока накачки, с одними входами первого и второго элементов И и через третий элемент ИЛИ с С-входами первого триггера и второго триггера, выход которого соединен с другими входами первого и второго элементов И, выходы которых подключены к соответствующим входам второго блока накачки заряда, инверсный выход первого триггера соединен с дополнительным входом запрета частотно-фазового компаратора и с дополнительным входом запрета фазового компаратора, являющимся одним входом дополнительного элемента И, другой вход которого является другим входом фазового компаратора и подключен к информационной шине и к другому входу частотно-фазового компаратора, а дополнительный инвертирующий выход управляемого генератора соединен с выходной шиной.

Фиг.1

-Л/-М

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации воспроизведения информации | 1987 |

|

SU1465909A1 |

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

| СИНТЕЗАТОР ЧАСТОТ С АСТАТИЧЕСКИМ КОЛЬЦОМ АДАПТИВНОЙ ЧАСТОТНО-ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2007 |

|

RU2329596C1 |

| Устройство для синхронизации и выделения данных | 1989 |

|

SU1675943A1 |

| Частотно-фазовый компаратор | 1981 |

|

SU983978A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ГЕНЕРАТОРА ИМПУЛЬСОВ | 2004 |

|

RU2259630C1 |

| Устройство для синхронизации воспроизводимой с вращающегося магнитного носителя информации | 1977 |

|

SU720488A1 |

| Устройство выделения информации из частотно-модулированного сигнала | 1977 |

|

SU622148A1 |

| Генератор синхросигналов | 1977 |

|

SU744719A1 |

| Устройство для синхронизации воспроизводимой информации | 1977 |

|

SU690552A1 |

Изобретение относится к накоплению информации, а именно к устройствам синхронизации для дисковых накопителей цифровых данных. Изобретение позволяет ускорить процесс начального установления синхронизма в процессе воспроизведения данных в дисковом накопителе. Основной режим синхронизации осуществляется петлей фазовой автоподстройки, включающей соединенные в кольцо фазовый компаратор 6, блок 1 накачки заряда, фильтр 2 и управляемый генератор 3. При начальном установлении синхронизма поступающие на управляющие шины 10, 12 сигналы заменяют фазовый компаратор 6 в петле на частотно-фазовый компаратор 5, а также подключают дополнительный блок 18 накачки заряда. При этом резко повышается скорость фазовой автоподстройки в устройстве. 3 ил.

Фиг, 2

Ceffmop

S

.З

Сентор

L

V

| Устройство для синхронизации воспроизведения информации | 1987 |

|

SU1465909A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-12-23—Публикация

1988-10-05—Подача