1

Изобретение относится к области накопления информации, sf именно к устройствам для синхронизации воспроизведения информации.

Целью изобретения является повышение точности синхронизации путем увеличения помехозащищенности режима синхронизма.

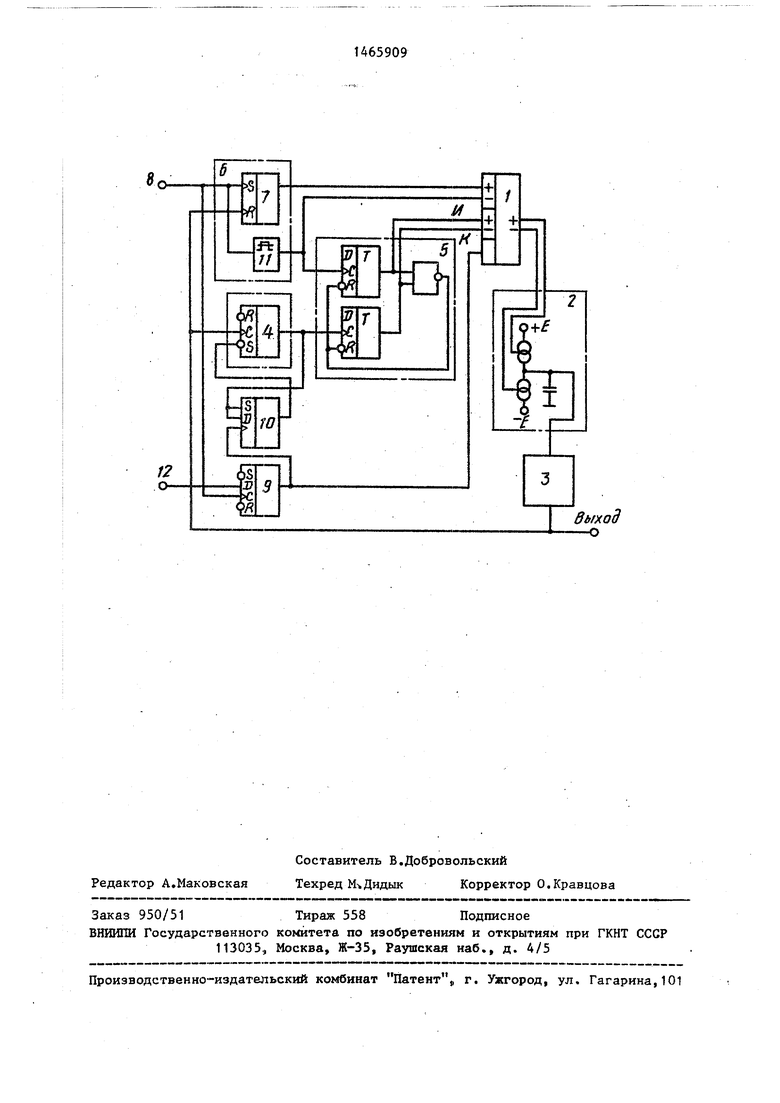

На чертеже приведена функциональная схема устройства для синхронизации воспроизведения информации.

Устройство для синхронизации воспроизведения информации содержит последовательно соединенные мультиплексор 1, двуполярный интегратор 2, управляемый генератор 3, делитель 4 частоты и частотно-фазовый детектор 5, подключенный вькодами к одним входам мультиплексора 1. Мультиплексор

1 подсоединен другими входами к выходам фазового детектора 6, содержащего триггер 7 и соединенного одним входом с информационной шиной 8 и другим входом - с выходом управляемого генератора 3. Кроме того устройство содержит первый 9 и второй to триггеры, а фазовый детектор - од- новибратор 11, причем первый триггер , 9 подключен информационным входом к управляющей шине 12, а выходом - к соединенным между собой управляющему входу мультиплексора 1 и синхронизи- рзтощему входу второго триггера 10. Второй триггер 10 подключен соединенными между собой информационным вхо.п дом и входом установки в 1 к выходу делителя 4 частоты и подсоединен выходом к установочному входу дели4 О5 01 О СО

3

геля 4 частоты. При этом триггер фа зового детекторе 6 выпалнен в виде |цинамического триггера 7, первый вхо Которого является одню.1 входом фазового детектора 6 и соедин€ н с входом одновибратора 11, Одновибратор 11 соединен выходом с соответствующим Эходом частотно-фазового детектора |5. Второй вход динамического триггера 7 является другим входом фазового детектора 6 выходы которого соединены с выходами динамического триггера 7 и одновибратора 11 „

Устройство работает следующим образом,

В исходном состоянии сигналы на иину 8 не поступают, на пкше 12 присутствует низкий уровеш. логической i 1. Мультиплексор 1, на управляющий вход .которого .с вьпсода триггера 9 поступает логическая 1, ко1 1мутируе к двухканальному входу интегратора 2 двухканальный выход фазового детектора б, где в связи с отсутствием входных сигналов присутствуют уровни гюгического О. На выходе интегратора 2 сохраняется заданное среднее напряжение, определяющее номинальную частоту управляемого генератора 3,

Начальное установление синхронизма в устройстве осзлцествляется в пол синхронизации воспроизводимого инфор мадионного массива., которое представ пяет собой сплошную последователь

ость нулей, т.е„ регулярных им- (пульсов с периодом,, в два раза боль™ Цим единичного интервала - периода выходных синхросигналов. На шину 12 подается сигнал, необходимой для рсуществления захвата длительности Ь ВЫСОК1-Ш нулевым рабочим уровнем. При поступлении очередного воспроизведенного сигнала данных на шину 8 йа вькоде триггера 9 згстапавливается уровень Каждым входным импульсом данных запускается одновибратор 11, формирующий импульс/ длительность которого равна половине тактового интервала. Шпульсы одновибратора 11, точнее моменты их оконча- йия, служат первьми входными сигналами частотно-фазового детектора 5. Вторые- входные сигналы частотно-фазового детектора 5 образуются на выход делителя 4 частоты Начальная разность фаз сравниваемых частотно-фазовым детектором 5 сигналов - величина случайная с равномерным распреде

лением. В наихудшем случае разность фаз может оказаться максимальной, равной целому периоду входных сигналов, и для установления синхронизма потребуется значительное время. Для уменьшения неопределенности указанной разности фаз предусмотрена при- нудид ельная коррекция фазы сигнала обратной связи, которая производится,

5

5

0

5

0

5

0

5

синхронно с первым сигналом данных, пришедшим после управляющего сигнала по шине 12, В этот момент фронт сигнала с выхода триггера 9 поступает на С-вход триггера 10, который проверяет состояние делн:теля 4 частоты .выходных синхросигналов. Если в указанный момент на выходе делителя 4 частоты оказывается уровень логического о, то триггер 10 сбрасывается, устанавливая делитель 4 частоты в состояние 1. Установившийся единичный уровень на выходе делителя 4 частоты, воздействуя на установочный вход триггера 10, возвращает, его в исходное взведенное состояние. Таким образом, в момент поступления jпервого сигнала данных, на выходе де- :лителя 4 частоты обязательно будет низкий уровень логической 1, который может смениться на высокий уро- вень логического О не позже чем через период после первого сигнала данных. Если учесть, что на первом Iвходе частотно-фазового детектора 5 1ВХРДНОЙ сигнал, пройдя через одно- вибратор 11, появится с задержкой, равной половине тактового интервала, то оказьшается, что воздействующий на второй вход частотно-фазового детектора 5 фронт сигнала обратной связи находится в интервале ±1/2 тактового интервала. Таким образом, за счет описанного принудительного фазирования максимально -возможная начальная разность фаз сигналов на входах частотно-фазового детектора 5 сокращается в четыре раза,

Все время, пока на выходе триггера 9 остается высокий уровень логического О, мультиплексор 1 замыкает входы интегратора 2 на выходы частотно-фазового детектора 5. Частотно-фазовый детектор 5 в зависимости от разности фаз сравниваемьпс сигналов формирует на выходах импульсы с длительностью, равной задержке между сравниваемыми сигналами. Эти импульсы приводят к соответствующему

приращению выходного напряжения интегратора 2 и коррекции частоты управляемого генератора 3 в направлении компенсации разности фаз. В итоге к моменту окончания сигнала на шине 12 в устройстве устанавливается синфазное состояние, при котором ,фронты сигнала обратной связи н.а выходе делителя 4 частоты и входного сигнала с одновибратора 11 совпадают во времени,

К моменту перехода устройства в режим слежения при переключении триггера 9 в исходное состояние 1 дли- тельность импульса на выходе триггера 7 в фазовом детекторе б вследстви синфазности сигналов становится равгг ной длительности импульса одновибратора 11. Поэтому, хотя мультиплексор 1 и- подключает к входу интегратора 2 выход фазового детектора б, генераторы токов в нем включаются и выключаются одновременно; так как токи равны по величине, напряжение на его выходе не изменяется, следовательно, в устройстве не возникает переходного процесса при переходе из режима захвата в режим слежения.

В режиме слежения фазовая- автопод-ЗО детектор содержит одновибратор, при5

14659096

пульсов на двухканальном выходе фазового детектора 6 равны, поэтому из- , менения выходного сигнала интеграто-i ра 2 и модуляции частоты генератора 3 не происходит, что и обеспечивает повышенную динамическую точность синхрониз ации.

ЮФормула изобретения

Устройство для синхронизации воспроизведения информации, содержащее последовательно соединенные мультиплексор, двуполярньй интегратор, управляемый генератор, делитель частоты и частотно-фазовьй детектор, подключенный выходами к одним входам мультиплексора, подсоединенного друг rm-jH входа ш к выходам фазового детектора, содержащего триггер и соединенного (Здним входом с информационной шиной и другим входом - с выходом управляемого генератора,от л и

повышенпя точности синхронизации за счет увеличения помехозащ1лденности режима синхронизма, в него введены первый и второй триггеры, а фазовый

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой синхронизации для дискового накопителя цифровых данных | 1988 |

|

SU1615799A1 |

| Устройство для синхронизации воспроизведения оптоэлектронного запоминающего устройства | 1983 |

|

SU1109806A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Устройство для синхронизации воспроизводимой информации | 1977 |

|

SU690552A1 |

| Устройство синхронизации сигналов данных воспроизведения с подвижного оптического носителя | 1988 |

|

SU1527662A1 |

| Устройство для тактовой синхронизации канала цифровой магнитной записи-воспроизведения | 1987 |

|

SU1432598A2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВОГО ПРИЕМНИКА | 1996 |

|

RU2138907C1 |

| Генератор последовательности импульсов | 1980 |

|

SU944088A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1783577A2 |

| Устройство для синхронизации канала воспроизведения данных | 1989 |

|

SU1674245A1 |

Изобретение позволяет расширить полосу захвата, уменьшить время установления синхронизма и повысить точность син}сронизации при воспроизведении данных в накопителе с перемещающимся магнитным носителем. После быстрого достижения синхронизма в кольце фазовой автоподстройки частоты, образованном двуполярным интегратором, управляемым генератором, делителем частоты и подключённым посредством мультиплексора частотно- фазовым детектором, обеспечивается максимально возможная ширина полосы захвата. В устройстве осуществляется плавный без переходного процесса переход в режим слежения. При этом кольцо ФАПЧ замыкается уже через фазовый детектор, способный работать с кодированными сигналами данных, а сигнал на выходе двуполярного интегратора в режиме синхронизма имеет повышенную помехозащищенность. 1 ил. с ел с

стройка осуществляется на основании сравнения длительностей импульсов заряда и разряда с выхода фазового ; детектора 6. Если, например, очередной входной сигнал данных опаздыг вает относительно своей номинальной позиции, то на выходе одновибратора 11 появляется импульс фиксированной длительности, а на выходе триггера Уимпульс меньшей длительности. Эта пара импульсов проходит через мультиплексор 1 и, воздействуя на входы- интегратора 2, приводит к понижению его выходного напряжения и, следовательно, частоты вь1ходных синхросигналов. Сигналы фазовой ошибки появляются на выходе фазового детектора 6 только после прихода каждого входного импульса. Благодаря этому фазовый детектор б не реагирует на частоту входных сигналов и способен работать с кодированным сигналом данных. Как уже отмечалось, в уста- .новившемся режиме длительности им5

0

5

0

чем первый триггер подключен инфор мационным входом к управляющей шине, синхронизирующим входом - к информационной шине и выходом - к соединен- ным между собой управляющему входу

;мультиплексора и синхронизирующему входу второго триггера, подключенного соединенными между собой информационным входом и входом установки в 1 к выходу делителя частоты и подсоединенного выходом к установочному входу делителя частоты, при этом триггер фазового детектора вы полнен в виде динамического триггера, первый вход которого является одним входом фазового детектора и соединен с входом одновибратора, соеди}{енного выходом с соответствующим входом

частотно-фазового детектора, а второй вход динамического триггера является другим входом фазового детектора, выходы которого соединены с выходами динамического триггера и одновибратора.

| Магнитная головка | 1978 |

|

SU690556A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Takagi N.A | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1989-03-15—Публикация

1987-04-02—Подача