w

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный аналого-цифровой преобразователь | 1989 |

|

SU1762409A2 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (АЦП) | 1996 |

|

RU2110887C1 |

| Параллельный аналого-цифровой преобразователь | 1982 |

|

SU1019623A1 |

| Силовой цифроаналоговый преобразователь | 1987 |

|

SU1434544A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Дифференциальный усилитель | 1988 |

|

SU1598112A1 |

| Импульсный стабилизатор напряжения с защитой от перегрузок по току | 2019 |

|

RU2711138C1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

Изобретение относится к устройствам автоматики, контрольно-измерительной и вычислительной техники и позволяет повысить быстродействие и надежность путем устранения чувствительности к перегрузкам. Это достигается тем, что в преобразователь, содержащий резистивный делитель 2 напряжений, блок 3 компараторов, блок 5 кодирующей логики, блок 6 коммутации, параллельный АЦП 8 младших разрядов, введены два компаратора 9 и 10, два элемента И 11 и 12, блок 4 элементов И, вычитателъ 7. 2 з.п.ф-лы, 2 ил.

QS 4J

О О

Изобретение относится к устройствам автоматики, контрольно-измерительной и вычислительной техники, а именно к быстродействующим аналого-цифровым преобразователям.

Целью изобретения является повышение быстродействия и надежности путем устранения чувствительности к перегрузкам.

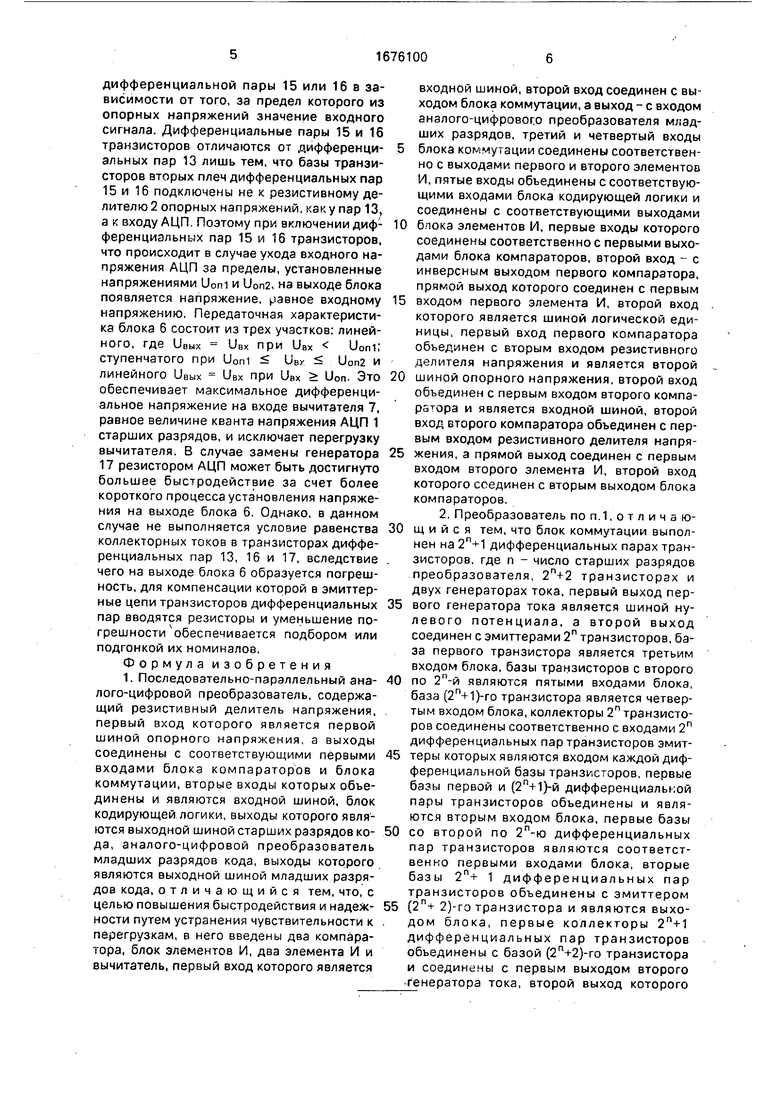

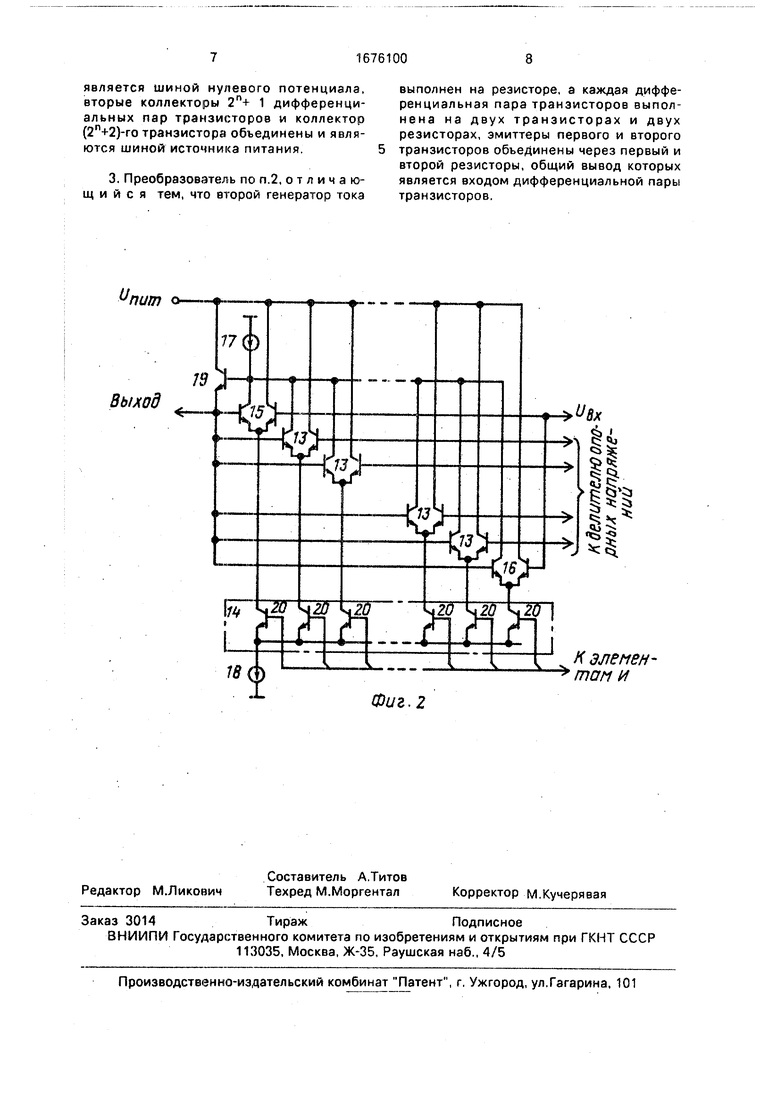

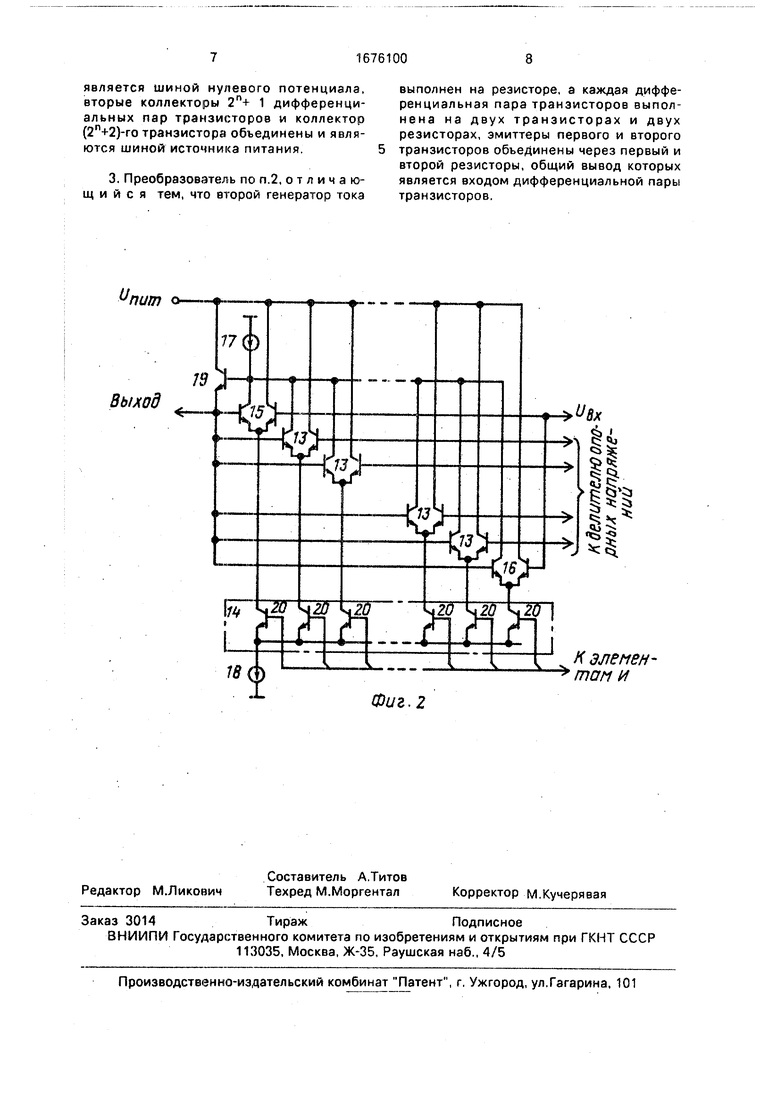

На фиг.1 представлена структурная схема последовательно-параллельного АЦП; на фиг.2 - структурная схемка блока коммутации.

Преобразователь содержит параллельный аналого-цифровой преобразователь 1 (АЦП) старших разрядов, состоящий из ре- зистивного делителя 2 напряжения, блока 3 компараторов, блока 4 элементов И и блока 5 кодирующей логики, блок 6 коммутации, вычитатель 7, параллельный АЦП 8 младших разрядов, компараторы 9 и 10, элементы И 11 и 12.

Блок коммутации (фиг.2) содержит 2п-1 дифференциальных 13 транзисторов, переключатель 14 тока, дифференциальные пары 15 и 16 транзисторов, генераторы 17 и 18 токов, транзистор 19, переключатель 14 содержит транзисторы 20.

Генератор 17 может быть заменен резистором, выключенным между шиной питания и точкой соединения коллекторов транзисторов первого плеча дифференциальных пар 13. 16 и 17, в этом случае эмиттеры транзисторов дифференциальных пар необходимо подключить к коллекторам транзисторов 20 через резисторы.

Последовательно-параллельный АЦП работает следующим образом.

Выходной аналоговый сигнал блоком 3 сравнивается с сеткой опорных напряжений резистивного делителя 2, при этом на выходах блока 3 образуется термометрический код, на прямых выходах сработавших компараторов имеется уровень логической 1. а на прямых выходах остальных компараторов имеется уровень логического О. Соответственно на инверсных выходах компараторов имеются уровни логических О и 1. Термометрический код с выходов блока 3 подается на входы блока 4 таким образом, что на один логический элемент И подаются Сигналы с прямого и инверсного выходов двух смежных компараторов. Элемент И образует на выходе уровень логической 1, когда логические уровни сигналов на его входах совпадают, либо уровень логического О, когда логические уровни сигналов на его входах не совпадают. Таким образом, логическая Т образуется только на выходе элемента И, соответствующего последнему

сработавшему компаратору, на выходах остальных логических элементов имеется уровень логического О. Данный унитарный цифровой код с выхода блока 4 подается на

блок 5, где он преобразуется в позиционный двоичный код старших разрядов и на управляющие входы блока 6, открывая один из транзисторов 20 переключателя 14, остальные транзисторы переключателя 14остэются закрытыми. Если входной сигнал имеет значение, ограниченное напряжениями источников опорных напряжений Uoni и Uon2, переключатель 14 тока включает одну из дифференциальных пар 13, а именно ту, которая подключена базой одного из транзисторов к опорному напряжению последнего сработавшего компаратора на резистивном делителе 2, открывая цепь для протекания токов генераторов 17 и 18 через данную

дифференциальную пару транзисторов. Величина тока генератора 17 меньше величины тока генератора 18, эти величины выбраны таким образом, что величины коллекторов первого и второго плечей дифференциальных пар 13 равны при одинаковых потенциалах без транзисторов. Дифференциальная пара 13 транзисторов вместе с транзистором 19 образует повторитель напряжения, который при одинаковых

параметрах транзисторов обоих плеч дифференциальных пар точно повторяет на выходе входное напряжение, т.е. опорное напряжение конкретной точки резистивного делителя 2. В эмиттерные цепи дифференциальных пар 13 транзисторов могут быть включены резисторы для балансировки дифференциальной пары. При изменении входного напряжения АЦП поочередно включаются (выключаются) все новые компараторы и на выходе блока 6 образуется ступенчатое напряжение, которое одновременно с входным сигналом поступает на вычитатель 7. Разностный сигнал с выхода вычитателя 7 поступает на параллельный

АЦП 8 младших разрядов, где он преобразуется в позиционный двоичный код младших разрядов АЦП.

Если значение входного сигнала выхо- дит за пределы, ограниченные значениями напряжений Uoni и 1)0п2, аналогично описанному выше срабатывают компараторы 9 или 10 и элементы 11 и 12. На выходе элемента 11 и 12 образуется уровень логи- ческой 1, при этом на выходах блока 4 образуются уровни логических О. Напряжение логической 1 с выхода элементов 11 или 12, минуя блок 5, подается на вход блока 6, включая транзистор переключателя 14 тока, управляющий включением

дифференциальной пары 15 или 16 в зависимости от того, за предел которого из опорных напряжений значение входного сигнала. Дифференциальные пары 15 и 16 транзисторов отличаются от дифференциальных пар 13 лишь тем, что базы транзисторов вторых плеч дифференциальных пар 15 и 16 подключены не к резистивному де- лителю2 опорных напряжений, как у пар 13, а к входу АЦП. Поэтому при включении дифференциальных пар 15 и 16 транзисторов, что происходит в случае ухода входного напряжения АЦП за пределы, установленные напряжениями U0ni и U0n2, на выходе блока появляется напряжение, равное входному напряжению. Передаточная характеристика блока 6 состоит из трех участков: линейного, где ивых UBX при DBX Uoni; ступенчатого при Doni UBy S U0n2 и линейного ивых UBX при U8x Uon. Это обеспечивает максимальное дифференциальное напряжение на входе вычитателя 7, равное величине кванта напряжения АЦП 1 старших разрядов, и исключает перегрузку вычитателя. В случае замены генератора 17 резистором АЦП может быть достигнуто большее быстродействие за счет более короткого процесса установления напряжения на выходе блока 6. Однако, в данном случае не выполняется условие равенства коллекторных токов в транзисторах дифференциальных пар 13, 16 и 17, вследствие чего на выходе блока 6 образуется погрешность, для компенсации которой в эмиттер- ные цепи транзисторов дифференциальных пар вводятся резисторы и уменьшение погрешности обеспечивается подбором или подгонкой их номиналов.

Формула изобретения 1. Последовательно-параллельный аналого-цифровой преобразователь, содержащий резистивный делитель напряжения, первый вход которого является первой шиной опорного напряжения, а выходы соединены с соответствующими первыми входами блока компараторов и блока коммутации, вторые входы которых объединены и являются входной шиной, блок кодирующей логики, выходы которого являются выходной шиной старших разрядов кода, аналого-цифровой преобразователь младших разрядов кода, выходы которого являются выходной шиной младших разрядов кода, отличающийся тем, что, с целью повышения быстродействия и надежности путем устранения чувствительности к перегрузкам, в него введены два компаратора, блок элементов И, два элемента И и вычитатель, первый вход которого является

входной шиной, второй вход соединен с выходом блока коммутации, а выход - с входом аналого-цифрового преобразователя младших разрядов, третий и четвертый входы блока коммутации соединены соответственно с выходами первого и второго элементов И, пятые входы объединены с соответствующими входами блока кодирующей логики и соединены с соответствующими выходами

0 блока элементов И, первые входы которого соединены соответственно с первыми выходами блока компараторов, второй вход - с инверсным выходом первого компаратора, прямой выход которого соединен с первым

5 входом первого элемента И, второй вход которого является шиной логической единицы, первый вход первого компаратора объединен с вторым входом резистивного делителя напряжения и является второй

0 шиной опорного напряжения, второй вход объединен с первым входом второго компаратора и является входной шиной, второй вход второго компаратора объединен с первым входом резистивного делителя напря5 жения, а прямой выход соединен с первым входом второго элемента И, второй вход которого соединен с вторым выходом блока компараторов.

2, Преобразователь по п. 1, о т л и ч а ю0 щ и и с я тем, что блок коммутации выполнен на дифференциальных парах транзисторов, где п - число старших разрядов преобразователя, 2п+2 транзисторах и двух генераторах тока, первый выход пер5 вого генератора тока является шиной нулевого потенциала, а второй выход соединен с эмиттерами 2П транзисторов, база первого транзистора является третьим входом блока, базы транзисторов с второго

0 по 2п-й являются пятыми входами блока, база (2п+1}-го транзистора является четвертым входом блока, коллекторы 2П транзисторов соединены соответственно с входами 2П дифференциальных пар транзисторов эмит5 теры которых являются входом каждой дифференциальной базы транзисторов, первые базы первой и (2п+1)-й дифференциальной пары транзисторов объединены и являются вторым входом блока, первые базы

0 со второй по 2п-ю дифференциальных пар транзисторов являются соответственно первыми входами блока, вторые базы 2П+ 1 дифференциальных пар транзисторов объединены с эмиттером

5 (2П+ 2)-го транзистора и являются выходом блока, первые коллекторы 2п+1 дифференциальных пар транзисторов объединены с базой (2п+2)-го транзистора и соединены с первым выходом второго генератора тока, второй выход которого

является шиной нулевого потенциала, вторые коллекторы 2П+ 1 дифференциальных пар транзисторов и коллектор (2п+2)-го транзистора объединены и являются шиной источника питания.

а,

пит оВыход

77

н

зп

дуг Длхр

- 1 I p-1r4-L /гэлем

там и

К элен

выполнен на резисторе, а каждая дифференциальная пара транзисторов выполнена на двух транзисторах и двух резисторах, эмиттеры первого и второго транзисторов объединены через первый и второй резисторы, общий вывод которых является входом дифференциальной пары транзисторов.

ц §i

« IS

ЈtSv

I

1

/гэлем

К элененФиг.2

| ElectronicLetters, 1985, № 6, р.235, fig.7 | |||

| Бахтияров Г.Д | |||

| Аналого-цифровые преобразователи | |||

| - М.: Сов.радио, 1980, с | |||

| Складная решетчатая мачта | 1919 |

|

SU198A1 |

Авторы

Даты

1991-09-07—Публикация

1989-07-11—Подача