Иэобретение относится к вычислительной и электроизмерительной технике и может быть использовано в системах автоматического контроля , информационно-измерительных система1 сбора и обработки информации повышенной надежности.

Цель изобретения - повышение достоверности преобразования за счет обеспечения самоконтроля работы преобразователя.

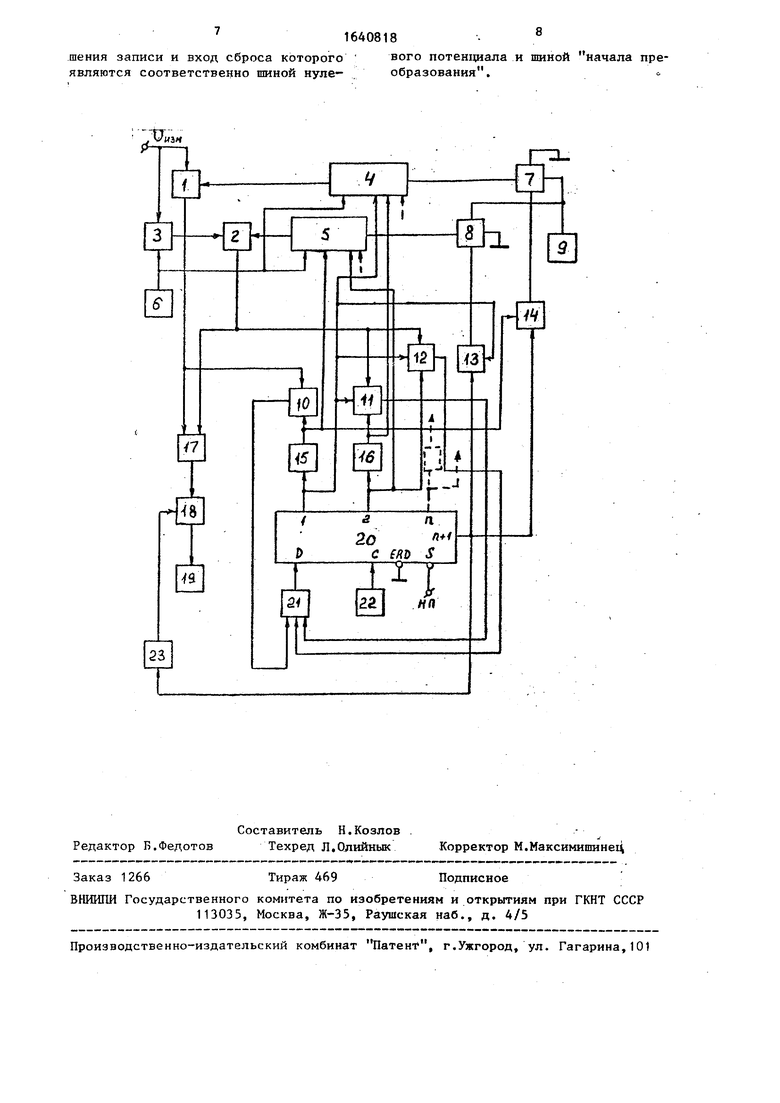

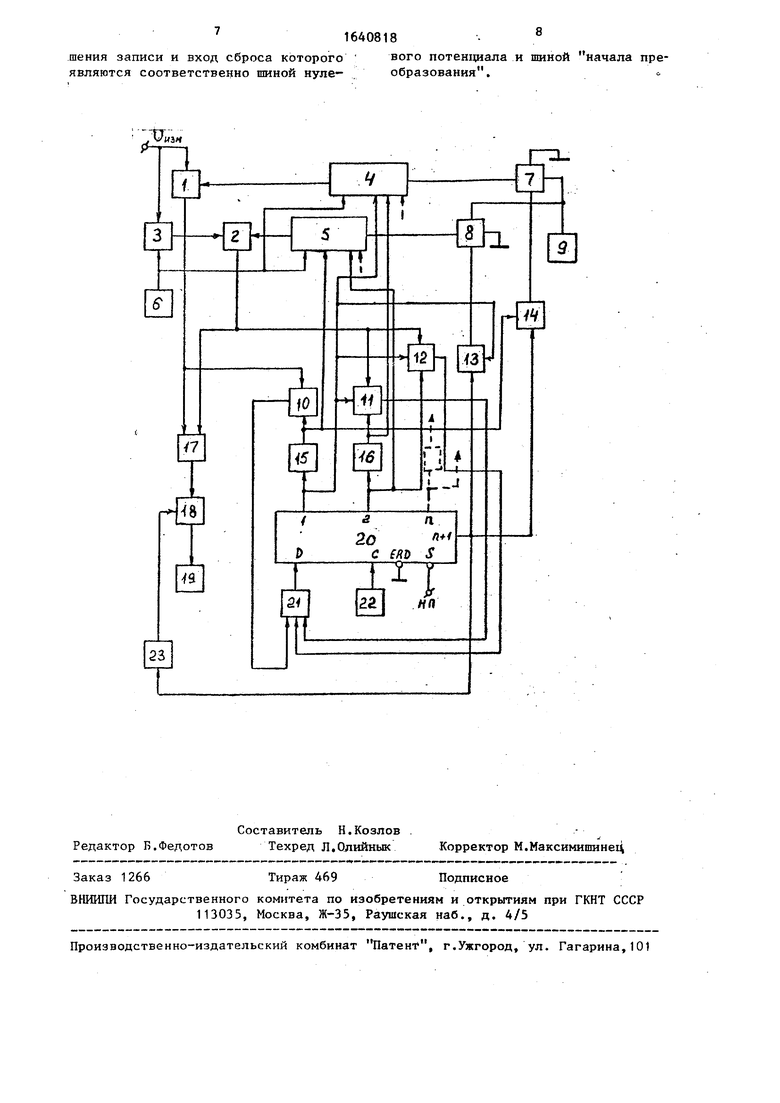

Йа чертеже представлена блок-схема аналого-цифрового преобразователя.

Устройство содержит компараторы 1, 2, аналоговый вычитатель 3, циф- роаналоговые преобразователи 4, 5, источник 6 эталонного напряжения положительной полярности, переключатели 7, 8, источник 9 эталонного

напряжения отрицательной полярности, элементы И 10-14, элементы НЕ 15, 16, элемент ИЛИ 17, элемент И 18, блок 19 индикации неисправностей, регистр 20, элемент ИЛИ 21, генератор 22 импульсов, элемент 23 задержки.

Устройство работает следующим образом.

Весь цикл преобразования происходит за n-И тактов, гпе п - число рабочих тактов, а п+1 - контрольный такт.

Аналого-цифровой преобразователь (АЦП) без самоконтроля работает следующим образом. Управление работой АЦП производится от регистра 20, который преобразует последовательный код, поступающий на информационный вход D, в параллельный. Регистр 20

оэ

ё

Оо

00

имеет вход С синхронизации, подключенный к выходу генератора импульсов, входы разрешения преобразования ERD и сброса S, подключенные к шинам нулевого потенциала и начало преобразования. При логическом уровне О на входах ERD и S по спаду отрицательного тактового импульса триг- , гера регистра 20 устанавливаются в начальное состояние: на выходах с 1 j по п-уровень 1, где выход 1 -нулевой) выход триггера старшего разряда, а вы( ходы с 2 по п - единичные выходы триг- j геров регистра 20. На выходе цифро- аналогового преобразователя (ЦАП) 4 устанавливается напряжение

Sf

лонного источника 6, а на выходе

1640818 - 4

ределяются все разряды АЦП. Выходной двоичный код снимается с выхо-1 дов с 1 по п (1 разряд снимается с нулевого выхода триггера старшего разряда регистра 20). Для слуиэт

2

снимается с выхода 1 регистра 20 10 и выходов элементов НЕ 15, 16.

При самоконтроле на п+1-ом такте

15

где Ugf напряжение эта20

чая, когда U/

выходной код

ИаГ

в случае, если U -& m+1-ый резис тор 2 R резистивной матрицы R-2R ЦАП 4 подключается через переключатель 7 к источнику 9, так как на управляющем входе переключателя 7 появляется разрешающий потенциал с элемента И 14. m+1-ый резистор 2 R резистивной матрицы R-2R ЦАП 5 остается подключенным к нулевой шине через переключатель 8, на управляющем входе которого имеется запрещающий потенциал. Тогда на выходе ЦАП 4 формируется напряжение а на выходе ЦАП 5 - напряжение UKOIW DMA.,, Затем производится сравнение напряжений U« и U мй.р компаратором 1, U$f UK и Vyr Uwwn UW.P. компаратором 2. Если Uy UKONHI- имл.р, и Uat - - - Una UMA.P, формируется сигнал Годен, который через элементы ИЛИ 17, И 18 поступает в устройство 19 индикации. Если выполняется хотя бы одно из условий U «i U От.р - -ицотч

ЦАП 5

- U№ft,p, где Uwft.p7 напряжение младшего разряда. Если преобразуемое напряжение Ux 4. -, сигнал

с компаратора 2 через элемент И 12 утанавливает триггер старшего разряда регистра 20 в состояние 1 и на выходе элементов НЕ 15, 16 устанавливается код 01111... 1, а тактовый импульс с генератора 22 устанавливает код 00111...1. В дальнейшем регистром 20 управляет компаратор 1 через элемент И 10, Б результате за п тактов в соответствии с алгоритмом поразрядного уравновешивания определяются все разряды АЦП,

Если U

JL2L

сигнал с компара

тора 2 через элемент И 12 сохраняет три гер старшего разряда регистра 20 в состоянии О, и на входе элементов НЕ 15, 16 сохраняется код 11111... 11, а тактовый импульс с генератора 22 устанавливает код 10111...1. В дальнейшем регистром 20 управляет компаратор 2 через элемент И 11 или элемент И 12 в зависимости от величины логического уровня на выходах регистра 20 (например, при логическом уровне О на выходе 2 регистра 20 информация на его вход D поступает через элемент И 1 Г от компара-. тора 2, а при логическом уровне 1 на выходе 2 эта информация на вход D поступает от компаратора 2 через элемент И 12. В результате за п тактов в соответствии с алгоритмом поразрядного уравновешивания оп

иэт

2

чая, когда U/

выходной код

5

0

5

0

5

5

0

5

ИаГ

в случае, если U -& m+1-ый резистор 2 R резистивной матрицы R-2R ЦАП 4 подключается через переключатель 7 к источнику 9, так как на управляющем входе переключателя 7 появляется разрешающий потенциал с элемента И 14. m+1-ый резистор 2 R резистивной матрицы R-2R ЦАП 5 остается подключенным к нулевой шине через переключатель 8, на управляющем входе которого имеется запрещающий потенциал. Тогда на выходе ЦАП 4 формируется напряжение а на выходе ЦАП 5 - напряжение UKOIW DMA.,, Затем производится сравнение напряжений U« и U мй.р компаратором 1, U$f UK и Vyr Uwwn UW.P. компаратором 2. Если Uy UKONHI- имл.р, и Uat - - - Una UMA.P, формируется сигнал Годен, который через элементы ИЛИ 17, И 18 поступает в устройство 19 индикации. Если выполняется хотя бы одно из условий U «i U От.р - -ицотч-U.p , формируется сигнал Негоден, который через элементы ИЛИ 17, И 18 поступает в блок 19 для индикации сигнала АЦП негоден. Элемент И 18 опрашивается на (п+1)-ом такте с задержкой, опредляемой элементом 23. При этом операция сравнения U у -Ux UgT Нкоип- Uwft,p тождественна операции сравнения Ujr UnoMn+ + и«л.р

Если m+1-й резистор 2 R резистивной матрицы R-2R ЦАП 4 подключается через переключатель 7 к нулевой шине, так как управляющий вход его имеет запрещающий потенциал от элемента И 14. m+1-ый резистор 2 R резистивной матрицы R-2R ЦАП 5 через переключатель 8 подключается к источнику 9, так как на управляющем входе переключателя 8 появляется разрешающий потенциал от

элемента И 13. При этом на.-«выходе ЦАП 5 - напряжение U 9т - UKOMQ-U/АЛ.р. На выходе НАЛ 4 - напряжение UXOMH- U м«.р. Если UK UKomn,-имл.р. и иэт - - Пкомп Ищй.р , формируется сигнал Годен. Если выполняется хотя бы одно из условий Ux -UnoMff- Umi/lp, U эТ U 11эт - ицомп- UMK.р. , Формируется сигнал Негоден, который через элег- менты ИЛИ 17,. И 18 поступает в устройство 19 для индикации сигнала АЦП негоден.

Таким образом, в устройстве одни и. те же ЦАП 5 и компаратор 2 участву- ют как в основной работе устройства, так и при его самоконтроле, что не требует дополнительных элементов для сам9контроля и позволяет повысить достоверность преобразования.

Формула изобретения

Аналого-цифровой преобразователь, содержащий регистр, выход старшего разряда которого соединен с входом старшего разряда первого цифроана- логового преобразователя, источник эталонного напряжения положительной полярности, выход которого соединен с первым входом аналогового вычятателя, второй вход которого объединен с первым входом первого компаратора и является входной шиной, выход аналогового вычитателя соединен с первым входом второго компаратора, второй вход первого компаратора соединен с выходом первого цифро- аналогового преобразователя, о т л и- чающийся тем, что, с целью повышения достоверности преобразования, за счет обеспечения самоконтроля работы преобразователя, в него введены второц цифроаналоговый преобразователь, источник эталонного напряжения отрицательной полярности, первый и второй переключатели, первый и второй элементы ИЛИ, генератор импульсов, блок индикации неисправностей, элемент задержки, первый, второй, третий, четвертый, пятый, шестой элементы И и п элементов НЕ причём первый вход первого элемента И соединен с выходом первого компаратора и объединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго ком16

10

15

20

25

40818.

паратора и объединен с первыми входами второго и третьего элементов И, вторые входы которых объединены с первым входом четвертого элемента И и с входом первого элемента НЕ, выход которого подключен ко второму входу первого элемента И и первому „ входу пятого элемента И, третий вход второго элемента И соединен с выходом второго элемента НЕ, вход которого подключен к третьему входу третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами первого и второго элементов И, выход второго элемента ИЛИ подключен к информационному входу регистра, входы п элементов НЕ подключены к соответствующим п выходам регистра, п+1 выход которого подключен к вторым входам четвертого и пятого элементов И, выходы которых подключены соответственно к управляющим входам первого и второго переключателей, первые входы которых соединены с. нулевой шиной, а вторые входы объединены и подключены к выходу источника эталонного напряжения отрицательной полярности, выходы первого и второго переключателей под- ключены соответственно к аналого, вым входам первого и второго цифро- аналоговых преобразователей, шины питания которых объединены с входом аналогового вычитателя, п+1 вы- . ход регистра соединен с входом эле40 мента задержки, выход которой подключен к первому входу шестого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, выход шестого элемента И под45 ключей к блоку индикации, второй вход первого элемента И подключен к входу старшего разряда второго циф- роаналогового преобразователя, входы остальных разрядов которого сое50 динены соответственно с выходами с второго но п разрядов регистра,., которые через элементы НЕ соединены с соответствующими входами первого цифроаналогового преобразователя, второй вход компаратора подключен к выходу второго цифроанало- гового преобразователя, выход генератора импульсов соединен с входом синхронизации регистра, вход разреЗС

55

71640818 - 8

шения записи и вход сброса которого вого потенциала и шиной начала пре- являются соответственно шиной нуле- образования.о

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно последовательный анало-гО-цифРОВОй пРЕОбРАзОВАТЕль C CAMOKOH-ТРОлЕМ | 1978 |

|

SU813770A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Устройство параллельно-последователь-НОгО АНАлОгО-цифРОВОгО пРЕОбРАзОВА-Ния C САМОКОНТРОлЕМ | 1979 |

|

SU815904A1 |

| Устройство контроля работоспособности | 1972 |

|

SU469212A1 |

| ДВУХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2251209C2 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1305859A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1350831A1 |

Изобретение относится к вычислительной и электроизмерительной технике и может быть использовано в системах контроля, сбора и обработки информации. Цель изобретения - повышение достоверности преобразования за счет обеспечения самоконтроля работы преобразователя. Для достижения поставленной цели в известное устройство, содержащее регистр, преобразователь цифра- аналог, два компаратора, аналоговый вычитатель, источник эталонного напряжения положительной полярности, в/ведены источник эталонного напряжения отрицательной полярности, устройство индикации неисправностей, элемент задержки, два элемента ИЛИ, два переключателя, шесть элементов И, второй преобразователь цифра-аналог, группа элементов НЕ, генератор импульсов. 1 ил. I (Л с

Составитель Н.Козлов Редактор Б.Федотов Техред Л.Олийнык

Заказ 1266

Тираж 469

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

Корректор М.МаксимишинеЦ

Подписное

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1978 |

|

SU750727A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-07—Публикация

1988-06-23—Подача