Изобретение относится к вычислительной технике и может быть использовано в системах автоматизированного контроля, сбора и обработки информации повышенной надежности.

Известно устройство параллельно-последовательного аналого-цифрового преобразования с самоконтролем (авт.св. СССР N 815904, кл. Н 03 К 13/00, 1978), содержащее два цифроаналоговых преобразователя, четыре нуль-органа, операционный усилитель, элементы И, ИЛИ, задержки, дешифратор, генератор импульсов, распределитель.

Недостатками устройства являются низкая точность преобразования, большой объем контрольных средств, низкое быстродействие контроля.

Известен резервированный аналого-цифрового преобразователь - АЦП (авт. св. СССР N 1510084, кл. Н 03 М 1/46, 1986), содержащий два АЦП, блок формирования выходного кода, два дифференциальных усилителя, два компаратора и элемент И-НЕ.

Недостатками резервированного АЦП являются низкая точность преобразования, большой объем контрольных средств, отсутствие самоконтроля каждого АЦП перед применением.

Известен АЦП (авт.св.СССР N 1529454, кл. Н 03 М 1/48, 1987), содержащий три компаратора, реверсивный счетчик, преобразователь кода в напряжение, элементы И, ИСКЛЮЧАЮЩЕЕ ИЛИ, коммутатор, генератор импульсов, триггер, источники опорных напряжений.

Недостатками АЦП являются низкие точность и быстродействие преобразования, большое количество компараторов, а также невозможность нормального функционирования при возникновении отказов его отдельных узлов.

Известно устройство аналого-цифрового преобразования (авт.св. СССР N 809554, кл. Н 03 К 13/17, 1979), содержащее два компаратора, регистр, узел разрядных переключателей, две резистивные матрицы типа R - 2R, элементы И, ИЛИ, задержки, два триггера, переключатели, генератор импульсов, распределитель тактов, логический блок.

Недостатками устройства являются низкая точность преобразования, большой объем контрольных средств, низкое быстродействие контроля, а также невозможность нормального функционирования при возникновении отказов его отдельных узлов и элементов.

Целью изобретения является повышение достоверности преобразования за счет совмещения операций контроля и рабочего преобразования и компенсации погрешностей при включении переключателя старшего разряда.

Цель достигается тем, что в устройство, содержащее два блока сравнения, первые входы которых являются входной шиной, вторые входы подключены соответственно к выходам первой и второй (m+1)-разрядным резистивным матрицам типа R-2R, входы которых подключены к выходам соответствующих разрядных переключателей, управляющие входы которых, кроме переключателя последнего разряда соединены с единичными выходами регистра последовательного приближения, которые, кроме последнего, являются шиной (n-1)-разрядного выходного кода, информационные входы - с выходом источника эталонного напряжения положительной полярности и объединены с входами резистивного делителя, первый и второй переключатели, выходы которых соответственно подключены к (m+2)-м резисторам 2R первой и второй (m+1)-разрядных резистивных матриц типа R-2R, генератор импульсов, выход которого соединен с входом синхронизации регистра последовательного приближения, первый элемент ИЛИ, первый вход которого подключен к выходу первого блока сравнения, а выход - к первому входу первого элемента И, второй вход которого через первый элемент задержки подключен к (n+1)-у выходу регистра последовательного приближения, первый RS-триггер, R-вход которого является шиной "Пуск", а нулевой выход подключен к управляющему входу первого переключателя, введены второй и третий RS-триггеры, два элемента НЕ, второй элемент ИЛИ, шесть элементов И, второй элемент задержки, источники удвоенного и учетверенного эталонных напряжений отрицательной и положительной полярностей, выходы последних из которых соединены соответственно с первым и вторым информационными входами первого переключателя, при этом первый и второй информационные входы второго переключателя соединены соответственно с выходами источников удвоенного и учетверенного эталонных напряжений отрицательной полярности, управляющий вход второго переключателя соединен с нулевым выходом первого RS-триггера и объединен с входом второго элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, третий вход - к выходу второго блока сравнения и объединен с входом первого элемента НЕ, выход второго элемента И подключен к информационному входу регистра последовательного приближения, выход первого элемента НЕ подключен к второму входу первого элемента ИЛИ, выход которого подключен к первому входу третьего элемента И, второй вход которого через второй элемент задержки подключен к n-у выходу регистра последовательного приближения, выходы третьего и первого элементов И подключены соответственно к S-входам первого и второго триггеров, нулевые выходы которых подключены соответственно к первому и второму входам четвертого элемента И, последний из которых объединен с первым входом пятого элемента И, второй вход которого подключен к единичному выходу первого триггера и объединен с первым входом шестого элемента И, второй вход которого соединен с единичным выходом второго триггера, третьи входы четвертого, пятого и шестого элементов И подключены к нулевому выходу третьего триггера, R-вход которого подключен к выходу второго элемента ИЛИ, первый вход которого через второй элемент НЕ соединен с выходом первого элемента ИЛИ, второй вход второго элемента ИЛИ подключен к выходу "Конец преобразования" регистра последовательного приближения, вход запуска которого соединен с нулевым выходом третьего триггера, выход резистивного делителя подключен к информационному входу переключателя последнего разряда, управляющий вход которого соединен с первым выходом регистра последовательного приближения, выход четвертого элемента И соединен с первым входом седьмого элемента И, второй вход которого подключен к n-у выходу регистра последовательного приближения, выход седьмого элемента И является шиной n-го разряда выходного кода, выходы четвертого, пятого и шестого элементов И являются соответственно первой, второй и третьей шинами индикации, R-вход второго RS-триггера и S-вход третьего RS-триггера объединены и соединены с шиной "Пуск".

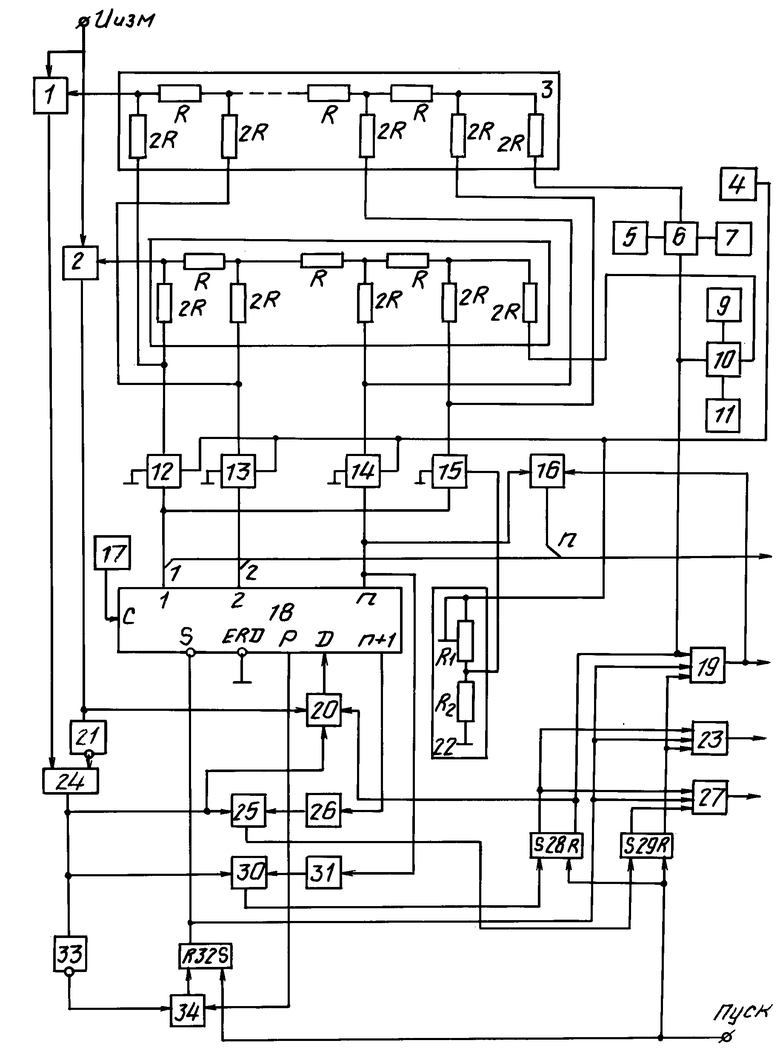

На чертеже представлена блок-схема устройства аналого-цифрового преобразования.

Устройство содержит блоки 1, 2 сравнения, (m+1)-разрядную резистивную матрицу 3 типа R-2R, источник 4 эталонного напряжения положительной полярности, источник 5 удвоенного эталонного напряжения положительной полярности, переключатель 6, источник 7 учетверенного эталонного напряжения положительной полярности, (m+1)-разрядную резистивную матрицу 8 типа R-2R, источник 9 удвоенного эталонного напряжения отрицательной полярности, переключатель 10, источник 11 учетверенного эталонного напряжения отрицательной поляpности, разрядные двухпозиционные переключатели 12-15, элемент И 16, генератор 17 импульсов, регистр 18 последовательного приближения, элементы И 19, 20, элемент НЕ 21, резистивный делитель 22, элемент И 23, элемент ИЛИ 24, элемент И 25, элемент 26 задержки, элемент И 27, RS-триггеры 28, 29, элемент И 30, элемент 31 задержки, RS-триггер 32, элемент НЕ 33, элемент ИЛИ 34.

Устройство работает следующим образом.

Процесс преобразования напряжения постоянного тока в код происходит с сокращенным циклом кодирования, но не более, чем за n тактов. В случае дефектов или случайных погрешностей производится реконфигурация устройства, при этом работоспособность сохраняется, но разрядность выходного кода уменьшается на один разряд.

Устройство вырабатывает сигнал "Конец преобразования" как только разность между компенсирующими и измеряемым напряжениями становится меньше величины напряжения младшего разряда. Для формирования напряжения Uкомп + U мл.р используется резистивная матрица 3 типа R-2R, у которой оконечный (m+2) резистор 2R через переключатель 6 подключен к источнику 5 удвоенного эталонного напряжения положительной полярности, Для формирования напряжения Uкомп - U мл.р используется резистивная матрица 8 типа R-2R, у которой оконечный (m+2) резистор 2R через переключатель 10 подсоединен к источнику 9 удвоенного эталонного напряжения отрицательной полярности. Для управления работой регистра 18 используются два блока 1 и 2 сравнения. На выходе блока 1 сравнения разрешающий уровень "1" формируется при Uизм > Uкомп + +Uмл.р, а запрещающий уровень "0" - при Uизм < Uкомп + U мл.р. На выходе блока 2 сравнения разрешающий уровень "1" формируется при Uизм > U комп - U мл.р, а запрещающий уровень; "0" - при Uизм < Uкомп - U мл.р. Если в процессе преобразования выполняются одновременно неравенства Uизм < <Uкомп + Uмл.р и Uизм > Uкомп - Uмл.р, то на выходе элемента ИЛИ 24 формируется запрещающий уровень "0", который через элемент НЕ 33 и элемент ИЛИ 34 устанавливает RS-триггер 32 в нулевое состояние, и на входе запуска  регистра 18 устанавливается уровень "1", прерывающий процесс преобразования.

регистра 18 устанавливается уровень "1", прерывающий процесс преобразования.

Рассмотрим управление работой устройства аналого-цифрового преобразования от регистра 18, который преобразует последовательный код, поступающий на информационный вход D, в параллельный код. При поступлении сигнала "Пуск" RS-триггеры 28, 29 устанавливаются в нулевое состояние, а RS-триггер 32 - в единичное состояние. В результате на входе запуска  регистра 18 устанавливается уровень "0". Первый тактовый импульс от генератора 17 импульсов устанавливает регистр 18 в исходное состояние, и на входы разрядных переключателей 12-14 поступает код 011...1. При этом на выходе резистивной матрицы 3 типа R-2R формируется напряжение 0,5 Uэт, а на выходе резистивной матрицы 8 типа R-2R формируется напряжение 0,5 Uэт - 2U мл.р. Блоки1 и 2 сравнения сравнивают эти напряжения с измеряемым напряжением, Если выполняются одновременно неравенства Uизм <0,5Uэт и Uизм > 0,5Uэт - -2Uмл.р, то на выходе элемента ИЛИ 24 формируется запрещающий уровень "0", который через элемент НЕ 33 и элемент ИЛИ 34 устанавливает RS-триггер 32 в нулевое состояние, на входе запуска

регистра 18 устанавливается уровень "0". Первый тактовый импульс от генератора 17 импульсов устанавливает регистр 18 в исходное состояние, и на входы разрядных переключателей 12-14 поступает код 011...1. При этом на выходе резистивной матрицы 3 типа R-2R формируется напряжение 0,5 Uэт, а на выходе резистивной матрицы 8 типа R-2R формируется напряжение 0,5 Uэт - 2U мл.р. Блоки1 и 2 сравнения сравнивают эти напряжения с измеряемым напряжением, Если выполняются одновременно неравенства Uизм <0,5Uэт и Uизм > 0,5Uэт - -2Uмл.р, то на выходе элемента ИЛИ 24 формируется запрещающий уровень "0", который через элемент НЕ 33 и элемент ИЛИ 34 устанавливает RS-триггер 32 в нулевое состояние, на входе запуска  регистра 18 устанавливается уровень "1" и процесс преобразования заканчивается. Если вышеупомянутые неравенства одновременно не выполняются, то на выходе блока 2 сравнения будет уровень "1" (при U изм > 0,5 Uэт - 2 U лм.р) или уровень "0" (при Uизм< 0,5 Uэт - 2 U мл.р). Если на выходе блока 2 сравнения уровень "1", то вторым тактовым импульсом он записывается в триггер первого с выхода регистра 18 и сохраняется до конца преобразования (при уровне "0" на выходе блока 2 сравнения в этом триггере регистра 18 сохраняется уровень "0").

регистра 18 устанавливается уровень "1" и процесс преобразования заканчивается. Если вышеупомянутые неравенства одновременно не выполняются, то на выходе блока 2 сравнения будет уровень "1" (при U изм > 0,5 Uэт - 2 U лм.р) или уровень "0" (при Uизм< 0,5 Uэт - 2 U мл.р). Если на выходе блока 2 сравнения уровень "1", то вторым тактовым импульсом он записывается в триггер первого с выхода регистра 18 и сохраняется до конца преобразования (при уровне "0" на выходе блока 2 сравнения в этом триггере регистра 18 сохраняется уровень "0").

По окончании второго тактового импульса в регистре 18 появляется уровень "0" и на входы разрядных переключателей 12-14 поступает код 1011...1, далее производится сравнение измеряемого напряжения с компенсирующими при помощи блоков 1 и 2 сравнения и т.д. Если на n-м импульсе одновременно выполнялись неравенства Uизм < U комп + U мл.р и Uизм > Uкомп - Uмл.р, то единичный уровень на выходе RS-триггера 32 и входе запуска  регистра 18 заканчивает процесс преобразования. Если после n-го импульса не были одновременно выполнены неравенства Uизм < Uкомп + U мл.р и Uизм > Uкомп - U мл.р, то с задержкой, определяемой элементом 31 задержки ( τ<τт, где τт - длительность такта), через элемент И 30 RS-триггер 28 устанавливается в единичное состояние и переключатели 6 и 10 подключают оконечные резисторы 2R резистивных матриц 3 и 8 типа R-2R соответственно к источникам 7 и 11 учетверенного эталонного напряжения положительной и отрицательной полярности. На выходах резистивных матриц 3 и 8 типа R-2R устанавливаются соответственно напряжения Uкомп + 2 Uмл.р и Uкомп - 2Uмл.р. Блоки 1 и 2 сравнения сравнивают измеряемое напряжение с компенсирующими напряжениями. Если одновременно выполняются неравенства Uизм < Uкомп + 2Uмл.р и Uизм > Uкомп - 2 U мл.р, то на выходе элемента И 19 формируется уровень "0", который запрещает выдачу кода младшего разряда во внешнее устройство через элемент И 16. Кроме того, при помощи элемента И 23 формируется уровень "1" на шине m-1, который может быть использовано для индикации. Если одновременно не выполняются вышеприведенные неравенства, то после (n+1)-го такта на выходе элемента И 25 будет уровень "1" , который устанавливает триггер 29 в единичное состояние, а на выходе RS - триггера 29 устанавливается разрешающий уровень "1" для элемента И 27, на выходе которого формируется сигнал "Отказ". После (n+1)-го такта на выходе "Конец преобразования" Р регистра 18 устанавливается уровень "1", который устанавливает на входе запуска S регистра 18 уровень "1" и процесс преобразования заканчивается. При этом сигнал "Отказ" не позволит записать код из регистра 18 во внешнее устройство.

регистра 18 заканчивает процесс преобразования. Если после n-го импульса не были одновременно выполнены неравенства Uизм < Uкомп + U мл.р и Uизм > Uкомп - U мл.р, то с задержкой, определяемой элементом 31 задержки ( τ<τт, где τт - длительность такта), через элемент И 30 RS-триггер 28 устанавливается в единичное состояние и переключатели 6 и 10 подключают оконечные резисторы 2R резистивных матриц 3 и 8 типа R-2R соответственно к источникам 7 и 11 учетверенного эталонного напряжения положительной и отрицательной полярности. На выходах резистивных матриц 3 и 8 типа R-2R устанавливаются соответственно напряжения Uкомп + 2 Uмл.р и Uкомп - 2Uмл.р. Блоки 1 и 2 сравнения сравнивают измеряемое напряжение с компенсирующими напряжениями. Если одновременно выполняются неравенства Uизм < Uкомп + 2Uмл.р и Uизм > Uкомп - 2 U мл.р, то на выходе элемента И 19 формируется уровень "0", который запрещает выдачу кода младшего разряда во внешнее устройство через элемент И 16. Кроме того, при помощи элемента И 23 формируется уровень "1" на шине m-1, который может быть использовано для индикации. Если одновременно не выполняются вышеприведенные неравенства, то после (n+1)-го такта на выходе элемента И 25 будет уровень "1" , который устанавливает триггер 29 в единичное состояние, а на выходе RS - триггера 29 устанавливается разрешающий уровень "1" для элемента И 27, на выходе которого формируется сигнал "Отказ". После (n+1)-го такта на выходе "Конец преобразования" Р регистра 18 устанавливается уровень "1", который устанавливает на входе запуска S регистра 18 уровень "1" и процесс преобразования заканчивается. При этом сигнал "Отказ" не позволит записать код из регистра 18 во внешнее устройство.

В качестве примера рассмотрим кодирование данным устройством напряжения постоянного тока Uизм = 7,49 В при числе разрядов n = 10. При поступлении сигнала "Пуск" первый тактовый импульс с выхода генератора 17 импульсов устанавливает регистр 18 в исходное состояние и на входах разрядных переключателей 12-14 устанавливается код 011. . .1. На выходе резистивной матрицы 3 типа R-2R формируется напряжение 5,00 В, а на выходе резистивной матpицы 8 типа R-2R формируется напряжение 4,98 В. Так как 7,49 В > 4,98 В, то на выходе блока 2 сравнения формируется уровень "1" и на первом выходе регистра 18 устанавливается уровень "1". По окончании второго тактового импульса на втором выходе регистра 18 устанавливается уровень "0" и на входе разрядных переключателей формируется код 1011...1. На выходе резистивной матрицы 3 типа R-2R формируется напряжение 7,50 В, а на выходе резистивной матрицы 8 типа R-2R формируется напряжение 7,48 В. Так как 7,49 В > 7,48 В и 7,49 В < 7,50 В, то на выходе блока 32 сравнения формируется уровень "0", который через элемент НЕ 21, элемент ИЛИ 24, элемент НЕ 33 им элемент ИЛИ 34 устанавливается уровень "1" и процесс преобразования заканчивается за два такта. Кроме того, при установке уровня "1" на первом выходе регистра 18 переключатель 15 коммутирует дополнительное напряжение к входам (m+1)-х резисторов 2R резистивных матриц 3 и 8 типа R - 2R. Как правило, погрешность в старшем разряде устройства в основном определяется сопротивлением замкнутого ключа переключателя и не превышает величины, равной половине напряжения младшего разряда. Для этой цели напряжение от источника 4 эталонного напряжения через резистивный делитель 22 поступает на информационный вход переключателя 15.

Таким образом, при возникновении в устройстве неисправностей в младшем разряде отказ не формируется, а производится реконфигурация схемы, при которой выходной код снимается с регистра устройства с разрядностью, меньшей на один разряд, и только в том случае, если устройство работоспособно после проведенной реконфигурации, т.е. измеряемое напряжение не выходит за пределы допуска Uкомп ±2Uмл.р. Применение дополнительного переключателя позволяет скомпенсировать погрешность при включенном старшем разряде, а использование минимального количества дополнительных аппаратных средств - повысить уровень отказоустойчивости устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| ДВУХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2251209C2 |

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Устройство параллельно-последователь-НОгО АНАлОгО-цифРОВОгО пРЕОбРАзОВА-Ния C САМОКОНТРОлЕМ | 1979 |

|

SU815904A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Обращенный цифроаналоговый преобразователь с резистивной матрицей R-2R | 1986 |

|

SU1345347A1 |

| Параллельно последовательный анало-гО-цифРОВОй пРЕОбРАзОВАТЕль C CAMOKOH-ТРОлЕМ | 1978 |

|

SU813770A1 |

| Преобразователь кода в напряжение | 1980 |

|

SU959273A1 |

| РАЗРЯДНЫЙ ЭЛЕМЕНТ ДЛЯ ПРЕОБРАЗОВАТЕЛЯ КОДА В НАПРЯЖЕНИЕ | 1967 |

|

SU224176A1 |

Устройство аналого-цифрового преобразования относится к вычислительной технике и может быть использовано в системах контроля, сбора и обработки информации. Цель изобретения - повышение достоверности, быстродействия контроля и надежности устройства. Для достижения цели в устройство, содержащее регистр последовательного приближения, двуматричный преобразователь кода в напряжение, переключатели, два компаратора, элемент ИЛИ, генератор импульсов, источник эталонного напряжения положительной полярности, элемент задержки, элемент И, первый триггер, введены второй и третий триггеры, два элемента НЕ, второй элемент ИЛИ, шесть элементов И, второй элемент задержки, резистивный двигатель, четыре источника эталонных напряжений, электронный ключ. Преобразование измеряемого напряжения в код производится с сокращенным циклом преобразования. Сигнал "Конец преобразования" формируется в тот момент, когда разность между компенсирующим и измеряемым напряжениями становится меньше величины младшего разряда. В регистре последовательного приближения формируется код разрядностью m. Если на последнем такте преобразования разность между компенсирующим и измеряемым напряжениями окажется больше величины младшего разряда, то на такте контроля формируются компенсирующие напряжения величиной Uкомп ± 2Uмл.р. . Если разность между измеряемым и компенсирующими напряжениями меньше, чем удвоенная величина младшего разряда, то в регистре последовательного приближения формируется код разрядностью m - 1, в противном случае формируется сигнал отказа. Для компенсации погрешности, возникающей при включении старшего разряда, в устройстве (m + 1)-е резисторы 2R резистивных матриц (R - 2R через ключ и делитель напряжения подсоединены к источнику эталонного напряжения положительной полярности. 1 ил.

УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ, содержащее два блока сравнения, первые входы которых являются входной шиной, вторые входы - подключены соответственно к выходам первой и второй (m + 1)-разрядным резистивным матрицам типа R - 2R, входы которых подключены к выходам соответствующих разрядных переключателей, управляющие входы которых, кроме переключателя последнего разряда, соединены с единичными выходами регистра последовательного приближения, которые, кроме последнего, являются шиной (n - 1)-разрядного выходного кода, информационные входы - с выходом источника эталонного напряжения положительной полярности и объединены с входами резистивного делителя, первый и второй переключатели, выходы которых соответственно подключены к (m + 2)-м резисторам 2R первой и второй (m + 1)-разрядных резистивных матриц типа R - 2R, генератор импульсов, выход которого соединен с входом синхронизации регистра последовательных приближений, первый элемент ИЛИ, первый вход которого подключен к выходу первого блока сравнения, а выход - к первому входу первого элемента И, второй вход которого через первый элемент задержки подключен к (n + 1)-му выходу регистра последовательного приближения, первый RS-триггер, R-вход которого является шиной "Пуск", а нулевой выход - к управляющему входу первого переключателя, отличающееся тем, что, с целью повышения достоверности преобразования, в него введены второй, третий RS-триггеры, два элемента НЕ, второй элемент ИЛИ, шесть элементов И, второй элемент задержки, источники удвоенного и учетверенного эталонных напряжений соответственно отрицательной и положительной полярностей, выходы последних из которых соединены соответственно с первым и вторым информационными входами первого переключателя, первый и второй информационные входы второго переключателя соединены соответственно с выходами источников удвоенного и учетверенного эталонных напряжения отрицательной полярности, управляющий вход второго переключателя соединен с нулевым выходом первого RS-триггера и объединен с первым входом второго элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, третий вход подключен к выходу второго блока сравнения и объединен с входом первого элемента НЕ, выход второго элемента И подключен к информационному входу регистра последовательного приближения, выход первого элемента НЕ подключен к второму входу первого элемента ИЛИ, выход которого подключен к первому входу третьего элемента И, второй вход которого через второй элемент задержки подсоединен к n-му выходу регистра последовательного приближения, выходы третьего и первого элементов И подключены соответственно к S-входам первого и второго RS-триггеров, нулевые выходы которых подключены соответственно к первому и второму входам четвертого элемента И, последний из которых объединен с первым входом пятого элемента И, второй вход которого подключен к единичному выходу первого триггера и объединен с первым входом шестого элемента И, второй вход которого соединен с единичным выходом второго триггера , третьи входы четвертого, пятого и шестого элемента И подключены к нулевому выходу третьего триггера, R-вход которого подключен к выходу второго элемента ИЛИ, первый вход которого через второй элемент НЕ соединен с выходом первого элемента ИЛИ, второй вход второго элемента ИЛИ подключен к выходу "Конец преобразования" регистра последовательного приближения, вход запуска которого соединен с нулевым выходом третьего RS-триггера, выход резистивного делителя подключен к информационному входу переключателя последнего разряда, управляющий вход которого соединен с первым выходом регистра последовательного приближения, при этом выход четвертого элемента И соединен с первым входом седьмого элемента И, второй вход которого подключен к n-му выходу регистра последовательного приближения, выход седьмого элемента И является шиной n-го разряда выходного кода, выходы четвертого, пятого и шестого элементов И являются соответственно первой, второй и третьей шинами индикации, R-вход второго RS -триггера и S-вход третьего RS-триггера объединены и соединены с шиной "Пуск".

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-09-30—Публикация

1991-06-26—Подача