(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения температуры | 1978 |

|

SU771485A1 |

| Цифровой интегрирующий вольтметр | 1990 |

|

SU1798711A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство для измерения температуры | 1984 |

|

SU1268970A1 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU849236A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

Изобретение относится к электроизмерительной технике. Цель изобретения - повышение точности и расширение частотного диапазона измерения. Предлагаемый измеритель содержит источник 2 опорного напряжения постоянного тока, цифровой вольтметр 3, сумматор 4, вычислительный блок 7. Введение интегратора 5, нуль-органа 6, блока 8 управления обеспечивает уст- ранение погрешностей, связанных с определением момента прекращения изменения знака интегрального значения суммарного сигнала и позволяет измерять сигналы частотой больше 50 Гц. 1 з.п. ф-лы, 1 ил.

о VI о

}

о

Изобретение относится к электроизмерительной технике.

Цель изобретения - повышение точности и расширение частотного диапазона измерения.

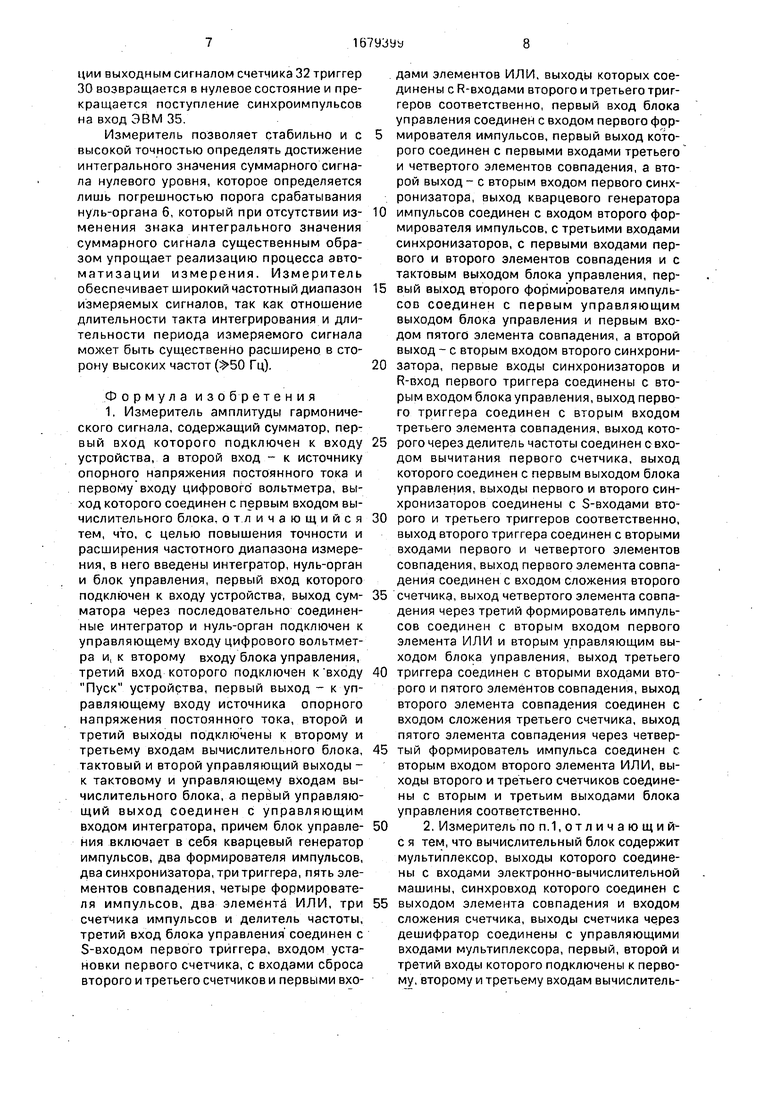

На чертеже представлена структурная схема измерителя.

Измеритель содержит вход для подключения источника 1 измеряемого сигнала, источник 2 регулируемого опорного напря- жения постоянного тока, цифровой вольтметр 3. сумматор 4 аналоговых сигналов, интегратор 5, нуль-орган б, вычислительный блок 7 и блок 8 управления, выполненный на первом триггере 9, кварцевом генерато- ре 10 импульсов, первом 11 и втором 12 формирователях импульсов, первом 13 и втором 14 синхронизаторах, втором 15 и третьем 16 триггерах, первом - пятом элементах 17-21 совпадения, делителе 22 час- тоты, первом счетчике 23, третьем 24 и четвертом 25 формирователях импульсов по заднему фронту, первом 26 и втором 27 элементах ИЛИ, втором 28 и третьем 29 счетчиках.

Вычислительный блок 7 выполнен на четвертом триггере 30, шестом элементе 31 совпадения, четвертом счетчике 32, дешифраторе 33, мультиплексоре 34 и электронно- вычислительной машине (ЭВМ) 35.

Вход устройства соединен с первым входом сумматора 4 и входом формирователя 11, образующим первый вход блока 8. Выход источника 2 подключен к второму входу сумматора 4 и входу вольтметра 3. Выход сумматора 4 через интегратор 5 соединен с входом нуль-органа 6. Вход Пуск устройства соединен с S-входом триггера 9, являющимся третьим входом блока 8, с входом установки счетчика 23, с входами сброса счетчиков 28 и 29 и первыми входами элементов ИЛИ 26 и 27, выходы которых соединены с R-входами триггеров 15 и 16 соответственно. Один из выходов формирователя 11 соединен с первыми входами элементов 19 и 20 совпадения, а другой выход - с вторым входом синхронизатора 13. Выход генератора 10 соединен с входом формирователя 12, с третьими входами синхронизаторов 13 и 14 с первыми входами элементов 17 и 18 и тактовым выходом блока 8, который соединен с первым входом элемента 31 совпадения, являющимся тактовым входом блока 7.

Один из выходов формирователя 12 соединен с управляющим входом интегратора 5 и первым входом элемента 21, а второй выход - с вторым входом синхронизатора 14. Первые входы синхронизаторов 13 и 14

и R-вход триггера 9 подключены к второму входу блока 8 и соединены с выходом нуль- органа 6 и с управляющим входом цифрового вольтметра 3, выход которого соединен с первым входом мультиплексора 34, являющимся первым входом блока 7. Выход триггера 9 соединен с вторым входом элемента 19, выход которого через делитель 22 соединен с входом вычитания счетчика 23, выход которого является первым выходом блока 8 и соединен с управляющими входами источника 2. Выходы синхронизаторов 13 и 14 соединены с S-входами триггеров 15 и 16 соответственно.

Выход триггера 15 соединен с вторыми входами элементов 17 и 20, выход элемента 17 соединен с входом сложения счетчика 28, а выход элемента 20 соединен с входом формирователя 24, выход которого соединен с вторым входом элемента ИЛИ 26 и S-входом триггера 30, являющегося управляющим входом блока 7. R-вход триггера 30 соединен с выходом счетчика 32. Выход триггера 30 соединен с вторым входом элемента 31, выход которого соединен с входом сложения счетчика 32 и синхровхо- дом ЭВМ 35. Выход триггера 16 соединен с вторыми входами элементов 18 и 21. Выход элемента 18 соединен с входом сложения счетчика 29, а выход элемента 21 через формирователь 25 соединен с вторым входом элемента ИЛИ 27. Выходы счетчиков 28 и 29, являющиеся вторым и третьим выходами блока 8, соединены с вторым и третьим входами мультиплексора 34 соответственно, являющимися вторым и третьим входами блока 7. Управляющие входы мультиплексора 34 соединены с выходами дешифратора 33, входы которого соединены с выходами счетчика 32. Выходы мультиплексора 34 соединены с входами ЭВМ 35.

Измеритель работает следующим образом.

В исходном состоянии на сумматор 4 поступают измеряемый сигнал Ux с источника 1 и опорный сигнал U0 с источника 2, причем Uo Ux по модулю, что обеспечивается подачей кодового сигнала со счет- чика 23 на входы источника 2, соответствующего максимальному значению его выходного напряжения. Последнее обеспечивается записью 1 во все разряды счетчика 23. При этом колебание сигнала на выходе сумматора 4 происходит без изменения знака сигнала. Одновременно сигнал Ux поступает на вход формирователя 11, который обеспечивает формирование как периодической последовательности импульсов длительностью, соответствующей периоду измеряемого сигнала, так и импульсов, соответствующих переднему фронту этих импульсов. Импульсы длительностью, равной периоду измерявмого сигнала, поступают на входы элемен- тов 19 и 20 совпадения, которые находятся в закрытом состоянии, а импульсы, соответствующие- переднему фронту этих импульсов, поступают на один из входов синхронизатора 13.

На вход формирователя 12 поступают импульсы с выхода кварцевого генератора 10, по которым формирователем 12 формируются импульсы периодической последовательности длительностью, равной такту интегрирования, а также импульсы, соответствующие их передним фронтам.

Импульсы длительностью, равной такту интегрирования, поступают на один из входов элемента 21 совпадения и на управляю- щий вход интегратора 5, обеспечивая периодическое интегрирование сигнала с выхода сумматора 4. Элемент 21 совпадения при этом находится в закрытом состоянии. Импульсы, соответствующие переднему фронту импульсов, длительностью, равной такту интегрирования, поступают на один из входов синхронизатора 14.

По команде Пуск, которая поступает на S-вход триггера 9, открывается элемент 19 совпадения, и импульсы длительностью, равной периоду измеряемого сигнала, поступают на вход делителя 22 частоты, коэффициент деления которого устанавливается заранее из условия обес- печения необходимой частоты изменения кода источника 2, а именно: Ткод « fx , где fx - частота сигнала Ux, при этом значение Uo на выходе источника 2 уменьшается с некоторого максимального значения до до- стижения интегрального значения суммарного сигнала нулевого значения. В этот момент нуль-орган 6 формирует выходной сигнал, которым триггер 9 возвращается в нулевое состояние и прекращает поступле- ние счетных импульсов на вход счетчика 23, Одновременно выходной сигнал нуль-органа б поступает на управляющий вход цифрового вольтметра 3 для измерения значения выходного сигнала с источника 2 и на входы синхронизаторов 13 и 14. Синхронизаторы 13 и 14 по сигналу с выхода нуль-органа 6 обеспечивают прохождение на S-входы триггеров 15 и 16 очередных импульсов с выходов формирователей 11 и 12, по которым на выходах триггеров 15 и 16 устанавливается высокий потенциал, открывающий элементы 17, 20 и 18, 21 совпадения соответственно. При этом на вход счетчика 28 поступает пачка импульсов, соответствующая длительности периода измеряемого сигнала, а на вход счетчика 29 поступает пачка импульсов, соответствующая длительности такта интегрирования.

Таким образом, осуществляется преобразование длительности периода измеряемого сигнала и такта интегрирования в цифровые коды, которые поступают на информационные входы вычислительного блока 7. Одновременно с преобразованием временной интервал - код формируются импульсы по заднему фронту импульсов дли- интервала интегрирования и периода измеряемого сигнала формирователями 24 и 25 импульсов, которые через элементы ИЛИ 26 и 27 возвращают триггеры 15 и 16 в нулевое состояние. Входной сигнал формирователя 24 определяет момент окончания измерения и поступает на управляющий вход вычислительного блока 7 для приема измерительной информации и последующего вычисления искомого амплитудного значения по формуле

- Uc

(f

I X

зтл:(-)

где Uо - результат

tu

измерения вольтметром 3; - - отноше1х

ние длительности такта интегрирования и периода измеряемого сигнала.

Однако, учитывая, что результаты измерения представляют собой цифровые коды, расчетную формулу можно представить в следующем виде:

3,141592

Ntu NTX

Sin 3,141592

Ntu NTX

ЭВМ 35 в блоке 7 в исходном состоянии находится в режиме готовности. По сигналу Конец измерения, который с выхода формирователя 24 поступает на S-вход триггера 30, открывается элемент 31 совпадения, и импульсы с его выхода поступают на вход счетчика 32 и, в качестве синхроимпульсов, на вход ЭВМ 35. Дешифратором 33 дешифрируется изменяющийся код с выхода счет- чика 32, который управляет подачей измерительной информации через мультиплексор 34 на информационный вход ЭВМ 35. При этом измерительная информация записывается в память ЭВМ 35 и далее по программе осуществляется вычисление искомого значения амплитуды. По окончании ввода в ЭВМ 35 измерительной инфармации выходным сигналом счетчика 32 триггер 30 возвращается в нулевое состояние и прекращается поступление синхроимпульсов на вход ЭВМ 35.

Измеритель позволяет стабильно и с высокой точностью определять достижение интегрального значения суммарного сигнала нулевого уровня, которое определяется лишь погрешностью порога срабатывания нуль-органа б, который при отсутствии изменения знака интегрального значения суммарного сигнала существенным образом упрощает реализацию процесса автоматизации измерения. Измеритель обеспечивает широкий частотный диапазон измеряемых сигналов, так как отношение длительности такта интегрирования и длительности периода измеряемого сигнала может быть существенно расширено в сторону высоких частот (50 Гц).

Формула изобретения 1, Измеритель амплитуды гармонического сигнала, содержащий сумматор, первый вход которого подключен к входу устройства, а второй вход - к источнику опорного напряжения постоянного тока и первому входу цифрового вольтметра, выход которого соединен с первым входом вычислительного блока, отличающийся тем, что, с целью повышения точности и расширения частотного диапазона измерения, в него введены интегратор, нуль-орган и блок управления, первый вход которого подключен к входу устройства, выход сумматора через последовательно соединенные интегратор и нуль-орган подключен к управляющему входу цифрового вольтметра и, к второму входу блока управления, третий вход которого подключен к входу Пуск устройства, первый выход - к управляющему входу источника опорного напряжения постоянного тока, второй и третий выходы подключены к второму и третьему входам вычислительного блока, тактовый и второй управляющий выходы - к тактовому и управляющему входам вычислительного блока, а первый управляющий выход соединен с управляющим входом интегратора, причем блок управления включает в себя кварцевый генератор импульсов, два формирователя импульсов, два синхронизатора, три триггера, пять элементов совпадения, четыре формирователя импульсов, два элемента ИЛИ, гри счетчика импульсов и делитель частоты, третий вход блока управления соединен с S-входом первого триггера, входом установки первого счетчика, с входами сброса второго и третьего счетчиков и первыми входами элементов ИЛИ, выходы которых соединены с R-входами второго и третьего триггеров соответственно, первый вход блока управления соединен с входом первого формирователя импульсов, первый выход которого соединен с первыми входами третьего и четвертого элементов совпадения, а второй выход- с вторым входом первого синхронизатора, выход кварцевого генератора

0 импульсов соединен с входом второго формирователя импульсов, с третьими входами синхронизаторов, с первыми входами первого и второго элементов совпадения и с тактовым выходом блока управления, пер5 вый выход второго формирователя импульсов соединен с первым управляющим выходом блока управления и первым входом пятого элемента совпадения, а второй выход - с вторым входом второго синхрони0 затора, первые входы синхронизаторов и R-вход первого триггера соединены с вторым входом блока управления, выход первого триггера соединен с вторым входом третьего элемента совпадения, выход кото5 рого через делитель частоты соединен ОБХОДОМ вычитания первого счетчика, выход которого соединен с первым выходом блока управления, выходы первого и второго синхронизаторов соединены с S-входами вто0 рого и третьего триггеров соответственно, выход второго триггера соединен с вторыми входами первого и четвертого элементов совпадения, выход первого элемента совпадения соединен с входом сложения второго

5 счетчика, выход четвертого элемента совпадения через третий формирователь импульсов соединен с вторым входом первого элемента ИЛИ и вторым управляющим выходом блока управления, выход третьего

0 триггера соединен с вторыми входами второго и пятого элементов совпадения, выход второго элемента совпадения соединен с входом сложения третьего счетчика, выход пятого элемента совпадения через четвер5 тый формирователь импульса соединен с вторым входом второго элемента ИЛИ, выходы второго и третьего счетчиков соединены с вторым и третьим выходами блока управления соответственно.

0 2. Измеритель по п. 1, от л и ч а ю щи й- с я тем, что вычислительный блок содержит мультиплексор, выходы которого соединены с входами электронно-вычислительной машины, синхровход которого соединен с

5 выходом элемента совпадения и входом сложения счетчика, выходы счетчика через дешифратор соединены с управляющими входами мультиплексора, первый, второй и третий входы которого подключены к первому, второму и третьему входам вычислитель

ного блока, S-вход триггера соединен с уп- вторым входом элемента совпадения, пер- равляющим входом вычислительного блока, вый вход которого подключен к тактовому R-вход - с выходом счетчика, а выход - с входу вычислительного блока.

| Способ измерения мгновенных значений электрического сигнала | 1982 |

|

SU1075177A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ измерения амплитуды гармонического сигнала | 1985 |

|

SU1310736A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-09-23—Публикация

1989-08-07—Подача