СЛ ОЭ СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство с динамическим выбором маршрутов передачи данных | 1987 |

|

SU1587529A1 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1985 |

|

SU1312560A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1403091A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1401447A1 |

| Устройство для считывания и отображения графической информации | 1986 |

|

SU1506459A1 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1339627A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

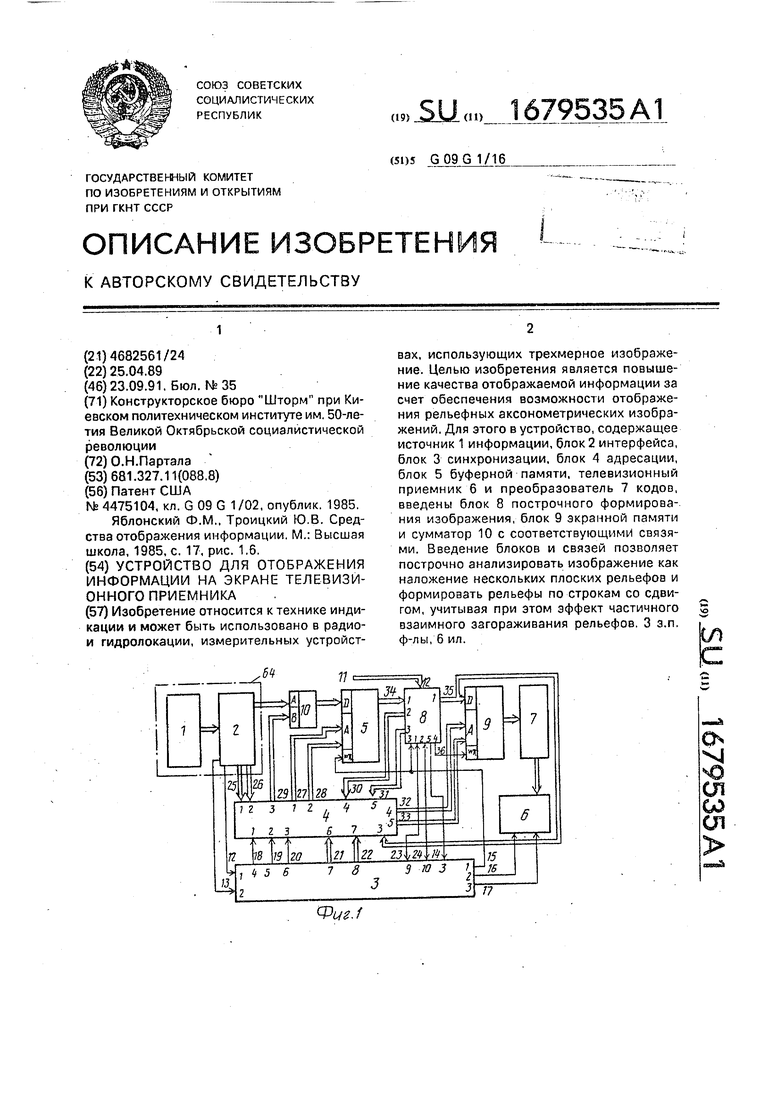

Изобретение относится к технике индикации и может быть использовано в радио- и гидролокации, измерительных устройствах, использующих трехмерное изображение. Целью изобретения является повышение качества отображаемой информации за счет обеспечения возможности отображения рельефных аксонометрических изображений. Для этого в устройство, содержащее источник 1 информации, блок 2 интерфейса, блок 3 синхронизации, блок 4 адресации, блок 5 буферной памяти, телевизионный приемник 6 и преобразователь 7 кодов, введены блок 8 построчного формирования изображения, блок 9 экранной памяти и сумматор 10 с соответствующими связями. Введение блоков и связей позволяет построчно анализировать изображение как наложение нескольких плоских рельефов и формировать рельефы по строкам со сдвигом, учитывая при этом эффект частичного взаимного загораживания рельефов. 3 з.п. ф-лы, 6 ил.

CPifg.f

Изобретение относится к технике индикации и может быть использовано в радио- и гидролокации, измерительных устройствах, использующих трехмерное изображение,

Целью изобретения является повышение качества отображаемой индикации за счет обеспечения возможности отображения рельефных аксонометрических изображений.

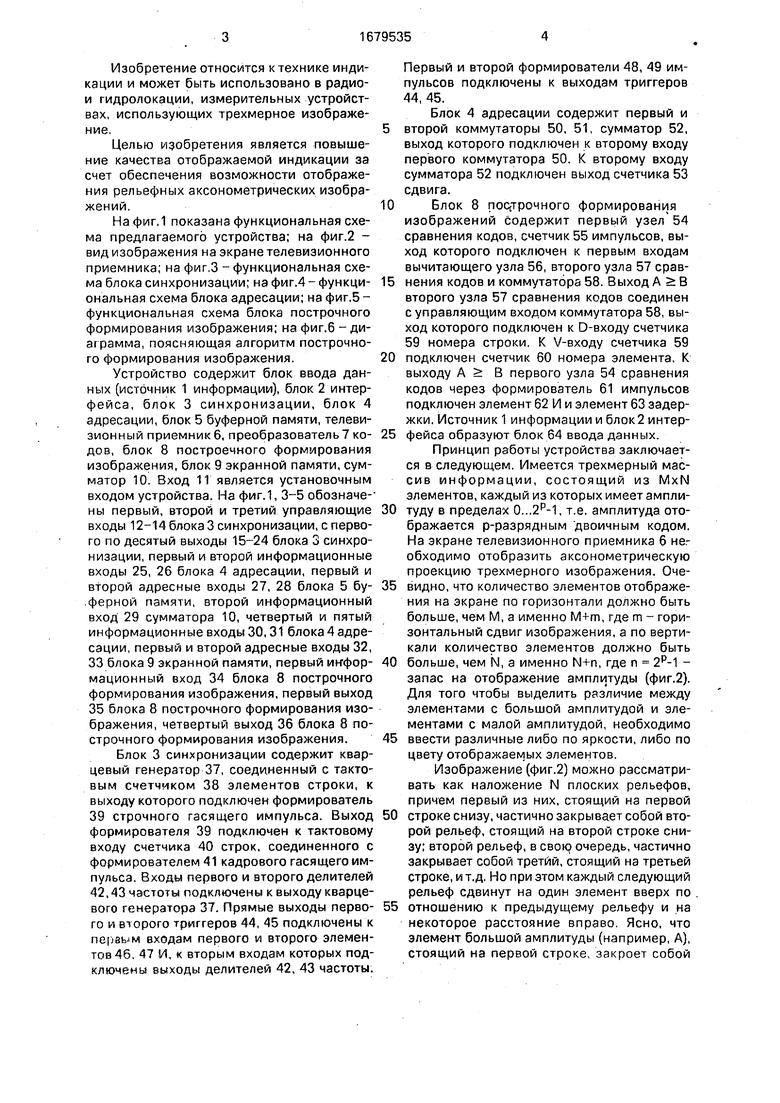

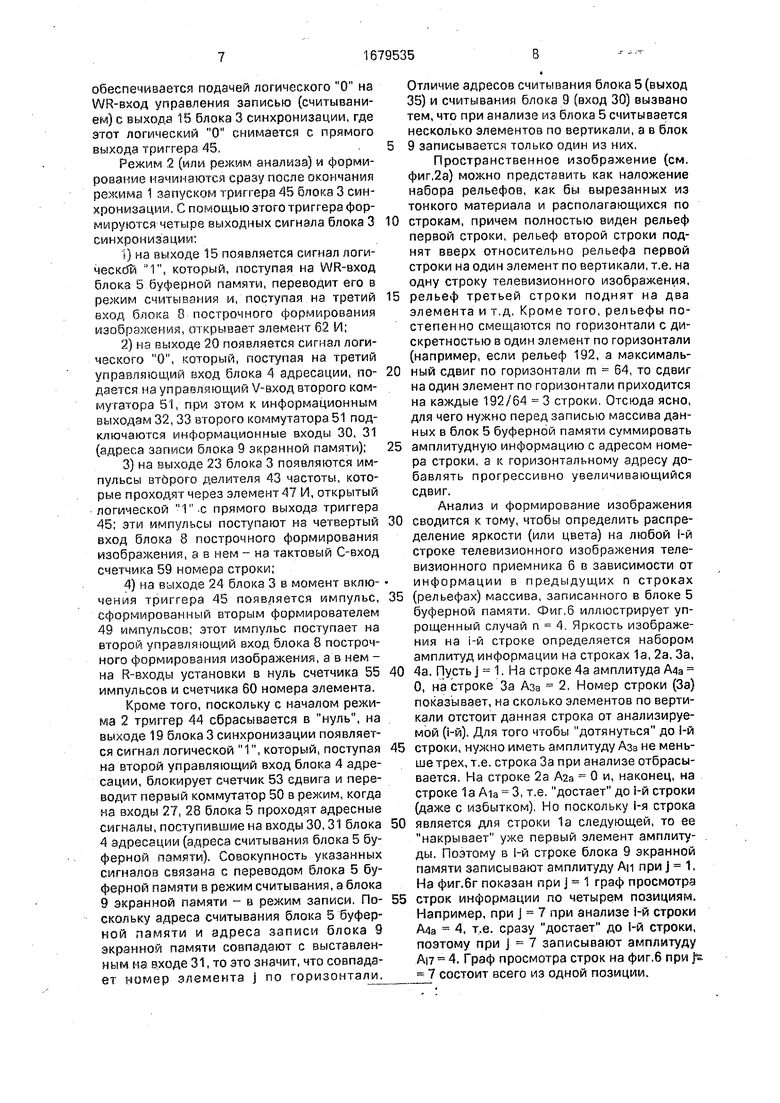

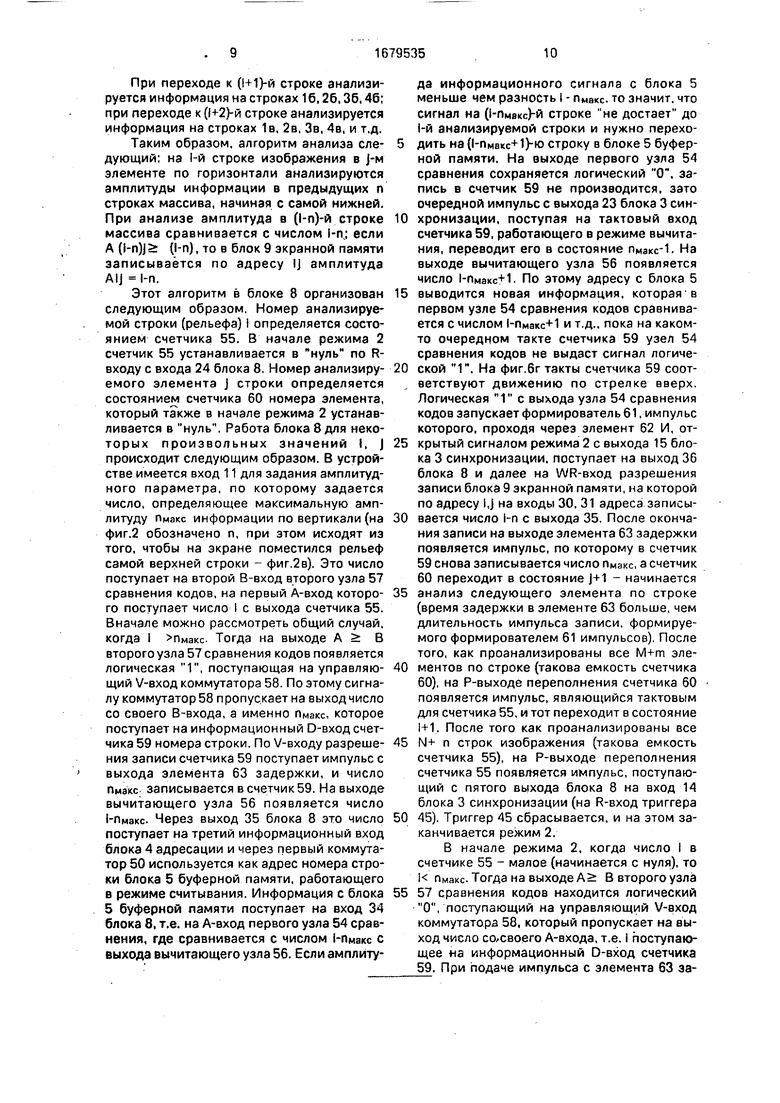

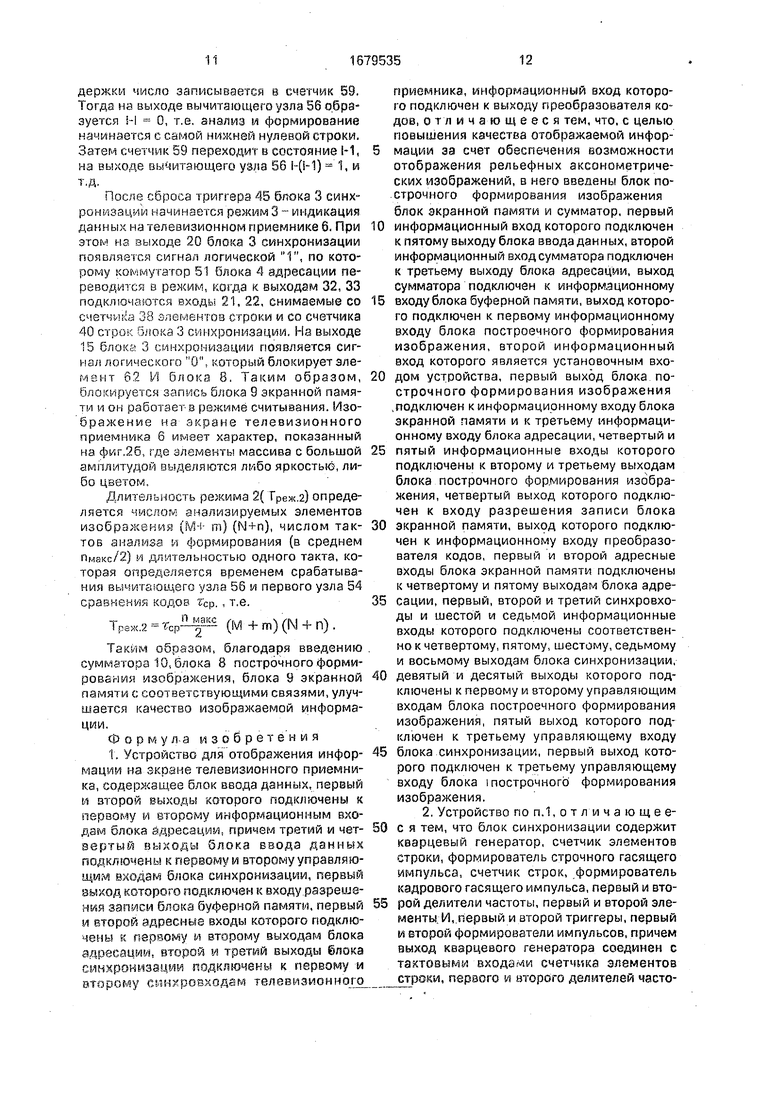

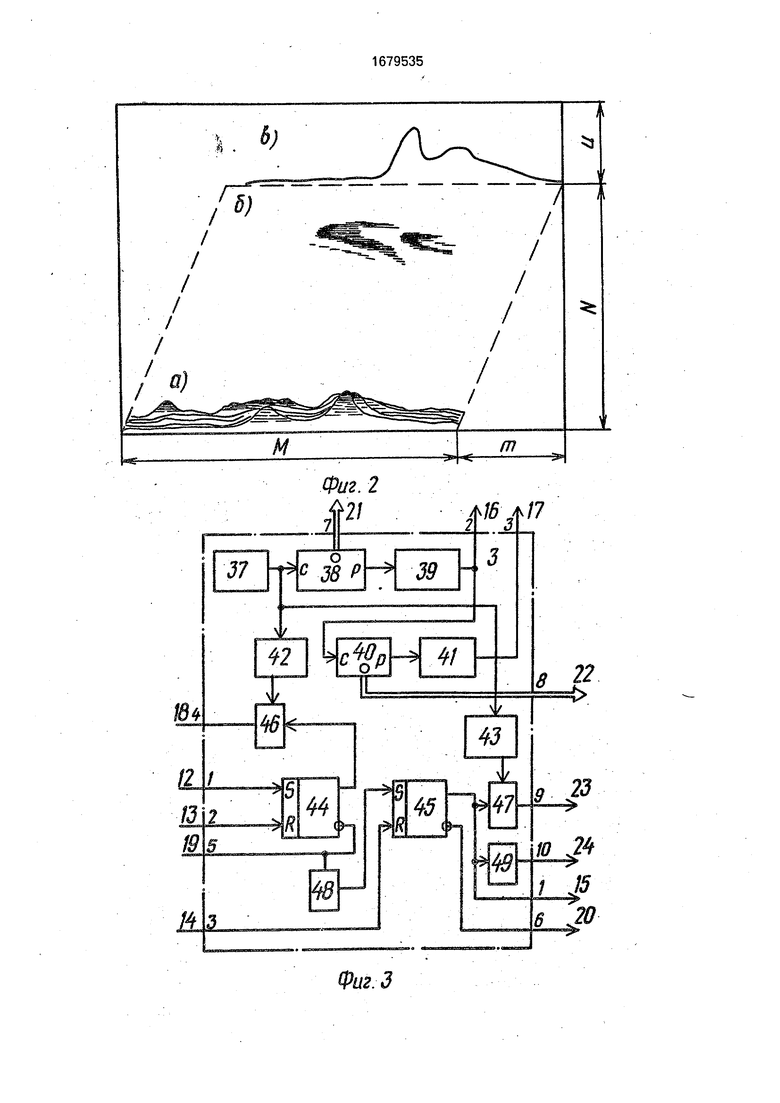

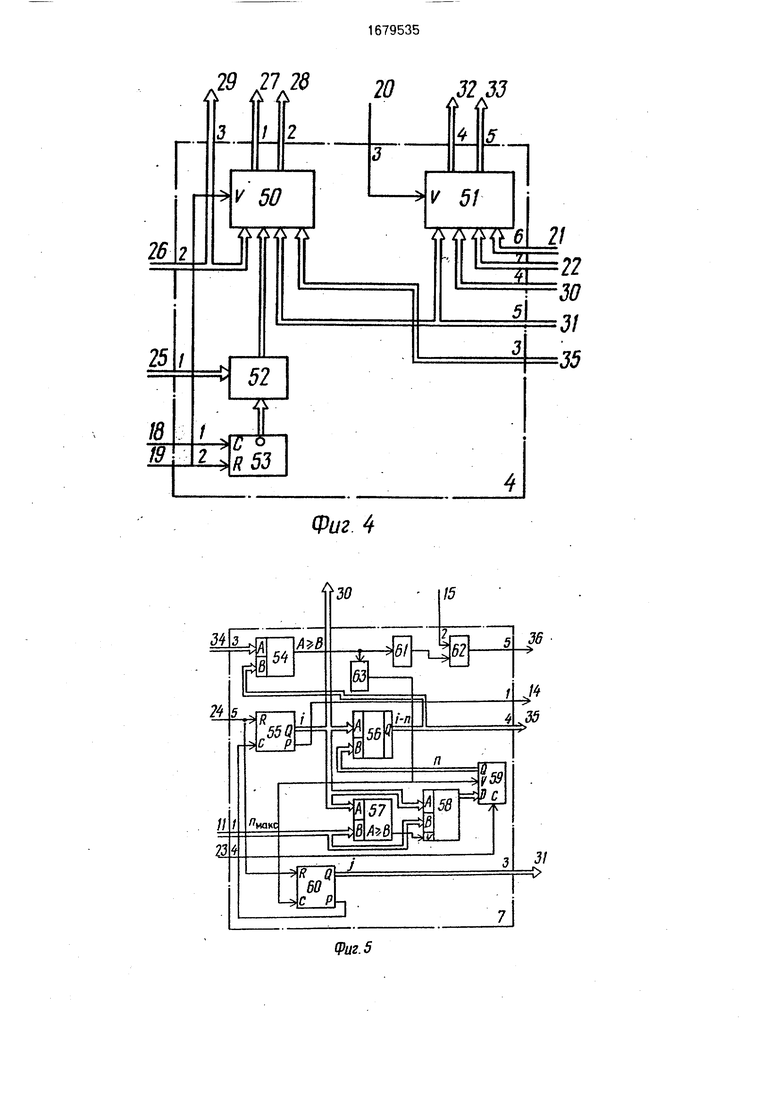

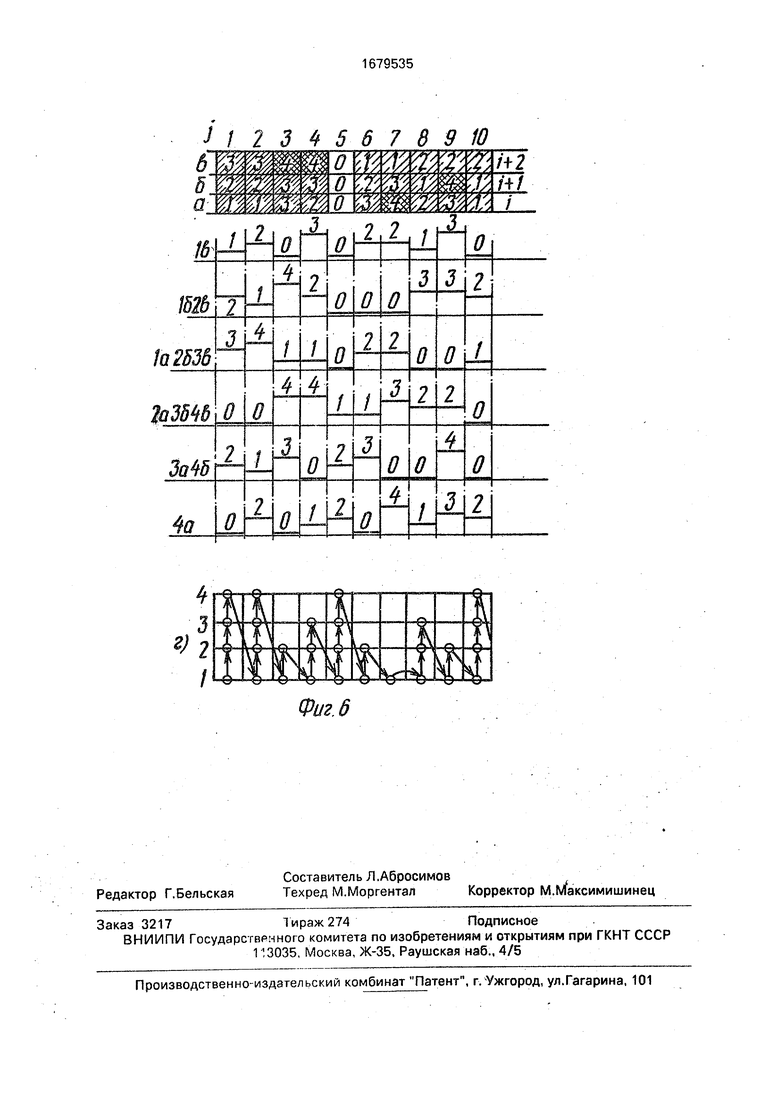

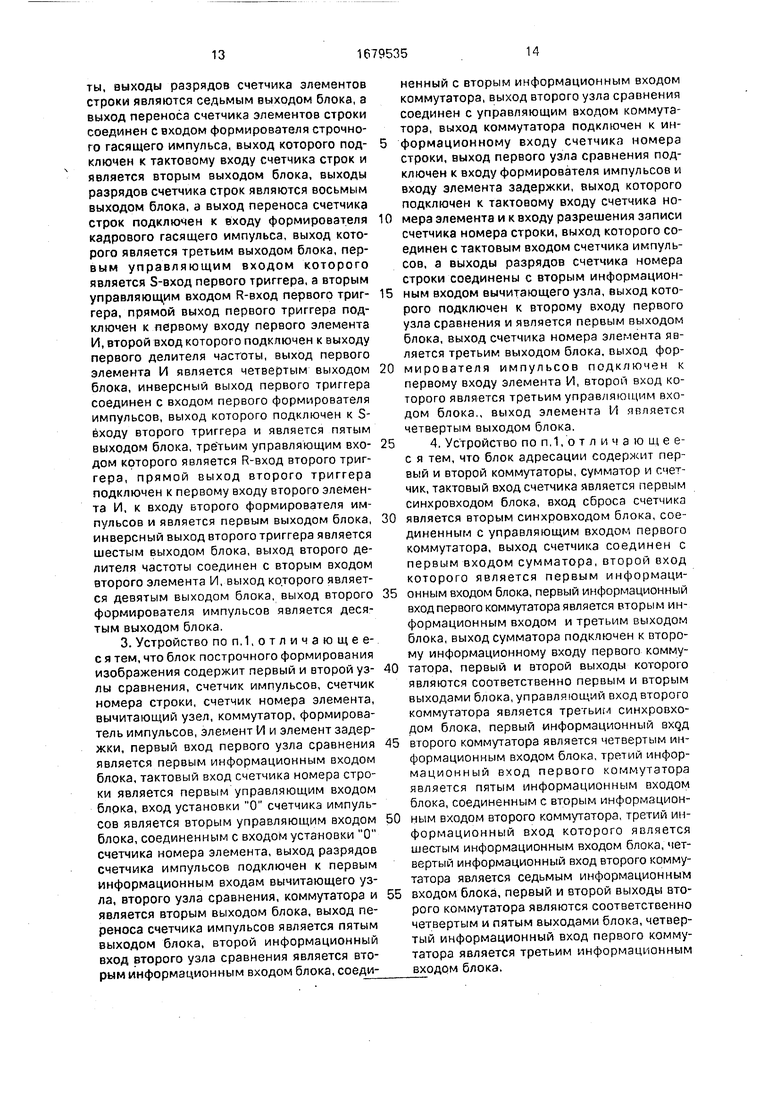

На фиг,1 показана функциональная схема предлагаемого устройства; на фиг.2 - вид изображения на экране телевизионного приемника; на фиг.З - функциональная схема блока синхронизации; на фиг.4 - функциональная схема блока адресации; на фиг.5 - функциональная схема блока построчного формирования изображения; на фиг.6 - диаграмма, поясняющая алгоритм построчного формирования изображения.

Устройство содержит блок ввода данных (источник 1 информации), блок 2 интерфейса, блок 3 синхронизации, блок 4 адресации, блок 5 буферной памяти, телевизионный приемник 6, преобразователь 7 кодов, блок 8 построечного формирования изображения, блок 9 экранной памяти, сумматор 10. Вход 11 является установочным входом устройства. На фиг.1, 3-5 обозначе- ны первый, второй и третий управляющие входы 12-14 блока 3 синхронизации, с первого по десятый выходы 15-24 блока 3 синхронизации, первый и второй информационные входы 25, 26 блока 4 адресации, первый и второй адресные входы 27, 28 блока 5 буферной памяти, второй информационный вход 29 сумматора 10, четвертый и пятый информационные входы 30,31 блока 4 адресации, первый и второй адресные входы 32, 33 блока 9 экранной памяти, первый информационный вход 34 блока 8 построчного формирования изображения, первый выход 35 блока 8 построчного формирования изображения, четвертый выход 36 блока 8 построчного формирования изображения.

Блок 3 синхронизации содержит кварцевый генератор 37, соединенный с тактовым счетчиком 38 элементов строки, к выходу которого подключен формирователь 39 строчного гасящего импульса. Выход формирователя 39 подключен к тактовому входу счетчика 40 строк, соединенного с формирователем 41 кадрового гасящего импульса. Входы первого и второго делителей 42,43 частоты подключены к выходу кварцевого генератора 37. Прямые выходы первого и второго триггеров 44, 45 подключены к первым входам первого и второго элементов 46, 47 И, к вторым входам которых подключены выходы делителей 42, 43 частоты.

Первый и второй формирователи 48, 49 импульсов подключены к выходам триггеров 44, 45.

Блок 4 адресации содержит первый и

второй коммутаторы 50, 51, сумматор 52, выход которого подключен к второму входу первого коммутатора 50. К второму входу сумматора 52 подключен выход счетчика 53 сдвига.

Блок 8 построчного формирования

изображений содержит первый узел 54 сравнения кодов, счетчик 55 импульсов, выход которого подключен к первым входам вычитающего узла 56, второго узла 57 сравнения кодов и коммутатора 58. Выход А В второго узла 57 сравнения кодов соединен с управляющим входом коммутатора 58, выход которого подключен к D-входу счетчика 59 номера строки. К V-входу счетчика 59

подключен счетчик 60 номера элемента. К выходу А В первого узла 54 сравнения кодов через формирователь 61 импульсов подключен элемент 62 И и элемент 63 задержки. Источник 1 информации и блок2 интерфейса образуют блок 64 ввода данных.

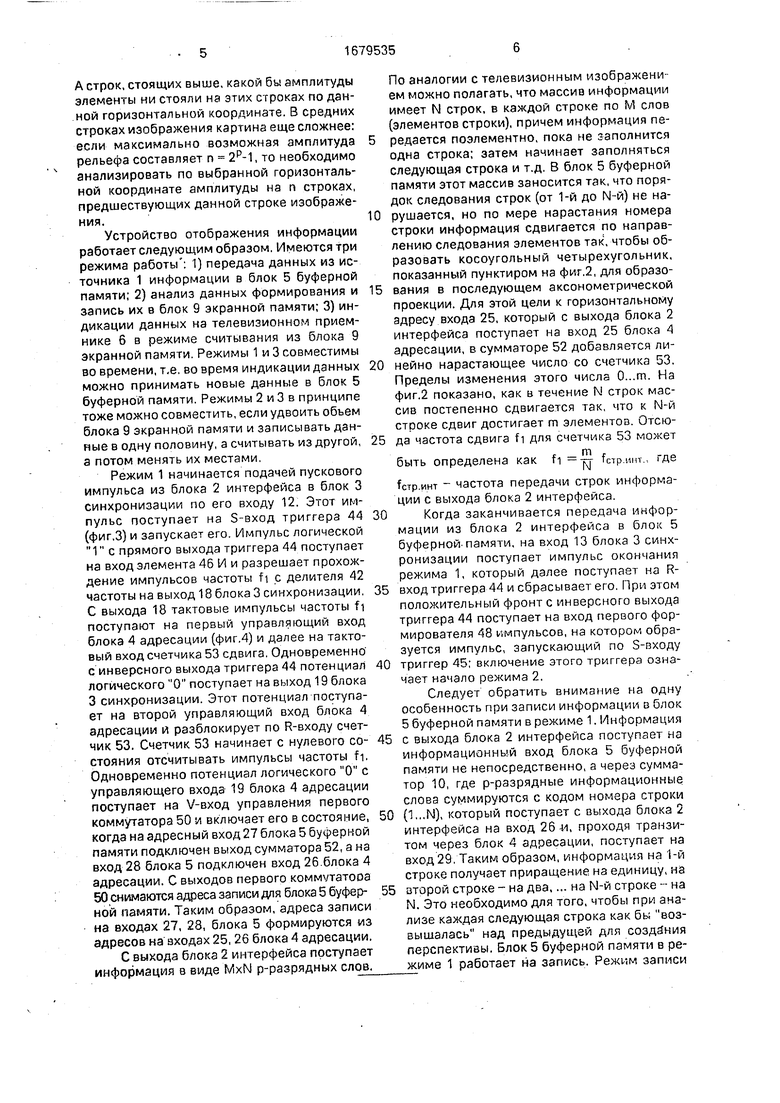

Принцип работы устройства заключается в следующем. Имеется трехмерный массив информации, состоящий из MxN элементов, каждый из которых имеет амплитуду в пределах 0...2р-1, т.е. амплитуда отображается р-разрядным двоичным кодом. На экране телевизионного приемника 6 необходимо отобразить аксонометрическую проекцию трехмерного изображения. Очевидно, что количество элементов отображения на экране по горизонтали должно быть больше, чем М, а именно М+m, где т - горизонтальный сдвиг изображения, а по вертикали количество элементов должно быть

больше, чем N, а именно N+rt, где п 2р-1 - запас на отображение амплитуды (фиг.2). Для того чтобы выделить различие между элементами с большой амплитудой и элементами с малой амплитудой, необходимо

ввести различные либо по яркости, либо по цвету отображаемых элементов.

Изображение (фиг.2) можно рассматривать как наложение N плоских рельефов, причем первый из них, стоящий на первой

строке снизу, частично закрывает собой второй рельеф, стоящий на второй строке снизу; второй рельеф, в свою очередь, частично закрывает собой третий, стоящий на третьей строке, и т.д. Но при этом каждый следующий рельеф сдвинут на один элемент вверх по

отношению к предыдущему рельефу и на некоторое расстояние вправо. Ясно, что элемент большой амплитуды (например, А), стоящий на первой строке, закроет собой

А строк, стоящих выше, какой бы амплитуды элементы ни стояли на этих строках по данной горизонтальной координате. В средних строках изображения картина еще сложнее: если максимально возможная амплитуда рельефа составляет п 2р-1, то необходимо анализировать по выбранной горизонтальной координате амплитуды на п строках, предшествующих данной строке изображения.

Устройство отображения информации работает следующим образом. Имеются три режима работы : 1) передача данных из источника 1 информации в блок 5 буферной памяти; 2) анализ данных формирования и запись их в блок 9 экранной памяти; 3) индикации данных на телевизионном приемнике 6 в режиме считывания из блока 9 экранной памяти. Режимы 1 и 3 совместимы во времени, т,е, во время индикации данных можно принимать новые данные в блок 5 буферной памяти. Режимы 2 и 3 в принципе тоже можно совместить, если удвоить объем блока 9 экранной памяти и записывать данные в одну половину, а считывать из другой, а потом менять их местами.

Режим 1 начинается подачей пускового импульса из блока 2 интерфейса в блок 3 синхронизации по его входу 12. Этот импульс поступает на S-вход триггера 44 (фиг.З) и запускает его. Импульс логической 1 с прямого выхода триггера 44 поступает на вход элемента 46 И и разрешает прохождение импульсов частоты fi с делителя 42 частоты на выход 18 блока 3 синхронизации. С выхода 18 тактовые импульсы частоты fi поступают на первый управляющий вход блока 4 адресации (фиг.4) и далее на тактовый вход счетчика 53 сдвига. Одновременно с инверсного выхода триггера 44 потенциал логического О поступает на выход 19 блока 3 синхронизации. Этот потенциал поступает на второй управляющий вход блока 4 адресации и разблокирует по R-входу счетчик 53. Счетчик 53 начинает с нулевого со- стояния отсчитывать импульсы частоты fi. Одновременно потенциал логического О с управляющего входа 19 блока 4 адресации поступает на V-вход управления первого коммутатора 50 и включает его в состояние, когда на адресный вход 27 блока 5 буферной памяти подключен выход сумматора 52, а на вход 28 блока 5 подключен вход 26 блока 4 адресации. С выходов первого комм /татооа 50 снимаются адреса записи для блока 5 буфер- ной памяти. Таким образом, адреса записи на входах 27, 28, блока 5 формируются из адресов на входах 25, 26 блока 4 адресации.

С выхода блока 2 интерфейса поступает информация в виде MxN р-разрядных слов.

По аналогии с телевизионным изображени ем можно полагать, что массив информации имеет N строк, в каждой строке по М слов (элементов строки), причем информация передается поэлементно, пока не заполнится одна строка; затем начинает заполняться следующая строка и т.д. В блок 5 буферной памяти этот массив заносится так, что порядок следования строк (от 1-й до N-й) не нарушается, но по мере нарастания номера строки информация сдвигается по направлению следования элементов так, чтобы образовать косоугольный четырехугольник, показанный пунктиром на фиг.2, для образования в последующем аксонометрической проекции. Для этой цели к горизонтальному адресу входа 25, который с выхода блока 2 интерфейса поступает на вход 25 блока 4 адресации, в сумматоре 52 добавляется линейно нарастающее число со счегчика 53. Пределы изменения этого числа О...т. На фиг.2 показано, как в течение строк массив постепенно сдвигается так, что к N-й строке сдвиг достигает m элементов. Отсюда частота сдвига fi для счетчика 53 может

быть определена как fi -Д Тстрипт где

fcip инт - частота передачи строк информации с выхода блока 2 интерфейса.

Когда заканчивается передача информации из блока 2 интерфейса в блок 5 буферной памяти, на вход 13 блока 3 синхронизации поступает импульс окончания режима 1, который далее поступает на R- вход триггера 44 и сбрасывает его. При этом положительный фронт с инверсного выхода триггера 44 поступает на вход первого формирователя 48 импульсов, на котором образуется импульс, запускающий по S-входу триггер 45; включение этого триггера означает начало режима 2.

Следует обратить внимание на одну особенность при записи информации в блок 5 буферной памяти в режиме 1. Информация с выхода блока 2 интерфейса поступает на информационный вход блока 5 буферной памяти не непосредственно, а через сумматор 10, где р-разрядные информационные слова суммируются с кодом номера строки (1...N), который поступает с выхода блока 2 интерфейса на вход 2641, проходя транзитом через блок 4 адресации, поступает на вход 29. Таким образом, информация на 1-й строке получает приращение на единицу, на второй строке - на два,... на N-й строке - на N. Это необходимо для того, чтобы прк анализе каждая следующая строка как бы возвышалась над предыдущей для создания перспективы. Блок 5 буферной памяти в режиме 1 работает на запись. Режим записи

обеспечивается подачей логического О на WR-вход управления записью (считыванием) с выхода 15 блока 3 синхронизации, где этот логический О снимается с прямого выхода триггера 45.

Режим 2 (или режим анализа) и формирование начинаются сразу после окончания режима 1 запуском триггера 45 блока 3 синхронизации. С помощью этого триггера формируются четыре выходных сигнала блока 3 синхронизации:

1)на выходе 15 появляется сигнал логический 1, который, поступая на WR-вход блока 5 буферной памяти, переводит его в режим считывания и, поступая на третий вход блока 8 построчного формирования изображения, открывает элемент 62 И;

2)на выходе 20 появляется сигнал логического О, который, поступая на третий управляющий вход блока 4 адресации, подается науправляющий V-вход второго коммутатора 51, при этом к информационным выходам 32, 33 второго коммутатора 51 подключаются информационные входы 30, 31 (адреса записи блока 9 экранной памяти);

3)на выходе 23 блока 3 появляются импульсы втйрого делителя 43 частоты, которые проходят через элемент 47 И, открытый логической 1.с прямого выхода триггера 45; эти импульсы поступают на четвертый вход блока 8 построчного формирования изображения, а в нем - на тактовый С-вход счетчика 59 номера строки;

4)на выходе 24 блока 3 в момент включения триггера 45 появляется импульс, сформированный вторым формирователем 49 импульсов; этот импульс поступает на второй управляющий вход блока 8 построчного формирования изображения, а в нем - на R-входы установки в нуль счетчика 55 импульсов и счетчика 60 номера элемента.

Кроме того, поскольку с началом режима 2 триггер 44 сбрасывается в нуль, на выходе 19 блока 3 синхронизации появляется сигнал логической 1, который, поступая на второй управляющий вход блока 4 адресации, блокирует счетчик 53 сдвига и переводит первый коммутатор 50 в режим, когда на входы 27, 28 блока 5 проходят адресные сигналы, поступившие на входы 30, 31 блока 4 адресации (адреса считывания блока 5 буферной памяти). Совокупность указанных сигналов связана с переводом блока 5 буферной памяти в режим считывания, а блока 9 экранной памяти - в режим записи. Поскольку адреса считывания блока 5 буферной памяти и адреса записи блока 9 экранной памяти совпадают с выставленным на входе 31, то это значит, что совпадает номер элемента j по горизонтали.

Отличие адресов считывания блока 5 (выход 35) и считывания блока 9 (вход 30) вызвано тем, что при анализе из блока 5 считывается несколько элементов по вертикали, а в блок

9 записывается только один из них,

Пространственное изображение (см. фиг,2а) можно представить как наложение набора рельефов, как бы вырезанных из тонкого материала и располагающихся по

0 строкам, причем полностью виден рельеф первой строки, рельеф второй строки поднят вверх относительно рельефа первой строки на один элемент по вертикали, т.е. на одну строку телевизионного изображения,

5 рельеф третьей строки поднят на два элемента и т.д. Кроме того, рельефы постепенно смещаются по горизонтали с дискретностью в один элемент по горизонтали (например, если рельеф 192, а мэксималь0 ный сдвиг по горизонтали m 64, то сдвиг на один элемент по горизонтали приходится на каждые 192/64 3 строки. Отсюда ясно, для чего нужно перед записью массива данных в блок 5 буферной памяти суммировать

5 амплитудную информацию с адресом номера строки, а к горизонтальному адресу добавлять прогрессивно увеличивающийся сдвиг.

Анализ и формирование изображения

0 сводится к тому, чтобы определить распределение яркости (или цвета) на любой 1-й строке телевизионного изображения телевизионного приемника б в зависимости от информации в предыдущих п строках

5 (рельефах) массива, записанного в блоке 5 буферной памяти. Фиг.6 иллюстрирует упрощенный случай п 4. Яркость изображения на i-й строке определяется набором амплитуд информации на строках 1а, 2а, За,

0 4а. Пусть j 1. На строке 4а амплитуда А4а О, на строке За Аза 2. Номер строки (За) показывает, на сколько элементов по вертикали отстоит данная строка от анализируемой (i-й). Для того чтобы дотянуться до 1-й

5 строки, нужно иметь амплитуду Азз не меньше трех, т.е. строка За при анализе отбрасывается. На строке 2а А2а 0 и, наконец, на строке 1а Aia 3, т.е. достает до i-й строки (даже с избытком). Но поскольку 1-я строка

0 является для строки 1а следующей, то ее накрывает уже первый элемент амплитуды. Поэтому в 1-й строке блока 9 экранной памяти записывают амплитуду Ап при j 1, На фиг.бг показан при j - 1 граф просмотра

5 строк информации по четырем позициям. Например, при j 7 при анализе 1-й строки А4а 4, т.е. сразу достает до 1-й строки, поэтому при j 7 записывают амплитуду AI 4. Граф просмотра строк на фиг.6 при fa -1 состоит всего из одной позиции.

При переходе к (1+1}-й строке анализируется информация на строках 16,26,36,46; при переходе к (1+2)-й строке анализируется информация на строках 1в, 2в, Зв, 4в, и т.д.

Таким образом, алгоритм анализа еле- дующий: на 1-й строке изображения в j-м элементе по горизонтали анализируются амплитуды информации в предыдущих п строках массива, начиная с самой нижней. При анализе амплитуда в (1-п)-й строке массива сравнивается с числом -п; если A (i-n)j2: (l-n), то в блок 9 экранной памяти записывается по адресу I амплитуда Alj l-n.

Этот алгоритм в блоке 8 организован следующим образом. Номер анализируемой строки (рельефа) i определяется состоянием счетчика 55. В начале режима 2 счетчик 55 устанавливается в нуль по R- входу с входа 24 блока 8. Номер анализиру- емого элемента j строки определяется состоянием счетчика 60 номера элемента, который также в начале режима 2 устанавливается в нуль. Работа блока 8 для некоторых произвольных значений I, J происходит следующим образом. В устройстве имеется вход 11 для задания амплитудного параметра, по которому задается число, определяющее максимальную амплитуду Пмакс информации по вертикали (на фиг.2 обозначено п, при этом исходят из того, чтобы на экране поместился рельеф самой верхней строки - фиг.2в). Это число поступает на второй В-вход второго узла 57 сравнения кодов, на первый А-вход которо- го поступает число I с выхода счетчика 55. Вначале можно рассмотреть общий случай, когда i пмакс Тогда на выходе А В второго узла 57 сравнения кодов появляется логическая 1, поступающая на управляю- щий V-вход коммутатора 58. По этому сигналу коммутатор 58 пропускает на выход число со своего В-входа, а именно Пмакс, которое поступает на информационный D-вход счетчика 59 номера строки. По V-входу разреше- ния записи счетчика 59 поступает импульс с выхода элемента 63 задержки, и число пмакс записывается в счетчик 59. На выходе вычитающего узла 56 появляется число i-Пмакс. Через выход 35 блока 8 это число поступает на третий информационный вход блока 4 адресации и через первый коммутатор 50 используется как адрес номера строки блока 5 буферной памяти, работающего в режиме считывания. Информация с блока 5 буферной памяти поступает на вход 34 блока 8, т.е. на А-вход первого узла 54 сравнения, где сравнивается с числом 1-пМакс с выхода вычитающего узла 56. Если амплитуда информационного сигнала с блока 5 меньше чем разность I - Пмакс, то значит, что сигнал на (1-Пмвкс)-й строке не достает до 1-й анализируемой строки и нужно переходить на (1-пМвкс+1)-ю строку в блоке 5 буферной памяти. На выходе первого узла 54 сравнения сохраняется логический О, запись в счетчик 59 не производится, зато очередной импульс с выхода 23 блока 3 синхронизации, поступая на тактовый вход счетчика 59, работающего в режиме вычитания, переводит его в состояние пМакс-1. На выходе вычитающего узла 56 появляется число 1-Пмакс+1. По этому адресу с блока 5 выводится новая информация, которая в первом узле 54 сравнения кодов сравнивается с числом 1-пМакс+1 и т.д.. пока на каком- то очередном такте счетчика 59 узел 54 сравнения кодов не выдаст сигнал логической Г. На фиг.бг такты счетчика 59 соответствуют движению по стрелке вверх. Логическая 1 с выхода узла 54 сравнения кодов запускает формирователь 61, импул ьс которого, проходя через элемент 62 И, открытый сигналом режима 2 с выхода 15 блока 3 синхронизации, поступает на выход 36 блока 8 и далее на WR-вход разрешения записи блока 9 экранной памяти, на которой по адресу l,j на входы 30, 31 адреса записывается число i-n с выхода 35. После окончания записи на выходе элемента 63 задержки появляется импульс, по которому в счетчик

59снова записывается число Пмакс, а счетчик

60переходит в состояние J+1 - начинается анализ следующего элемента по строке (время задержки в элементе 63 больше, чем длительность импульса записи, формируемого формирователем 61 импульсов) После того, как проанализированы все М+т элементов по строке (такова емкость счетчика 60), на Р-выходе переполнения счетчика 60 появляется импульс, являющийся тактовым для счетчика 55, и тот переходит в состояние 1+1. После того как проанализированы все N+ п строк изображения (такова емкость счетчика 55), на Р-выходе переполнения счетчика 55 появляется импульс, поступающий с пятого выхода блока 8 на вход 14 блока 3 синхронизации (на R-вход триггера 45). Триггер 45 сбрасывается, и на этом заканчивается режим 2.

В начале режима 2, когда число I в счетчике 55 - малое (начинается с нуля), то 1 Пмаке. Тогда на выходе А В второго узла 57 сравнения кодов находится логический О, поступающий на управляющий V-вход коммутатора 58, который пропускает на выход число со/своего А-входа, т.е. i поступающее на информационный D-вход счетчика 59. При подаче импульса с элемента 63 задержки число записывается в счетчик 59. Тогда на выходе вычитающего узла 56 образуется Н 0, т.е. анализ и формирование начинается с самой нижней нулевой строки. Затем счетчик 59 переходит в состояние 1-1, на выходе вычитающего узла 56 i-(M) 1, и т.д.

После сброса триггера 45 бпока 3 синхронизации начинается режим 3 - индикация данных на телевизионном приемнике 6. При этом на выходе 20 блока 3 синхронизации появляется сигнал логической 1, по которому коммутатор 5 блока 4 адресации переводится в режим, когда к выходам 32, 33 подключаются входы 21, 22, снимаемые со сметчика 38 элементов строки и со счетчика 40 строк Чяока 3 синхронизации. На выходе 15 блока 3 синхронизации появляется сигнал логического О, который блокирует элемент 62 И блока 8. Таким образом, блокируется запись блока 9 экранной памяти и он работает в режиме считывания. Изображение на экране телевизионного приемника 6 имеет характер, показанный на фиг,26, где элементы массива с большой амплитудой выделяются либо яркостью, либо цветом.

Длительность режима 2( Греж.2) определяется числом анализируемых элементов изображения (IVI-i- rn) (N+n), числом тактов анализа и формирования (в среднем пмакс/2) м длительностью одного такта, которая определяется временем срабатывания вычитающего узла 56 и первого узла 54 сравнения кодов тср., т.е.

ТрЗЖ.2 (М + m) (N + П) .

Таким образом, благодаря введению сумматора 10, блока 8 построчного формирования изображения, блока 9 экранной памяти с соответствующими связями, улучшается качество изображаемой информации.

Формул.а изобрете ния 1. Устройство для отображения информации на экране телевизионного приемника, содержащее блок ввода данных, первый и зторой выходы которого подключены к первому и второму информационным входам блока адресации, причем третий и четвертый выходы блока ввода данных подключены к первому и второму управляющим входам блока синхронизации, первый которого подключен к входу разрешений записи блока буферной памяти, первый и второй адресные входы которого подключены к первому л второму выходам блока адресации, второй и третий выходы ёлока синхронизации подключены к первому и второму емнхровходам телевизионного

приемника, информационный вход которого подключен к выходу преобразователя кодов, отличающееся тем, что, с целью повышения качества отображаемой информации за счет обеспечения возможности отображения рельефных аксонометрических изображений, в него введены блок построчного формирования изображения блок экранной памяти и сумматор, первый

0 информационный вход которого подключен к пятому выходу блока ввода данных, второй информационный вход сумматора подключен к третьему выходу блока адресации, выход сумматора подключен к информационному

5 входу блока буферной памяти, выход которого подключен к первому информационному входу блока построечного формирования изображения, второй информационный вход которого является установочным вхо0 дом устройства, первый выход блока построчного формирования изображения «подключен к информационному входу блока экранной памяти и к третьему информационному входу блока адресации, четвертый и

5 пятый информационные входы которого подключены к второму и третьему выходам блока построчного формирования изображения, четвертый выход которого подключен к входу разрешения записи блока

0 экранной памяти, выход которого подключен к информационному входу преобразователя кодов, первый и второй адресные входы блока экранной памяти подключены к четвертому и пятому выходам блока адре5 сации, первый, второй и третий синхровхо- ды и шестой и седьмой информационные входы которого подключены соответственно к четвертому, пятому, шестому, седьмому и восьмому выходам блока синхронизации,

0 девятый и десятый выходы которого подключены к первому и второму управляющим входам блока построечного формирования изображения, пятый выход которого подключен к третьему управляющему входу

5 блока синхронизации, первый выход которого подключен к третьему управляющему входу блока i построчного формирования изображения.

Фиг. 2

Фиг.З

Фиг 4

J12345678910

4

3 $2

I

Фиг. 5

| Патент США № 4475104, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Яблонский Ф.М., Троицкий Ю.В | |||

| Средства отображения информации | |||

| М.: Высшая школа, 1985, с | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-09-23—Публикация

1989-04-25—Подача