Изобретение относится к цифровой вычислительной технике и может быть исполь- зовано для обработки логической информации, например в системах распознавания.

Цель изобретения - расширение функциональных возможностей классификатора за счет произвольного выбора числа классов от 1 до N (N - размерность входного вектора) и количества единичных бит в каждом классе от 1 до т-1 (т - разрядность настроечных входов группы).

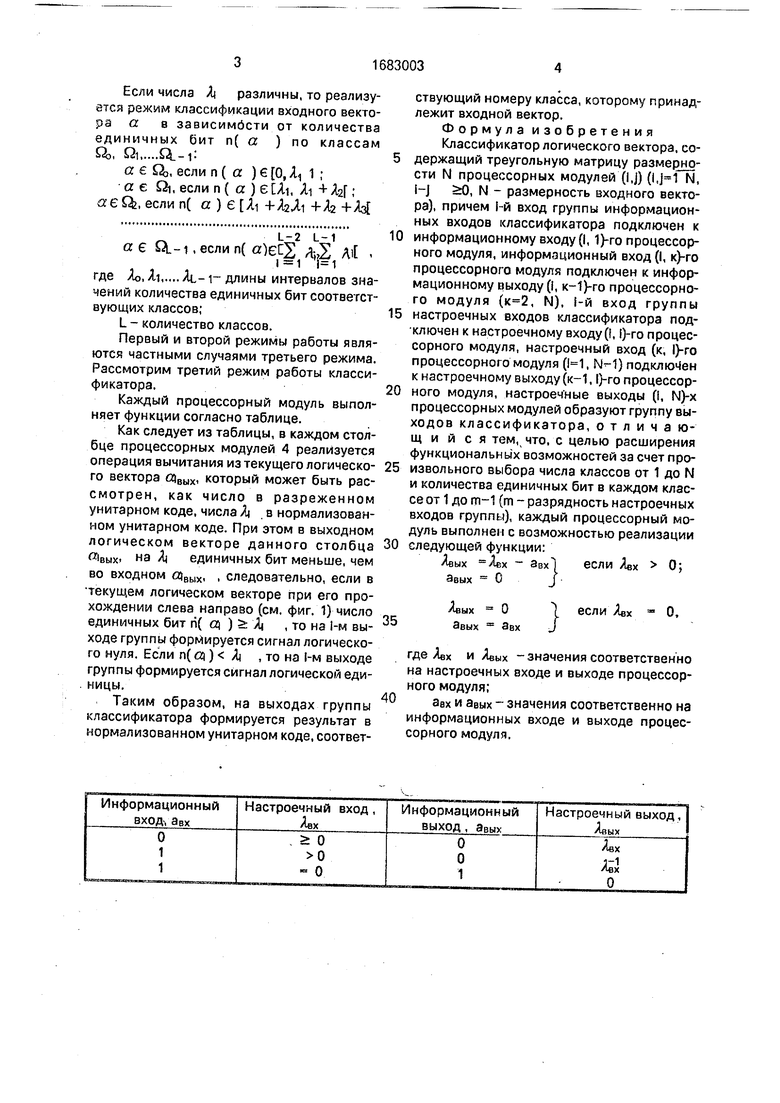

На фиг. 1 приведена структурная схема классификатора; на фиг. 2 - процессорный модуль.

Классификатор (фиг. 1) содержит группу информационных входов 1| (1, N), группу настроечных входов 2|, группу выходов 3i и треугольную матрицу процессорных модулей 4i (1,, I-J 0), Каждый процессорный модуль 4ij (фиг. 2) содержит инвертор 5, элемент И 6, информационные вход 7 и выход 8, настроечные вход 9 и выход 10, логические блоки 11i (, т-1), каждый из которых, в свою очередь, содержит элемент И 12 и элемент ИЛИ 13,

Классификатор логического вектора является настраиваемым устройством. Настройка осуществляется подачей на группу i зстроечных входов чисел ,- Дм , задан- в нормализованном унитарном коде Д| {н-ь 1|2...-.....1|п|Различнь1е значения этих чисел соответствуют различным режимам работы.

Если Дт Д2.., то реализуется режим подсчета единичных бит во входном векторе.

Если Д1 Д2.. то реализуется деление количества единичных бит n( a ) входного вектора а на число Д) .

О

ы

Если числа AI различны, то реализуется режим классификации входного вектора а в зависимбсти от количества единичных бит n( a ) по классам Оэ, QI.....Q,а е Оо, если п ( а ) € О, Я1 1 ;

а е QI, если п ( а ) е Ai, Ai + aeQ, если п( а ) 6 Ai + A2,Ai -fAa +Лз

L-2 L-1

а е flL-i, если n( GOeQJ AI I - j j«

где АО, AiAt-1- длины интервалов значений количества единичных бит соответствующих классов;

L - количество классов.

Первый и второй режимы работы являются частными случаями третьего режима. Рассмотрим третий режим работы классификатора.

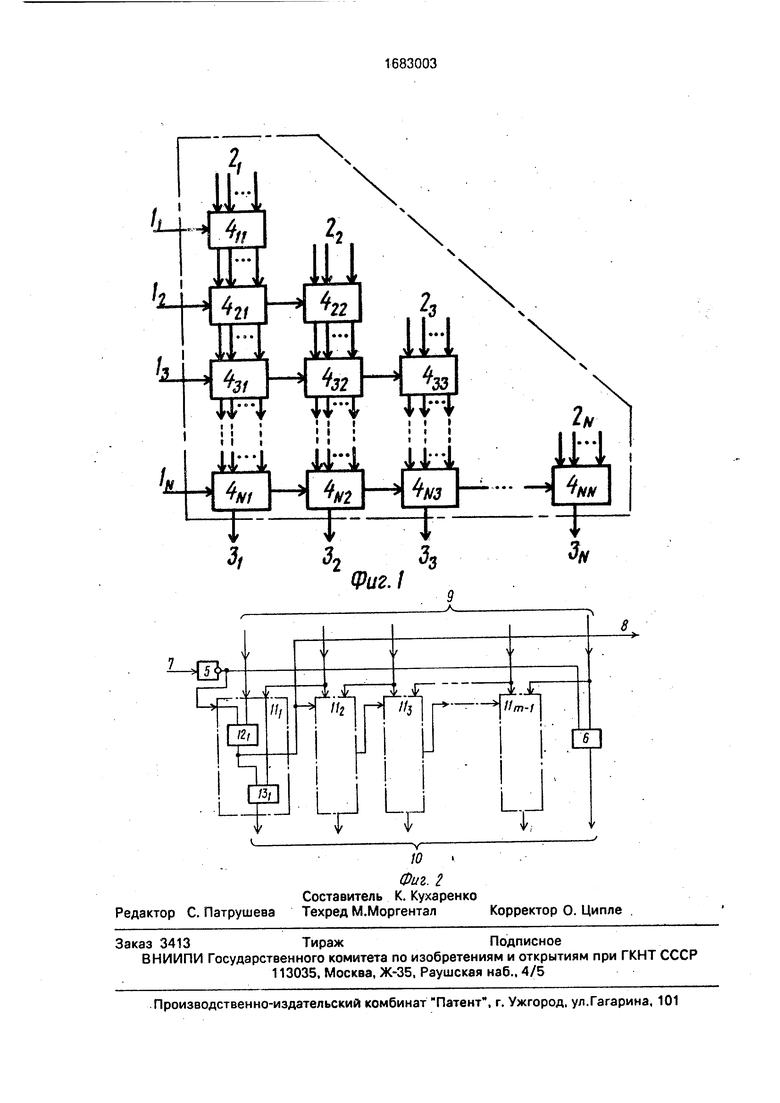

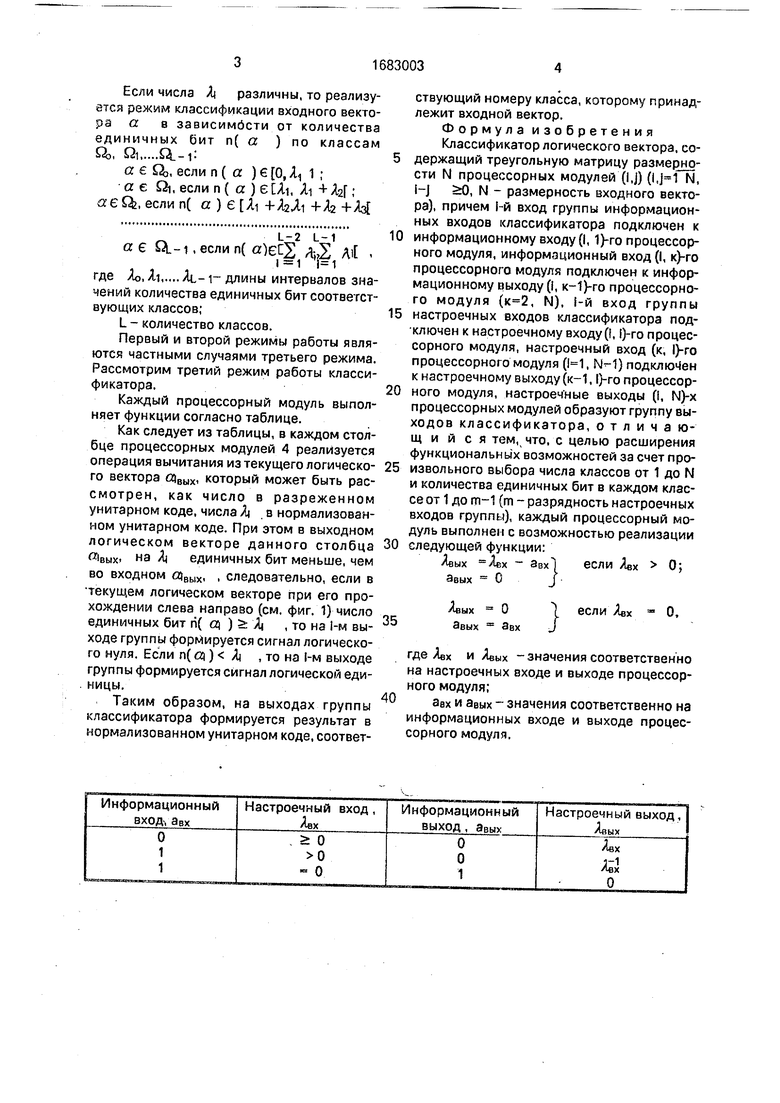

Каждый процессорный модуль выполняет функции согласно таблице.

Как следует из таблицы, в каждом столбце процессорных модулей 4 реализуется операция вычитания из текущего логического вектора 05ВЫХ, который может быть рассмотрен, как число в разреженном унитарном коде, числа k в нормализованном унитарном коде. При этом в выходном логическом векторе данного столбца Л|вых« на AI единичных бит меньше, чем во входном О)вых. , следовательно, если в текущем логическом векторе при его прохождении слева направо (см. фиг. 1) число единичных бит ri( а ) AJ , то на l-м выходе группы формируется сигнал логического нуля. Если п( а) fa , то на 1-м выходе группы формируется сигнал логической единицы.

Таким образом, на выходах группы классификатора формируется результат в нормализованном унитарном коде, соответствующий номеру класса, которому принадлежит входной вектор.

Формула изобретения Классификатор логического вектора, содержащий треугольную матрицу pasMepj p- сти N процессорных модулей (l,j) (l, N, i-J 0, N - размерность входного вектора), причем 1-й вход группы информационных входов классификатора подключен к

информационному входу (1,1)-го процессорного модуля, информационный вход (I, к)-го процессорного модуля подключен к информационному выходу (I, к-1}-го процессорного модуля (, N). 1-й вход группы

настроечных входов классификатора под- ключен к настроечному входу (1,1)-го процессорного модуля, настроечный вход (к, l)-ro процессорного модуля (, N-1) подключен к настроечному выходу (к-1, fj-ro процессорного модуля, настроечные выходы (I, N)-x процессорных модулей образуют группу выходов классификатора, отличающийся тем, что, с целью расширения функциональных возможностей за счет произвольного выбора числа классов от 1 до N и количества единичных бит в каждом классе от 1 до m-1 (m - разрядность настроечных входов группы), каждый процессорный модуль выполнен с возможностью реализации

следующей функции:

Леых Аех - Звх если Аех 0; Оj

Эвых

Авых Эвых

О Эвх

}

если Лвх О,

где Дех и Авых -значения соответственно на настроечных входе и выходе процессорного модуля;

аах и авых - значения соответственно на информационных входе и выходе процессорного модуля.

3233

Фиг. I

ЛГ

9 л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для комбинационно-логического управления сложными системами | 1987 |

|

SU1539775A1 |

| Устройство для вычисления симметричных булевых функций | 1980 |

|

SU959064A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2004 |

|

RU2284568C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| ПОИСК ФОРМЫ ПИРАМИДАЛЬНОГО ВЕКТОРНОГО КВАНТОВАТЕЛЯ | 2015 |

|

RU2665898C2 |

| ПОИСК ФОРМЫ ПИРАМИДАЛЬНОГО ВЕКТОРНОГО КВАНТОВАТЕЛЯ | 2015 |

|

RU2762329C2 |

| Устройство для нахождения оптимального вектора решения системы линейных неравенств | 1985 |

|

SU1315996A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Устройство для обработки логической информации | 1987 |

|

SU1446616A1 |

| Устройство для определения экстремальных чисел | 1990 |

|

SU1753468A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки логической информации, например, в устройствах распознавания, Цель изобретения - расширение функциональных возможностей за счет произвольного выбора числа классов от 1 до N (N - размерность входного вектора) и количества единичных бит в каждом классе от 1 до т-1 (т - разрядность настроечных входов группы). Классификатор содержит треугольную матрицу процессорных модулей. Цель изобретения достигается за счет возможности перенастройки процессорных модулей. 2 ил.

;

. -.

//Л Н/ Г

I

Р

Р

| Ячейка однородной среды | 1977 |

|

SU664169A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Фет Я, И | |||

| Специализированные однородные структуры | |||

| Синтез схем на основе цифровых компрессоров, - Препринт № 27, Новосибирск; Институт математики СО АН СССР | |||

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1991-10-07—Публикация

1989-07-20—Подача