113

Изобретение относится к автоматике и вычислительной технике и может быть использовано для решения задач, которые сводятся к нахождению решения произвольной конечной системы линейных неравенств, в частности задач классификации и распознавания образов, синтеза оптимальных структур пороговых элементов, проектирования линейных электрических схем, например блоков взвешенного суммирования с оптимальными дараметрами, управления адаптивными цифровыми фильтрами.

Целью изобретения- является повышение быстродействия устройства за счет повьшения скорости движения текущего вектора структуры;

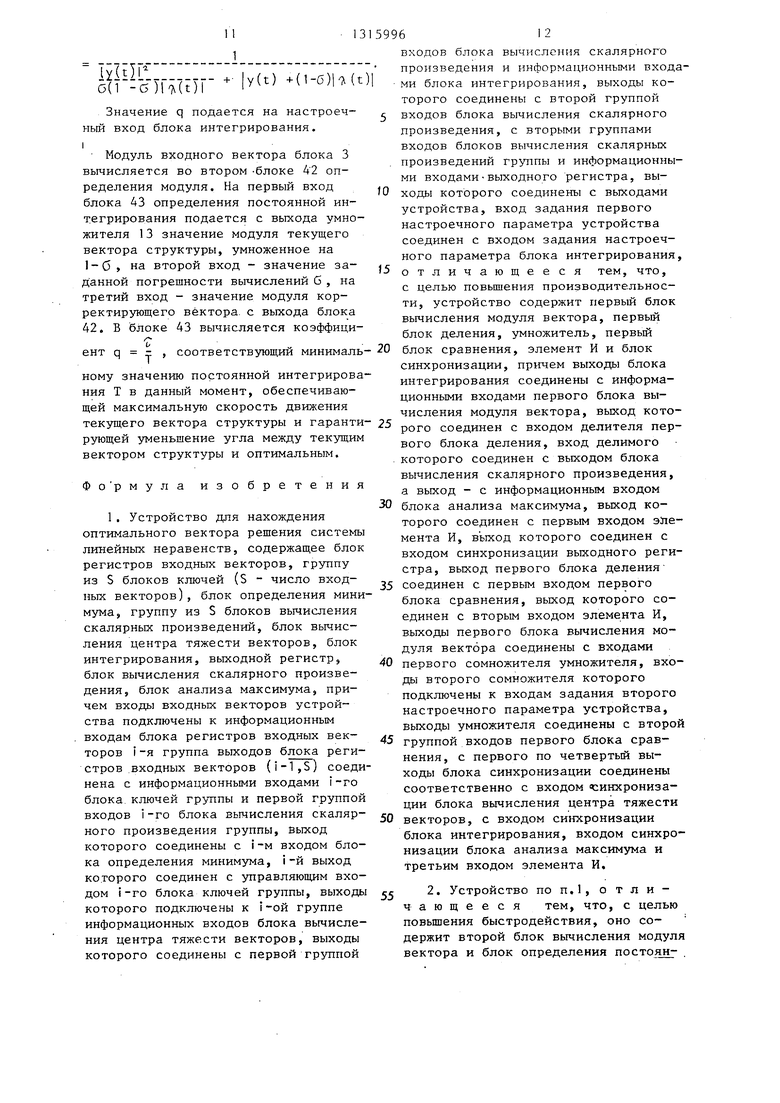

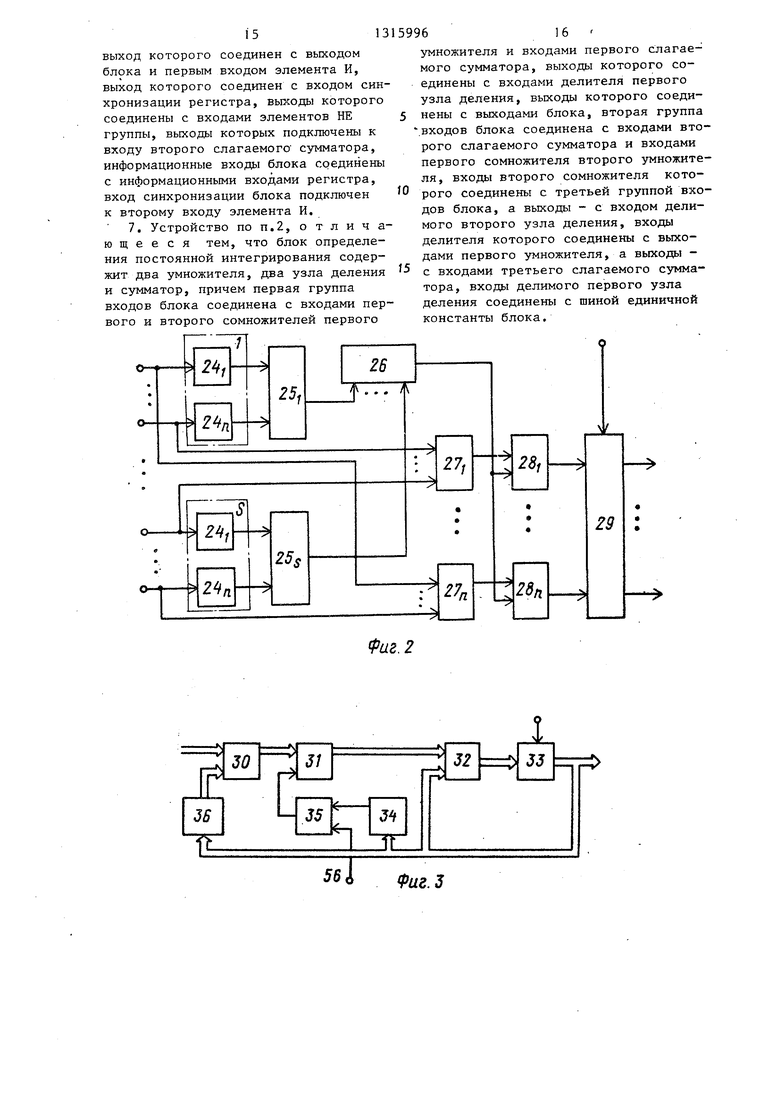

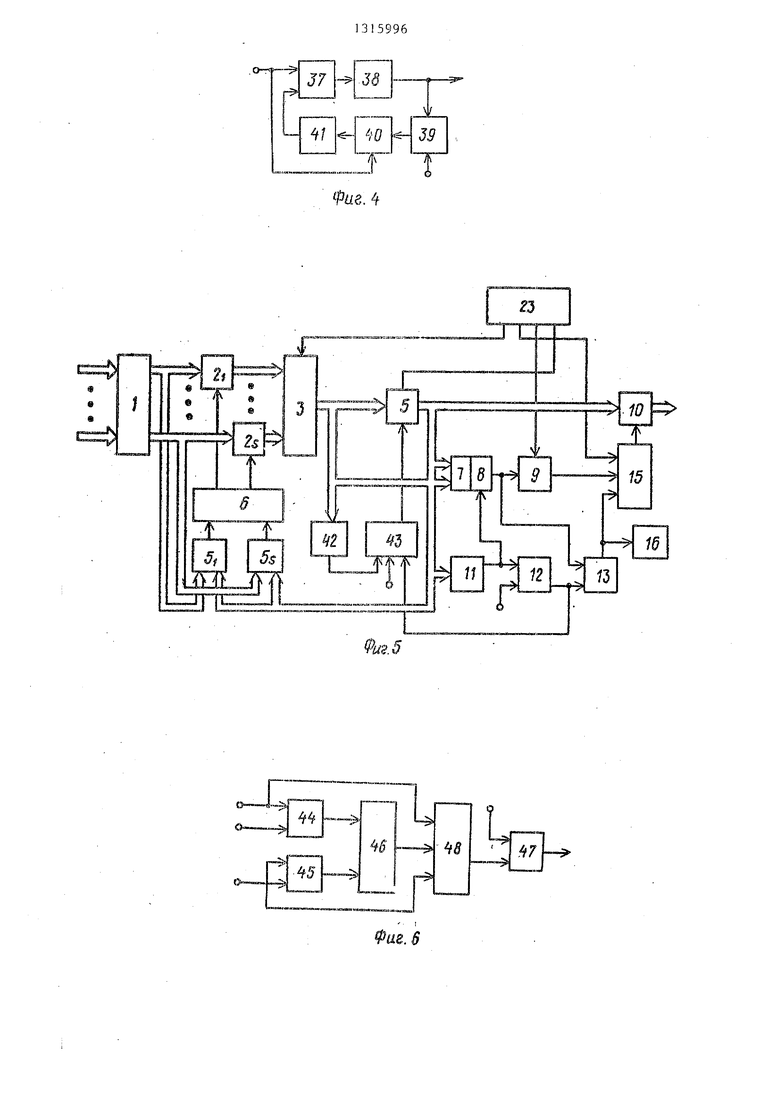

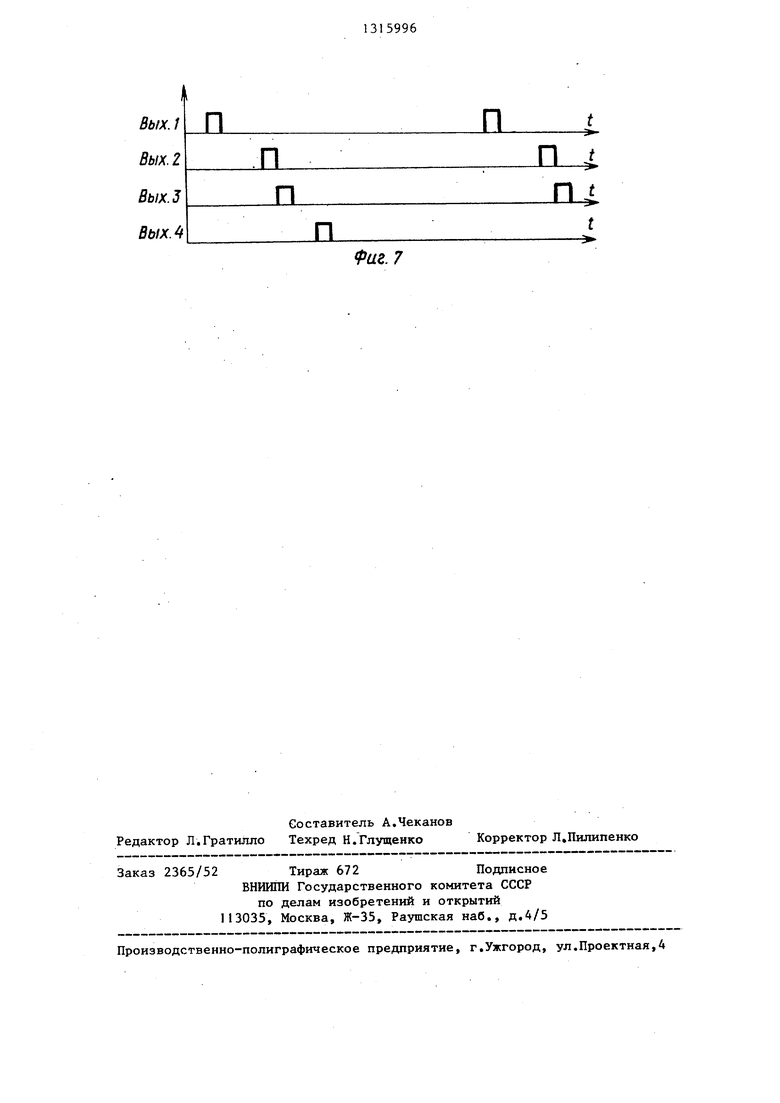

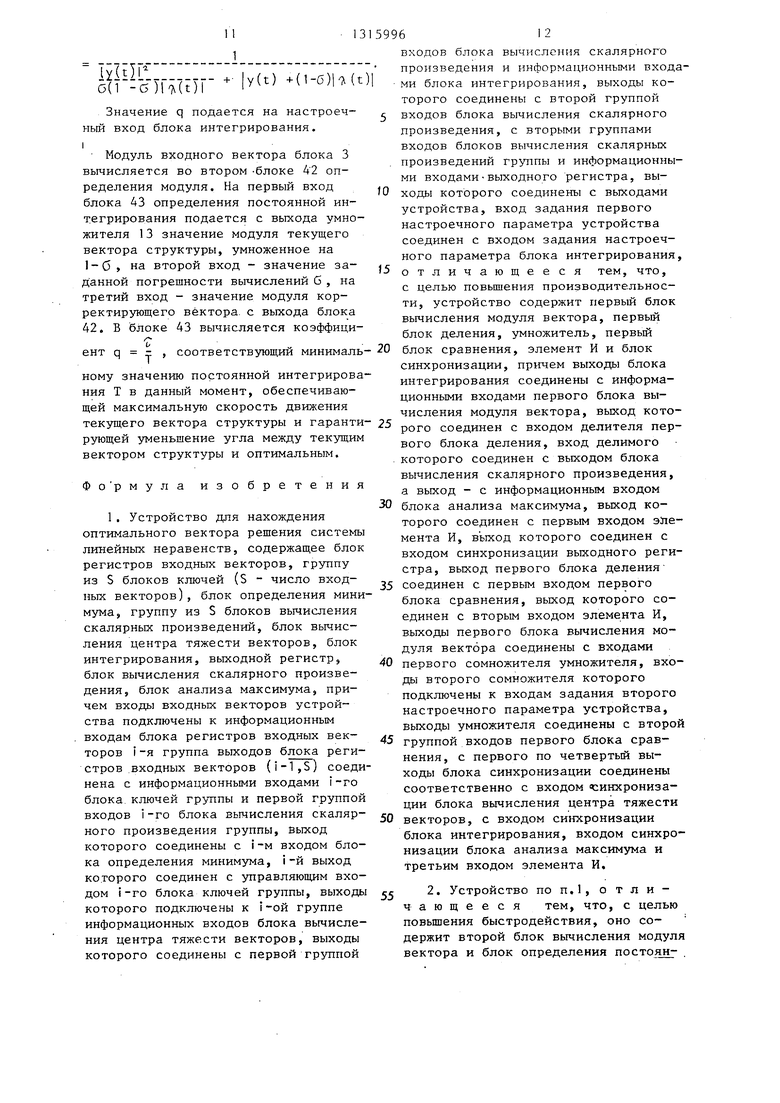

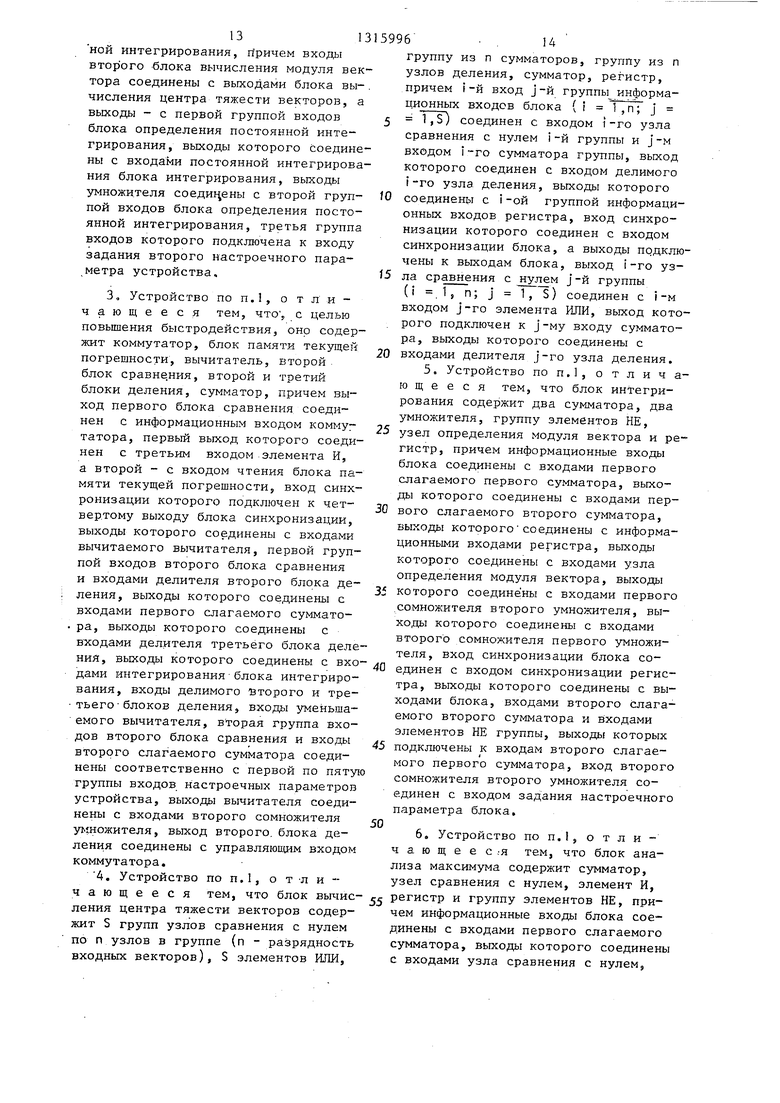

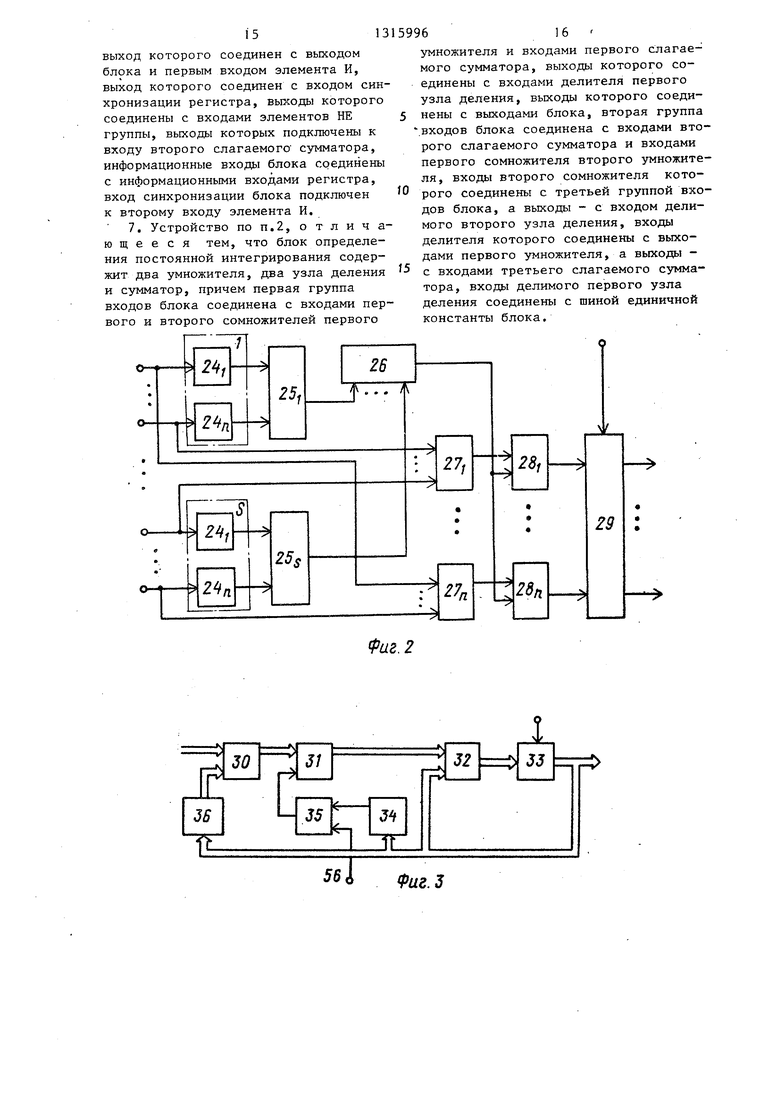

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока вычисления центра тяжести векторов; на фиг.З - структурная схема блока интегрирования; на фиг.4 - структурная схема блока анализа максимума; на фиг,5 - схема подключения второго блока вычисления модуля вектора и блока вычисления постоянной интегрирования к устройству; на фиг.6 - блок-схема определения постоянной интегрирования; на фиг.7 - временная диаграмма, формируемая блоком синхронизации.

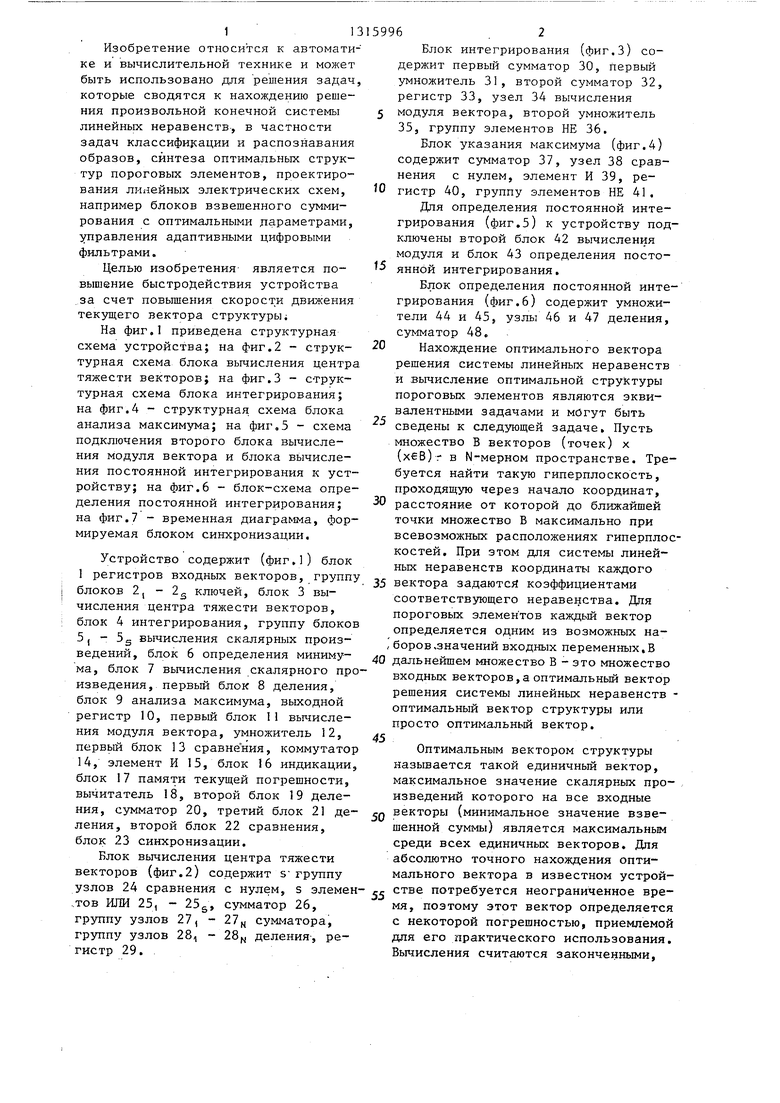

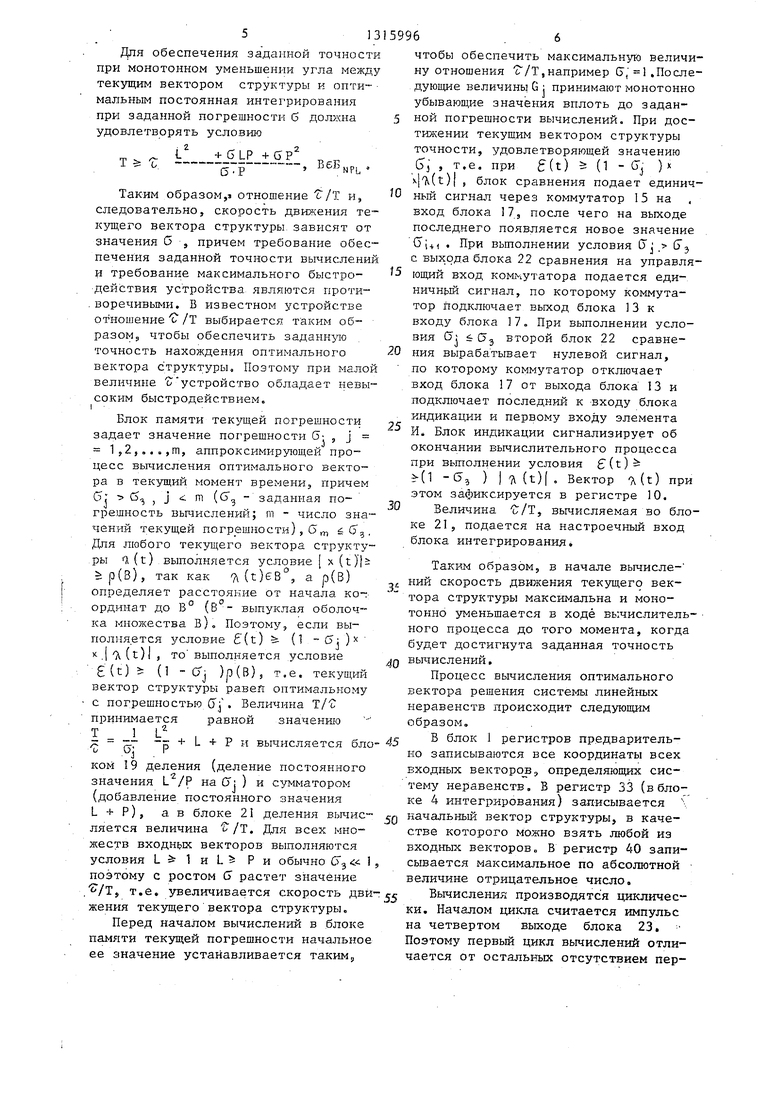

Устройство содержит (фиг.1) блок 1 регистров входных векторов, группу блоков 2, - 2 ключей, блок 3 вычисления центра тяжести векторов, блок 4 интегрирования, группу блоков 5, - 5д вычисления скалярных произведений, блок 6 определения минимума, блок 7 вычисления скалярного произведения, первый блок 8 деления, блок 9 анализа максимума, выходной регистр 10, первый блок II вычисления модуля вектора, умножитель 12, первый блок 13 сравне ния, коммутатор 14, элемент И 15, блок 16 индикации, блок 17 памяти текущей погрешности, вычитатель 18, второй блок 19 деления, сумматор 20, третий блок 21 деления, второй блок 22 сравнения, блок 23 синхронизации.

Блок вычисления центра тяжести векторов (фиг.2) содержит s группу узлов 24 сравнения с нулем, s элемен ..тов ИЛИ 25, - 25g, сумматор 26, группу узлов 27( - 27 сумматора, группу узлов 28, - 28,, деления, регистр 29.

6 . 2

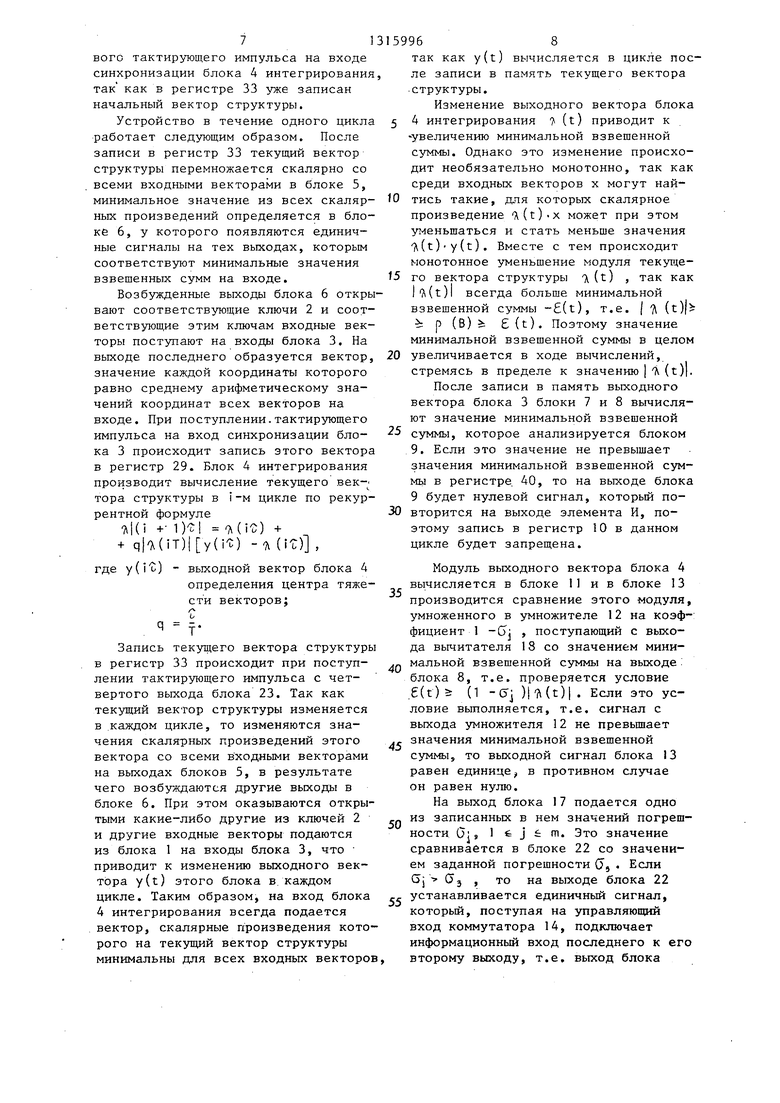

Блок интегрирования (фиг.З) содержит первый сумматор 30, первый умножитель 31, второй сумматор 32, регистр 33, узел 34 вычисления

модуля вектора, второй умножитель 35, группу элементов НЕ 36.

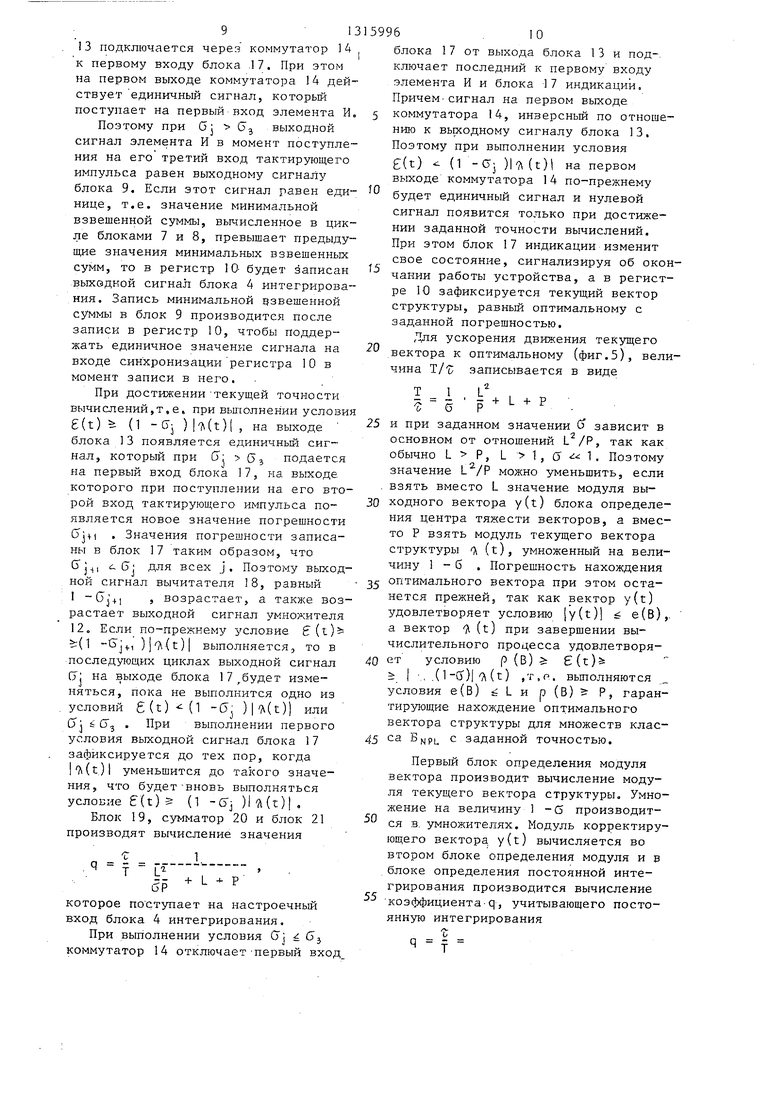

Блок указания максимума (фиг.4) содержит сумматор 37, узел 38 сравнения с нулем, элемент И 39, регистр 40, группу элементов НЕ 41.

Для определения постоянной интегрирования (фиг.5) к устройству подключены второй блок 42 вычисления модуля и блок 43 определения постоянной интегрирования.

Блок определения постоянной интегрирования (фиг.6) содержит умножители 44 и 45J узлы 46 и 47 деления, сумматор 48,

Нахождение оптимального вектора решения системы линейных неравенств и вычисление оптимальной структуры пороговых элементов являются эквивалентными задачами и могут быть

сведены к следующей задаче. Пусть множество В векторов (точек) х ()г в N-мерном пространстве. Требуется найти такую гиперплоскость, проходящую через начало координат,

расстояние от которой до ближайшей точки множество В максимально при всевозможных расположениях гиперплоскостей. При этом для системы линейных неравенств координаты каждого

вектора задаются коэффициентами соответствующего неравенства. Для пороговых элементов каждый вектор определяется одним из возможных на- боров.значений входных переменных,Б

дальнейшем множество В - это множество входных векторов,а оптимальньш вектор решения системы линейных неравенств - оптимальный вектор структуры или просто оптимальный вектор.

Оптимальным вектором структуры

называется такой единичный вектор, максимальное значение скалярных произведений которого на все входные векторы (минимальное значение взвешенной суммы) является максимальным среди всех единичных векторов. Для абсолютно точного нахождения оптимального вектора в известном устройстве потребуется неограниченное время, поэтому этот вектор определяется с некоторой погрешностью, приемлемой для его практического использования. Вычисления считаются законченными,

9v(0)B°; л(г) +

когда минимальное значение взвешенной суммы для текущего вектора структуры отличается от минимальной взвешенной суммы для оптимального вектора не более чем на заданное зна- 5 где В - выпуклая оболочка множе1 Т

г (t) y(t) - TiCt) dt,

чение погрешности.

Так как оптимальный вектор априорно неизвестен, то в известном устройстве невозможно определить в ходе работы устройства с какой погрешностью текущий вектор структуры равен оптимальному. Поэтому считывание показаний производится только через такое время, по истечении которого гарантируется, что заданна величина точности достигнута хотя бы один раз. Определение этого времени для каждого конкретного множества входных векторов является сложной задачей. Поэтому оценить это время можно только косвенным путем. Один из таких путей заключается в том, что все множества входных векторов распределяются по классам и по параметрам, характеризующим тот или иной класс, определяется время, гарантирующее достижение заданной точности для всех множеств данного класса.

Для определения классов множеств введем характеристики произвольного множества В входных векторов х: N(B) - размерность векторов из В; р(В) - минимальная взвешенная сумма для оптимального вектора структуры: е(В) max х| , а)(В) max 1х;| ,

Х.Е В

хЕВ 1 i N(B)

где х- - i-я координата вектора х.

Не уменьшая общности, можно счи- ,тать,что всегда о(В)1.Тогда класс множеств БЛР| можно охарактеризовать тремя действительными числами N,P,L, удовлетворяющими условиям: N - целое положительное число, OiPi-L, I LfeN/Tl. Множество В принадлежит классу Б р, если

СО(В) 1; М(В) N;p(B)5 Р; е(В) L.

Скоростъ движения текущего вектора структуры зависит от некоторых параметров устройства. Все реальные интеграторы обладают постоянной времени интегрирования - Т. Кроме того, в специализированных аналого- цифровых устройствах для выполнения любой вычислительной операции требуются конечные затраты времени. Поэтому текущий вектор структуры появляется на выходе устройства с некоторой задержкой С . Погрешность, с которой устройство аппроксимирует процесс вычисления оптимального вектора, а следовательно, и погрешность нахождения этого вектора определяются отношением /Т, Причем уменьшение величины ZT /Т ведет к уменьшению еп погрешности нахождения оптимального вектора структуры. Однако, чем меньше IJ/T, тем меиьше скорость движения текущего вектора структуры. В специализированных устройствах время заДля того, чтобы гарантировать нахождение оптимального вектора структуры, необходимо, чтобы угол между ним и текущим вектором, держки € обычно не поддается регули- структуры уменьшался в ходе вычисли- рованию и является конструктивным тельного процесса. Движение текущего параметром.Поэтому величина С/Т может вектора структуры определяется вы- меняться за счет изменения постоянной ражениеминтегрирования Т.

9v(0)B°; л(г) +

е В - выпуклая оболочка м

В - выпуклая оболочка множе1 Т

г (t) y(t) - TiCt) dt,

o

5

0

5

ства В;

Т - постоянная интегрирования; y(t) - корректирующий вектор.

Вектор y(t) определяется в блоке определения центра тяжести векторов выражением

1

y(t) Г ZLx;. k S, х.,В, Ui

X(t) X; (t)-x,

где s - число векторов множества В. Погрешность б приближения произвольного текущего вектора структуры к оптимальному удобно оценивать выражением

.. Р(В) - 5(t)

,рТвТ

где {t) - минимальная взвешенная

сумма для текущего вектора структуры.

Тогда, если {t) (I-C) р(В) ,то текущий вектор структуры Л (t) равен оптимальному с погрешностью, не вышающей б .

Скоростъ движения текущего вектора структуры зависит от некоторых параметров устройства. Все реальные интеграторы обладают постоянной времени интегрирования - Т. Кроме того, в специализированных аналого- цифровых устройствах для выполнения любой вычислительной операции требуются конечные затраты времени. Поэтому текущий вектор структуры появляется на выходе устройства с некоторой задержкой С . Погрешность, с которой устройство аппроксимирует процесс вычисления оптимального вектора, а следовательно, и погрешность нахождения этого вектора определяются отношением /Т, Причем уменьшение величины ZT /Т ведет к уменьшению п погрешности нахождения оптимального вектора структуры. Однако, чем меньше IJ/T, тем меиьше скорость движения текущего вектора структуры. В специализированных устройствах время за0

5

0

5

, держки € обычно не поддается регули- рованию и является конструктивным параметром.Поэтому величина С/Т может меняться за счет изменения постоянной интегрирования Т.

513

Для обеспечения заданной точности при монотонном уменьшении угла между текущим вектором структуры и оптимальным постоянная интегрирования при заданной погрешности б долхша удовлетворять условию

1 + GI.P + бР TS ь --- , ,

Таким образом, отношение сГ/Т и, следовательно, скорость двилсения текущего вектора структуры, зависят от значения С , причем требование обеспечения заданной точности вычислений И требование максимального быстродействия устройства являются противоречивыми, В известном устройстве отношение о /Т выбирается таким образом, чтобы обеспечить заданн то точность нахождения оптимального вектора Структуры, Поэтому при малой величине о устройство обладает невысоким быстродействием. I .

Блок памяти текзга ей погрешности задает значение погрешности (5- , j 1,2,,..,m, аппроксимирующей процесс вычисления оптимального вектора в текущий момент времени, причем (5; (5 J j i m (G - заданная погрешность вычислений; m - число значений текущей погрешности), (5 & Gу, Для любого текзлцего вектора структуры Л (t) выполняется условие х (t)|2: р(З), так как ({t)eB°, а р(В) определяет расстояние от начала координат до В° {в - выпуклая оболочка множества В). Поэтому, если выполняется условие (t) (1 - G j ) X .I А (t)l , то выполняется условие (t) i (1 - C j )р(В), т.е. текущий вектор структуры равен оптимальному с погрешностью (j . Величина Т/С

принимается Т 1 1

J равной

значению

. . + L 4 р и вычисляется бло о G; Р

J - .

ком 19 деления (деление постоянного значения L /Р на ) и сумматором (добавление постоянного значения L -н Р), а в блоке 21 деления вьгаис- ляется величина . Для всех множеств входн к векторов выполняются условия L 1 и L 5 Р и обычно 1 поэтому с ростом G растет значение , т.е. увеличивается скорость движения текущего вектора структуры.

Перед началом вычислений в блоке памяти погрешности началтьное ее значение устанавливается таким.

5996

чтобы обеспечить максимальную величину отношения Г/Т,например G, 1 .Последующие величины G j принимают монотонно убывающие значения вплоть до заданной погрешности вычислений. При достижении текущим вектором структуры точности, удовлетворяющей значению G i , т.е. при {t) ё (1 - GT )х l (t)| , блок сравнения подает единичный сигнал через коммутатор 15 на вход блока 17 5 после чего на выходе последнего появляется новое значение + i . При вьтолнении условия (J j . б з с выхода блока 22 сравнения на управляющий вход кoм iyтaтopa подается еди- ничньш сигнал, по которому коммутатор подключает выход блока 3 к входу блока 17. При выполнении условия (j; (Jj второй блок 22 сравнения вырабатывает нулевой сигнал, по котором коммутатор отключает вход блока 17 от выхода блока 13 и подключает последний к входу блока индикации и первому входу элемента

И. Блок индикации сигнализирует об окончании вычислительного процесса при выполнении условия 6(t) - (1 ) Г А (t)f . Вектор л(г) при этом зафиксируется в регистре 10.

Величина о/Т, вычисляемая во блоке 21, подается на настроечный вход блока интегрирования

Таким образом, в начале вычислеНИИ скорость движения текущего вектора структуры максимальна и монотонно уменьшается в ходе вычислитель- гого процесса до того момента, когда будет достигнута заданная точность

вычислений.

Процесс вычисления оптимального вектора реяюния системы линейных неравенств происходит следующим образом,

В блок 1 регистров предварительно записываются все координаты всех входных векторо,, определяющих систему неравенств. В регистр 33 (в блоке 4 интегрирования) записывается

начальный вектор структуры, в качестве которого можно взять любой из входных векторов. В регистр 40 записывается максимальное по абсолютной величине отрицательное число.

Вычисления производятся циклически. Началом цикла считается импульс на четвертом выходе блока 23. Поэтому первый цикл вычислений отличается от остальных отсутствием пер7

вогс тактирующего импульса на входе синхронизации блока А интегрирования так как в регистре 33 уже записан начальный вектор структуры.

Устройство в течение одного цикла работает следующим образом. После записи в регистр 33 текущий вектор структуры перемножается скалярно со всеми входными векторами в блоке 5, минимальное значение из всех скалярных произведений определяется в блоке 6, у которого появляются единичные сигналы на тех выходах, которым соответствуют минимальные значения взвешенных сумм на входе.

Возбужденные выходы блока 6 открывают соответствующие ключи 2 и соответствующие этим ключам входные векторы поступают на входы блока 3. На выходе последнего образуется вектор значение каждой координаты которого равно среднему арифметическому значений координат всех векторов на входе. При поступлении.тактирующего импульса на вход синхронизации блока 3 происходит запись этого вектора в регистр 29. Блок 4 интегрирования производит вычисление текущего век- тора структуры в i-м цикле по рекуррентной формуле

-ЛК +- 1) A(il) +

+ q| A(iT)(i C) --л (it),

где y(i C) - выходной вектор блока 4 определения центра тяжести векторов; /

и

тЗапись текущего вектора структуры в регистр 33 происходит при поступлении тактирующего импульса с четвертого выхода блока 23. Так как текущий вектор структуры изменяется в каждом цикле, то изменяются значения скалярных произведений этого вектора со всеми входными векторами на выходах блоков 5, в результате чего возбуждаются другие выходы в блоке 6. При этом оказываются открытыми какие-либо другие из ключей 2 и другие входные векторы подаются из блока 1 на входы блока 3, что приводит к изменению выходного вектора y(t) этого блока в каждом цикле. Таким образом, на вход блока 4 интегрирования всегда подается вектор, скалярные произведения которого на текущий вектор структуры минимальны для всех входных векторо

968

так как y(t) вычисляется в цикле после записи в память текущего вектора структуры.

Изменение выходного вектора блока

4 интегрирования (t) приводит к -увеличению минимальной взвешенной суммы. Однако это изменение происходит необязательно монотонно, так как среди входных векторов х могут найтись такие, для которых скалярное произведение A(t) X может при этом у -1еньшаться и стать меньше значения (t) y(t). Вместе с тем происходит монотонное уменьшение модуля текущего вектора структуры T(t) , так как )((t)l всегда больше минимальной взвешенной суммы -(t), т.е. Т (t)|b Ь р (б)ь {t). Поэтому значение минимальной взвешенной суммы в целом

увеличивается в ходе вычислений,

стремясь в пределе к значению Л (t)|.

После записи в память выходного вектора блока 3 блоки 7 и 8 вычисляют значение минимальной взвешенной

суммы, которое анализируется блоком 9. Если это значение не превышает значения минимальной взвешенной суммы в регистре. 40, то на выходе блока 9 будет нулевой сигнал, который повторится на выходе элемента И, поэтому запись в регистр 10 в данном цикле будет запрещена.

5

0

5

Модуль выходного вектора блока 4 вычисляется в блоке 11 и в блоке 13 производится сравнение этого модуля, умноженного в умножителе 12 на коэф-: фициент 1 -5j , поступающий с выхода вычитателя 18 со значением минимальной взвешенной суммы на выходе: блока 8, т.е. проверяется условие .(t)5: (1 -(Jj )| r(t)| . Если это условие выполняется, т.е. сигнал с выхода умножителя 12 не превышает значения минимальной взвешенной суммы, то выходной сигнал блока 13 равен единице в противном случае он равен нулю.

На выход блока 17 подается одно из записанных в нем значений погрешности G; , 1 fe j т. Это значение сравнивается в блоке 22 со значением заданной погрешности (J, . Если Gj (э то на выходе блока 22 г устанавливается единичный сигнал, который, поступая на управляющий вход коммутатора 14, подключает информационный вход последнего к его второму выходу, т.е. выход блока

0

91

13 подключается через коммутатор 14 к первому входу блока .17. При этом на первом выходе коммутатора 1А действует единичный сигнал, который поступает на первый вход элемента И

Поэтому при GJ Gj выходной сигнал элемента И в момент поступления на его третий вход тактирзтащего импульса равен выходному сигналу блока 9, Если этот сигнал равен единице, т.е. значение минимальной взвешенной суммы, вычисленное в цикле блоками 7 и 8, превышает предыдущие значения минимальных взвешенных сумм, то в регистр 10- будет записан выходной сигнал блока 4 интегрирования. Запись минимальной взвешенной суммы в блок 9 производится после записи в регистр 10, чтобы поддержать единичное значение сигнала на входе синхронизации регистра 10 в момент записи в него.

При достижении текущей точности вычислений,т,е, при вьшолнении услови (t) 5 (1 - (Jj ) U(t)I , на выходе блока 13 появляется единичный сигнал, который при (J; G J подается на первый вход блока 17, на выходе которого при поступлении на его второй вход тактирующего импульса появляется новое значение погрешности G , Значения погрешности записаны в блок 17 таким образом, что СГ;, (j ; для всех J. Поэтому выходной сигнал вычитателя 18, равный I Сй| J возрастает, а также возрастает выходной сигнал умножителя 12. Если по-прежнему условие 5(t) 5:( 1 G ji-i )j /(t)| выполняется, то в последующих циклах выходной сигнал на выходе блока 17 будет изменяться, пока не выполнится одно из условий (t)-(l -6. )(t)) или fc G . При выполнении первого условия выходной сигнал блока 17 зафиксируется до тех пор, когда | (t)| уменьшится до такого значения, что будет-вновь выполняться условие e(t) г (1 -GJ )| (t)j ,

Блок 19, сумматор 20 и блок 21 производят вычисление значения

С 1. q

Ь + L р оР

которое по ступает на настроечный вход блока 4 интегрирования.

При выполнении условия Gj ё Gj коммутатор 14 отключает-первый вход

6 . 10

блока 17 от выхода блока 13 и под-- ключает последний к первому входу элемента И и блока 17 индикации. Причем-сигнал на первом выходе

коммутатора 14, инверсньш по отношению к вьгходному сигналу блока 1 3. Поэтому при выполнении условия {t:) (1 - GJ )| (t) на первом выходе коммутатора 14 по-прежнему будет единичный сигнал и нулевой сигнал появится только при достижении заданной точности вычислений. При этом блок 17 индикации изменит свое состояние, сигнализируя об окончании работы -устройства, а в регистре 10 зафиксируется текзпций вектор структуры, равньш оптимальному с заданной погрешностью.

,Тля ускорения движения текущего

вектора к опт1 1мальному (фиг.5), величина l/ i/ записывается в виде

Т 1 L

1 1 -ы.Р

и при заданном значении (J зависит в

основном от отношений L /Р, так как

обычно L Р, L 1 , С) - 1 . Поэтому

значение L /Р можно уменьшить, если

взять вместо L значение модуля вы-

ходного вектора y(t) блока определения центра тяжести векторов, а вместо Р взять модуль текущего вектора структуры 1 (t), умноженный на величину 1 -G . Погрешность нахождения

оптимального вектора при этом останется прежней, так как вектор y(t) удовлетворяет условию y(t)) е(В),. а вектор Д (t) при завершении вычислительного процесса удовлетворяет условию р(В)гг (t)5

5 I -., .(1 (J )| Л () .т.п. вьшолняются условия е(В) 4г1и р(В)г- Р, гарантирующие нахождение оптимального вектора структуры для множеств класса с заданной точностью.

Первый блок определения модуля вектора производит вычисление модуля текущего вектора структуры. Умножение на величину 1 -G производит

ся в. -умножителях. Модуль корректирующего вектора, y(t) вычисляется во втором блоке определения модуля и в блоке определения постоянной интегрирования производится вычисление коэффициента-q5 учитывающего постоянную интегрирования t

q Т

(T )lt}

y(t) +(i-6)l(t)l

Значение q подается на настроечный вход блока интегрирования.

I Модуль входного вектора блока 3

вычисляется во втором -блоке 42 определения модуля. На первый вход блока 43 определения постоянной интегрирования подается с вьпсода умножителя 13 значение модуля текущего вектора структуры, умноженное на 1-6, на второй вход - значение заданной погрешности вычислений G, на третий вход - значение модуля корректирующего вёктора с выхода блока

42. В блоке 43 вычисляется коэффици/

I,

ант q - , соответствующий минимальному значению постоянной интегрирования Т в данный момент, обеспечивающей максимальную скорость движения текущего вектора структуры и гарантирующей уменьщение угла между текущим вектором структуры и оптимальным.

Фо рмула изобретения

1. Устройство для нахождения оптимального вектора решения системы линейных неравенств, содержащее блок регистров входных векторов, группу из S блоков ключей (S - число входных векторов), блок определения минимума, группу из S блоков вычисления скалярных произведений, блок вычисления центра тяжести векторов, блок интегрирования, выходной регистр, блок вычисления скалярного произведения, блок анализа максимума, причем входы входных векторов устройства подключены к информационным входам блока регистров входных векторов i-я группа выходов блока регистров входных векторов (i-1,S) соединена с информационными входами i-ro блока ключей группы и первой группой входов 1-го блока вычисления скалярного произведения группы, выход которого соединены с i-м входом блока определения минимума, i-и выход которого соединен с управляющим входом i-ro блока ключей группы, выходы которого подключены к i-ой группе информационных входов блока вычисления центра тяжести векторов, выходы которого соединены с первой группой

)l

25

599612

входов блока вычисления скалярного произведения и информационными входами блока интегрирования, выходы которого соединены с второй группой

5 входов блока вычисления скалярного произведения, с вторыми группами входов блоков вычисления скалярных . произведений группы и информационными входами-выходного регистра, ходы которого соединены с выходами устройства, вход задания первого настроечного параметра устройства соединен с входом задания настроечного параметра блока интегрирования,

-5 отличающееся тем, что, с целью повышения производительности, устройство содержит первый блок вычисления модуля вектора, первый блок деления, умножитель, первый

20 блок сравнения, элемент И и блок синхронизации, причем выходы блока интегрирования соединены с информационными входами первого блока вычисления модуля вектора, выход которого соединен с входом делителя первого блока деления, вход делимого которого соединен с выходом блока вычисления скалярного произведения, а выход - с информационным входом

30 блока анализа максимума, выход которого соединен с первым входом элемента И, в ыход которого соединен с входом синхронизации выходного регистра, выход первого блока деления

35 соединен с первым входом первого блока сравнения, выход которого соединен с вторым входом элемента И, выходы первого блока вычисления модуля вектора соединены с входами

40 первого сомножителя умножителя, входы второго сомножителя которого подключены к входам задания второго настроечного параметра устройства, выходы умножителя соединены с второй

45 группой входов первого блока сравнения, с первого по четвертый выходы блока синхронизации соединены соответственно с входом синхронизации блока вычисления центра тяжести

50 векторов, с входом синхронизации

блока интегрирования, входом синхронизации блока анализа максимума и третьим входом элемента И,

2. Устройство по п.1, о т л и - чающееся тем, что, с целью повьш1ения быстродействия, оно содержит второй блок вычисления модуля вектора и блок определения постоян1313

ной интегрирования, причем входа втор ого блока вычисления модуля вектора соединены с выходами блока вычисления центра тяжести векторов, а выходы - с первой группой входов блока определения постоянной интегрирования, выходы которого соединены с входами постоянной интегрирования блока интегрирования, выходы умножителя соедия ены с второй группой входов блока определения постоянной интегрирования, третья группа входов которого подключена к входу задания второго настроечного параметра устройства,

3, Устройство по п., отличающееся тем, ЧТО , с целью повышения быстродействия, оно содержит коммутатор, блок памяти текущей погрешности, вычитатель, второй блок сравне.ния, второй и третий блоки деления, сумматор, причем выход первого блока сравнения соединен с информационным входом коммутатора, первый выход которого соединен с третьим входом элемента И, а второй - с входом чтения блока памяти текущей погрешности, вход синхронизации которого подключен к четвертому выходу блока синхронизации, выходы которого соединены с входами вычитаемого вычитателя, первой группой входов второго блока сравнения и входами делителя второго блока деления, выходы которого соединены с входами первого слагаемого сумматора, выходы которого соединены с входами делителя третьего блока деления, выходы которого соединены с входами интегрирования-блока интегрирования, входы делимого 1зторого и тре- тьего-блоков деления, входы уменьшаемого вычитателя, вторая группа входов второго блока сравнения и входы второго слагаемого сумматора соединены соответственно с первой по пяту группы входов настроечных параметров устройства, выходы вычитателя соединены с входами второго сомножителя у ножителя, выход второго, блока деления соединены с управляющим входом коммутатора.

4. Устройство по п. 1, о т Л и - чающееся тем, что блок вычисления центра тяжести векторов содержит S групп узлов сравнения с нулем по п узлов в группе (п - разрядность входных векторов), S элементов ИЛИ,

6 . 14

группу из п сумматоров, группу из п узлов деления, сумматор, регистр, причем i-и вход j-й группы информа- ционньгх входов блока ( i 1 , п; j

T7s) соединен с входом i-го узла сравнения с нулем i-и группы и j-м входом i-ro сумматора группы, выход которого соединен с входом делимого узла деления, выходы которого

соединены с i-ей группой информаци- OHHbDC входов регистра, вход синхронизации которого соединен с входом синхронизации блока, а выходы подключены к выходам блока, выход i-ro узла сравнения с нулем j-и группы

( -.1 п; j 1, S) соединен с i-м входом j-ro элемента ИЛИ, выход которого подключен к j-му входу сумматора, выходы которого соединены с входами делителя j-ro узла деления.

5.Устройство по п,1, о т л и ч а- ю щ е е с я тем, что блок интегрирования содержит два сумматора, два умножителя, группу элементов НЕ, узел определения модуля вектора и регистр, причем информационные входы блока соединены с входами первого слагаемого первого сумматора, выходы которого соединены с входами первого слагаемого второго сумматора, выходь которого соединены с информационными входами регистра, выходы которого соединены с входами узла определения модуля вектора, выходы которого соединены с входами первого .сомножителя второго умножителя, выхода которого соединены с входами второго сомножителя первого умножителя, вход синхронизации блока соединен с входом синхронизации регистра, выходы которого соединены с выходами блока, входами второго слагаемого второго сумматора и входами элементов НЕ группы, выхода которых

подключены к входам второго слагаемого первого сумматора, вход второго сомножителя второго умножителя соединен с входом задания настроечного параметра блока.

6,Устройство поп,1,отлич а ю щ е е с . Я тем, что блок анализа максимума содержит сумматор, узел сравнения с нулем, элемент И, регистр и группу элементов НЕ, причем информационные входы блока соединены с входами первого слагаемого сумматора, выходы которого соединены с входами узла сравнения с нулем.

15

выход которого соединен с выходом блока и первым входом элемента И, выход которого соединен с входом синхронизации регистра, выходы которого соединены с входами элементов НЕ группы, выходы которых подключены к входу второго слагаемого сумматора, информационные входы блока соединены с информационными входами регистра, вход синхронизации блока подключен к второму входу элемента И.

7. Устройство по п.2, отличающее с я тем, что блок определения постоянной интегрирования содержит два умножителя, два узла деления и сумматор, причем первая группа входов блока соединена с входами первого и второго сомножителей первого

56

15996

умножителя и

16

fO

15

входами первого слагаемого сумматора, выходы которого соединены с входами делителя первого узла деления, выходы которого соединены с выходами блока, вторая группа входов блока соединена с входами второго слагаемого сумматора и входами первого сомножителя второго умножителя, входы второго сомножителя которого соединены с третьей группой входов блока, а выходы - с входом делимого второго узла деления, входы делителя которого соединены с выходами первого умножителя, а выходы - с входами третьего слагаемого сумматора, входы делимого первого узла деления соединены с шиной единичной константы блока.

Фаг. 2

I

.З

0--4.

44

nw

45

4

i

Фаг. 7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления оптимальной структуры пороговых элементов | 1976 |

|

SU635488A1 |

| Устройство формирования программы кинематического разворота твердого тела | 1989 |

|

SU1659979A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Адаптивный фильтр | 1983 |

|

SU1116537A1 |

| Адаптивный цифровой фильтр | 1987 |

|

SU1494212A1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714407A1 |

| АДАПТИВНАЯ СИСТЕМА ТЕРМИНАЛЬНОГО УПРАВЛЕНИЯ | 2012 |

|

RU2500009C1 |

| Устройство для решения систем дифференциальных уравнений | 1977 |

|

SU714406A1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1388896A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МОДУЛЯ СКОРОСТИ АЭРОДИНАМИЧЕСКОЙ ЦЕЛИ | 2012 |

|

RU2559296C2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для решения задач классификации, распознания образов, управления адаптивными фильтрами, синтеза структур пороговых элементов. Цель изобретения - повьппе.ние быстродействия устройства за счет повьшения скорости движения текущего вектора структуры. Устройство содержит блок 1 регистров входных векторов, блоки 2 ключей, блок 3 вычисления спектра тяжести векторов, блок 4 интегрирования, блоки 5 вычисления скалярных произведений, блок 6 определения минимума, блоки 8,19,21 деления, блок 9 анализа максимума, выходной регистр 10, два блока 11 вычисления модуля вектора, блок определения постоянной интегрирования, умножитель 12, блоки 13, 22 сравнения, коммутатор 14, блок 16 памяти текущей погрешности, элемент И 15, вычитатель 18, сумматор 20, блок 23 синхронизации. В устройстве непрерывно оценивается погрешность достижения оптимального значения и изменяется скорость движения вектора к оптимуму, что увеличивает быстродействие. 6 з.п. ф-лы, 7 ил. i СЛ 00 сд со со о:) ut.l

| АДАПТИВНЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ | 0 |

|

SU267214A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления оптимальной структуры пороговых элементов | 1976 |

|

SU635488A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-02—Подача