(5) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ МНОГОКАНАЛЬНЫМ ВИБРОСТЕНДОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ БАЛАНСИРОВКИ РЕЗОНАТОРА ТВЕРДОТЕЛЬНОГО ВОЛНОВОГО ГИРОСКОПА ЛУЧОМ ЛАЗЕРА | 1993 |

|

RU2079107C1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Устройство для измерения скорости изменения температуры | 1989 |

|

SU1643954A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 1991 |

|

RU2014740C1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Устройство импульсно-фазовой автоподстройки частоты | 1989 |

|

SU1737721A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ | 2000 |

|

RU2191468C2 |

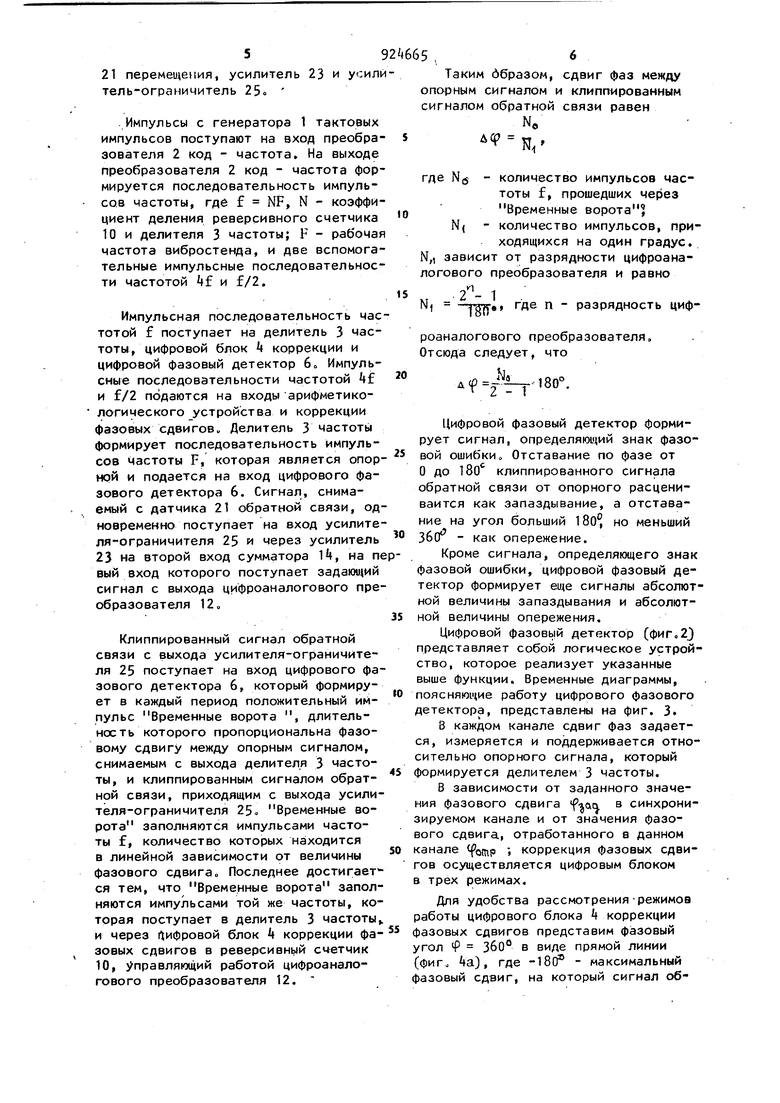

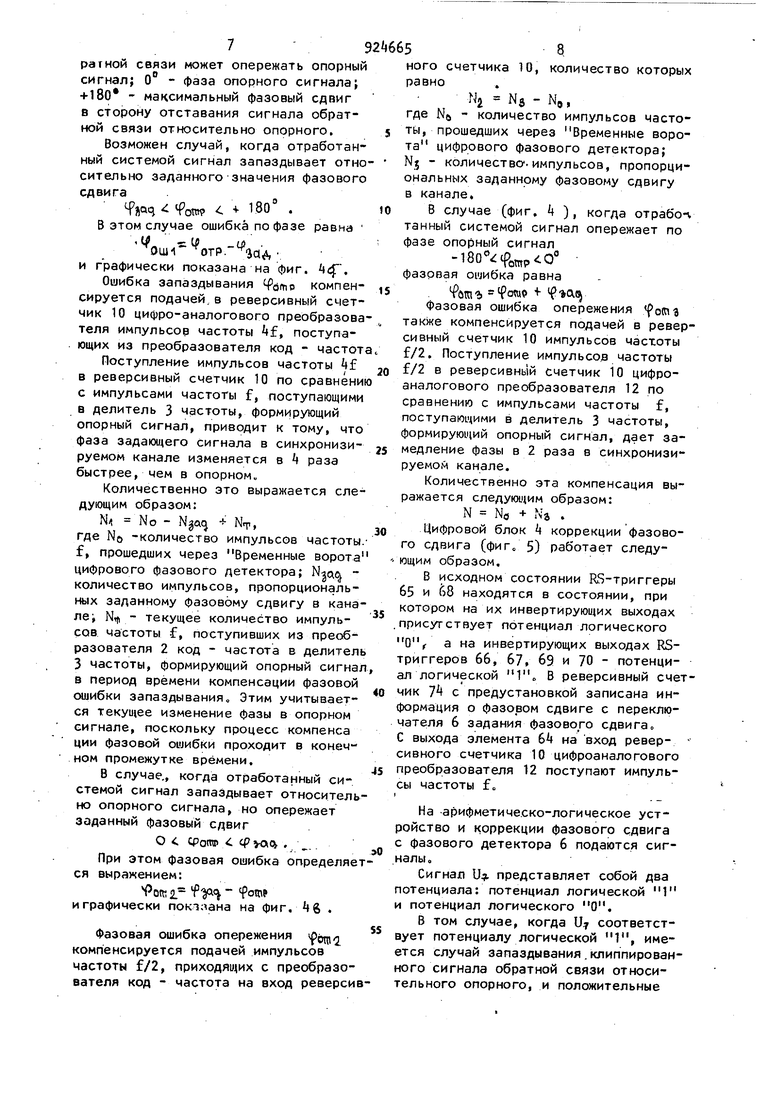

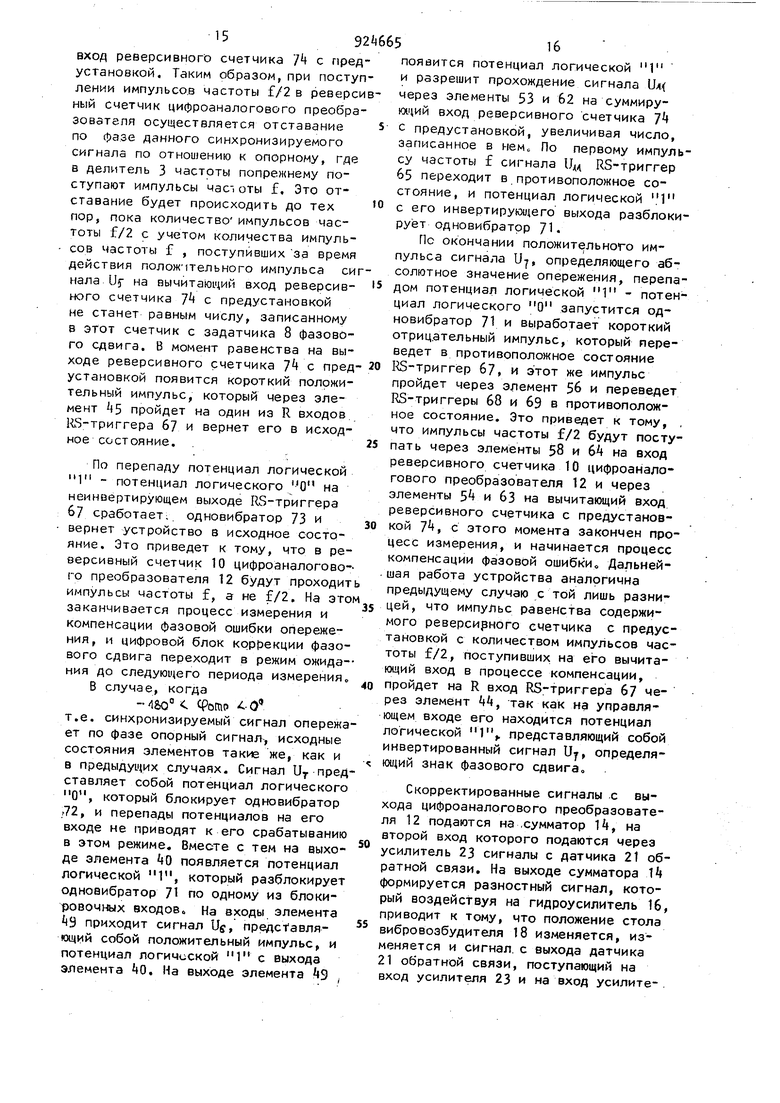

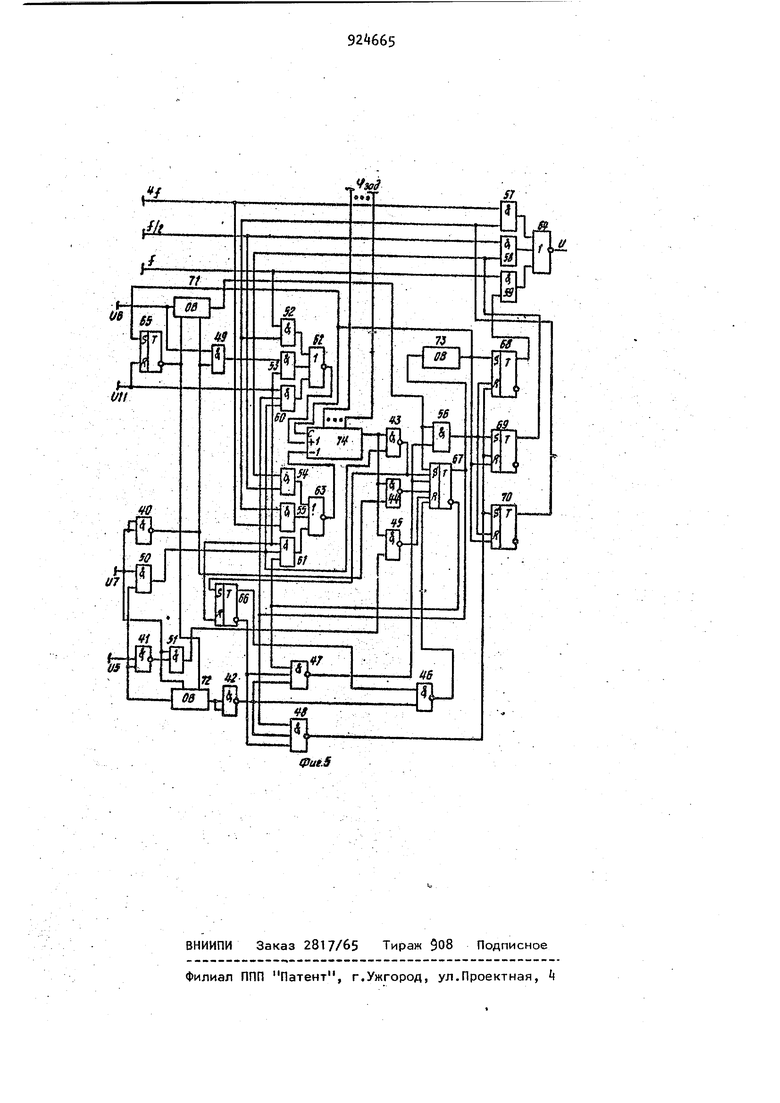

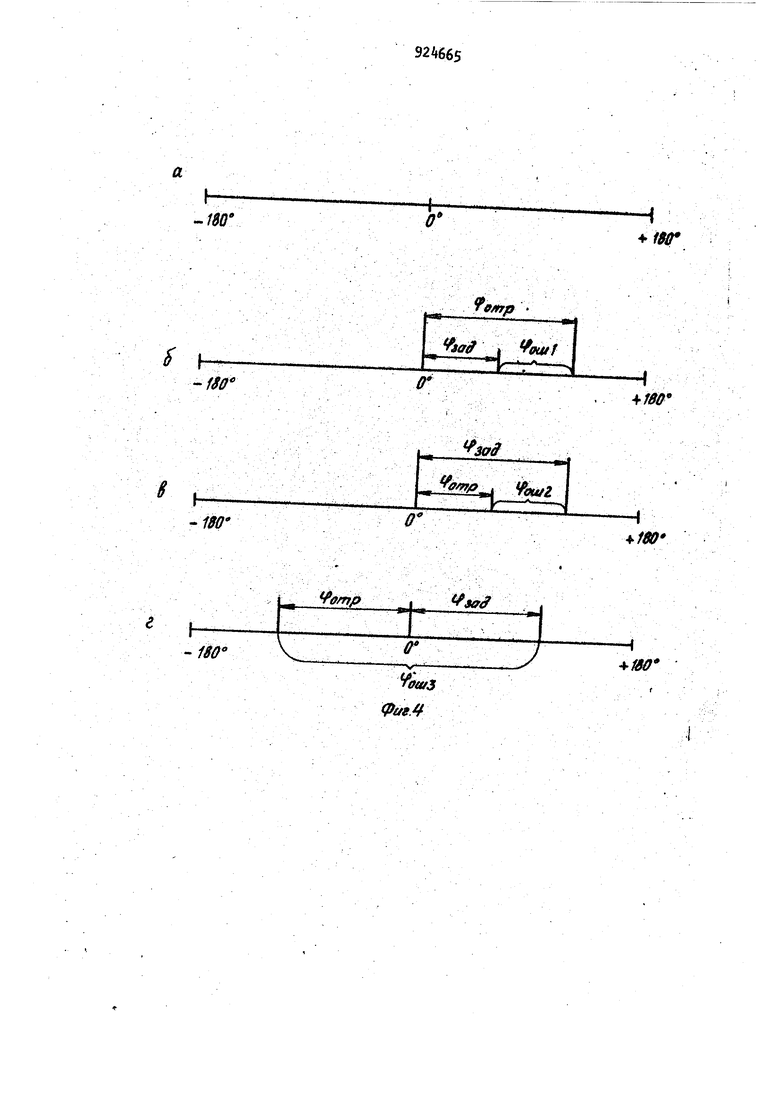

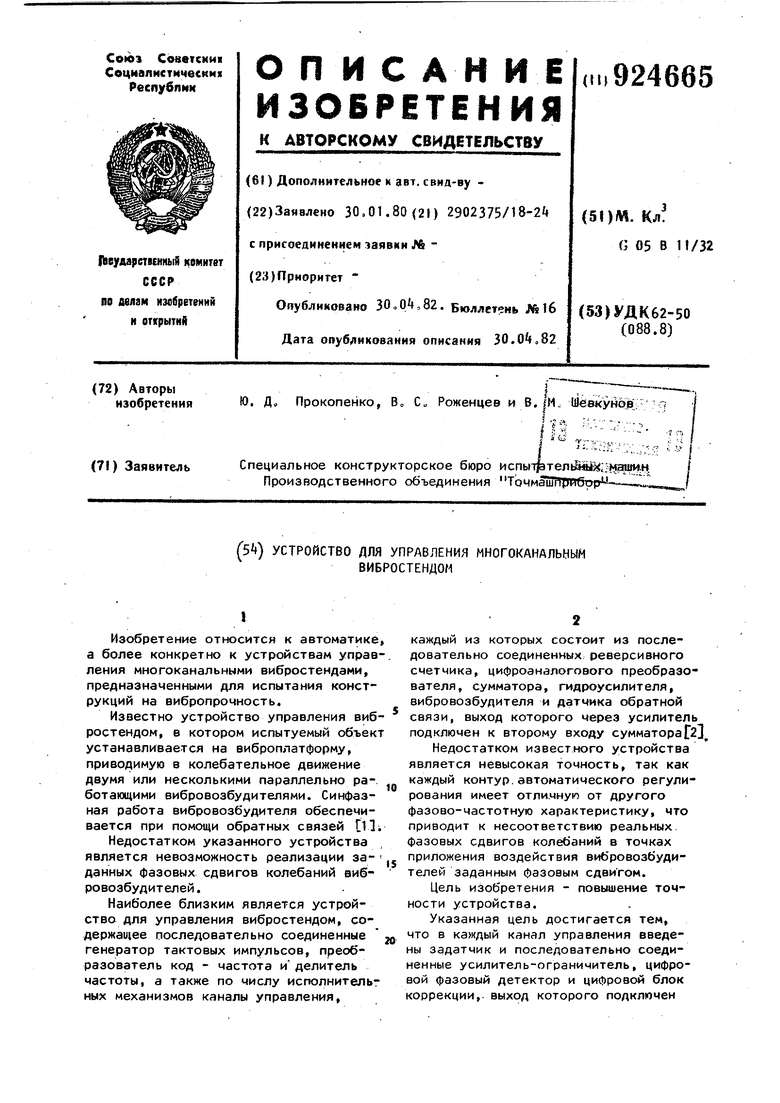

Изобретение относится к автоматике а более конкретно к устройствам управ ления многоканальными вибростендами, предназначенными для испытания конструкций на вибропрочность. Известно устройство управления виб ростендом, в котором испытуемый объек устанавливается на виброплатформу, приводимую в колебательное движение двумя или несколькими параллельно работающими вибровозбудителями. Синфазная работа вибровозбудителя обеспечивается при помощи обратных связей H Недостатком указанного устройства является невозможность реализации заданных фазовых сдвигов колебаний вибровозбудителей. Наиболее близким является устройство для управления вибростендом, содержащее последовательно соединенные генератор тактовых импульсов, преобразователь код - частота и делитель частоты, а также по числу исполнитель ных механизмов каналы управления. каждый из которых состоит из последовательно соединенных реверсивного счетчика, цифроаналогового преобразователя, сумматора, гидроусилителя, вибровозбудителя и датчика обратной связи, выход которого через усилитель подключен к второму входу сумматораИ Недостатком известного устройства является невысокая точность, так как каждый контур.автоматического регулирования имеет отли,чнуп от другого фазово-частотную характеристику, что приводит к несоответствию реальных фазовых сдвигов колебаний в точках приложения воздействия вибровозбудителем заданным фазовым сдвигом. Цель изобретения - повышение точности устройства. Указанная цель достигается тем, что в каждый канал управления введены задатчик и последовательно соединенные усилитель-ограничитель, цифровой фазовый детектор и цифровой блок коррекции, выход которого подключен 3 9 к входу реверсивного счетчика, вторая группа входов к соответствующим выходам задатчика, а третья группа йходоо к соответствующим выходам пре образователя код - частоты, примем вход и выход делителя частоты соединены соответственно с вторым и треть им входами цифрового фазового детекто ра, а вход усилителя-ограничителя под-ключен к выходу датчика обратной связи.. На фиг. 1 представлена структурная схема устройства для управления много канальным вибростендом для упрощения схемы на ней показано 2 канала, в общем случае количество каналов не ограничено) на фиго 2 - функциональ ная схема цифрового фазового детектора; на фиг. 3 временные диаграммы, поясняющие работу цифрового фазового детектора; на фиг. 4 - фазовые соотно шения, поясняюецие работу цифрового блока коррекции фазовых сдвигов; на фиг. 5 функциональная схема цифрового блока коррекции фазовых сдвигов Устройство для управления многоканальными вибростенд-ами содержит генератор 1 тактовых импульсов, преобразователь . код - частота, делитель 3 частоты, цифровые блоки 4 и 5 коррекции, цифровые фазовые детекторы 6 и 7, задатчики 8 и 9 реверсивные счетчики 10 и П, цифроаналоговы преобразователи 12 и 13 сумматоры 1 и 15 гидроусилители 16 и 17 виб ровозбудители 18 и 19 испытуемый объект 20, датчики 21 и 22 обратной связи, усилители 23 и 2k, усилителиограничители 25 и 2б. В качестве генератора 1 тактовых импульсов может быть использовано любое из известных устройств, способ ное формировать последовательность импульсов заданной частоты. Преобразователь 2 код - частота предназначен для формирования последовательностей импульсов, частота которых пропорциональна задаваемому коду. . Делитель 3 частоты представляет собой обычный асинхронный двоичный счетчик, сигнал на выходе которого является опорным. Задатчики 8 и 9 представляют собой переключатели, работакхцие в двоичио-десятичном коде. Усилители 23 и предназначены для масштабирования сигналов обратНОИ связи, снимаемых с датчиков 21 и 22„ Усилители-ограничители 25 и 26 предназначены для клиппирования сигналов обратной связи с датчиков 21 и 22 перемещения, в результате чего на выходе усилителей-ограничителей присутствуют последовательности импулъсов напряжения с постоянной ам-плитудой. Длительность импульсов, частота следования и временный сдвиг между сигналами точно соответствуют длительности полупериодов, частоте и фазе сигналов обратных-связей, снимаемых с датчиков 21 и 22. Необходимое равенство частот клиппированного сигнала обратной связи и опорного сигнала достигается уравниванием коэффициентов пересчета частоты у делителя 3 частоты, у реверсивных счетчиков 10 и 11 и у цифроаналоговых преобразователей 12 и 13. Цифровые фазовые детекторы 6 и 7 предназначены для определения сдвига фаз между опорным сигналом и клиппированным сигналом обратной связи. Фазовый детектор (фиг. 2) представляет собой устройство, выполненное на логических элементах, и содержит одновибраторы 27 и 28, элементы 2И-НЕ , KS-триггеры 36 и 37 и элементы 2И 38 и 39. ,. Цифровые блоки 4 и 5 коррекции фазового сдвига (фиг. 5) представляют собой логическую схему, осуществляющую коррекцию фазовой ошибки в каждом канале вибростенда, и которая содержит элементы 2И-НЕ itO-ii6, ЗИ-НЕ и 8, 2И kS-53, ЗИ 60 и 61, ИЛИ-НЕ б2-64, RS- триггеры 65-70, одновибраторы 71-73 и реверсивный счетчик 7 с предустановкой. Входы предустановки этого счетчика поразрядно соединены с выходами переключателей 8 и 9 задания фазовых сдвигов. Работу устройства управления многоканальными системами (фиг. 1) рассмотрим на примере одного из каналов, в который входят генератор 1 тактовых импульсов, преобразователь 2 код Частота, делитель 3 частоты, которые являютсяобщими для всех каналов вибростенда, цифровой блок Ц коррекции фазовых сдвигов, цифровой фазовый детектор 6, задатчик 8, реверсивный счетчик 10, цифроаналоговый преобразователь 12, сумматор 14, гидроусилитель 16, вибровозбудитель 18, датчик 21 перемещения, усилитель 23 и усили тель-ограничитель 25о Импульсы с генератора 1 тактовых импульсов поступают на вход преобразователя 2 код - частота. На выходе преобразователя 2 код - частота формируется последовательность импульсов частоты, где NF, N - коэффициент деления реверсивного счетчика 10 и делителя 3 частоты; F - рабочая частота вибростенда, и две вспомогательные импульсные последовательности частотой Ц и /2. Импульсная последовательность час тотой поступает на делитель 3 частоты, цифровой блок коррекции и цифровой фазовый детектор 6 Импульсные последовательности частотой и /2 подаются на входы арифметикологического устройства и коррекции фазовых сдвигов Делитель 3 частоты формирует последовательность импульсов частоты F, которая является опорной и подается на вход цифрового фазового детектора 6. Сигнал, снимаемый с датчика 21 обратной связи, одновременно поступает на вход усилителя-ограничителя 25 и через усилитель 23 на второй вход сумматора 1, на пе вый вход которого поступает задаки)4ий сигнал с выхода цифроаналогового преобразователя 12 Клиппированный сигнал обратной связи с выхода усилителя-ограничителя 25 поступает на вход цифрового фазового детектора 6, который формирует в каждый период положительный импульс Временные ворота , длительность которого пропорциональна фазовому сдвигу между опорным сигналом, снимаемым с выхода делителя 3 частоты, и клиппированным сигналом обратной связи, приходящим с выхода усилителя-ограничителя 25, Временные ворота заполняются импульсами частоты , количество которых находится в линейной зависимости от величины фазового сдвига Последнее достигается тем, что Временные ворота заполняются импульсами той же частоты, которая поступает в делитель 3 частоты и через 1 ифровой блок k коррекции фазовых сдвигов в реверсивный счетчик 10, Управляющий работой цифроаналогового преобразователя 12. Таким дбразом, сдвиг фаз между опсфным сигналом и клиппированным сигналом обратной связи равен , где N(5 - количество импульсов частоты , прошедших через Временные ворота N( - количество импульсов, приходящихся на один градус, N,, зависит от разрядности цифроаналогового преобразователя и равно «, где п - разрядность цифроаналогового преобразователя, Отсюда следует, что т 2 - 1 Цифровой фазовый детектор формирует сигнал, определяю1чий знак фазовой ошибки Отставание по фазе от О до ТбО клиппированного сигнала обратной связи от опорного расцениваится как запаздывание, а отставание на угол больший но меньший ЗбОг - как опережение. Кроме сигнала, определяющего знак фазовой ошибки, цифровой фазовый детектор формирует еще сигналы абсолютной величины запаздывания и абсолютной величины опережения. Цифровой фазовь|й детектор (фиг,2) представляет собой логическое устройство, которое реализует указанные выше функции. Временные диаграммы, поясняющие работу цифрового фазового детектора, представлены на фиг. 3. 8 каждом канале сдвиг фаз задается, измеряется и поддерживается относительно опорного сигнала, который ормируется делителем 3 частоты. В зависимости от заданного значения фазового сдвига . в синхрониируемом канале и от значения фазоого сдвига, отработанного а данном анале (fo(j,p -, коррекция фазовых сдвиов осуществляется цифровым блоком трех режимах. Для удобства рассмотрения-режимов аботы цифрового блока i коррекции азовых сдвигов представим фазовый гол Ф ЗбО° в виде прямой линии фиГо ta), где -180° - максимальный азовый сдвиг, на который сигнал обратной связи может опережать опорный сигнал; 0° - фаза опорного сигнала; +l80 - максимальный фазовый сдвиг в сторону отставания сигнала обратной связи относительно опорного. Возможен случай, когда отработанный системой сигнал запаздывает отно сительно заданного значения фазового сдвигаg 4jaq Pow . В этом случае ошибка по фазе равна V «IP ц} . ош1 отр. зад и графически показана на фиг. , Ошибка запаздывания Фото компенсируется подачей,в реверсивный счетчик 10 цифро-аналогового преобразова теля импульсов частоты , поступающих из преобразователя код - частот Поступление импульсов частоты в реверсивный счетчик 10 по сравнени с импульсами частоты f, поступающими в делитель 3 частоты, формирующий опорный сигнал, приводит к тому, что фаза задающего сигнала в синхронизируемом канале изменяется в раза быстрее, чем в опорном Количественно это выражается следующим образом: N No - Nga -ь NT,, где NO -количество импульсов частоты f, прошедших через Временные ворота цифрового фазового детектора; количество импульсов, пропорциональных заданному фазовому сдвигу а кана лец N,fi - текущее количество импульсов частоты -f, поступивших из преобразователя 2 код - частота в делител 3 частоты, формирующий опорный сигна в период времени компенсации фазовой ошибки запаздывания Этим учитываегтся текущее изменение фазы в опорном сигнале, поскольку процесс компенса ции фазовой ошибки проходит в конечном промежутке времени. В случае., когда отработанный системой сигнал запаздывает относитель но опорного сигнала, но опережает заданный фазовый сдвиг О . Фотр Ч vocv . ... При этом фазовая ошибка определяе ся выражением: foTOf и графически покт;1ана на фиг. 46 . Фазовая ошибка опережения компенсируется подачей импульсов частоты /2, приходящих с преобразователя код - частота на вход реверси ного счетчика 10, количество которых равно N2 NS - N,, где NU - количество импульсов частоты, прошедших через Временные ворота цифрового фазового детектора; NJ - количества, импульсов, пропорциональных заданному фазовому сдвигу в канале, В случае (фиг. 4 ), когда отрабоп тайный системой сигнал опережает по фазе опорный сигнал фазовая ошибка равна . furo Powo (5 Фазовая ошибка опережения «foRi также компенсируется подачей в реверсивный счетчик 10 импульсов частоты /2. Поступление импульсов частоты /2 в реверсивный счетчик 10 цифроаналогового преобразователя 12 по сравнению с импульсами частоты , поступаю1чими в делитель 3 частоты, формирующий опорный сигнал, дает замедление фазы в 2 раза в синхронизируемом канале. Количественно эта компенсация выражается следую1цим образом: N Ne + Na . Цифровой блок 4 коррекции фазового сдвига (фиг/ 5) работает следующим образом. В исходном состоянии RS-триггеры б5 и 68 находятся в состоянии, при котором на их инвертирующих выходах присутствует потенциал логического 0 а на инвертирующих выходах RSтриггеров 66, 67, б9 и 70 - потенциал логической В реверсивный счетчик 7 е предустановкой записана информация о фазовом сдвиге с переключателя 6 задания фазового сдвига С выхода элемента 64 на вход ревер- сивного счетчика 10 цифроаналогового преобразователя 12 поступают импульсы частоты о ), На арифметическо-логическое устройство и коррекции фазового сдвига с фазового детектора 6 подаются сигналы. Сигнал и представляет собой два потенциала: потенциал логической 1 и потенциал логического О. В том случае, когда U соответствует потенциалу логической 1, имеется случай запаздывания.клиппированного сигнала обратной связи относительного опорного, и положительные 9 на суммируПрохождение сигнала ющий вход реверсивного счетчика 7 с предустановкой. Первый импульс час тоты f сигнала U-i/i , который поступает на R вход RS-триггера 66 (после того как он изменяет свое состояние с приходом импульса с выхода элемента {З), возвращает его в исходное состояние. По окончании положительного импул са сигнала Ug, определяющего абсолют ное значение запаздывания, закрываются Временные вороТ;а в фазовом детекторе, и сигнал U/JX не приходит на арифметическо-логическое устройство коррекции фазового сдвига Позаднему фронту положительного .импуль са сигнала Ug- срабатывает рдйовибратор 72, поскольку на двух блокирующих входах его присутствуют потенци алы логическо 1, пришедшие с инвертирующего выхода 1 5-триггера 37 фазового детектора бис инвертирующего выхода RS-триггера б5о Одновиб ратор вырабатывает короткий отрицательный импульс, который проинвертировавшись элементом tZ, проходит на входы двух элементов 4 и 48. Эти элементы управляются противофазными сигналами, приходящими с инвертируЮ1цего и неинвертирующего выходов RS-триггера 67 Элемент А8 управляет ся также сигналом с инвертирующего выхода 1Й-триггера 66. Этот сигнал после момента HV Ротр представляет собой потенциал логической 1. На неинвертирующем выходе RS-триггера 67 .присутствует потенциал логичес кой 1% на инвертирующем - О, поэтому, положительный импульс с выход элемента 2, проинвертировавшись, проходит через элемент 8 и поступае на R входы RS-триггеров, 68 и б9 и на S вход RS-триггера 70. RS-триггер 69 не изменяет своего состояния., а 1 -триггеры 68 и 70 изменяют свои со стояния на противоположные. Таким образом, на неинвертирующем выходе RS-триггера 68 - потенциал ло гического О, а на неинвертирующем выходе RS-триггера70 - потенциал логической С этого момента времени начинается процесс компенсации фазовой ошибки. Потенциал логической 1 с неинвертирующего выхода RS-триггера 70 подается на один из входов элемента 57, на другой вход которого посту 512 пают импульсы частоты 4f, приходящие с преобразователя 2 код частота. Импульсы частоты проходят через элемент 57 и элемент 6k на реверсивный счетчик 10, управляющий работой цифроаналогового преобразователя 12, Поступление импульсов частоты 4f в реверсивный счетчик 10 приводит к более быстрому изменению их состояния, чем делителя 3 частоты, формирующего опорный сигнал, куда постоянно приходят импульсы частоты , и так как существует связь между количеством импульсов и фазовым сдвигом, то это приводит к изменению фазы выходного сигнала цифроаналогового преобразователя относительно опорного сигнала на величину, которая определяется следующим образом. С неинвертирующего выхода RS-триггера 70 потенциал логической 1 поступает также и на входы- элементов 52 и 55. Импульсы частоты k поступают через элемент 55 и элемент 63 на. вычитающий вход реверсивного счетчика 7 с предустановкой Через элемент 52 и элемент 62 импульсы частоты поступают на суммирующий вход реверсивного счетчика 7 с предустановкой Подача импульсов частоты на суммирующий вход реверсивного счетчика 7 с предустановкой необходима для того, чтобы в период времени компенсации фазовой ошибки запаздывания учесть текущее изменение фазы опорного сигнала. В момент равенства числа импульсов, определяющих собой фазовую ошибку запаздывания, плюс количество импульсов частоты , поступивших в период компенсации на суммирующий вход реверсивного счетчика 7 с предустановкой, и количество импульсов частоты kf, поступивших на вычитающий вход реверсивного счетчика 7 с предустановкой, на выходе последнего появляется короткий положительный импульс, который проходит через элемент на один из R входов RS-триггера б7о На управляющем входе элемента 3, который соединен с выходом элемента 50, присутствует потенциал логического О, поскольку сигнал Ur после окончания положительного импульса, определяющего абсолютное значение запаздывания, представляет собой потенциал логического О. На выходе элемента 51 присутствует поимпульсы сигнала Uj несут информацию об абсолютной величине запаздывания Если 07 соответствует потенциалу логического О, имеется случай опережения клиппированным сигналом обратном связи опорного сигнала, и положительные импульсы сигнала Щ в этом случае несут информацию об абсолютной величине опережения. Сигнал и представляет собой пач ки импульсов частоты , прошедших через Временные ворота. Количество импульсов в пачке пропорционально фазовому сдвигу. Рассмотрим случай, когда (, cpcOTP t-fSO На вход элемента 41, элемента 50, одновибратора 72 с фазового детекто.ра 6 приходит сигнал Us, представляющий собой положительный импульс, на вход элемента ЦО, на входы элемен тов 50 и 51 и блокировочный вход одновибратора 72 с фазового детектора 6 с инвертирущего выхода RS-триггера 37 приходит СУ гнал О, который представляет собой потенциал логичес кой 1. На входы R RS-триггеров 65 и 66, на входы элементов 53, 60 и 61 с фазового детектора 6 приходит сигнал -f , который представляет собой последовательность импульсов частоты , заполняющих Временные ворота Первый приходящий импульс переводит RS-триггер 65 в П|эотивоположное состояние, при котором на его инвертирующем выходе появляется потенциал логической 1, и, тем самым, по одному, из блокировочных входов одновибраторов 71 и 72 снимается запрет. Применение RS-триггера, осуидествля ющего блокировку одновибраторов 71 и 72, необходимо для того, чтобы цифровой блок коррекции не реагировал на Временные ворота, длительность которых меньше, чем период следования заполняющих импульсов частоты . Сигнал и,и проходит через элементы 61 и 63 на вычитающий вход реверсивного счетчика 7 с предустановкой. Прохождение сигнала ИГук через элемент 61 обусловлено тем, что на двух других входах присутствуют потенциалы логической 1, приходящие с выхода элемента 50 и инвертирующего выхода RS-триггера 67. Через элементы 63 и 60 и элемент 62 на суммирующий вход реверсивного счетчика 7 с предустановкой сигнал и« не поступает. 6510 поскольку на.входе элемента 53.присутствует 1тотенциал логической О, поступающий сюда с выхода элемента 4э, на входе которого присутствуют также потенциалы логического О. На одном из двух управляющих входов элемента 60 присутствует потенциал логического О, подаваемый сюда с инвертирующего выхода RS триггера 67 После прихода на вычитающий вход реверсивного счетчика 7 с предустановкой количества импульсов, равного числу, записанному в него с задатчика 8 фазового сдвига, на выходе реверсивного счетника 7 с предустанов-. кой появляется короткий положительный импульс. Этот импульс свидетельствует о равенстве fora Щ . Все последующие импульсы, приходящие через Временныеворота, уже представляют величину фазовой ошибки и поступают они на суммирующий вход реверсивногосчетчика 7 с предустановкой. Осущест вляется это следующим образом. Короткий положительный импульс с выхода реверсивного счетчика 7 с предустановкой, инвертируясь, проходит через элемент 43, на другом входе которого присутствует потенциал логической 1, подаваемый с элемента 50 и несущий информацию о том, чтоимеется случай запаздывания и что положительный импульс, определяющий абсолютное значение .запаздывания, еще не закончился. Через элементы k и 45 импульс с выхода реверсивного счетчика 7 с предустановкой не проходит, поскольку они блокированы потенциалами логического О, приходящими соответственно с элемента 40 и элемента 51. Короткий отрицательный импульс подается с выхода элемента 43 на входы RS -триггеров 66 и б7 и переводит их в противоположное состояние, при котором на инвертируюсцих выходах будет присутствовать потенциал логического Назначение RS-триггера 66 описывается ниже. Потенциал логического О с инвертирующего выхода . . S-триггера67 поступает на один из входов элемента 47 и на один из вхоп ов 3|лемента 61, запрещая тем самым прохождение сигнала на вычитащий вход реверсивного счетчика 74 с предустановкой. Потенциал логичесой 1 с неинвертирующего выхода S-триггера 67 поступает на один из входов элемента 48 и на один из вхоов элемента 60, разрешая тем самым тенциал логической., который и разрешает прохождение импульса чере элемент kS на R вход RS-триггера б7 который возвращается в исходное состояние. По перепаду потенциал логической t - потенциал Логического: О на неинвертирующем выходе RSтриггера 67 сработает одновибратор 73, и на его выходе появится короткий отрицательный импульс, который вернет RS-триггер б5 в исходное состояние. Приход короткогоОтрицательного импульса на вход предустановки С реверсивного счетчика 7 с предустановкой приводит к записи информации о заданном значении фазового сдвига с переключателя 8 задания фазового сдвига в . реверсивный счетчик 7 с предустановкой. По этому импуль су возвращается в исходное состояние RS-триггеры б5, 68 и 70, что приводит к тому, что в реверсивный счетчик 10 цифроаналогового преобразователя 12 проходят уже импульсы частоты , а не k. На этом процесс измерения и компенсации фазовой ощибки запаздывания закончен, и устройство переходит в режим ожидания до следующего периода измерения. RS-триггер 66 необходим для того чтобы в случае, когда фазовый сдвиг сигнала на выходе цифроаналогового преобразователя соответствует заданному значению относительно опорного сигнала, т.е, fomp .J цифровой блок коррекции фазового сдвига не изменил частоты, поступающей в реверсивный счетчик 10 цифроаналогового преобразователя 12. Если после прихода отрицательного импульса с выхода элемента 3 на S вход RS-триггера 66 импульсы частоты f не приходят на R вхОд этого же триггера, то потенциал логического О с инвертирующего выхода этого триггера запретит прохождение импуль са с одновибратора 72 через элемент 8 на S вход RS-tpиггepa 70 и вход R RS-триггера 68. Вместо этого импульс пройдет через элемент () на один из R входов RS-триггера 67 и вернет его в исходное состояние. По перепаду потенциал логической 1 потенциал логического О на неинвертирующем выходе RS-триггера 67 сработает одновибратор 73 и короткий отрицательный импульс с его выхода по65падает на S вход RS-триггера 68 и на R входы RS-триггеров б9 и70, но не изменит их состояния. Одновременно по этому же импульсу произойдет перепись информации о фазовом сдвиге с переключателя 8 задания фазового сдвига в реверсивный счетчик 7 с предустановкой, и вернется в исходное состояние RS-триггер б5. Устройство готово к новому периоду измерения и компенсации фазовой ошибки о Рассмотрим случай, когда i Фзас| , т.е, имеет место отставание по фазе синхронизируемого канала относительно опорного, но опережение относительно заданного значения фазового сдвига. Как и в предыдущем случае, импульсы, прошедшие через Временные ворота, будут поступать на вычитающий вход реверсивного счетчика 7 с предустановкой, но в отличив от предыдущего случая, Временные ворота закроются раньше, чем произой дет сравнение поступившего количества импульсов с числом, заданным задатчиком 8 фазового сдвига По заднему фронту положительногО| импульса сигнала Uj сработает однови(5ратор 72 и выработает короткий отрицательный импульс, который теперь уже пройдет через элемент так как RS-;Tpиггep 67 не изменял своего состояния, поскольку не было момента ftsfifP - 9 Короткий отрицательный импульс с выхода элемента Л7 поступит на вход элемента 5б и один из S входов RS-триггера 67t который изменит свое состояние на противоположное. С выхода элемента 5б короткий отрицательный импульс поступает на S вход RS-триггера 69 и R входы RS-триггеров 68 и 70. Это приведет к тому, что на неинвертирующих выходах RSтриггеров 68 и 7Р будут присутствовать потенциалы логичгского О, а на неинведтирующем выходе RS-триггера 69 появится потенциал логической 1, который поступит на один из вхоов элемента-58 и на один из входов элемента Б . С этого момента времени начинаетя процесс компенсации фазовой ошибки пережения. Импульсы частоты /2 поступают дновременно через элементы 58 и 6 на вход реверсивного счетчика lU цифроаналогового преобразователя 12 через элементы 5 и 63 на вычитающий 1592 вход реверсивного счетчика 7 с пред установкой. Таким образом, при поступ лении импульсов частоты f/2 в реверси ный сметчик цифроаналогового преобразователя осуществляется отставание по фазе данного синхронизируемого сигнала по отношению к опорному, где в делитель 3 частоты попрежнему поступают импульсы част оты f, Это отставание будет происходить до тех пор, пока количество импульсов частоты f/2 с учетом количества импульсов частоты f , поступивших за время действия положительного импульса си| нала Uf на вычитающий вход реверсивного счетчика У с предустановкой не станет равным числу, записанному в этот счетчик с задатчика 8 фазового сдвига. В момент равенства на выходе реверсивного счетчика 7 с предустановкой появится короткий положительный импульс, который через элемент f5 пройдет на один из R входов RS-триггера 67 и вернет его в исходное состояние. По перепаду потенциал логической 1 - потенциал логического О на неинаертирующем выходе RS-триггера 67 сработает;, одновибратор 73 и вернет устройство в исходное состояние. Это приведет к тому, что в реверсивный счетчик 10 цифроаналоговогр преобразователя 12 будут проходит импульсы частоты f, а не /2. На это заканчивается процесс измерения и компенсации фазовой ошибки опережения, и цифровой блок коррекции фазового сдвига переходит в режим ожидания до следующего периода измерения В случае, когда -А&о Фото -0 т.е. синхронизируемый сигнал опережа ет по фазе опорный сигнал исходные состояния элементов такие же, как и в предыдущих случаях. Сигнал пред ставляет собой потенциал логического О, который блокирует одновибратор -72, и перепады потенциалов на его входе не приводят к его срабатыванию в этом режиме. Вместе с тем на выходе элемента kQ появляется потенциал логической 1, который разблокирует одноаибратор 71 по одному из блокировочных входово На входы элемента kS приходит сигнал Uj, представляющий собой положительный импульс и потенциал логической 1 с выхода элемента 0. На выходе элемента Э , появится потенциал логической 1 и разрешит прохождение сигнала Ux через элементы 53 и 62 на суммирукхций вход реверсивного счетчика 7 с предустановкой, увеличивая число, записанное в неМо По первому импульсу частоты сигнала U RS-триггер 65 переходит в противоположное состояние, и потенциал логической 1 с его инвертирующего выхода разблокирует одновибратрр 71По окончании положительного импульса сигнала Uj, определяющего абсолютное значение опережения, перепадом потенциал логической 1 - потенциал логического О запустится одновибратор 71 и выработает короткий отрицательный импульс, который переведет в противоположное состояние 1 -триггёр 67, и этот же импульс пройдет через элемент 5б и переведет RS-триггеры 68 и 69 в противоположное состояние. Это приведет к тому, , что импульсы частоты /2 будут поступать через элементы 58 и 64 на вход реверсивного счетчика 10 цифроаналогового преобразователя 12 и через элементы 5 и 63 на вычитающий вход реверсивного счетчика с предустановкой 7, с этого момента закончен процесс измерения, и начинается процесс компенсации фазовой ошибки. Дальнейшая работа устройства аналогична предыдущему случаю с той лишь разницей, что импульс равенства содержимого реверсирного счетчика с предустановкой с количеством импульсов частоты /2, поступивших на его вычитающий вход в процессе компенсации, пройдет на R вход RS-триггера 67 через элемент , так как на управляющем входе его находится потенциал логической 1,. представляющий собой инвертированный сигнал Uy, определяющий знак фазового сдвига Скорректированные сигналы с выхода цифроаналогового преобразователя 12 подаются на .сумматор 14, на второй вход которого подаются через усилитель 23 сигналы с датчика 21 обратной связи. На выходе сумматора 14 формируется разностный сигнал, который вoздeйctвyя на гидроусилитель 16, приводит к тому, что положение стола вибровозбудителя 18 изменяется, изменяется и сигнал, с выхода датчика 21 обратной связи, поступающий на вход усилителя 23 и на вход усилителя-ограничителя 25, что в конечном итоге приводит к коррекции фазы сиг нала в каждом из синхронизируемых каналов. Применение предлагаемого устройства управления многоканальными системами позволяет за счет повышения точности поддержания устанрвленных фазовых сдвигов между синхронизируемыми каналами повысить точность вое

произведения задаваемых воздействий, что позволяет получить определенный технико-экономический эффект.

Формула изобретения

Устройство для управления многоканальным вйбростендом, содержащее последовательно соединенные генератор тaкtoвыx импульсов, преобразователь код - частоте и делитель частоты, а также по числу исполнительных механизмов каналы управления, каждый из которых состоит из последовательно соединенных реверсивного счетчика, цифроаналогового преобразователя, сумматора, гидроусилителя, вибровозключен к входу реверсивного счетчика, вторая группа входов к соответствующим выходам задатчика, а третья группа входов к соответствующим выходам преобразов.теля код - частота причем вхой и выход делителя частоты соединены соответственно с вторым и третьим входами цифрового фазового детектора, а вход усилителя-ограничителя подключен к выходу датчика обратной связи.

Источники информации, принятые во внимание при экспертизе 1. Патент США К 3700588, кл. 73-716, опублик. 1972....

JJ.

DIlliiiiJIillflllllllllllltlillllUlliiillUllillHtlliL

ut

90

i

.

1/3

i t

IX

Tl

n

1Л

Л.

.t ut «.f

../ из

int

-/

on

Ш

JIM

-«./

./

ВНИИПИ Заказ 2817/65 Тираж 908 Подписное филиал ППП Патент, г.Ужгород, ул.Проектная,

-т

/ f

н

Ь

18ff

o/frp

;..,.,,„.,......,.,,.J7,, ,„ .- , .; .

r

Авторы

Даты

1982-04-30—Публикация

1980-01-30—Подача