---Л}

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2003 |

|

RU2254603C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ LDPC-КОДОВ | 2013 |

|

RU2549134C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179365C1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2222822C2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Изобретение относится к технике средств связи и может быть использовано в системах передачи дискретной информации по каналам с шумами, в частности по радиоканалам и стандартным телефонным каналам. Цель изобретения - расширение области применения за счет декодирования произвольных мажоритарно декодируемых линейных кодов. Устройство содержит аналого-цифровой преобразователь 1, блок 2 оперативной памяти, блок 3 отбора минимума, коммутатор 4, счетчики 5 и 6 импульсов, блок 7 памяти, блок 8 оперативной памяти, блок 9 суммирования по модулю два, накопитель 10, регистр 11 сдвига, дешифратор 12, блок 13 управления, ключ 14, блок 15 прерывания и блок 16 инверсии адреса. 2 з.п. ф-лы, 4 ил., 1 табл.

ХЛэ

/Ч г

Ш

1

НУ..я

15

J 4

ON 00 00

Ј

сл

Изобретение относится к технике средств связи и может быть использовано в системах передачи дискретной информации по каналам с шумами, в частности по радиоканалам и стандартным телефоннным каналам.

Цель изобретения - расширение области применения за счет декодирования про- извольных мажоритарно декодируемых линейных кодов.

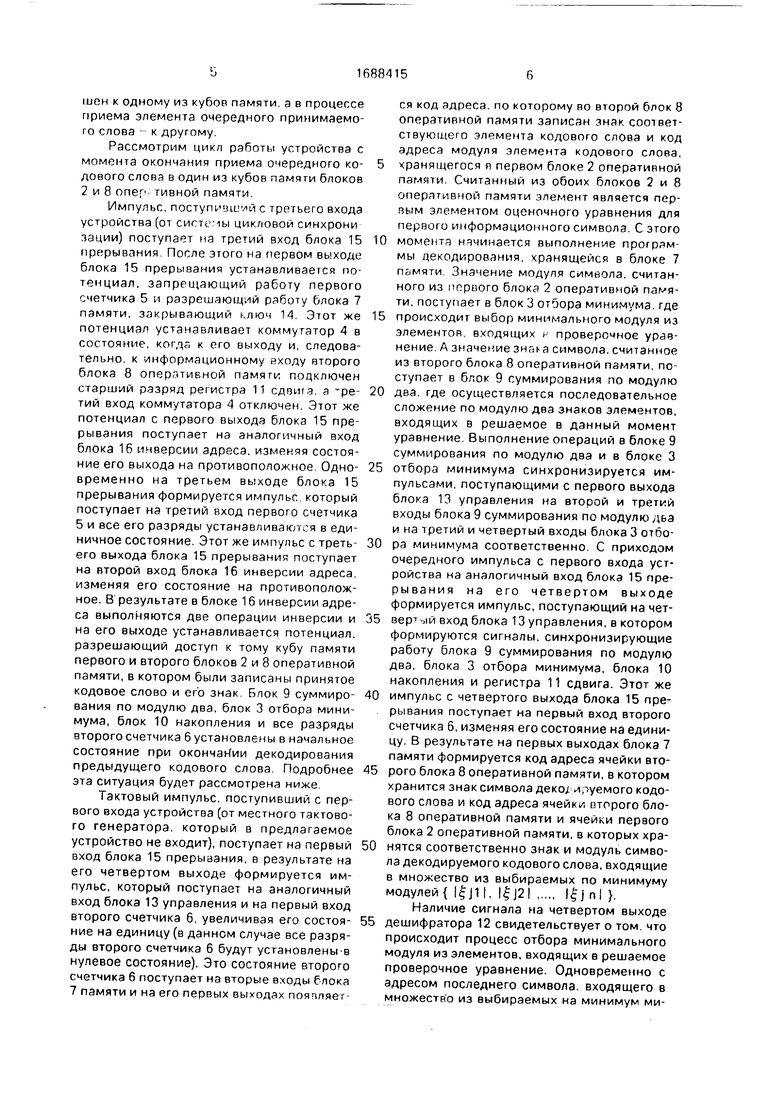

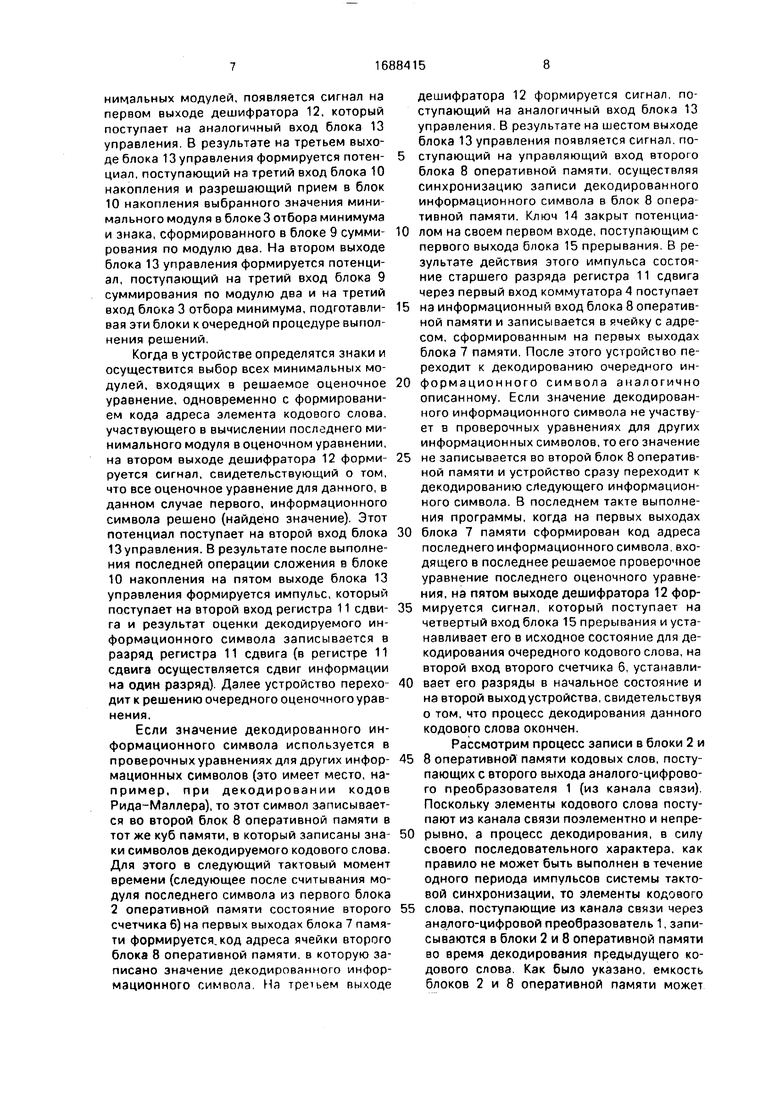

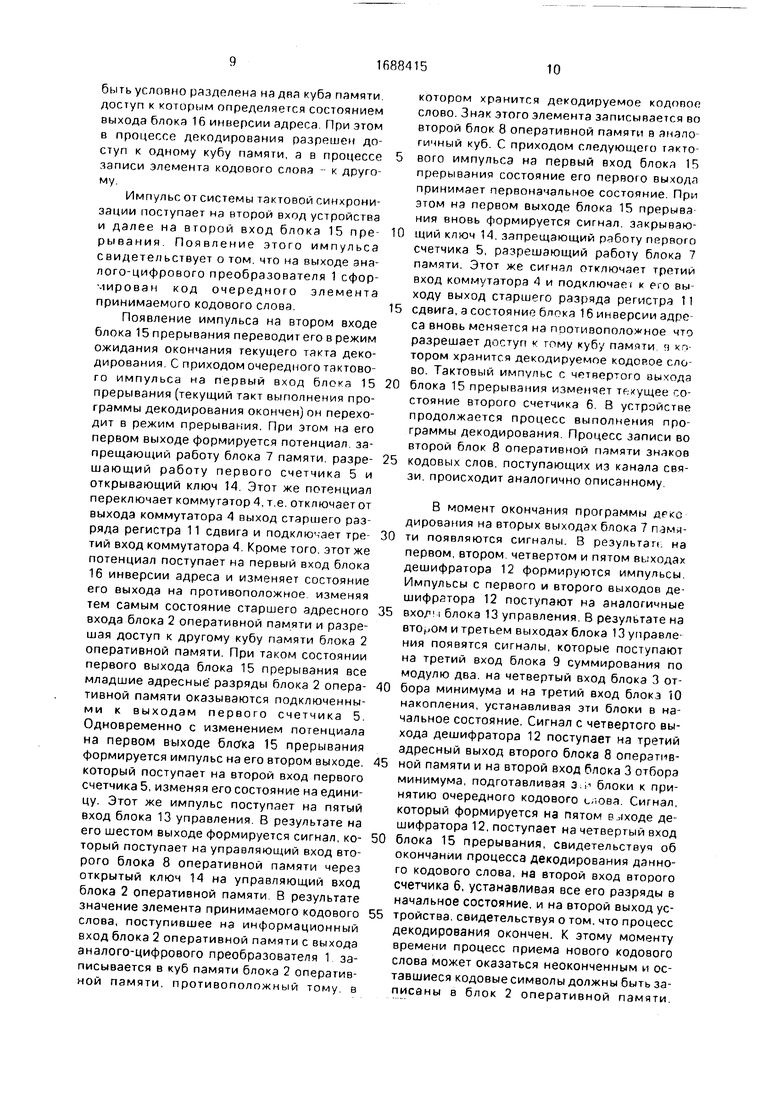

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема блока отбора минимума; на фиг. 3 - функциональная схема дешифратора; на фиг. 4 - функциональная схема блока управления.

Устройство содержит аналого-цифровой преобразователь 1, блок 2 оперативной памяти, блок 3 отбора минимума, коммутатор 4, счетчики 5 и б импульсов, блок 7 памяти, блок 8 оперативной памяти, блок 9 суммирования по модулю два, ьакопитель 10, регистр 11 сдвига, дешифратор 12, блок 13 управления, ключ 14, блок 15 прерывания и блок 16 инверсии адреса.

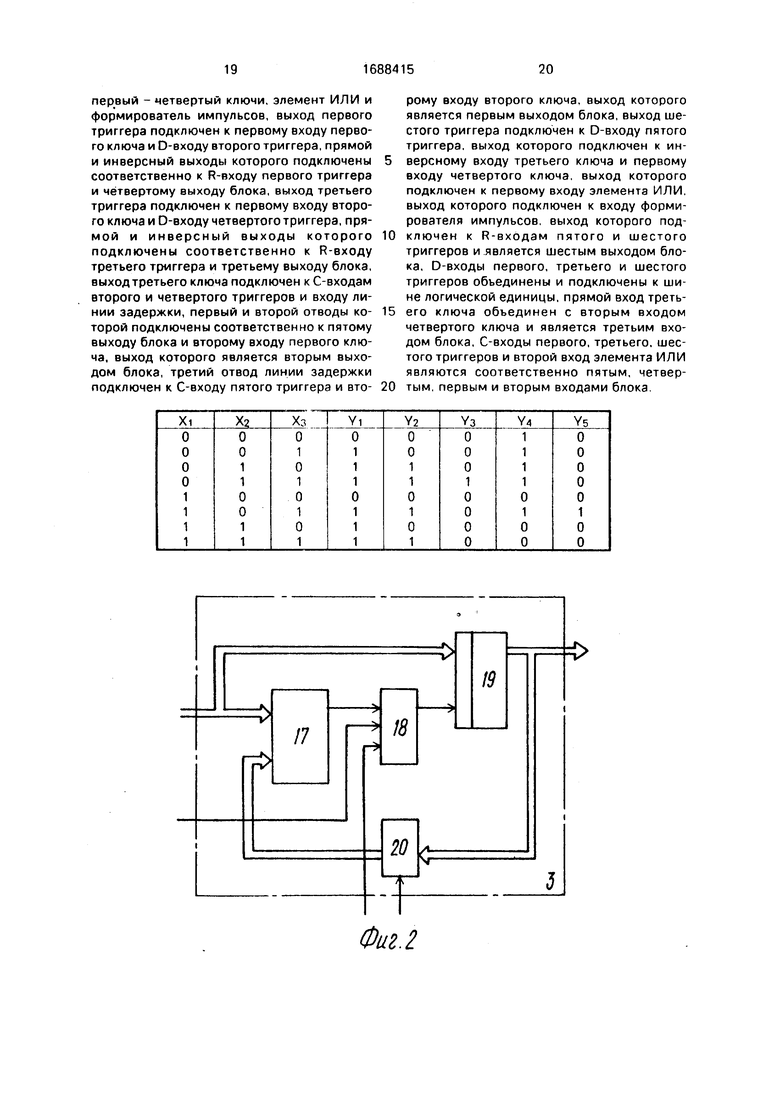

Блок 3 отбора минимума (фиг. 2) содержит сумматор 17, элемент И 18, регистр 19 и группу ключей 20.

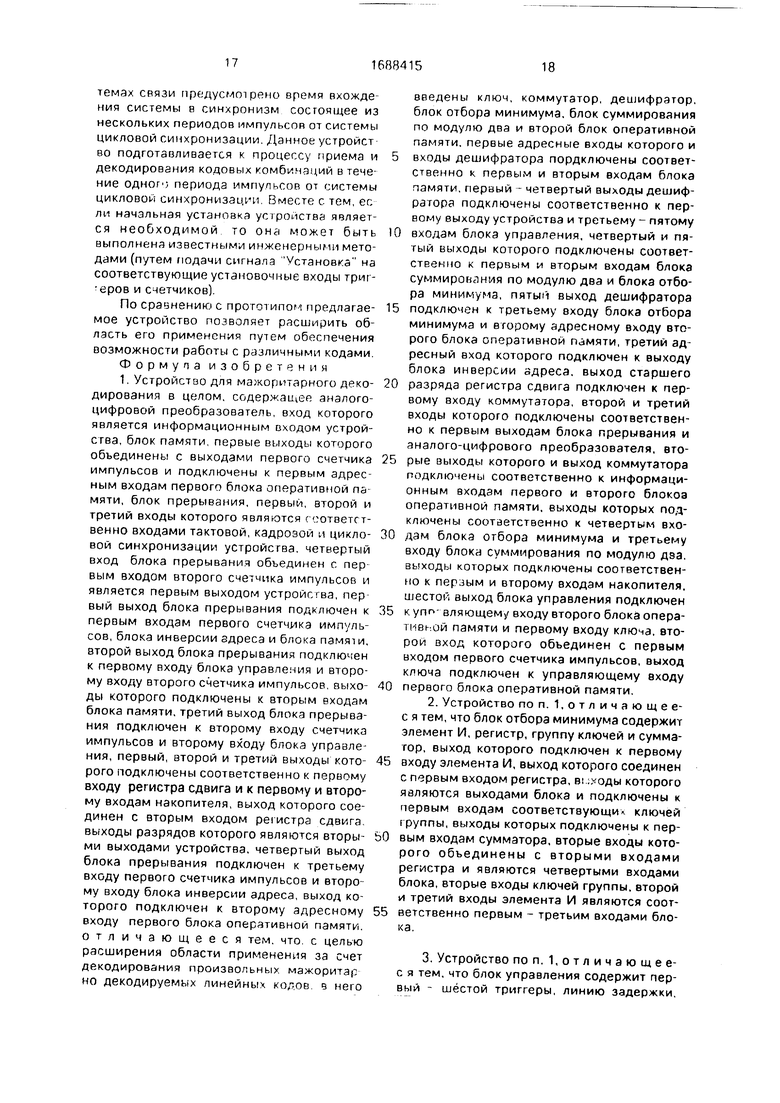

Блок 13 управления (фиг. 4) содержит первый - шестой триггеры 21-26, линию 27 задержки, первый - четвертый ключи 28-31, элемент ИЛИ 32 и формирователь 33 импульсов.

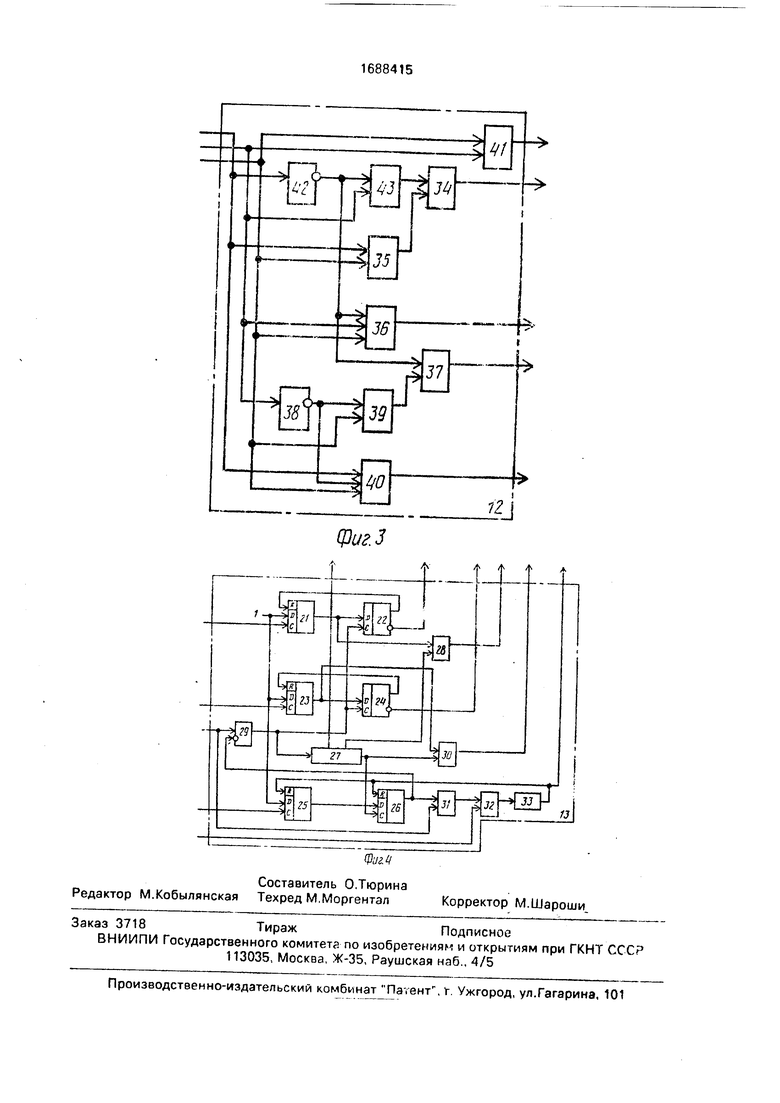

Дешифратор 12 (фиг. 3) содержит элемент ИЛИ 34, элементы И 35 и 36, элемент ИЛИ 37. элемент ИЛИ 38 и элемент И 39, а также элемент И 40, элемент ИЛ И 41, инвертор 42. элемент И 43.

Блок 9 суммирования по модулю два может быть выполнен аналогично одноименному блоку в (1).

Блок 15 прерывания может быть выполнен аналогично одноименному блоку в (2).

Блок 7 памяти выполняется на элементной базе с трехстабильным выходом.

Устройство работает следующим образом.

Компоненты аналогового вектора статистики, представляющие собой результат оптимальной посимвольной обработки сигнала в демодуляторе (в состав предлагаемого устройства не входит), поступают на вход аналого-цифрового преобразователя 1. С выхода аналого-цифрового преобразователя 1 двоичный код каждого символа Јj,j 1 ,п в порядке их следования записывается: модуль - в первый блок 2 оперативной памяти, а его знак через коммутатор 4 - во второй блок 8 оперативной памяти. Запись в оба блока 2 и 8 оперативной памяти производится через информационные входы соответствующих блоков в ячейку с адресом, сформированным на выходах первого счетчика 5.

Коэффициент пересчета первого счетчика 5 должен быть не меньше или равен п. Начальным состоянием счетчиков следует считать установление всех их разрядов в единичное состояние. Число разрядов реги0 стра сдвига 11 выбирается равным К, где п - длина кодового слова используемого кода, К - число информационных символов. Коэффициент пересчета второго счетчика 6 должен быть не меньше суммы/т С + KI/ где

5 т - число тактов программы декодирования, С - суммарное число символов, входящих во все оценочные уравнения для всех информационных символов, Ki -число декодированных информационных символов

0 слов, это необходимо для декодирования, например, кодов Рида-Маллера iKi К- -II.

mx (Iog2 (п + Ki)J + К2 бит, где квадратными скобками обозначена

5 операция нахождения ближайшего целого числа от выражения, стоящего внутри квадратных скобок, К2 - число дополнительных выходов блока 7 памяти.

Объем первого блока 2 оперативной па0 мяти должен быть не меньше 2 п ячеек, каждая из которых состоит из Ы разрядов, где I - разрядность аналого-цифрового преобразователя 1. При этом объем первого блока 2 оперативной памяти может быть

5 разделен на два куба памяти no n ячеек в каждом. В одном из кубов памяти хранятся модули двоичных кодов символов очередного кодового слова, а в другой куб памяти осуществляется запись модулей двоичных

0 кодов символов очередного кодового слова, поступающего из канала связи.

Объем второго блока 8 оперативной памяти должен быть не меньше 2(п + К) ячеек. При этом объем второго блока 8 оператив5 ной памяти также может быть разделен на два куба памяти по п + К ячеек в каждом, В одном из кубов памяти хранятся знаки двоичных кодов символов декодируемого кодового слова, а в другой куб памяти

0 осуществляется запись знаков двоичных кодов символов очередного кодового слова, поступающего из канала связи.

Разрешение доступа к тому или иному кубу памяти осуществляется блоком 16 ин5 версии адреса. Текущее состояние блока 16 инверсии адреса определяет номер куба памяти блоков 2 и 8 оперативной памяти (первый или второй), к которому разрешен доступ в текущий момент времени. При этом в процессе декодирования доступ разрешен к одному из кубов памяти, а в процессе приема элемента очередного принимаемого слова - к другому.

Рассмотрим цикл работы устройства с момента окончания приема очередного кодового слова в один из кубов памяти блоков 2 и 8 опер тивной памяти.

Импульс, поступивший с третьего входа устройства (от сигтечы цикловой синхрони зации) поступает на третий вход блока 15 прерывания После этого на первом выходе блока 15 прерывания устанавливается потенциал, запрещающий работу первого счетчика 5 и разрешающий работу блока 7 памяти, закрывающий ключ 14 Этот же потенциал устанавливает коммутатор 4 в состояние, когда к его выходу и, следовательно, к информационному входу второго блока 8 оперативной памяти подключен старший разряд регистра 11 сдвига, а тре- тий вход коммутатора 4 отключен. Этот же потенциал с первого выхода блока 15 прерывания поступает на аналогичный вход блока 16 инверсии адреса, изменяя состояние его выхода на противоположное Одновременно на третьем выходе блока 15 прерывания формируется импульс который поступает на третий вход первого счетчика 5 и все его разряды устанавливаются в единичное состояние. Этот же импульс с третьего выхода блока 15 прерывания поступает на второй вход блока 16 инверсии адреса, изменяя его состояние на противоположное. В результате в блоке 16 инверсии адреса выполняются две операции инверсии и на его выходе устанавливается потенциал, разрешающий доступ к тому кубу памяти первого и второго блоков 2 и 8 оперативной памяти, в котором были записаны принятое кодовое слово и его знак Блок 9 суммирования по модулю два, блок 3 отбора минимума, блок 10 накопления и все разряды второго счетчика 6 установлены в начальное состояние при окончании декодирования предыдущего кодового слова. Подробнее эта ситуация будет рассмотрена ниже

Тактовый импульс, поступивший с первого входа устройства (от местного тактового генератора, который в предлагаемое устройство не входит), поступает на первый вход блока 15 прерывания, в результате на его четвертом выходе формируется импульс, который поступает на аналогичный вход блока 13 управления и на первый вход второго счетчика 6, увеличивая его состояние на единицу (в данном случае все разряды второго счетчика 6 будут установлены-в нулевое состояние). Это состояние второго счетчика 6 поступает на вторые входы блока 7 памяти и на его первых выходах пояпляегся код адреса, по которому во второй блок 8 оперативной памяти записан знак соответствующего элемента кодового слова и код адреса модуля элемента кодового слова, хранящегося п первом блоке 2 оперативной памяти. Считанный из обоих блоков 2 и 8 оперативной памяти элемент является первым элементом оценочного уравнения для первого информационного символа. С этого

0 момента начинается выполнение программы декодирования, хранящейся в блоке 7 пьмяти Значение модуля символа, считанного из первого блока 2 оперативной памяти, поступает в блок 3 отбора минимума, где

5 происходит выбор минимального модуля из элементов, входящих н проверочное уравнение. А значение символа, считанное из второго блока 8 оперативной памяти, поступает в блок 9 суммирования по модулю

0 два, где осуществляется последовательное сложение по модулю два знаков элементов, входящих в решаемое в данный момент уравнение. Выполнение операций в блоке 9 суммирования по модулю два и в блоке 3

5 отбора минимума синхронизируется импульсами, поступающими с первого выхода блока 13 управления на второй и третий входы блока 9 суммирования по модулю дьа и на третий и четвертый входы блока 3 отбо0 ра минимума соответственно. С приходом очередного импульса с первого входа устройства на аналогичный вход блока 15 пре- рывания на его четвертом выходе формируется импульс, поступающий на чет5 вертый вход блока 13 управления, в котором формируются сигналы, синхронизирующие работу блока 9 суммирования по модулю два, блока 3 отбора минимума, блока 10 накопления и регистра 11 сдвига. Этот же

0 импульс с четвертого выхода блока 15 прерывания поступает на первый вход второго счетчика 6, изменяя его состояние на единицу. В результате на первых выходах блока 7 памяти формируется код адреса ячейки вто5 рого блока 8 оперативной памяти, в котором хранится знак символа деко; ируемого кодового слова и код адреса ячейки второго блока 8 оперативной памяти и ячейки первого блока 2 оперативной памяти, в которых хра0 нятся соответственно знак и модуль символа декодируемого кодового слова, входящие в множество из выбираемых по минимуму

модулей{ |ЈJ1|, ||J2| lЈjnl }.

Наличие сигнала на четвертом выходе

5 дешифратора 12 свидетельствует о том. что происходит процесс отбора минимального модуля из элементов, входящих в решаемое проверочное уравнение. Одновременно с адресом последнего символа, входящего в множеств о из выбираемых на минимум миницальных модулей, появляется сигнал на первом выходе дешифратора 12, который поступает на аналогичный вход блока 13 управления. В результате на третьем выходе блока 13 управления формируется потенциал, поступающий на третий вход блока 10 накопления и разрешающий прием в блок 10 накопления выбранного значения минимального модуля в блоке 3 отбора минимума и знака, сформированного в блоке 9 суммирования по модулю два. На втором выходе блока 13 управления формируется потенциал, поступающий на третий вход блока 9 суммирования по модулю два и на третий вход блока 3 отбора минимума, подготавливая эти блоки к очередной процедуре выполнения решений.

Когда в устройстве определятся знаки и осуществится выбор всех минимальных модулей, входящих в решаемое оценочное уравнение, одновременно с формированием кода адреса элемента кодового слова, участвующего в вычислении последнего минимального модуля в оценочном уравнении, на втором выходе дешифратора 12 формируется сигнал, свидетельствующий о том, что все оценочное уравнение для данного, в данном случае первого, информационного символа решено (найдено значение). Этот потенциал поступает на второй вход блока 13управления. В результате после выполнения последней операции сложения в блоке 10 накопления на пятом выходе блока 13 управления формируется импульс, который поступает на второй вход регистра 11 сдвига и результат оценки декодируемого информационного символа записывается в разряд регистра 11 сдвига (в регистре 11 сдвига осуществляется сдвиг информации на один разряд). Далее устройство переходит к решению очередного оценочного уравнения.

Если значение декодированного информационного символа используется в проверочных уравнениях для других информационных символов (это имеет место, например, при декодировании кодов Рида-Маллера), то этот символ записывается во второй блок 8 оперативной памяти в тот же куб памяти, в который записаны знаки символов декодируемого кодового слова. Для этого в следующий тактовый момент времени (следующее после считывания модуля последнего символа из первого блока 2 оперативной памяти состояние второго счетчика 6) на первых выходах блока 7 памяти формируется, код адреса ячейки второго блока 8 оперативной памяти, в которую записано значение декодированного информационного символа. На третьем выходе

дешифратора 12 формируется сигнал, поступающий на аналогичный вход блока 13 управления. В результате на шестом выходе блока 13 управления появляется сигнал, поступающий на управляющий вход второго блока 8 оперативной памяти, осуществляя синхронизацию записи декодированного информационного символа в блок 8 оперативной памяти. Ключ 14 закрыт потенциа0 лом на своем первом входе, поступающим с первого выхода блока 15 прерывания. В результате действия этого импульса состояние старшего разряда регистра 11 сдвига через первый вход коммутатора 4 поступает

5 на информационный вход блока 8 оперативной памяти и записывается в ячейку с адресом, сформированным на первых выходах блока 7 памяти. После этого устройство переходит к декодированию очередного ин0 формационного символа аналогично описанному. Если значение декодированного информационного символа не участвует в проверочных уравнениях для других информационных символов, то его значение

5 не записывается во второй блок 8 оперативной памяти и устройство сразу переходит к декодированию следующего информационного символа. В последнем такте выполнения программы, когда на первых выходах

0 блока 7 памяти сформирован код адреса последнего информационного символа, входящего в последнее решаемое проверочное уравнение последнего оценочного уравнения, на пятом выходе дешифратора 12 фор5 мируется сигнал, который поступает на четвертый вход блока 15 прерывания и устанавливает его в исходное состояние для декодирования очередного кодового слова, на второй вход второго счетчика 6, устанавли0 вает его разряды в начальное состояние и на второй выход устройства, свидетельствуя о том, что процесс декодирования данного кодового слова окончен.

Рассмотрим процесс записи в блоки 2 и

5 8 оперативной памяти кодовых слов, поступающих с второго выхода аналого-цифрового преобразователя 1 (из канала связи). Поскольку элементы кодового слова поступают из канала связи поэлементно и непре0 рывно, а процесс декодирования, в силу своего последовательного характера, как правило не может быть выполнен в течение одного периода импульсов системы тактовой синхронизации, то элементы кодового

5 слова, поступающие из канала связи через аналого-цифровой преобразователь 1, записываются в блоки 2 и 8 оперативной памяти во время декодирования предыдущего кодового слова. Как было указано, емкость блоков 2 и 8 оперативной памяти может

быть условно разделена на двя куба памяти, доступ к которым определяется состоянием выхода блока 16 инверсии адреса При этом в процессе декодирования разрешен доступ к одному кубу памяти, а в процессе записи элемента кодового слова - к другому.

Импульс от системы тактовой синхронизации поступает на второй вход устройства и далее на второй вход блока 15 прерывания. Появление этого импульса свидетельствует о том. что на выходе аналого-цифрового преобразователя 1 сформирован код очередного элемента принимаемого кодового слова.

Появление импульса на втором входе блока 15 прерывания переводит его в режим ожидания окончания текущего такта декодирования. С приходом очередного тактового импульса на первый вход блока 15 прерывания (текущий такт выполнения программы декодирования окончен) он переходит в режим прерывания. При этом на его первом выходе формируется потенциал, запрещающий работу блока 7 памяти, разрешающий работу первого счетчика 5 и открывающий ключ 14. Этот же потенциал переключает коммутатор 4, т.е. отключает от выхода коммутатора 4 выход старшего разряда регистра 11 сдвига и подключает третий вход коммутатора 4. Кроме того, этот же потенциал поступает на первый вход блока 16 инверсии адреса и изменяет состояние его выхода на противоположное изменяя тем самым состояние старшего адресного входа блока 2 оперативной памяти и разрешая доступ к другому кубу памяти блока 2 оперативной памяти. При таком состоянии первого выхода блока 15 прерывания все младшие адресные разряды блока 2 оперативной памяти оказываются подключенными к выходам первого счетчика 5. Одновременно с изменением потенциала на первом выходе блеска 15 прерывания формируется импульс на его втором выходе, который поступает на второй вход первого счетчика 5, изменяя его состояние на единицу. Этот же импульс поступает на пятый вход блока 13 управления. В результате на его шестом выходе формируется сигнал, который поступает на управляющий вход второго блока 8 оперативной памяти через открытый ключ 14 на управляющий вход блока 2 оперативной памяти В результате значение элемента принимаемого кодового слова, поступившее на информационный вход блока 2 оперативной памяти с выхода аналого-цифрового преобразователя 1 записывается в куб памяти блока 2 оперативной памяти, противоположный тому, в

котором хранится декодируемое кодовое слово. Знак этого элемента записывается во второй блок 8 оперативной памяти в аналогичный куб. С приходом следующего такто5 вого импульса на первый вход блока 15 прерывания состояние его первого выхода принимает первоначальное состояние. При этом на первом выходе блока 15 прерывания вновь формируется сигнал, эакрываю0 щий ключ 14, запрещающий работу первого счетчика 5, разрешающий работу блока 7 памяти. Этот же сигнал отключает третий вход коммутатора 4 и подключав к его выходу выход старшего разряда регистра 11

5 сдвига, а состояние блока 16 инверсии адреса вновь меняется на противоположное что разрешает доступ тому кубу памяти п котором хранится декодируемое кодовое слово. Тактовый импульс с четвертого выхода

0 блока 15 прерывания изменяет текущее состояние второго счетчика 6. В устройстве продолжается процесс выполнения программы декодирования. Процесс записи во второй блок 8 оперативной памяти знаков

5 кодовых слов, поступающих из канала связи, происходит аналогично описанному.

В момент окончания программы ДРКС дирования на вторых выходах блока 7 памн0 ти появляются сигналы. В результэп. на первом, втором, четвертом и пятом выходах дешифратора 12 формируются импульсы. Импульсы с первого и второго выходов дешифратора 12 поступают на аналогичные

5 вхо/111 блока 13 управления. В результате на втором и третьем выходах блока 13 управления появятся сигналы, которые поступают на третий вход блока 9 суммирования по модулю два. на четвертый вход блока 3 от0 бора минимума и на третий вход блока 10 накопления, устанавливая эти блоки в начальное состояние. Сигнал с четвертого выхода дешифратора 12 поступает на третий адресный выход второго блока 8 оператив5 ной памяти и на второй вход блока 3 отбора минимума, подготавливая з.,- блоки к принятию очередного кодового слова. Сигнал, который формируется на пятом выходе дешифратора 12, поступает на четвертый вход

0 блока 15 прерывания, свидетельствуя об окончании процесса декодирования данного кодового слова, на второй вход второго счетчика 6, устанавливая все его разряды в начальное состояние, и на второй выход ус5 тройства, свидетельствуя о том, что процесс декодирования окончен. К этому моменту времени процесс приема нового кодового слова может оказаться неоконченным и оставшиеся кодовые символы должны быть записаны в блок 2 оперативной памяти.

Появление сигнала на четвертом входе блока 15 прерывания с пятого выхода дешифратора 12 вызывает формирование потенциала на первом выходе блока 15 прерывания, запрещающего работу блока 7 памяти, открывающего ключ 14, разрешающего работу первого счетчика 5 и изменяющего состояние выхода блока 16 инверсии адреса на противоположное. Этот же потенциал переключает коммутатор 4, т.е. отключает от выхода коммутатора 4 выход старшего разряда регистра 11 сдвига и подключает третий вход коммутатора 4. Этот потенциал на первом выходе блока 15 прерывания сохраняется неизменным до прихода импульса на eio третий вход. С приходом этого импульса описанные процессы декодирования и приема повторяются. С приходом очередного импульса на второй вход блока 15 прерывания блок 15 прерывания переходит в режим ожидания, и с приходом очередного тактово. о импульса на его первый вход на его BIOTJM выходе формируется потенциал, изменяющий состояние первого счетчика 5 на единицу. Этот же потенциал поступает на пятый вход блока 13 управления, в результате; на его шестом выходе формируется импульс, который поступает на управляющий вход перво- го блока 2 оперативной памяти и через ключ 14 - на управляющий вход второго блока 8 оперативной памяти. Таким образом осуществляется запись очередного символа и его знака принимаемого кодового слова, поступившего с первого и вторых выходов аналого-цифрового преобразователя 1 на информационные входы первого и второго блоков 2 и 8 оперативной памяти (причем с первого выхода аналою-цифрового преобразователя 1 импульс поступает на управляющий вход блока 8 оперативной памяти через третий вход коммутатора 4) по адресу, сформированному на выходах первого счетчика 5 и на выходе блока 16 инверсии адреса.

С приходом очередного тактового импульса на третий вход блока 15 прерывания с входа цикловой синхронизации, что свидетельствует о том, что все принимаемое кодовое слово и его знак приняты в блоки 2 и 8 оперативной памяти, устройство переходит в режим декодирования. При этом на первом выходе блока 15 прерывания формируется импульс, который переключает коммутатор 4 (отключает выход блока 3 и подключает к выходу коммутатора 4 выход старшего разряда регистра 11 сдвига), закрывает ключ 14. запрещает работу первого счетчика 5, разрсмиае работу блока 7 памяти. Этот же потенциал поступаем на первый

вход блока 16 инверсии адреса, изменяя его состояние на противоположное. Одновременно на четвертом выходе блока 15 прорывания формируется импульс, который

поступает на вход блока 16 инверсии адреса, также изменяя его состояние на противоположное. Таким образом, в блоке 16 инверсии адреса выполняются две операции инверсии и на его выходе устанавливается потенциал, разрешающий доступ к тому кубу памяти блоков 2 и 8 оперативной памяти, в который были записаны принятое кодовое слово и его знак.

С третьего выхода блока 15 прерывания

импульс поступает на третий вход первого счетчика 5, устанавливая все его разряды в начальное состояние. Второй счетчик устанавливается в начальное состояние импульсом с пятого выхода дешифратора 12 после

окончания программы декодирования. Далее процесс декодирования повторяется.

Блок 3 отбора минимума (фиг, 2) работает следующим образом.

Сигнал с инверсного выхода триггера 22

блока 13 управления поступает через четвертый вход блока 3 отбора минимума на вторые входы группы ключей 20, закрывая их, тем самым устанавливая блок 3 отбора минимума в начальное состояние, т.е. нахождение модуля минимального элемента, входящего в решаемое в данный момент времени управление, будет начинаться с нуля. После того, как на первых входах блока 3 отбора минимума сформировано значение

модуля очередного элемента, входящего в решаемое уравнение, на третьем входе блока 3 отбора минимума появится синхроимпульсе первого выхода блока 13 управления через время п , необходимое для срабатывания второго счетчика 6, блока 7 памяти, первого блока 2 оперативной памяти, сумматора 17 блока 3 отбора минимума. В результате данный элемент записывается в регистр 19 блока 3 отбора минимума, так как

группа ключей 20 закрыта сигналом с второго выхода блока 13 управления, т.е. на вторых входах сумматора 17 потенциал логического нуля. Будем считать, что первая группа входов сумматора 17 является вычитающей, а вторая - суммирующей. Наличие нуля на вторых входах сумматора 17 означает, что сравнение модуля первого элемента осуществляется с нулем. После окончания обработки первого элемента запрещающий

сигнал на вторых входах группы ключей 20 заканчивается. С приходом следующего синхроимпульса на первой группе входов сумматора 17 формируется модуль следующего элемента, входящий в данное уравнение, а ранее записанный в регистр модуль первого элемента поступает через группу ключей 20 на вторую группу входов сумма тора 17, где производится операция сравнения. Запись в регистр осуществляется, если модуль принимаемого элемента меньше модуля хра-.ящегося в регистрМЭ. Если результат « равнения имеет отрицательный знак, то запись в регистр 19 не производится. Это означает, что в регистре находится модуль наименьшего из ранее принятых элементов С приходом очередного синхрс импульса с первого выхода блока 3 отбора минимума последнею модуля элемента в решстре 19 оказывается сформирован минимальный модуль из элементов, входящих в решаемое в данный мсмечт уравнение. Полученный результат передается в накопитель 10усфОйс1вл С приходом модуля первого элемента описанный процесс повторяется. Импульс, поступающий с четвертого выхода дешифратора 12 необходим для блокировки работы блока 3 отбора минимума на время прохождения процесса декодирования, когда блок 3 отбора минимума не задействуется.

Работа одного из возможных варианте дешифратора 12 понятна из описания и приведенной таблицы истинности. Дл ч данного варианта логического блока программа декодирования, хранящаяся в блоке 7 памяти, будет иметь следующую особенность. Значения Xi, ранее декодированные, не должны быть последними в системе оценочных уравнений и последними во всей программе декодирования, если декодируемый данной системой Xj подлежит записи гзо второй блок 8 оперативной памяти. Данное ограничение является легковыполнимым и не вызывает трудностей для программирования блока 7 памяти. Этот вариант схемного решения дешифратора 12 представляется наиболее целесообразным. Однако если эти ограничения являются нежелательными, тогда управляющая шина (вторые выходы) блока 7 памяти должна иметь четыре выхо да, что даег возможность использовать в дешифраторе 12 шестнадцать состояний, а не восемь, как в предлагаемом варианте Однако это приведет к увеличению емкости блока 7 памяти, что может быть существенным при декодировании длинных кодов.

Дешифратор 12 работает следующим образом.

При отсутствии сигналов на всех трех входах дешифратора 12 сигнал появится на его четвергом выходе. Это свидетельствует о том. что происходит нормальная работа (процесс декодирования). С появлением сигнала нз третьем входе дешифратора 12

(с вторых выходов блока 7 памяти) появятся сигналы на его первом и четвертом выходах Это свидетельствует о том что текущее уравнение решено. С появлением сигнала на втором входе дешифратора 12 (с вторых выходов блока 7 памяти) появятся сигналы на его первом, втором и четвертом выходах, Это свидетельствует о том, что система проверочных уравнений для данного информа0 ционного символа решена (найдено значение XiJ. С появлением сигналов на втором и третьем входах дешифратора 12 появятся сигналы на первых его четырех выходах Это свидетельствует о том. «то воз5 никла необходимость записи Xi во второй блок 8 оперативной пэмяти. При появлении сигнала на г ервом входе дешифратора 12 сигналы на всех его пяти выходах отсутствуют. Это свидетельствует о том, что

0 происходит обращение во второй блок 8 оперативной пэмяти к Х|, т.е. возникла необходимость переадресации второго блока 8 оперативной памяти. При появлении сигнала на первом итретьем входахдешифратора

5 12 появляются сигналы на его первом, втором, четвертом и пятом выходах Это свидетельствует о том, что процесс, декодирования окончен. При появлении сигнллов на первом и втором входах дешифратора 12

0 появится сигнал на его первом выходе. Это означает, что происходит обращение во второй блок 8 оперативной памяти к Xi при окончании текущего уравнения. При появлении cm налов на трех входах дешифратора

5 12 вятся сигналы на его первом и втором выходах. Это означает, что происходит обращение во второй блок 8 оперативной памяти к Я| при окончании решения системы уравнений для данного информационного

0 символа Таблица истинности для дешифратора 12 приведена ниже.

Блок 13 управления (фиг. 4) работает следующим образом.

Сигнал с первого выхода дешифратора

5 12 устройства поступает через аналогичный вход блока 13 управления ..г синхровход первого триггера 21 и устанасливает его в единичное состояние. Это свидетельствует о том, что текущее уравнение решено (най0 ден модуль минимального элемента и определен его знак). Очередной импульс с четвертого выхода блока 15 прерывания через четвертый вход блока 13 управления и через открытый второй ключ 29 поступает на

5 синхровход второго триггера 22 и устанавливает его в единичное состояние, так как на его D-входе был установлен единичный потенциал с выхода первого триггера 21. В результате первый триггер 21 устанавливается в нулевое состояние сигналом, поступившим о выхода второго триггера 22 на R-вход первого триггера 21 Сигнал с инверсного выхода второго триггера 22 поступает на второй вход болка 13 управления и далее через четвертый вход блока 3 отбора мини- мума и через третий вход блока 9 суммирования по модулю два - на соответствующие ключи, закрывая их, тем самым устанавливая эти блоки в начальное состояние, т.е. решение очередного уравнения (нахожде- ние модуля минимального элемента и оценка его знака в блоке 9 суммирования по модулю два) начинается с нуля. Тактовые импульсы на первый выход блока 13 управления поступают непосредственно с перво- го выхода линии 27 задержки через время ri необходимое для срабатывания второго счетчика 6, блока 7 памяти и второго блока 8 оперативной памяти. Сигнал с второго выхода логического блока дешифратора 12 че- рез аналогичный вход блока 13 управления поступает на синхровход третьего триггера 23, устанавливая его в единичное состояние, так как на его D-входе установлен потенциал логической единицы. Поступление сигнала с второго выхода логического блока дешифратора 12 свидетельствует о том, что на первых адресных выходах блока 7 памяти находится адрес последнего элемента, входящего в последнее проверочное уравне- ние, решаемое в данный момент времени, т.е. после обработки этого элемента и приема результата в накопитель 10 процесс декодирования данного информационного символа заканчивается (этот сигнал появля- ется совместно с приходом сигнала с первого выхода дешифратора 12). Очередной импульс с четвертого выхода блока 15 прерывания через аналогичный вход блока 13 управления и через открытый второй ключ 29 поступает на синхровход четвертого триггера 24 и устанавливает его в единичное состояние. В результате третий триггер 23 устанавливается в нулевое состояние сигналом, поступившим с выхода четвертого триг- гера 24 на R-вход третьего триггера 23. Сигнал с инверсного выхода четвертого триггера 24 поступает на третий выход блока 13 управления и далее через третий вход накопителя 10 - на вторые выходы блока ключей 20, закрывая их и тем самым подготавливая накопитель 10 к решению следующей системы уравнений. Единичный потенциал с выхода первою триггера 21 поступает на первый вход первого ключа 28. открывая его. В результате появляется импульс на четвертом выходе блока 13 управления, поступающий с второго выхода линии 27 задержки через вррмч (г i - TI} где

Г2 - время, наибольшее из необходимых для срабатывания блока 9 суммирования по модулю два. либо блока 3 отбора минимума Далее этот импульс через открытый первый ключ 28 поступает на вход (вход синхронизации параллельного приема) накопителя 10. Сигнал, поступающий с выхода третьего триггера 23, подается на первый вход третьего ключа 30, тем самым открывая его. В результате импульс с третьего выхода линии 37 задержки через время (т + гг + гз) относительно появления сигнала на ее входе, где Гз - время, необходимое для срабатывания накопителя 10, поступает через открытый третий ключ 30 на пятый выход блока 13 управления. Этот импульс синхронизирует прием в сдвиговый регистр 11 результата декодирования очередного информационного символа. Если этот декодированный информационный символ необходимо записать во второй блок 8 оперативной памяти, то вместе с сигналами на первом и втором выходах дешифратора 12 появится сигнал на его третьем выходе. Этот сигнал через третий вход блока 13 управления поступает на синхровход пятого триггера 25, устанавливая его в единичное состояние. Сигналом, поступающим с третьего выхода линии 27 задержки через время (п +Т2 + гз), относительно появления сигнала на ее входе, в единичное состояние устанавливается шестой триггер 26. В результате закрывается второй ключ 29 и открывается четвертый ключ 31. Сигнал с четвертого входа блока 13 управления поступает через открытый четвертый ключ 31 и первый вход элемента 32 на вход формирователя 33 импульсов. В результате через время, необходимое для приема информации во второй блок 8 оперативной памяти, на выходе формирователя 33 импульсов появится импульс, который поступает на шестой выход блока 13 управления и далее - на управляющий вход второго блока 8 оперативной памяти. Управление записью в первый блок 2 оперативной памяти осуществляется через ключ 14. Сигнал поступающий с второго выхода блока 15 прерывания через пятый вход блока 13 управления на второй вход элемента ИЛИ 32 и далее на вход формирователя 33 импульсов, вызывает описанные процессы.

Начальная установка устройства (установка всех счетчиков, триггеров и регистров, входящих в состав устройства, в исходное состояние после подачи питания) является несущественной и в данном устройстве не предусмотрена, поскольку перед началом сеанса связи в существующих сиетемах связи предусмотрено время вхождения системы в синхронизм состоящее из нескольких периодов импульсов от системы цикловой синхронизации. Данное устройст во подготавливается к процессу приема и декодирования кодовых комбинаций в течение одного периода импупьсов от системы цикловой синхронизации. Вместе с тем, ее ли начальная установка устройства является необходимой то она может быть выполнена известными инженерными методами (путем подачи сигнала Установка на соответствующие установочные входы триг- еров и счетчиков).

По сравнению с прототипом предлагаемое устройство позволяет расширить область его применения путем обеспечения возможности работы с различными кодами. Формупа изобретения 1. Устройство для мажоритарного декодирования в целом, содержащее аналого- цифровой преобразователь, вход которого является информационным входом устройства, блок памяти, первые выходы которого объединены с выходами первого счетчика импульсов и подключены к первым адресным входам первого блока оперативной памяти, блок прерывания, первый, второй и третий входы которого являются соответственно входами тактовой, кадровой и цикловой синхронизации устройства, четвертый вход блока прерывания объединен с первым входом второго счетчика импульсов и является первым выходом устройства, первый выход блока прерывания подключен к первым входам первого счетчика импульсов, блока инверсии адреса и блока памяти, второй выход блока прерывания подключен к первому входу блока управления и второму входу второго счетчика импульсов, выходы которого подключены к вторым входам блока памяти, третий выход блока прерывания подключен к второму входу счетчика импульсов и второму входу блока управления, первый, второй и третий выходы которого подключены соответственно к первому входу регистра сдвига и к первому и второму входам накопителя, выход которого соединен с вторым входом режстра сдвига, выходы разрядов которого являются вторыми выходами устройства, четвертый выход блока прерывания подключен к третьему входу первого счетчика импульсов и второ му входу блока инверсии адреса, выход которого подключен к второму адресному входу первого блока оперативной памяти. отличающееся тем. что. с целью расширения области применения за счет декодирования произвольных мажоритар но декодируемых линейных колов в него

введены ключ, коммутатор, дешифратор, блок отбора минимума, блок суммирования по модулю два и второй блок оперативной памяти, первые адресные входы которого и входы дешифратора пордключены соответственно к первым и вторым входам блока памяти, первый - четвертый выходы дешифратора подключены соответственно к первому выходу устройства и третьему - пятому

входам блока управления, четвертый и пятый выходы которого подключены соответственно к первым и вторым входам блока суммирования по модулю два и блока отбора минимума, пятый выход дешифратора

подключен к третьему входу блока отбора минимума и второму адресному входу второго блока оперативной памяти, третий адресный вход которого подключен к выходу блока инверсии адреса, выход старшего

разряда регистра сдвига подключен к первому входу коммутатора, второй и третий входы которого подключены соответственно к первым выходам блока прерывания и аналого-цифрового преобразователя, вторые выходы которого и выход коммутатора подключены соответственно к информационным входам первого и второго блоков оперативной памяти, выходы которых подключены соответственно к четвертым входам блока отбора минимума и третьему входу блока суммирования по модулю два, выходы которых подключены соответственно к перзым и второму входам накопителя. шестой выход блока управления подключен

к вляющем/ входу второго блока опера- i йеной памяти и первому входу ключа, второй вход которого объединен с первым входом первого счетчика импульсов, выход ключа подключен к управляющему входу

первого блока оперативной памяти.

входу элемента И, выход которого соединен с первым входом регистра, BI ;ходы которого являются выходами блока и подключены к первым входам соответствующие ключей группы, выходы которых подключены к первым входам сумматора, вторые входы которого объединены с вторыми входами регистра и являются четвертыми входами блока, вторые входы ключей группы, второй и третий входы элемента И являются соответственно первым - третьим входами блока.

первый -четвертый ключи, элемент ИЛИ и формирователь импульсов, выход первого триггера подключен к первому входу первого ключа и D-входу второго триггера, прямой и инверсный выходы которого подключены соответственно к R-входу первого триггера и четвертому выходу блока, выход третьего триггера подключен к первому входу второго ключа и D-входу четвертого триггера, пря- мой и инверсный выходы которого подключены соответственно к R-входу третьего триггера и третьему выходу блока, выход третьего ключа подключен к С-входам второго и четвертого триггеров и входу линии задержки, первый и второй отводы ко- торой подключены соответственно к пятому выходу блока и второму входу первого ключа, выход которого является вторым выходом блока, третий отвод линии задержки подключен к С-входу пятого триггера и вто-

рому входу второго ключа, выход которого является первым выходом блока, выход шестого триггера подключен к D-входу пятого триггера, выход которого подключен к инверсному входу третьего ключа и первому входу четвертого ключа, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к входу формирователя импульсов, выход которого подключен к R-входам пятого и шестого триггеров и является шестым выходом блока, D-входы первого, третьего и шестого триггеров обьединены и подключены к шине логической единицы, прямой вход третьего ключа объединен с вторым входом четвертого ключа и является третьим входом блока, С-входы первого, третьего, шестого триггеров и второй вход элемента ИЛИ являются соответственно пятым, четвертым, первым и вторым входами блока

Фиг. 2

фиг.З

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-10-30—Публикация

1989-03-24—Подача