10

11Д71313

Изобретение относится к технике передачи дискретных сообщений и может быть использовано для передачи цифровой информации по каналам с шумами .

Цель изобретения - повьшение достоверности декодирования.

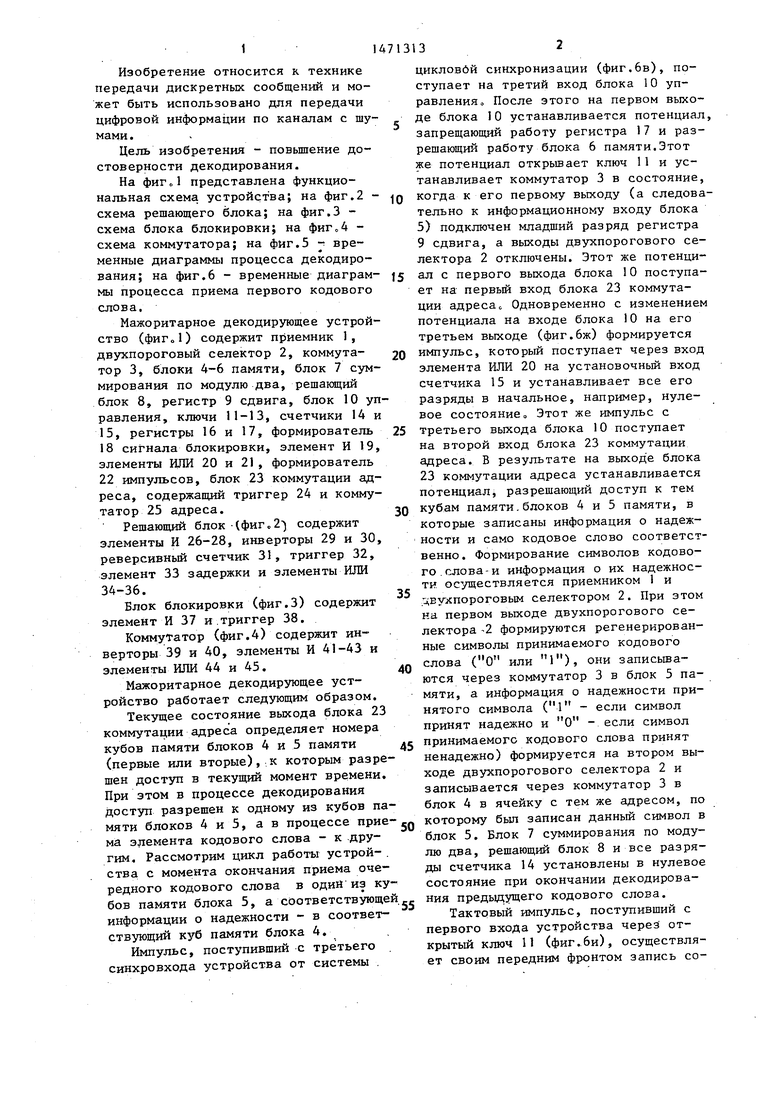

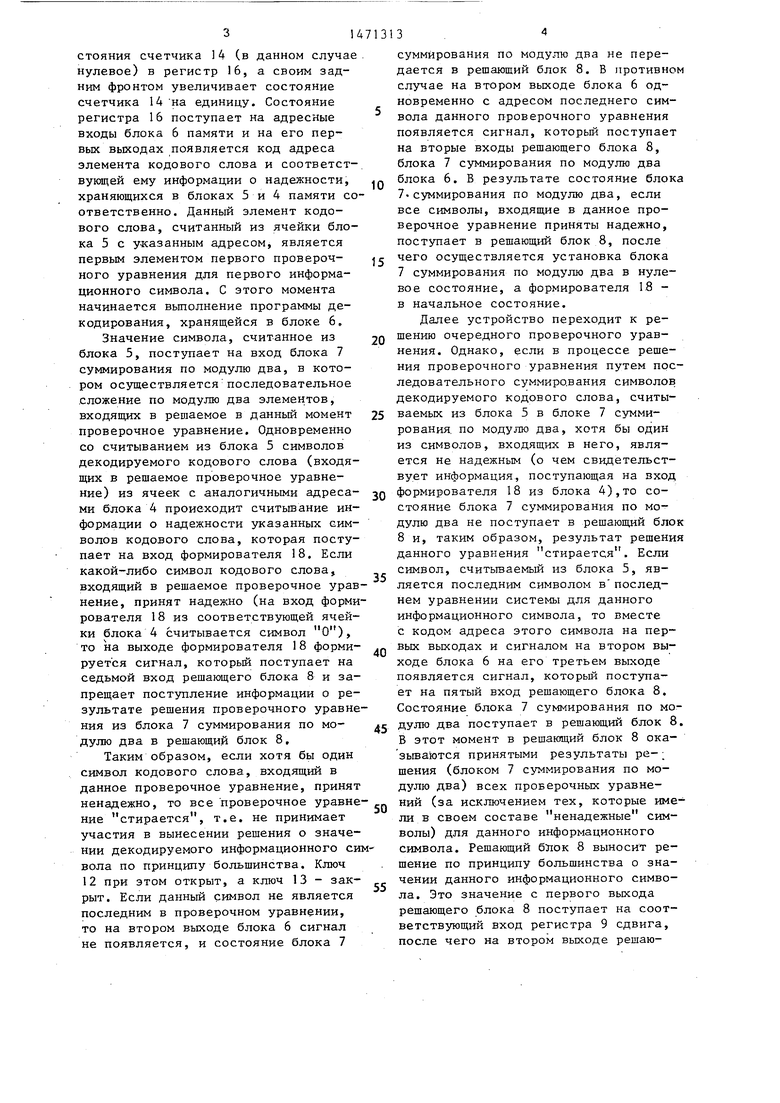

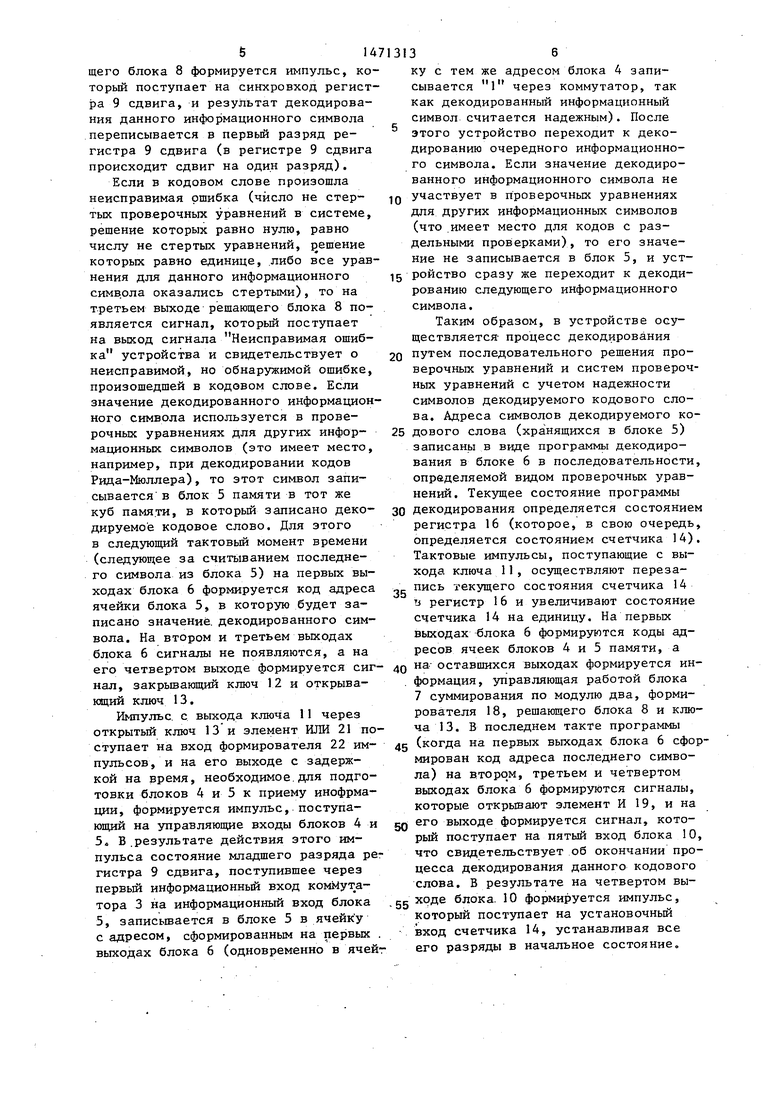

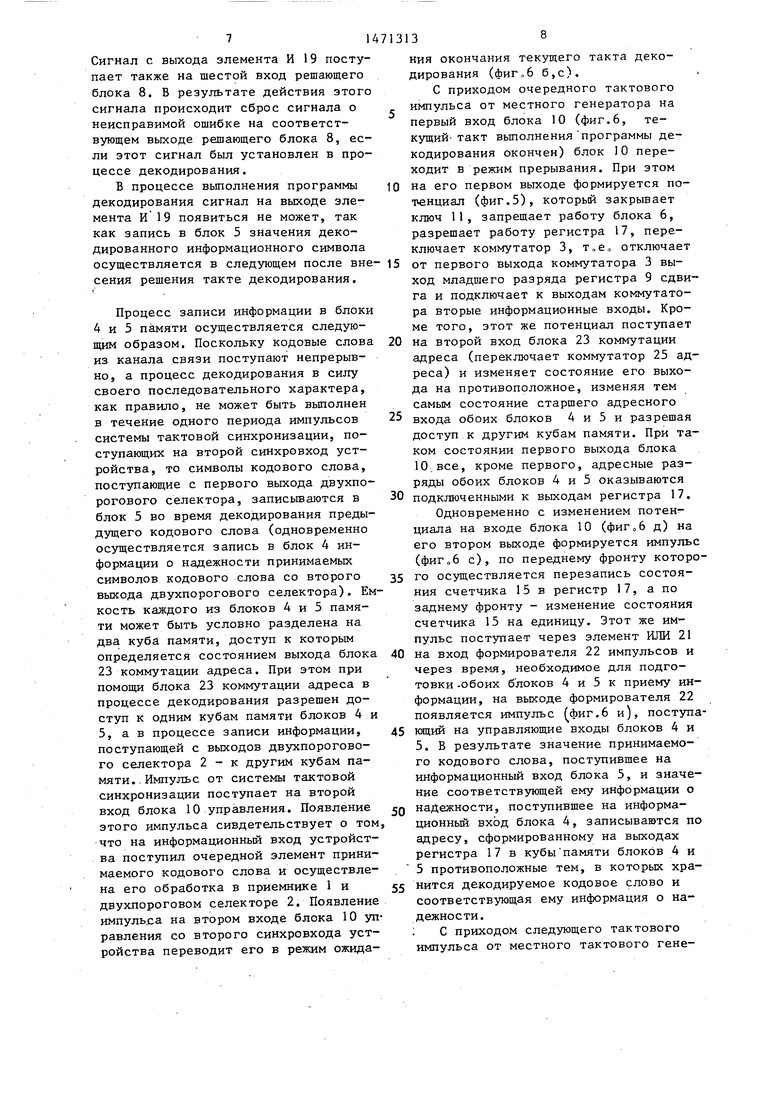

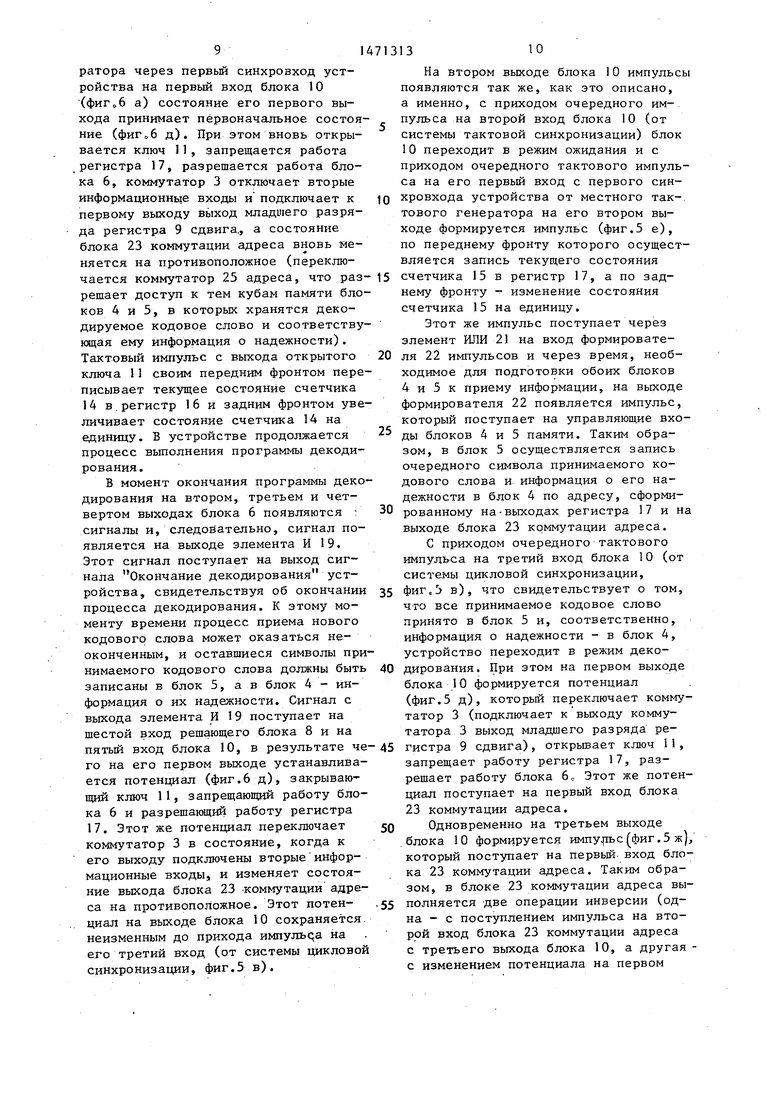

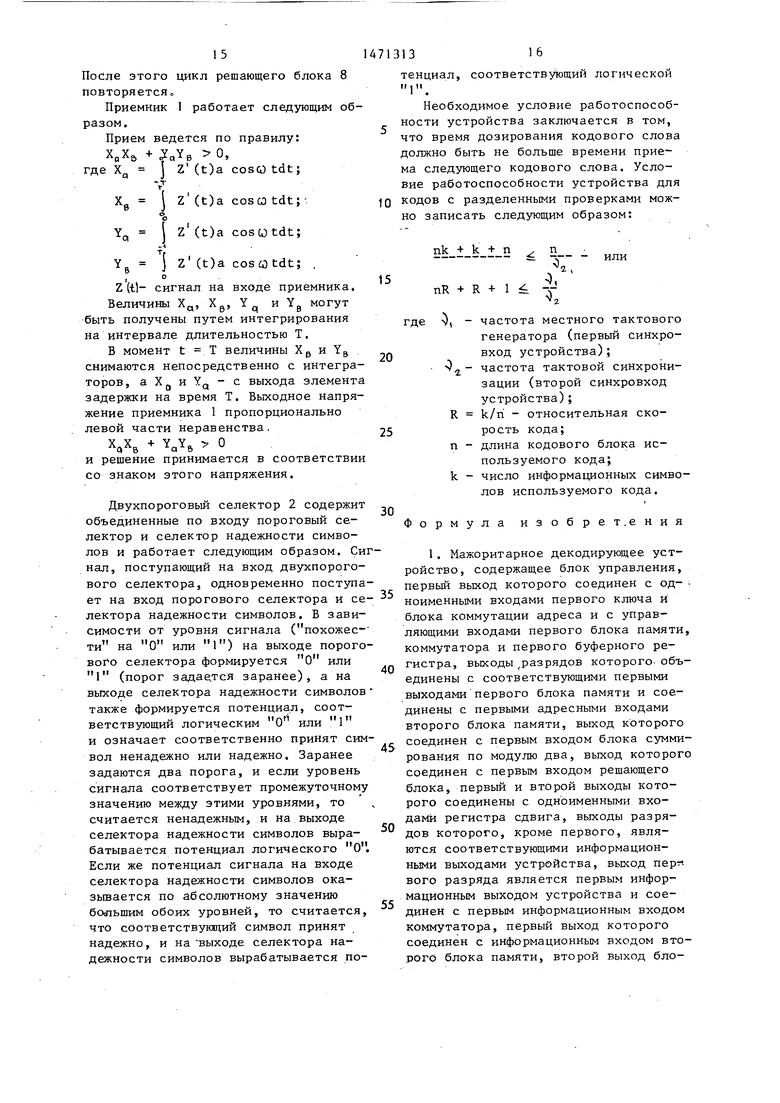

На представлена функциональная схема устройства; на фиг.2 - схема решающего блока; на фиг.З - схема блока блокировки; на фиг„4 - схема коммутатора; на фиг.5 - временные диаграммы процесса декодирования; на фиг.6 - временные диаграм- J5 мы процесса приема первого кодового слова.

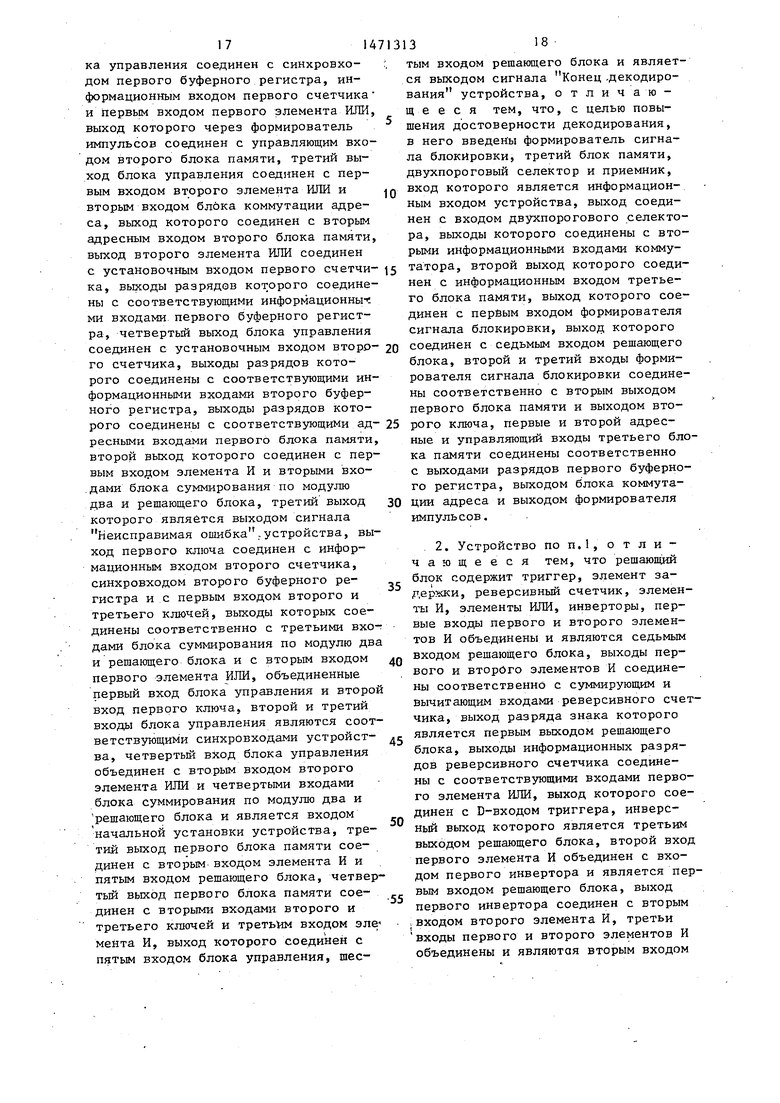

Мажоритарное декодирующее устройство (фиГоО содержит приемник 1, двухпороговый селектор 2, коммутатор 3, блоки 4-6 памяти, блок 7 суммирования по модулю два, решающий блок 8, регистр 9 сдвига, блок 10 управления, ключи 11-13, счетчики 14 и 15, регистры 16 и 17, формирователь 18 сигнала блокировки, элемент И 19, элементы ИЛИ 20 и 21, формирователь 22 импульсов, блок 23 коммутации адреса, содержащий триггер 24 и коммутатор 25 адреса.

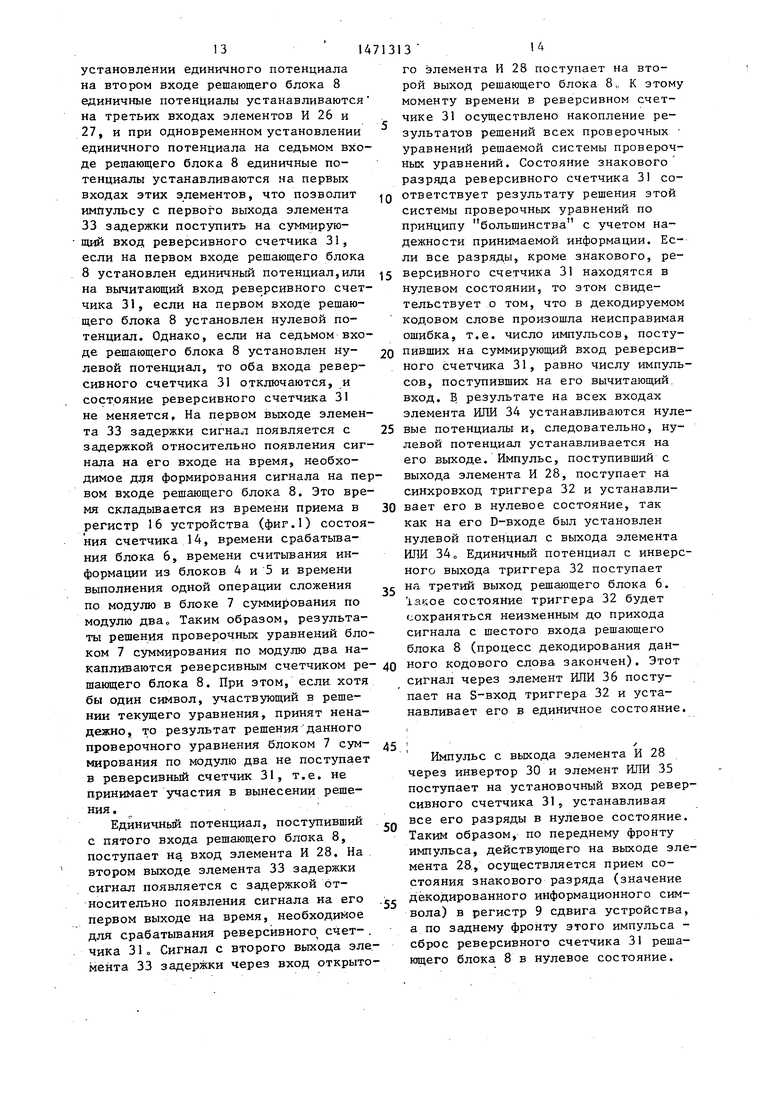

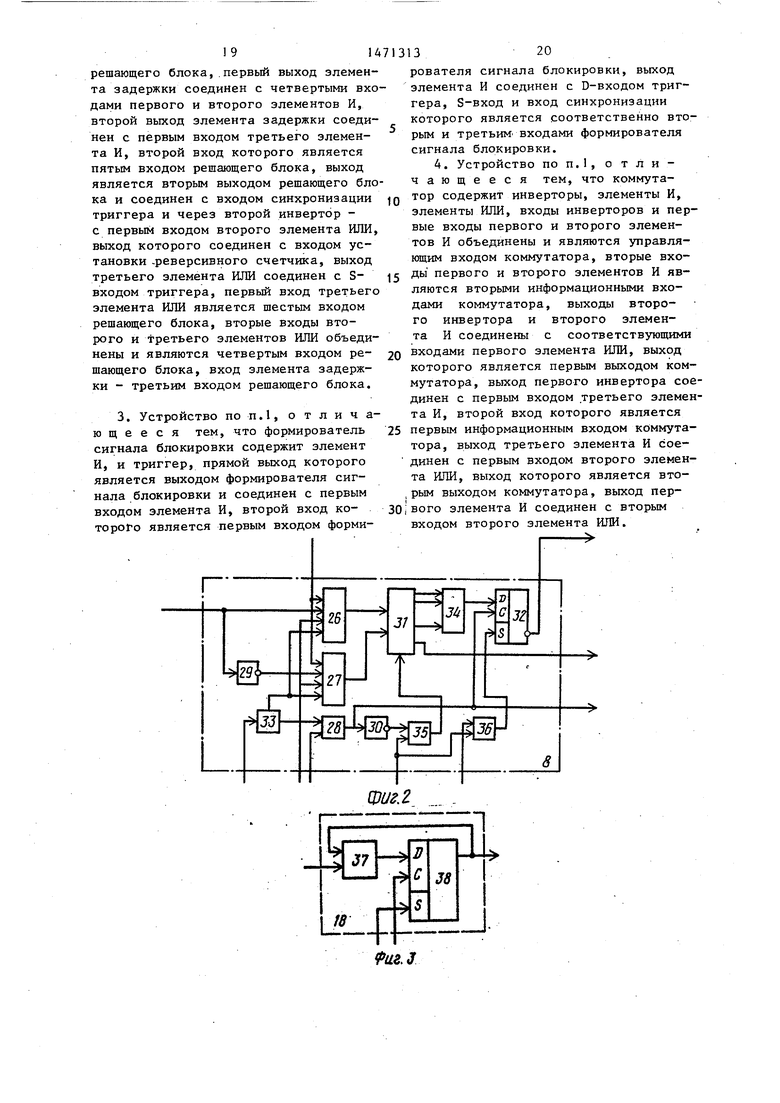

Решающий блок (Фиг«2 содержит элементы И 26-28, инверторы 29 и 30, реверсивный счетчик 31, триггер 32, элемент 33 задержки и элементы ИЛИ

34-36.

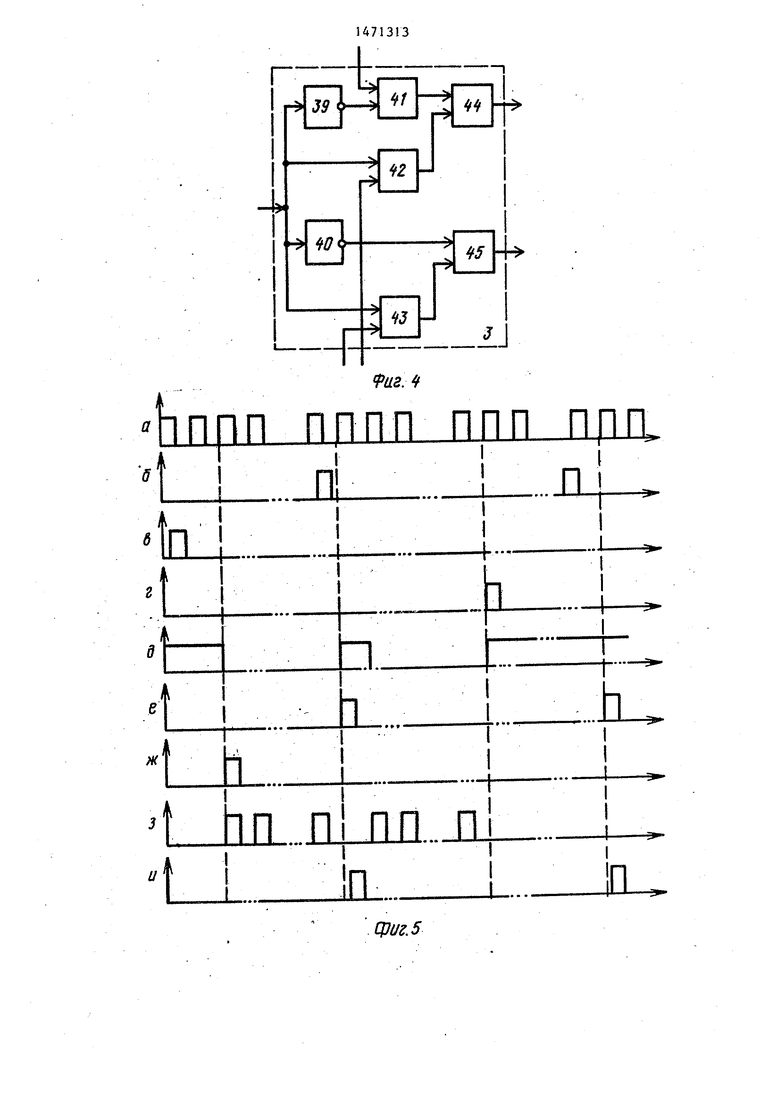

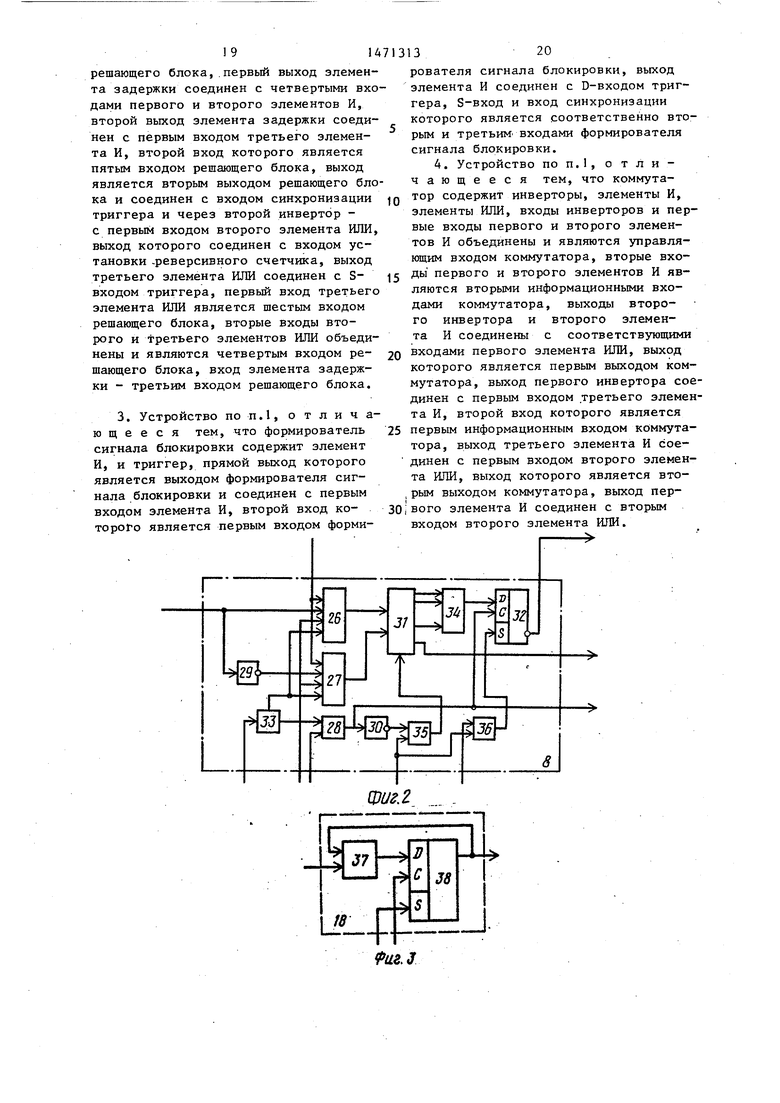

Блок блокировки (фиг.З) содержит элемент И 37 и триггер 38.

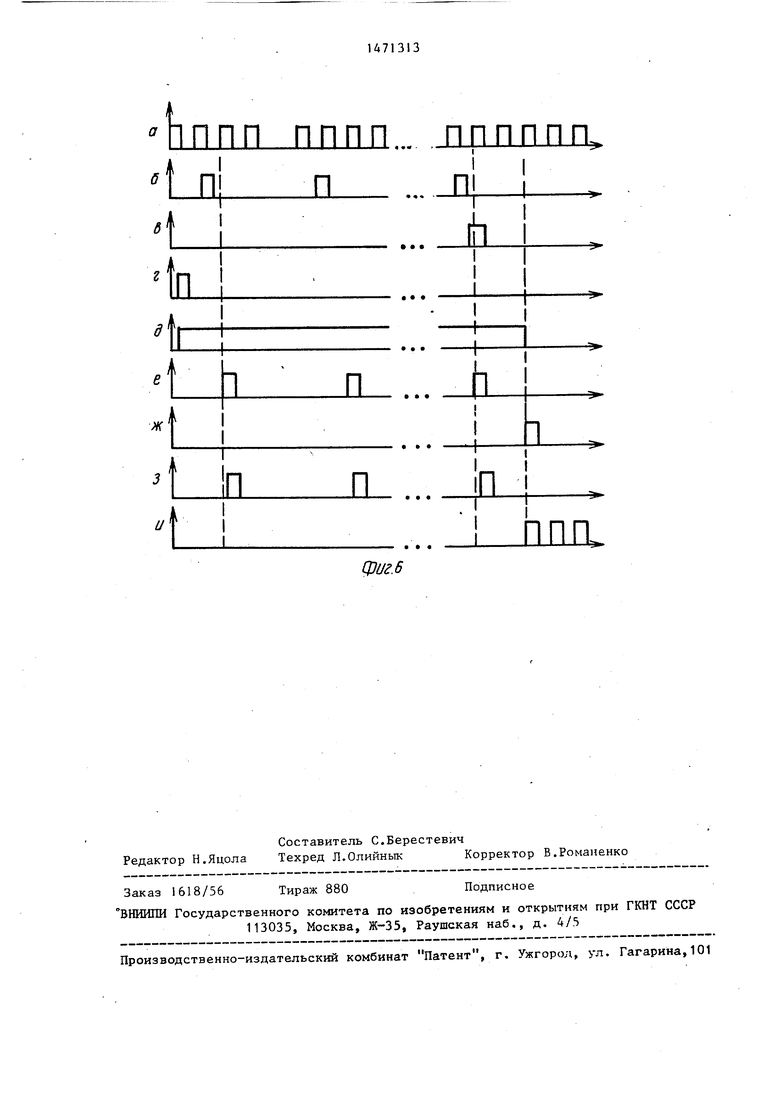

Коммутатор (фиг.4) содержит инверторы 39 и 40, элементы И 41-43 и элементы ИЛИ 44 и 45.

Мажоритарное декодирующее устройство работает следующим образом.

Текущее состояние выхода блока 23 коммутации адреса определяет номера кубов памяти блоков 4 и 5 памяти (первые или вторые), к которьм разре- текущий момент времени.

цикловбй синхронизации (фиг.бв), поступает на третий вход блока 10 управления,, После этого на первом выходе блока 10 устанавливается потенциал запрещающий работу регистра 17 и разрешающий работу блока 6 памяти.Этот же потенциал открьшает ключ 11 и устанавливает коммутатор 3 в состояние, когда к его первому выходу (а следова тельно к информационному входу блока 5) подключен младший разряд регистра 9 сдвига, а выходы двухпорогового селектора 2 отключены. Этот же потенциал с первого выхода блока 10 поступает на первьй вход блока 23 коммутации адреса о Одновременно с изменением потенциала на входе блока 10 на его третьем выходе (фиг.бж) формируется импульс, который поступает через вход элемента ИЛИ 20 на установочньй вход счетчика 15 и устанавливает все его разряды в начальное, например, нулевое состояние о Этот же импульс с третьего выхода блока 10 поступает на второй вход блока 23 коммутации адреса. В результате на выход е блока 23 коммутации адреса устанавливается потенциалj разрешающий доступ к тем кубам памяти.блоков 4 и 5 памяти, в которые записаны информация о надежности и само кодовое слово соответственно . Формирование символов кодового, слова- и информация о их надежности осуществляется приемником 1 и двухпороговым селектором 2. При этом на первом выходе двухпорогового селектора 2 формируются регенерированные символы принимаемого кодового слова (О или 1), они записьша- ются через коммутатор 3 в блок 5 па- мяти, а информация о надежности принятого символа (1 - если символ принят надежно и О - если символ де принимаемого кодового слова принят ненадежно) формируется на втором выходе двухпорогового селектора 2 и записывается через коммутатор 3 в блок 4 в ячейку с тем же адресом, по

20

25

30

40

шен доступ в

При этом в процессе декодирования поступ разрешен к одному из кубов па ти локов 4 и 5, а в процессе прие-JQ которому был записан данньш символ в элемента кодового слова - к .дру- ° блок 5. Блок 7 суммирования по моду- гим. Рассмотрим цикл работы устрой-. лю два, решающий блок 8 и все разря- ствд с момента окончания приема очередного кодового слова в один из кубов памяти блока 5, а соответствующей ния предыдущего кодового слова информда о надежности - в соответ- Тактовый импульс поступивший с ст™ куб памяти блока 4., . первого входа устройства через отИмпульс, поступивший с третьего синхровхода устройства от системы

ды счетчика 14 установлены в нулевое состояние при окончании декодироваIIC -D VJ. V j - f

крытьй ключ 11 (фиг.6и), осуществляет своим передним фронтом запись со0

5

цикловбй синхронизации (фиг.бв), поступает на третий вход блока 10 управления,, После этого на первом выходе блока 10 устанавливается потенциал, запрещающий работу регистра 17 и разрешающий работу блока 6 памяти.Этот же потенциал открьшает ключ 11 и устанавливает коммутатор 3 в состояние, когда к его первому выходу (а следовательно к информационному входу блока 5) подключен младший разряд регистра 9 сдвига, а выходы двухпорогового селектора 2 отключены. Этот же потенциал с первого выхода блока 10 поступает на первьй вход блока 23 коммутации адреса о Одновременно с изменением потенциала на входе блока 10 на его третьем выходе (фиг.бж) формируется импульс, который поступает через вход элемента ИЛИ 20 на установочньй вход счетчика 15 и устанавливает все его разряды в начальное, например, нулевое состояние о Этот же импульс с третьего выхода блока 10 поступает на второй вход блока 23 коммутации адреса. В результате на выход е блока 23 коммутации адреса устанавливается потенциалj разрешающий доступ к тем кубам памяти.блоков 4 и 5 памяти, в которые записаны информация о надежности и само кодовое слово соответственно . Формирование символов кодового, слова- и информация о их надежности осуществляется приемником 1 и двухпороговым селектором 2. При этом на первом выходе двухпорогового селектора 2 формируются регенерированные символы принимаемого кодового слова (О или 1), они записьша- ются через коммутатор 3 в блок 5 па- мяти, а информация о надежности принятого символа (1 - если символ принят надежно и О - если символ де принимаемого кодового слова принят ненадежно) формируется на втором выходе двухпорогового селектора 2 и записывается через коммутатор 3 в блок 4 в ячейку с тем же адресом, по

0

25

30

40

JQ которому был записан данньш символ в ° блок 5. Блок 7 суммирования по моду- лю два, решающий блок 8 и все разря- ния предыдущего кодового слова Тактовый импульс поступивший с первого входа устройства через откоторому был записан данньш символ в блок 5. Блок 7 суммирования по моду- лю два, решающий блок 8 и все разря- ния предыдущего кодового слова Тактовый импульс поступивший с первого входа устройства через отды счетчика 14 установлены в нулевое состояние при окончании декодировакоторому был записан данньш символ в блок 5. Блок 7 суммирования по моду- лю два, решающий блок 8 и все разря- ния предыдущего кодового слова Тактовый импульс поступивший с первого входа устройства через отIIC -D VJ. V j - f

крытьй ключ 11 (фиг.6и), осуществляет своим передним фронтом запись со31

стояния счетчика 14 (в данном случае нулевое) в регистр 16, а своим задним фронтом увеличивает состояние счетчика 14 на единицу. Состояние регистра 16 поступает на адресные входы блока 6 памяти и на его первых выходах появляется код адреса элемента кодового слова и соответствующей ему информации о надежности, храняющихся в блоках 5 и 4 памяти соответственно. Данный элемент кодового слова, считанный из ячейки блока 5 с у-казанным адресом, является первым элементом первого провероч- ного уравнения для первого информационного символа. С этого момента начинается вьшолнение программы декодирования, хранящейся в блоке 6.

Значение символа, считанное из блока 5, поступает на вход блока 7 суммирования по модулю два, в котором осуществляется последовательное сложение по модулю два элементов, входящих в решаемое в данный момент проверочное уравнение. Одновременно со считыванием из блока 5 символов декодируемого кодового слова (входящих в решаемое проверочное уравнение) из ячеек с аналогичными адреса- ми блока 4 происходит считьшание информации о надежности заказанных символов кодового слова, которая поступает на вход формирователя 18. Если какой-либо символ кодового слова, входящий в решаемое проверочное уравнение, принят надежно (на вход формирователя 18 из соответствующей ячейки блока 4 считывается символ О), то на выходе формирователя 18 форми- руется сигнал, который поступает на седьмой вход решающего блока 8 и запрещает поступление информации о результате решения проверочного уравнения из блока 7 суммирования по мо- дулю два в решающий блок 8,

Таким образом, если хотя бы один символ кодового слова, входящий в данное проверочное уравнение, принят ненадежно, то все проверочное уравнение стирается, т.е. не принимает участия в вынесении решения о значении декодируемого информационного си вола по принципу большинства. Ключ 12 при этом открыт, а ключ 13 - зак- рыт. Если данный символ не является последним в проверочном уравнении, то на втором выходе блока 6 сигнал не появляется, и состояние блока 7

суммирования по модулю два не передается в решающий блок 8. В противно случае на втором выходе блока 6 одновременно с адресом последнего символа данного проверочного уравнения появляется сигнал, который поступает на вторые входы решающего блока 8, блока 7 суммирования по модулю два блока 6. В результате состояние блок 7.суммирования по модулю два, если все символы, входящие в данное проверочное уравнение приняты надежно, поступает в решающий блок 8, после чего осуществляется установка блока

7суммирования по модулю два в нулевое состояние, а формирователя 18 - в начальное состояние.

Далее устройство переходит к решению очередного проверочного уравнения. Однако, если в процессе решения проверочного уравнения путем последовательного суммиро.вания символов декодируемого кодового слова, считываемых из блока 5 в блоке 7 суммирования, по модулю два, хотя бы один из символов, входящих в него, является не надежным (о чем свидетельствует информация, поступающая на вход формирователя 18 из блока 4),то состояние блока 7 суммирования по модулю два не поступает в решающий бло

8и, таким образом, результат решени данного уравнения стирается. Если символ, считьшаемый из блока 5, является последним символом в последнем уравнении системы для данного информационного символа, то вместе

с кодом адреса этого символа на первых выходах и сигналом на втором выходе блока 6 на его третьем выходе появляется сигнал, который поступает на пятый вход решающего блока 8. Состояние блока 7 суммирования по модулю два поступает в решающий блок 8 В этот момент в решанлций блок 8 ока- зьшаются принятыми результаты ре-; шения (блоком 7 суммирования по модулю два) всех проверочных уравнений (за исключением тех, которые имели в своем составе ненадежные символы) для данного информационного символа. Решающий блок 8 выносит решение по принципу большинства о значении данного информационного символа. Это значение с первого выхода решающего блока 8 поступает на соответствующий вход регистра 9 сдвига, после чего на втором выходе решающего блока 8 формируется импульс, который поступает на синхровход регистра 9 сдвига, и результат декодирования данного информационного символа переписывается в первьй разряд регистра 9 сдвига (в регистре 9 сдвига происходит сдвиг на один разряд). Если в кодовом слове произошла неисправимая ошибка (число не стертых проверочных уравнений в системе, решение которых равно нулю, равно числу не стертых уравнений, 1зешение которых равно единице, либо все уравнения для данного информационного симв.ола оказались стертьши), то на третьем выходе решающего блока 8 появляется сигнал, который поступает на выход сигнала Неисправимая ошибка устройства и свидетельствует о неисправимой, но обнаружимой ошибке, произошедшей в кодовом слове. Если значение декодированного информационного символа используется в проверочных уравнениях для других информационных символов (это имеет место, например, при декодировании кодов Рида-Мюллера), то этот символ записывается в блок 5 памяти в тот же куб памяти, в который записано декодируемое кодовое слово. Для зтого в следующий тактовый момент времени (следующее за считыванием последнего символа из блока 5) на первых выходах блока 6 формируется код адреса ячейки блока 5, в которую будет записано значение, декодированного символа. На втором и третьем выходах блока 6 сигналы не появляются, а на

10

15

ку с тем же адресом блока 4 записывается 1 через коммутатор, так как декодированный информационный символ считается надежным). После этого устройство переходит к декодированию очередного информационного символа. Если значение декодированного информационного символа не участвует в проверочных уравнениях для других информационных символов (что .имеет место для кодов с раздельными проверками), то его значение не записывается в блок 5, и устройство сразу же переходит к декодированию следующего информационного символа.

Таким образом, в устройстве осуществляется- процесс декодирования путем последовательного решения проверочных уравнений и систем проверочных уравнений с учетом надежности символов декодируемого кодового слова. Адреса символов декодируемого ко- 25 дового слова (хранящихся в блоке 5) записаны в виде программы декодирования в блоке 6 в последовательности, определяемой видом проверочных уравнений. Текущее состояние программы декодирования определяется состоянием регистра 16 (которое, в свою очередь, определяется состоянием счетчика 14). Тактовые импульсы, поступающие с выхода ключа 11, осуществляют перезапись текущего состояния счетчика 14 в регистр 16 и увеличивают состояние счетчика 14 на единицу. На первых выходах блока 6 формируются коды адресов ячеек блоков 4 и 5 памяти, а

20

30

35

его четвертом выходе формируется сиг- 40 - оставшихся выходах формируется ин- нал, закрьшающий ключ 12 и открыва- . формация, управляющая работой блока ющий ключ 13.

Импульс, с выхода ключа

11 через

открытый ключ 13 и элемент ИЛИ 21 поступает на вход формирователя 22 импульсов, и на его выходе с задержкой на время, необходимое.для подготовки блоков 4 и 5 к приему инофрма- ции, формируется импульс, поступающий на управляющие входы блоков 4 и 5. В .результате действия этого импульса состояние младшего разряда регистра 9 сдвига, поступившее через первый информационный вход комМут а- тора 3 на информационный вход блока 5, записьшается в блоке 5 в ячейк у с адресом, сформированным на первых . вькодах блока 6 (одновременно в ячейг

7 суммирования по модулю два, формирователя 18, решающего блока 8 и ключа 13. В последнем такте программы

45 (когда на первых выходах блока 6 сфор мирован код адреса последнего символа) на втором, третьем и четвертом выходах блока 6 формируются сигналы, которые открьшают элемент И 19, и на

gQ его выходе формируется сигнал, который поступает на пятый вход блока 10, что свидетельствует об окончании процесса декодирования данного кодового слова. В результате на четвертом высс ходе блока. 10 формируется импульс, который поступает на установочньй вход счетчика 14, устанавливая все его разряды в начальное состояние.

5

ку с тем же адресом блока 4 записывается 1 через коммутатор, так как декодированный информационный символ считается надежным). После этого устройство переходит к декодированию очередного информационного символа. Если значение декодированного информационного символа не участвует в проверочных уравнениях для других информационных символов (что .имеет место для кодов с раздельными проверками), то его значение не записывается в блок 5, и устройство сразу же переходит к декодированию следующего информационного символа.

Таким образом, в устройстве осуществляется- процесс декодирования путем последовательного решения проверочных уравнений и систем проверочных уравнений с учетом надежности символов декодируемого кодового слова. Адреса символов декодируемого ко- 5 дового слова (хранящихся в блоке 5) записаны в виде программы декодирования в блоке 6 в последовательности, определяемой видом проверочных уравнений. Текущее состояние программы декодирования определяется состоянием регистра 16 (которое, в свою очередь, определяется состоянием счетчика 14). Тактовые импульсы, поступающие с выхода ключа 11, осуществляют перезапись текущего состояния счетчика 14 в регистр 16 и увеличивают состояние счетчика 14 на единицу. На первых выходах блока 6 формируются коды адресов ячеек блоков 4 и 5 памяти, а

0

0

5

40 - оставшихся выходах формируется ин- . формация, управляющая работой блока

7 суммирования по модулю два, формирователя 18, решающего блока 8 и ключа 13. В последнем такте программы

45 (когда на первых выходах блока 6 сформирован код адреса последнего символа) на втором, третьем и четвертом выходах блока 6 формируются сигналы, которые открьшают элемент И 19, и на

gQ его выходе формируется сигнал, который поступает на пятый вход блока 10, что свидетельствует об окончании процесса декодирования данного кодового слова. В результате на четвертом высс ходе блока. 10 формируется импульс, который поступает на установочньй вход счетчика 14, устанавливая все его разряды в начальное состояние.

111471313

входе блока 10) и, следовательно, состояние его выхода не изменяется, т.е. разрешается доступ к тем кубам памяти блоков 4 и 5, в которые записаны подлежащее декодированию кодовое слово и информация о надежности. Запись следующего кодового слова осуществляется в противоположный куб памяти аналогично описанному.

С третьего выхода блока 10 импульс поступает через элемент ИЛИ 20 на ус- тановочньй вход счетчика 15 и устанавливает все его разряды в нулевое

10

I 2

том выходе появляется сигнал, который поступает на установочньш вход счетчика 14, осуществляя первоначальную установку всех его разрядов в нулевое состояние. С приходом первого импульса на третий синхровход устройства (фиг,6 в) начинается процесс декодирования, как это описано, Начальная установка блока 23 коммутации адреса не существенна, так как безразлично, в какой куб памяти (первый или второй) блоков 4 и 5 будет произведен прием первого кодового

состояние (счетчик 14 устанавливает- 15 слова, важно лишь, чтобы запись слеся в нулевое состояние импульсом с четвертого выхода блока 10 после окончания программы декодирования). Далее процесс декодирования повторяется. Решающий блок 8 и блок 7 суммирования по модулю два уже подготовлены к решению новой системы проверочных уравнений после обработки последнего символа последнего уравнения

дующего кодового слова производила в куб памяти, противоположный тому в котором записано декодирующее ко довое слово (и информация о его на 20 дежности).

Введение в устройство регистров 16 и 17 не является обязательным. Так выходы счетчика 14 могут быть посредственно подключены к адресны

системы для последнего информационно- 25 входам блока 6. Однако, поскольку

время переключения счетчика 14 мно больше времени приема в регистр 16 то введение регистра 16 позволяет повысить частоту следования тактов импульсов на первом синхровходе ус ройства, что может оказаться сущес венным при декодировании длинных к дов .

го символа Декодированного кодового слова. Однако в начале декодирования первого кодового слова (после включения устройства) состояние решающего блока 8 и блока 7 суммирования по модулю два может оказаться произвольным и они должны быть подготовлены к рещению системы проверочных уравнений.

С этой целью на вход начальной установки устройства подается сигнал Установка перед приемом первого кодового слова (фиг.6 г). Этот сигнал через элемент ИЛИ 20 поступает на установочный вход счетчика 15 и устанавливает все его разряды в нулевое состояние. Этот же сигнал Установка поступает на четвертые входы блока 7 суммирования по модулю два и решающего блока 8, подготавливая их к решению первого .проверочного уравнения первой системы первого кодового слова. Одновременно сигнал Установка поступает на четвертый вход блока 10 и вызывает в нем те же процессы, что и сигнал на его пятом входе (фиг.6), т.е. устройство переходит в режим приема кодового слова из канала связи в один из кубов памяти блока 5 (информация о надежности - в аналогичный куб памяти блока 4). Одновременно с приходом сигнала Установка на четвертый вход блока 10 на его четвер

0

I 2

том выходе появляется сигнал, который поступает на установочньш вход счетчика 14, осуществляя первоначальную установку всех его разрядов в нулевое состояние. С приходом первого импульса на третий синхровход устройства (фиг,6 в) начинается процесс декодирования, как это описано, Начальная установка блока 23 коммутации адреса не существенна, так как безразлично, в какой куб памяти (первый или второй) блоков 4 и 5 будет произведен прием первого кодового

дующего кодового слова производилась в куб памяти, противоположный тому, в котором записано декодирующее кодовое слово (и информация о его на- дежности).

Введение в устройство регистров 16 и 17 не является обязательным. Так выходы счетчика 14 могут быть не- посредственно подключены к адресным

5 входам блока 6. Однако, поскольку

0

5

0

время переключения счетчика 14 много больше времени приема в регистр 16, то введение регистра 16 позволяет повысить частоту следования тактовых импульсов на первом синхровходе устройства, что может оказаться существенным при декодировании длинных кодов .

Решающий блок 8 работает следую- щам образом. Сигнал, поступивший на четвертый вход решающего блока 8 через элемент ИЛИ 35, поступает на установочный вход реверсивного счетчика 31, устанавливая все его разряды в нулевое состояние Этот же сигнал с четвертого входа через элемент ИЛИ 36 поступает на S-вход триггера 32 и устанавливает его в единичное состояние (на его инверсном выходе с устанавливается нулевой потенциал). Сигнал с первого входа решающего бло- ка 8 поступает на вход элемента И 26 непосредственно, а на вход элемента И 27 - через инвертор 29. Следовательно, если сигнал на первбм входе решающего блока 8 имеет единичное значение, то на втором входе элемента И 26 будет единичньш потенциал, а на втором входе элемента И 27 - нулевой потенциал. Если же сигнал на первом входе решающего блока 8 принимает нулевое значение, то потенциалы на вторых входах элементов 26 и 27 изменяются на противоположные. При

0

5

установлении единичного потенциала на втором входе решающего блока 8 единичные потенциалы устанавливаются на третьих входах элементов И 26 и 27, и при одновременном установлении единичного потенциала на седьмом входе решающего блока 8 единичные потенциалы устанавливаются на первых входах этих элементов, что позволит д импульсу с первого выхода элемента 33 задержки поступить на суммирую- щий вход реверсивного счетчика 31, если на первом входе решающего блока 8 установлен единичньй потенциал,или 5 на вычитаюш;ий вход реверсивного счетчика 31, если на первом входе решающего блока В установлен нулевой потенциал. Однако, если на седьмом входе решающего блока 8 установлен ну- 20 левой потенциал, то оба входа реверсивного счетчика 31 отключаются, и состояние реверсивного счетчика 31 не меняется. На первом вьшоде элемента 33 задержки сигна т появляется с 25 задержкой относительно появления сигнала на его входе на время, необходимое ДJJя формирования сигнала на первом входе решающего блока 8. Это время складывается из времени приема в 30 регистр 16 устройства (фиг.1) состояния счетчика 14, времени срабатьша- ния блока 6, времени считывания информации из блоков 4 и 5 и времени выполнения одной операции сложения по модулю в блоке 7 суммирования по модулю два Таким образом, результаты решения проверочных уравнений блоком 7 суммирования по модулю два накапливаются реверсивным счетчиком ре- 40 тающего блока 8. При этом, если хотя бы один символ, участвующий в решении текущего уравнения, принят ненадежно, то результат решения данного проверочного уравнения блоком 7 сум- 45 мирования по модулю два не поступает в реверсивньй счетчик 31, т.е. не принимает участия в вынесении решения .

Единичньй потенциал, поступивший с пятого входа решающего блока В, поступает на вход элемента И 28. На втором выходе элемента 33 задержки сигнал появляется с задержкой относительно появления сигнала на его . первом выходе на время, необходимое для срабатывания реверсивного счет- . чика 31. Сигнал с второго выхода элемента 33 задержки через вход открытого элемента И 28 поступает на второй выход решающего блока В,. К этому моменту времени в реверсивном счетчике 31 осуществлено накопление результатов решений всех проверочных уравнений решаемой системы проверочных уравнений. Состояние знакового разряда реверсивного счетчика 31 соответствует результату решения этой системы проверочных уравнений по принципу большинства с учетом надежности принимаемой информации. Если все разряды, кроме знакового, реверсивного счетчика 31 находятся в нулевом состоянии, то этом свидетельствует о том, что в декодируемом кодовом слове произошла неисправимая ошибка, т.е. число импульсов, поступивших на суммирующий вход реверсивного счетчика 31, равно числу импульсов, поступивших на его вычитающий. вход. В результате на всех входах элемента ИЛИ 34 устанавливаются нулевые потенциалы и, следовательно, нулевой потенциал устанавливается на его выходе. Импульс, поступивший с выхода элемента И 2В, поступает на синхровход триггера 32 и устанавливает его в нулевое состояние, так как на его D-входе был установлен нулевой потенциал с выхода элемента ИЛИ 34,, Единичный потенциал с инверсного выхода триггера 32 поступает на третий выход решающего блока 6. lar.oe состояние триггера 32 будет сохраняться неизменным до прихода сигнала с шестого входа решающего блока 8 (процесс декодирования данного кодового слова закончен). Этот сигнал через элемент ИЛИ 36 поступает на S-вход триггера 32 и устанавливает его в единичное состояние.

t V

Импульс с выхода элемента И 2В через инвертор 30 и элемент ИШИ 35 поступает на установочный вход реверсивного счетчика 31, устанавливая все его разряды в нулевое состояние Таким образом, по переднему фронту импульса, действующего на выходе элемента 2В., осуществляется прием состояния знакового разряда (значение декодированного информационного символа) в регистр 9 сдвига устройства а по заднему фронту этого импульса - сброс реверсивного счетчика 31 решающего блока 8 в нулевое состояние.

714

Сигнал с выхода элемента И 19 поступает также на шестой вход решающего блока 8. В результате действия этого сигнала происходит сброс сигнала о неисправимой ошибке на соответствующем выходе решающего блока 8, если этот сигнал был установлен в процессе декодирования.

В процессе выполнения программы декодирования сигнал на выходе элемента И 19 появиться не может, так как запись в блок 5 значения декодированного информационного символа осуществляется в следующем после вне- сения решения такте декодирования.

Процесс записи информации в блоки 4 и 5 памяти осуществляется следующим образом. Поскольку кодовые слова из канала связи поступают непрерывно, а процесс декодирования в силу своего последовательного характера, как правило, не может быть выполнен в течение одного периода импульсов системы тактовой синхронизации, поступающих на второй синхровход устройства, то символы кодового слова, постзшающие с первого выхода двухпо- рогового селектора, записьшаются в блок 5 во время декодирования предыдущего кодового слова (одновременно осуществляется запись в блок 4 информации о надежности принимаемых символов кодового слова со второго выхода двухпорогового селектора). Емкость каждого из блоков 4 и 5 памяти может быть условно разделена на два куба памяти, доступ к которым определяется состоянием выхода блока 23 коммутации адреса. При этом при помощи блока 23 коммутации адреса в процессе декодирования разрешен доступ к одним кубам памяти блоков 4 и 5, а в процессе записи информации, поступающей с выходов двухпорогового селектора 2 - к другим кубам памяти. . Импульс от системы тактовой синхронизации поступает на второй вход блока 10 управления. Появление этого импульса сивдетельствует о том что на информационный вход устройства поступил очередной элемент принимаемого кодового слова и осуществлена его обработка в приемнике 1 и двухпороговом селекторе 2. Появление импуль га на втором входе блока 10 управления со второго синхровхода устройства переводит его в режим ожидания окончания текущего такта декодирования (фиг„6 б,с).

С приходом очередного тактового импульса от местного генератора на первый вход блока 10 (фиг.6, текущий- такт вьтолнения программы декодирования окончен) блок 10 переходит в режим прерывания. При этом на его первом выходе формируется потенциал (фиг.5), который закрывает ключ 11, запрещает работу блока 6, разрешает работу регистра 17, переключает коммутатор 3, т,ео отключает от первого выхода коммутатора 3 выход младшего разряда регистра 9 сдвига и подключает к выходам коммутатора вторые информационные входы. Кроме того, этот же потенциал поступает на второй вход блока 23 коммутации адреса (переключает коммутатор 25 адреса) и изменяет состояние его выхода на противоположное, изменяя тем самым состояние старшего адресного входа обоих блоков 4 и 5 и разрешая доступ к другим кубам памяти. При таком состоянии первого выхода блока 10,все, кроме первого, адресные разряды обоих блоков 4 и 5 оказываются подключенными к выходам регистра 17. Одновременно с изменением потенциала на входе блока 10 (фиг„6 д) на его втором выходе формируется импульс (фигоб с), по переднему фронту которого осуществляется перезапись состояния счетчика 15 в регистр 17, а по заднему фронту - изменение состояния счетчика 15 на единицу. Этот же импульс поступает через элемент ИЛИ 21 на вход формирователя 22 импульсов и через время, необходимое для подготовки -обоих блоков 4 и 5 к приему информации, на выходе формирователя 22 появляется импульс (фиг.6 и), поступ кщий на управляющие входы блоков 4 и 5. В результате значение принимаемого кодового слова, поступившее на информационный вход блока 5, и значение соответствующей ему информации о надежности, поступившее на информа- ционньш вход блока 4, записываются п адресу, сформированному на выходах регистра 17 в кубы памяти блоков 4 и 5 противоположные тем, в которых хранится декодируемое кодовое слово и соответствующая ему информация о надежности.

; С приходом следующего тактового импульса от местного тактового генератора через первый синхровход устройства на первый вход блока 10 (фиг о6 а) состояние его первого выхода принимает первоначальное состояние (фиго6 д). При этом вновь открывается ключ 11, запрещается работа ,регистра 17, разрешается работа блока 6, коммутатор 3 отключает вторые информационные входы и подключает к первому выходу выход младшего разряда регистра 9 сдвига,, а состояние блока 23 коммутации адреса вновь меняется на противоположное (переклюНа втором выходе блока 10 импульсы появляются так же, как это описано, а именно, с приходом очередного импульса на второй вход блока 10 (от системы тактовой синхронизации) блок 10 переходит в режим ожидания и с Приходом очередного тактового импульса на его первый вход с первого син- Q хровхода устройства от местного тактового генератора на его втором выходе формируется импульс (фиг,5 е), по переднему фронту которого осуществляется запись текущего состояния

чается коммутатор 25 адреса, что раз-15 счетчика 15 в регистр 17, а по зад- решает доступ к тем кубам памяти блоков 4 и 5, в которых хранятся декодируемое кодовое слово и соответству- кяцая ему информация о надежности) . Тактовый импульс с выхода открытого 20 ключа 11 своим передним фронтом переписывает текущее состояние счетчика 14 в.регистр 16 и задним фронтом увеличивает состояние счетчика 14 на

единицу. В устройстве продолжается процесс выполнения программы декодирования.

В момент окончания программы декодирования на втором, третьем и четвертом выходах блока 6 появляются ; сигналы и, следовательно, сигнал появляется на выходе элемента И 19. Этот сигнал поступает на выход сигнала Окончание декодирования устройства, свидетельствуя об окончании процесса декодирования. К этому моменту времени процесс приема нового кодового слова может оказаться неоконченным, и оставшиеся символы принимаемого кодового слова должны быть записаны в блок 5, а в блок 4 - информация о их надежности. Сигнал с выхода элемента И 19 поступает на шестой вход решающего блока 8 и на

нему фронту - изменение состояния счетчика 15 на единицу.

Этот же импульс поступает через элемент ИЛИ 21 на вход формирователя 22 импульсов и через время, необходимое для подготовки обоих блоков 4 и 5 к приему информации, на выходе формирователя 22 появляется импульс, который поступает на управляющие входы блоков 4 и 5 памяти. Таким образом, в блок 5 осуществляется запись очередного символа принимаемого кодового слова и информация о его надежности в блок 4 по адресу, сформи30 рованному на-выходах регистра 17 и н выходе блока 23 коммутации адреса. С приходом очередного тактового импульса на третий вход блока 10 (от системы цикловой синхронизации,

35 фиг.З в), что свидетельствует о том, что все принимаемое кодовое слово принято в блок 5 и, соответственно, информация о надежности - в блок 4, устройство переходит в режим деко40 дирования. При этом на первом выходе блока 10 формируется потенциал (фиг.5 д), которьй переключает комму татор 3 (подключает к выходу коммутатора 3 выход младшего разряда репятый вход блока 10, в результате че-45 гистра 9 сдвига), открывает ключ 11,

запрещает работу регистра 17, разрешает работу блока 6о Этот же потен циал поступает на первый вход блока 23 коммутации адреса.

го на его первом выходе устанавливается потенциал (фиг.6 д), закрываю- щий ключ 11, запрещающий работу блока 6 и разрешающий работу регистра 17. Этот же потенциал переключает коммутатор 3 в состояние, когда к его выходу подключены вторые информационные входы, и изменяет состояние выхода блока 23 -коммутации адреса на противоположное. Этот потенциал на выходе блока 10 сохраняется неизменным до прихода импульца на его третий вход (от системы цикловой синхронизации, фиг.5 в).

47131310

На втором выходе блока 10 импульсы появляются так же, как это описано, а именно, с приходом очередного импульса на второй вход блока 10 (от системы тактовой синхронизации) блок 10 переходит в режим ожидания и с Приходом очередного тактового импульса на его первый вход с первого син- Q хровхода устройства от местного тактового генератора на его втором выходе формируется импульс (фиг,5 е), по переднему фронту которого осуществляется запись текущего состояния

5 счетчика 15 в регистр 17, а по зад- 0

нему фронту - изменение состояния счетчика 15 на единицу.

Этот же импульс поступает через элемент ИЛИ 21 на вход формирователя 22 импульсов и через время, необходимое для подготовки обоих блоков 4 и 5 к приему информации, на выходе формирователя 22 появляется импульс, который поступает на управляющие входы блоков 4 и 5 памяти. Таким образом, в блок 5 осуществляется запись очередного символа принимаемого кодового слова и информация о его надежности в блок 4 по адресу, сформи0 рованному на-выходах регистра 17 и на выходе блока 23 коммутации адреса. С приходом очередного тактового импульса на третий вход блока 10 (от системы цикловой синхронизации,

5 фиг.З в), что свидетельствует о том, что все принимаемое кодовое слово принято в блок 5 и, соответственно, информация о надежности - в блок 4, устройство переходит в режим деко0 дирования. При этом на первом выходе блока 10 формируется потенциал (фиг.5 д), которьй переключает коммутатор 3 (подключает к выходу коммутатора 3 выход младшего разряда регистра 9 сдвига), открывает ключ 11,

запрещает работу регистра 17, разрешает работу блока 6о Этот же потенциал поступает на первый вход блока 23 коммутации адреса.

Одновременно на третьем выходе

блока 10 формируется импу{1ьс(фиг.5 ж), который поступает на первый- вход блока 23 коммутации адреса. Таким образом, в блоке 23 коммутации адреса выполняется две операции инверсии (одна - с поступлением импульса на второй вход блока 23 коммутации адреса с третьего выхода блока 10, а другая - с изменением потенциала на первом

15

После этого цикл решающего блока 8 повторяется.

Приемник 1 работает следующим образом.

Прием ведется по правилу:

х„Хь -- J,YB о,

где Хд Z (t)a cosOtdt; Kg j z (t)a cosco tdt}

О

Yg j z (t)a cos(0tdt;

T.

„ z (t)a cosatdt; ,

D - ,0

Z (tl- сигнал на входе приемника.

Величины Xg, Хц, Yq и Y могут быть получены путем интегрирования на интервале длительностью Т.

В момент t Т величины Х и Yg снимаются непосредственно с интеграторов, а Хц и Yg - с выхода элемент задержки на время Т. Выходное напряжение приемника 1 пропорционально левой части неравенства.

Х, Y,Y, О

и решение принимается в соответстви со знаком этого напряжения.

Двухпороговый селектор 2 содержи

объединенные по входу пороговый селектор и селектор надежности символов и работает следующим образом. Сигнал, поступающий на вход двухпорого- вого селектора, одновременно поступает на вход порогового селектора и се- лектора надежности символов. В зависимости от уровня сигнала (похожее- ти на О или 1) на выходе ПОРОГОВОГО селектора формируется О или

1 (порог задае тся заранее), а на выходе селектора надежности символов также формируется потенциал, соответствующий логическим О или 1 и означает соответственно принят символ ненадежно или надежно. Заранее задаются два порога, и если уровень сигнала соответствует промежуточному значению между этими уровнями, то считается ненадежным, и на выходе селектора надежности символов вырабатывается потенциал логического О . Если же потенциал сигнала на входе селектора надежности символов ока- зьшается по абсолютному значению большим обоих уровней, то считается, что соответствунл5ий символ принят надежно, и на выходе селектора надежности символов вырабатывается по

313

16

тенциал, соответствующий логической

1Г I II

1 .

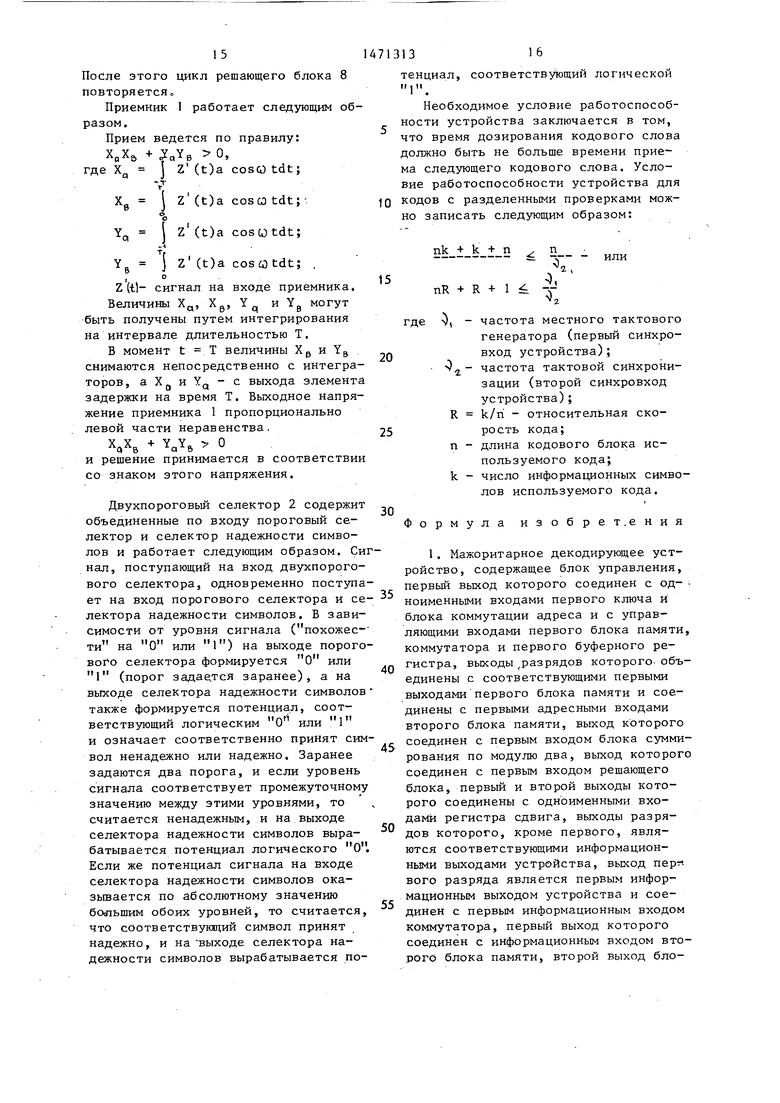

Необходимое условие работоспособности устройства заключается в том, что время дозирования кодового слова должно быть не больше времени приема следующего кодового слова. Условие работоспособности устройства для кодов с разделенными проверками можно записать следующим образом:

nk + n

.,.

uR + R + 1 -ч- 1

или

2,

5

30

3-

40

4S

50

55

где , - частота местного тактового генератора (первый синхро- вход устройства); . . частота тактовой синхронизации (второй синхровход устройства);

R k/ri - относительная скорость кода;

n - длина кодового блока используемого кода;

k - число информационных символов используемого кода.

Формула изобре т.е н и я

1. Мажоритарное декодирующее устройство, содержащее блок управления, первый выход которого соединен с од- ноименными входами первого ключа и блока коммутации адреса и с управляющими входами первого блока памяти, коммутатора и первого буферного регистра, выходы разрядов которого- объединены с соответствующими первыми выходами первого блока памяти и соединены с первыми адресными входами второго блока памяти, выход которого соединен с первым входом блока суммирования по модулю два, выход которого соединен с первым входом решающего блока, первый и второй выходы которого соединены с одноименными входами регистра сдвига, выходы разрядов которого, кроме первого, являются соответствующими информационными выходами устройства, выход вого разряда является первым информационным выходом устройства и соединен с первым информационным входом коммутатора, первый выход которого соединен с информационным входом второго блока памяти, второй выход бло171471313

ка управления соединен с синхровхо- :, дом первого буферного регистра, ин- формадионкым входом первого счетчика и первым входом первого элемента РШИ, выход которого через формирователь импульсов соединен с управляющим вхо- дом второго блока памяти, третий выход блока управления соединен с первым входом второго элемента ИЛИ и Q вторым входом блока коммутации адреса, выход которого соединен с вторым адресным входом второго блока памяти, выход второго элемента ИЛИ соединен с установочным входом первого счетчи- 5 ка, выходы разрядов которого соединены с соответствующими информационны-г: ми входами первого буферного регистра, четвертый выход блока управления

18

тым входом решанлцего блока и является выходом сигнала Конец .декодирования устройства, отличающееся тем, что, с целью повышения достоверности декодирования, в него введены формирователь сигнала блокировки, третий блок памяти, двухпороговый селектор и приемник, вход которого является информационным входом устройства, выход соединен с входом двухпорогового селектора, выходы которого соединены с вто- рьши информационными входами коммутатора, второй выход которого соединен с информационным входом третьего блока памяти, выход которого сое динен с первым входом формирователя сигнала блокировки, выход которого

соединен с установочным входом вторр- 20 соединен с седьмым входом решающего

блока, второй и третий входы формирователя сигнала блокировки соедине ны соответственно с вторым выходом первого блока памяти и выходом втого счетчика, выходы разрядов которого соединены с соответствующими информационными входами второго буферного регистра, выходы разрядов котоблока, второй и третий входы форми рователя сигнала блокировки соедин ны соответственно с вторым выходом первого блока памяти и выходом вто

рого соединены с соответствующими ад- 25 рого ключа, первые и второй адресные и управляющий входы третьего б ка памяти соединены соответственно с выходами разрядов первого буферн го регистра, выходом блока коммута ции адреса и выходом формирователя импульсов,

ресными входами первого блока памяти, второй выход которого соединен с первым Bxofl;oM элемента И и вторыми вхо- дами блока суммирования по модулю два и решающего блока, третий выход которого является выходом сигнала Неисправимая ошибка,устройства, выход первого ключа соединен с информационным входом второго счетчика, синхровходом второго буферного регистра и с первым входом второго и третьего ключей, выходы которых соединены соответственно с третьими вхо-т дами блока суммирования по модулю два и решающего блока и с вторым входом первого элемента ИЛИ, объединенные первый вход блока управления и второй вход первого ключа, второй и третий входы блока управления являются соот- ветствзпощими синхровходами устройства, четвертый вход блока управления объединен с вторым входом второго элемента ИЛИ и четвертыми входами блока суммирования по модулю два и рещающего блока и является входом начальной установки устройства, третий выход первого блока памяти сое- динен с вторым- входом элемента И и пятым входом рещающего блока, четвертый выход первого блока памяти соединен с вторыми входами второго и третьего ключей и третьим входом эле мента И, выход которого соединен с пятым входом блока управления, шес3

18

тым входом решанлцего блока и является выходом сигнала Конец .декодирования устройства, отличающееся тем, что, с целью повышения достоверности декодирования, в него введены формирователь сигнала блокировки, третий блок памяти, двухпороговый селектор и приемник, вход которого является информационным входом устройства, выход соединен с входом двухпорогового селектора, выходы которого соединены с вто- рьши информационными входами коммутатора, второй выход которого соединен с информационным входом третьего блока памяти, выход которого соединен с первым входом формирователя сигнала блокировки, выход которого

соединен с седьмым входом решающего

блока, второй и третий входы формирователя сигнала блокировки соединены соответственно с вторым выходом первого блока памяти и выходом вто5 рого ключа, первые и второй адрес0

5

0

5

0

5

ные и управляющий входы третьего блока памяти соединены соответственно с выходами разрядов первого буферного регистра, выходом блока коммутации адреса и выходом формирователя импульсов,

2. Устройство по п.1, о т л и - чающееся тем, что решаюащй блок содержит триггер, элемент задержки, реверсивный счетчик, элементы И, элементы ИЛИ, инверторы, первые входы первого и второго элементов И объединены и являются седьмым входом рещающего блока, выходы первого и второго элементов И соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выход разряда знака которого является первым выходом рещающего блока, выходы информационных разрядов реверсивного счетчика соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с D-входом триггера, инверсный выход которого является третьим выходом рещающего блока, второй вход первого элемента И объединен с входом первого инвертора и является первым входом решающего блока, выход первого инвертора соединен с вторым .входом второго элемента И, третьи входы первого и второго элементов И объединены и являются вторым входом

решающего блока,.первый выход элемента задержки соединен с четвертыми входами первого и второго элементов И, второй выход элемента задержки соединен с первым входом третьего элемента И, второй вход которого является пятым входом решающего блока, выход является вторым выходом решающего блока и соединен с входом синхронизации триггера и через второй инвертор - с первым входом второго элемента ИЛИ, выход которого соединен с входом установки -реверсивного счетчика, выход третьего элемента ИЛИ соединен с S- входом триггера, первый вход третьего элемента ИЛИ является шестьш входом решающего блока, вторые входы второго и третьего элементов ИЛИ объединены и являются четвертым входом решающего блока, вход элемента задержки - третьим входом решающего блока.

3. Устройство по П.1, о т л и ч а- ю щ е е с я тем, что формирователь сигнала блокировки содержит элемент И, и триггер, прямой выход которого является выходом формирователя сигнала блокировки и соединен с первым входом элемента И, второй вход которого является первым входом форми

рователя сигнала блокировки, выход элемента И соединен с D-входом триггера, S-вход и вход синхронизации которого является соответственно вторым и третьим входами формирователя сигнала блокировки.

4. Устройство по П.1, о т л и - чающееся тем, что коммутатор содержит инверторы, элементы И, элементы ИЛИ, входы инверторов и первые входы первого и второго элементов И объединены и явл5потся управляющим входом коммутатора, вторые вхоC ды первого и второго элементов И являются вторыми информационными входами коммутатора, выходы второго инвертора и второго элемента И соединены с соответствующими

0 входами первого элемента ИЛИ, выход которого является первым выходом коммутатора, выход первого инвертора соединен с первым входом третьего элемента И, второй вход которого является

5 первым информационным входом коммутатора, выход третьего элемента И сое- динен с первым входом второго элемента ИЛИ, выход которого является вто- ,рым выходом коммутатора, выход первого элемента И соединен с вторым входом второго элемента ИЛИ.

0,

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ LDPC-КОДОВ | 2013 |

|

RU2549134C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2007866C1 |

Изобретение относится к технике передачи дискретных сообщений и может быть использовано для передачи цифровой информации по каналам с шумами. Цель изобретения - повышение достоверности декодирования. Устройство содержит приемник 1, двухпороговый селектор 2, коммутатор 3, блоки 4-6 памяти, блок 7 суммирования по модулю два, решающий блок 8, регистр 9 сдвига, блок 10 управления, ключи 11-13, счетчики 14, 15, регистры 16, 17, формирователь 18 сигнала блокировки, элемент И 19, элементы 20, 21 ИЛИ, формирователь 22 импульсов, блок 23 коммутации адреса, содержащий триггер 24 и коммутатор 25 адреса. 3 з.п. ф-лы, 6 ил.

шиг.г

.J

сриг.б

ПППП ПППП

3

и

фиг. 6

| Мажоритарное декодирующее устройство корректирующего кода Рида-Маллера | 1980 |

|

SU902283A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Мажоритарное декодирующее устройство | 1986 |

|

SU1372627A1 |

Авторы

Даты

1989-04-07—Публикация

1987-08-03—Подача