сриг.

Поставленная цель достигается тем, что процедура декодирования осуществляется путем последовательного решения проверочных уравнений и систем проверочных уравнений для каждого информационного символа. Символы поступающего из канала связи кодового слова записьшаются в один из кубов памяти блока 4 оперативной памяти в ячейки с адресом, сформированным вторым счетчиком 2. Декодируемое в текущий момент времени кодовое слово хранится в другом кубе памяти блока 4. Переключение устройства из режима декодирования в режим приема и обратно осуществляется блоком прерьшания 8. Блок 18 инверсии адреса в режиме декодирования разрешает доступ к тому кубу памяти блока 4, в котором хранится декодируемое кодовое слово, а в режиме приема - к другому кубу памяти блока 4. Решение проверочных уравнений осуществляется блоком 5 путем последовательного сложения по модулю два символов декодируемого кодового слова, считываемых из блока

4. Адреса соответствуюгдах ячеек блока 4 хранятся в запоминающем блоке 3 в последовательности, определяемой видом проверочных уравнений и систем проверочных уравнений. Управление запоминающим блоком 3 осуществляется при помощи первого счетчика 1. Результаты рещений проверочных уравнений накапливаются в решающем блоке 6. Оценка декодируемого в текущий момент времени информационного символа осуществляется в решающем блоке 6 по принципу большинства решений проверочных уравнений, входящих в систему проверок для данного информационного символа. Декодированный информационный символ переписьшается из решающего блока 6 в регистр 7. Если этот информационный символ входит в проверочные уравнения для других информационных символов, его значение с выхода младшего разряда регистра 7 записьшается через коммутатор 9 в блок 4 в ячейку с адресом, сформулированным на выходах запоминающего блока 3. 3 з.п. ф-лы, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

| Устройство для мажоритарного декодирования | 1987 |

|

SU1517137A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

| Кодер | 1990 |

|

SU1783623A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

Изобретение относится к радиотехнике и может быть использовано при передаче дискретной информации по каналам с шумами, в частности по стандартным телефонным каналам. Целью изобретения является расширение области применения устройства путем обеспечения возможности работы с различными кодами и улучшения устройства при декодировании длинных кодов.

1

Изобретение относится к радиотехнике и может быть использовано в системах передачи дискретной информации по каналам с шумами, в частности по стандартным телефонным каналам.

Цель изобретения - расширение области применения устройства путем обеспечения возможности работы с различными кодами и упрощения устройства при декодировании длинных кодов.

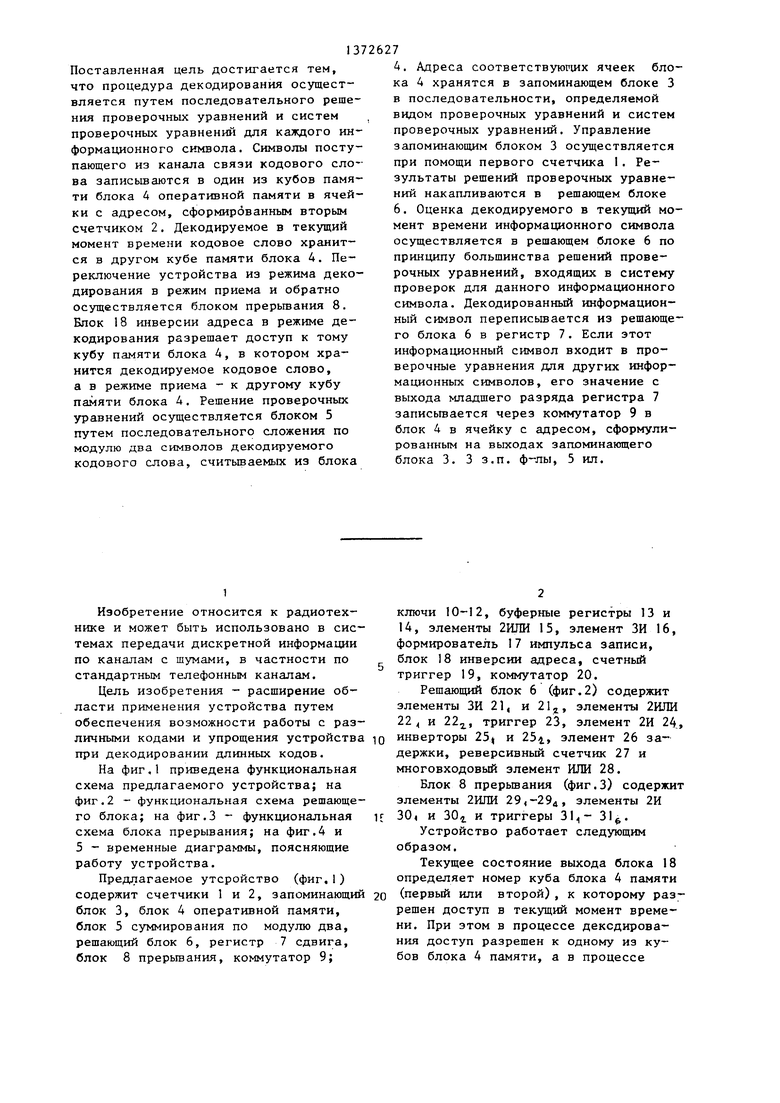

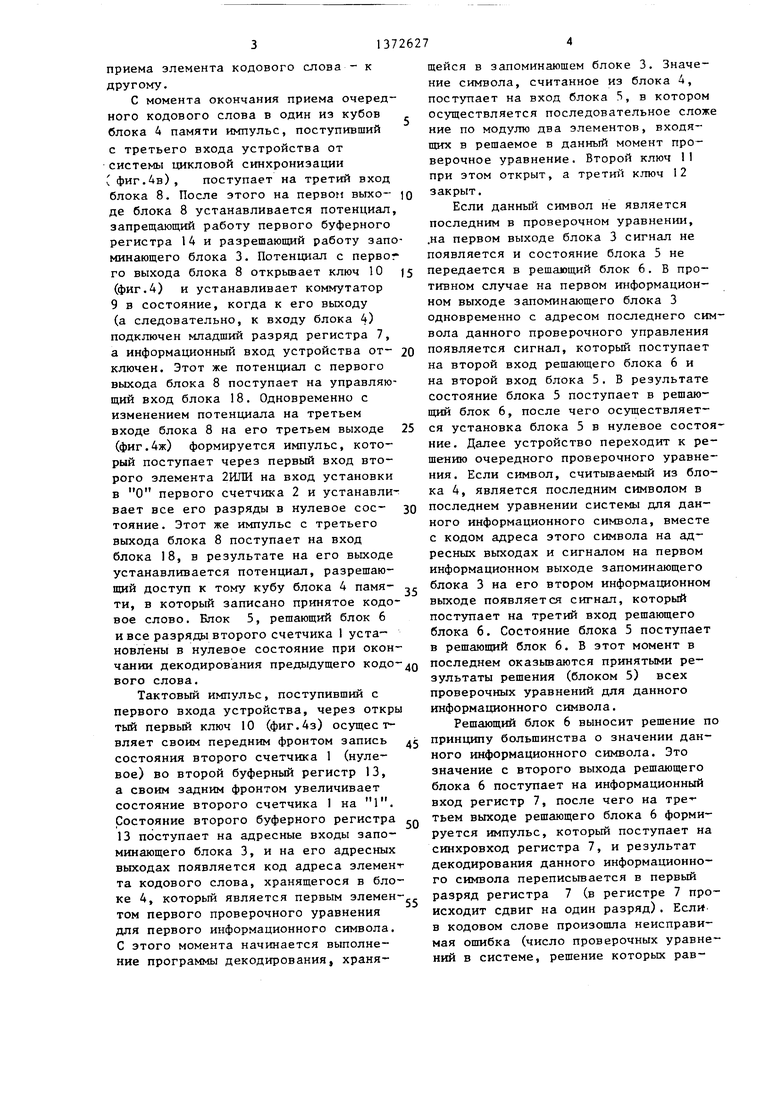

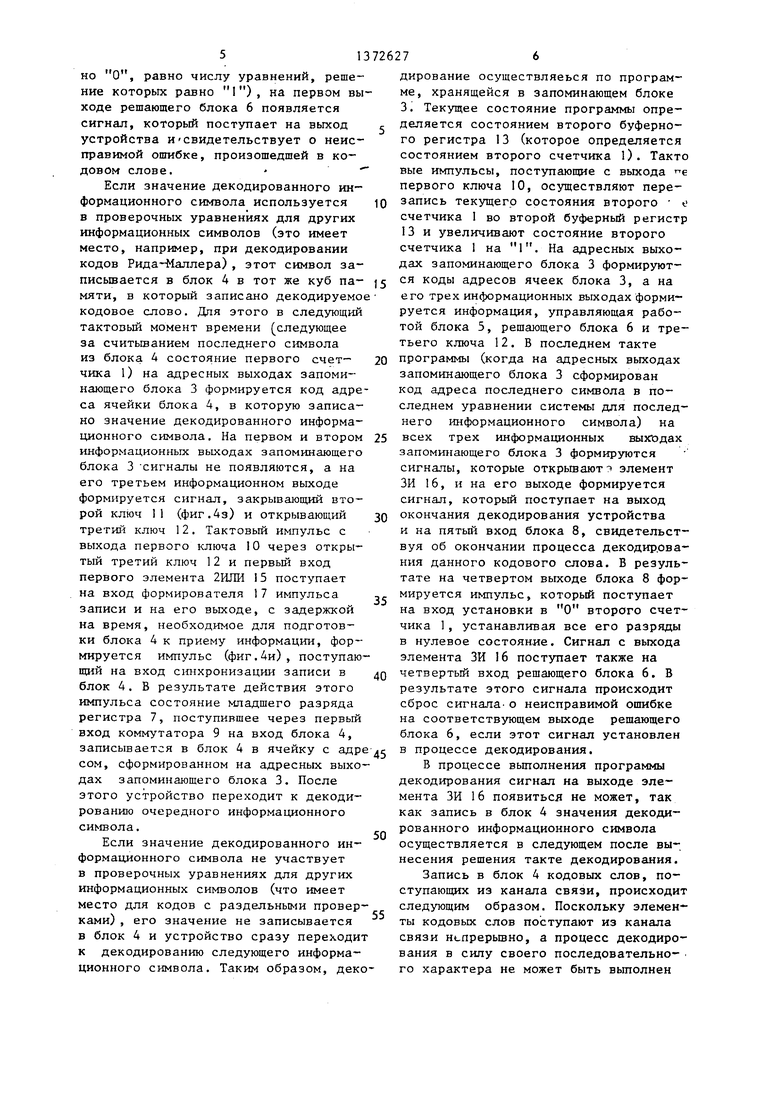

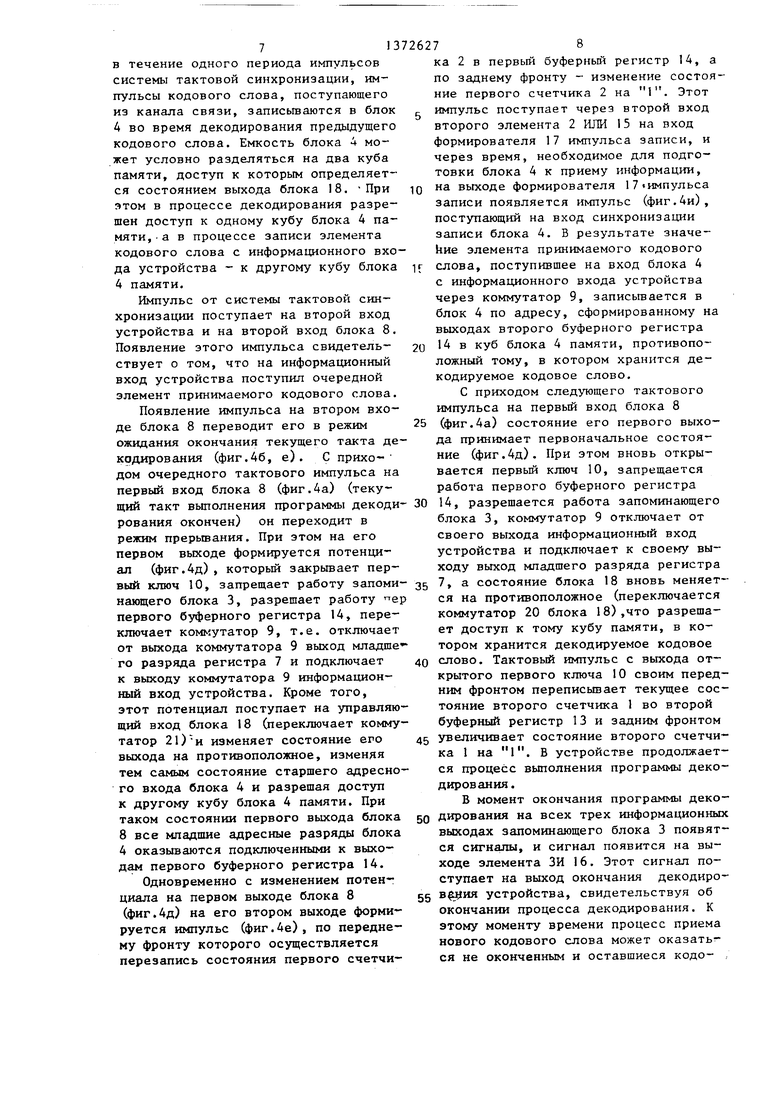

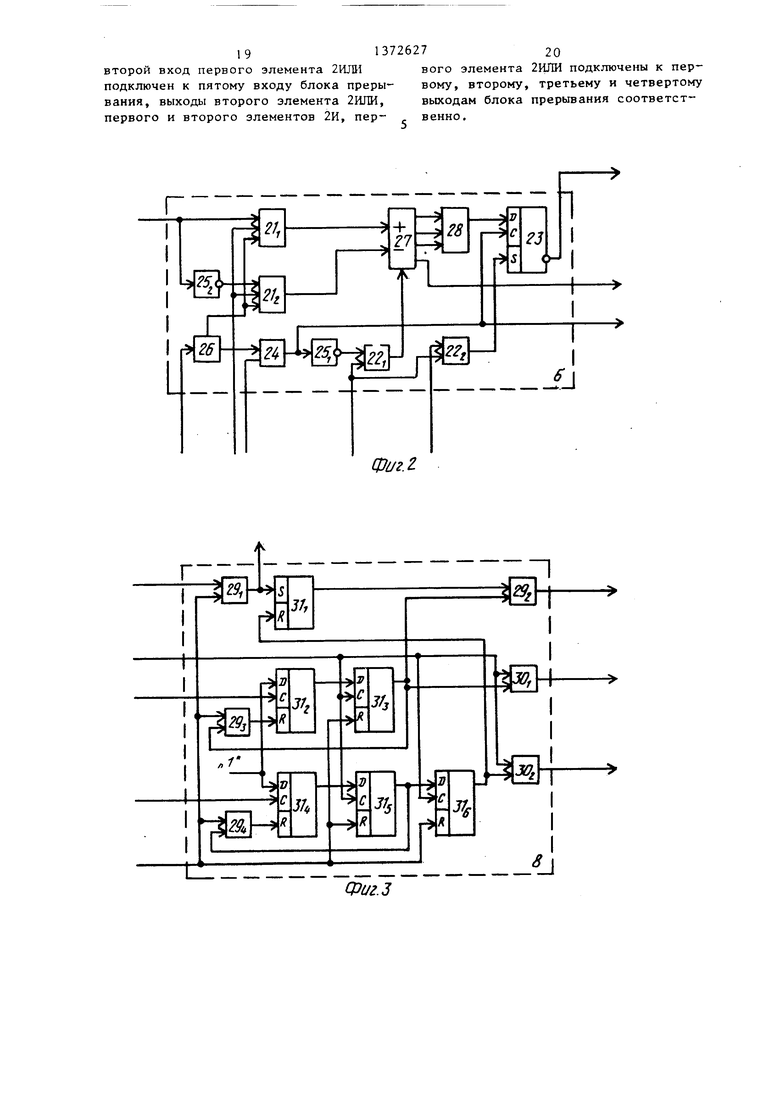

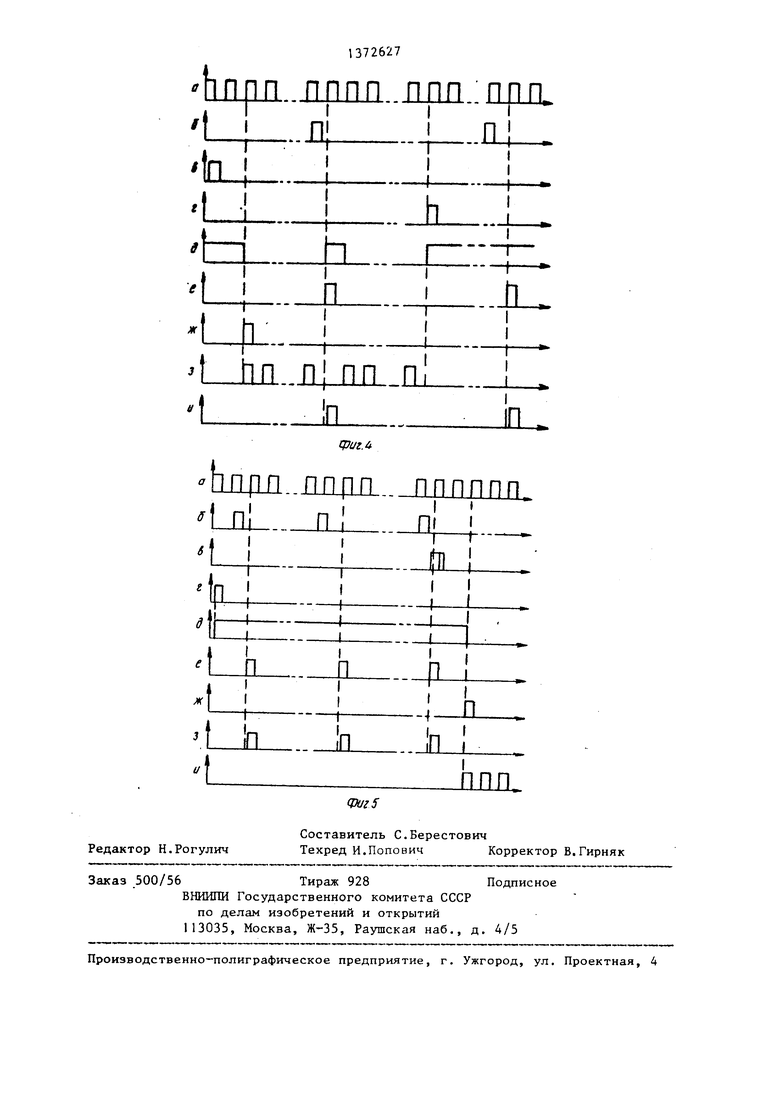

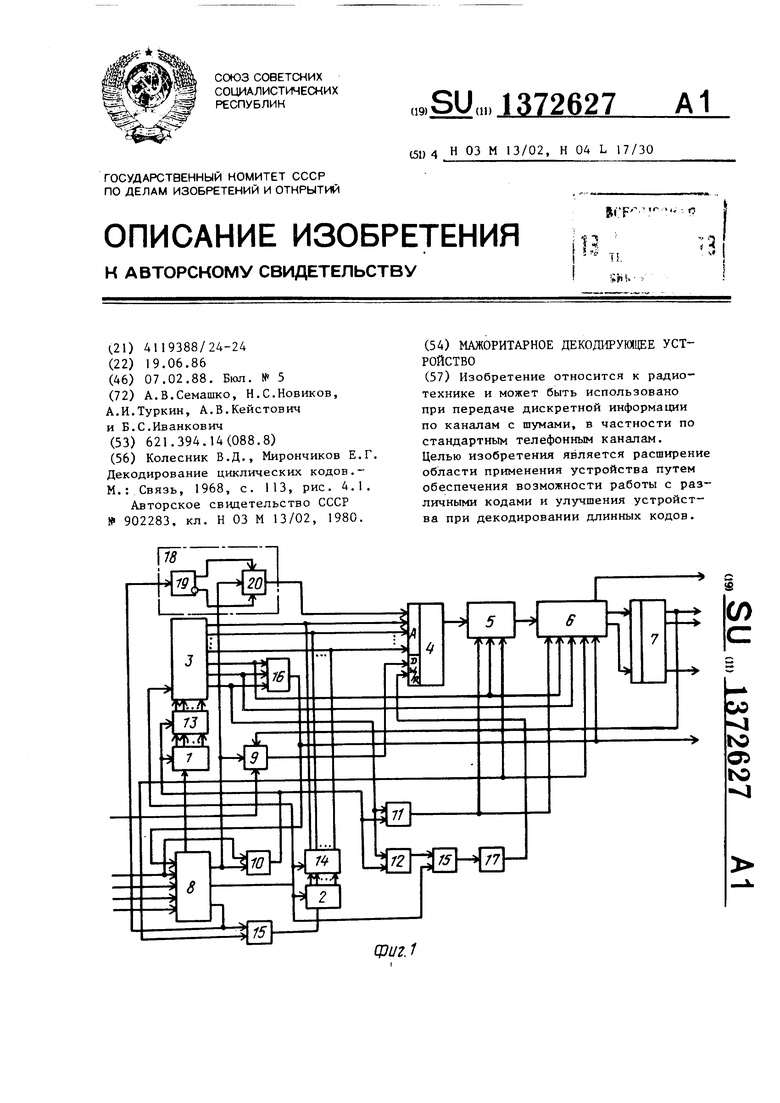

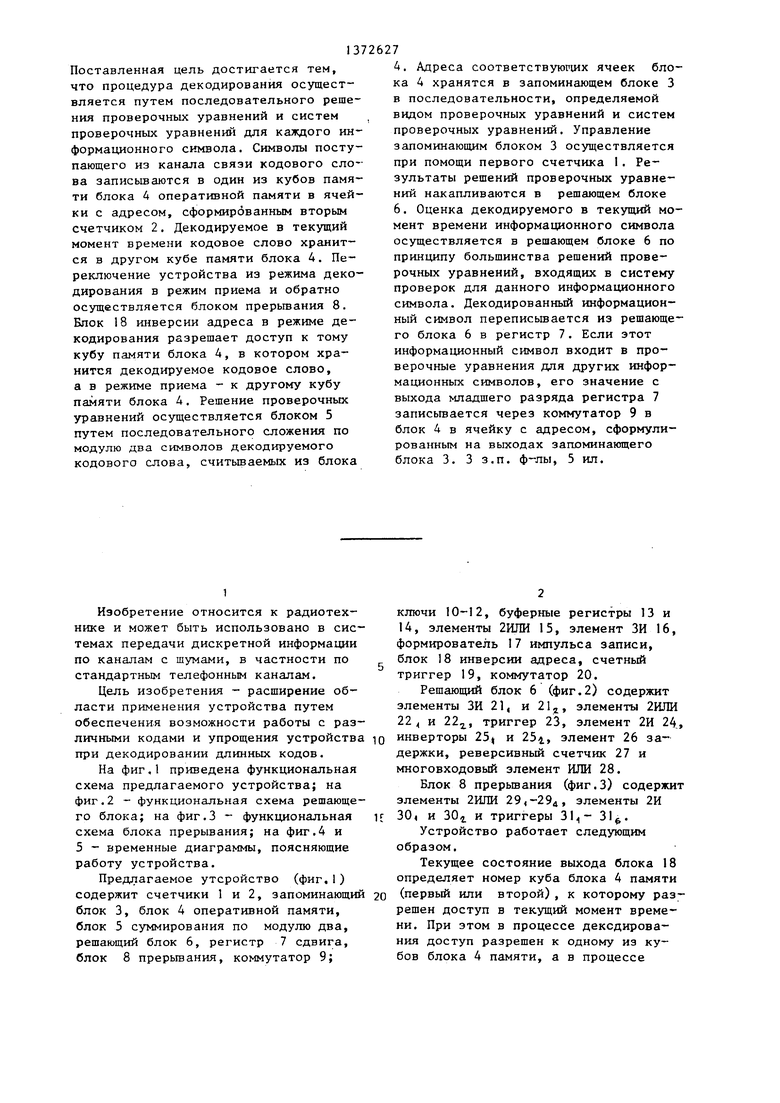

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема решающего блока; на фиг.З - функциональная схема блока прерывания; на фиг.4 и 5 - временные диаграммы, поясняющие работу устройства.

Предлагаемое утсройство (фиг,1) содержит счетчики 1 и 2, запоминающий блок 3, блок 4 оперативной памяти, блок 5 суммирования по модулю два, решающий блок 6, регистр 7 сдвига, блок 8 прерьшания, коммутатор 9;

ключи 10-12, буферные регистры 13 и 14, злементы 2ИЛИ 15, элемент ЗИ 16, формирователь 17 импульса записи, блок 18 инверсии адреса, счетный триггер 19, коммутатор 20.

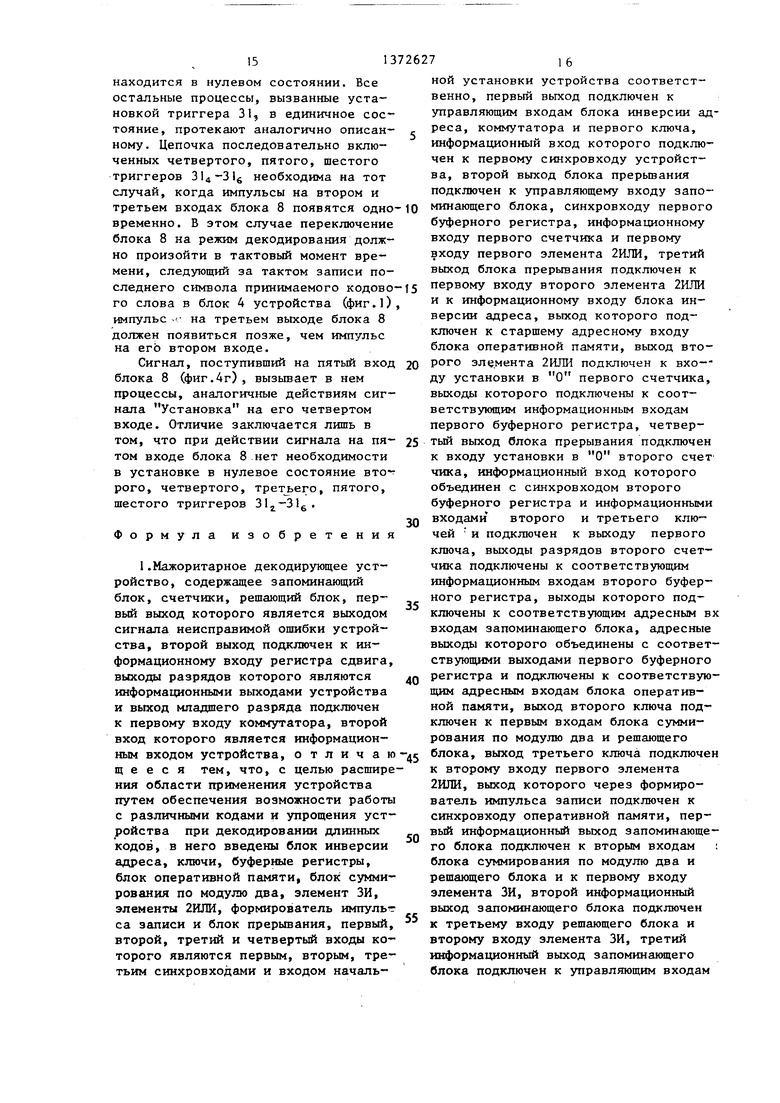

Решающий блок 6 (фиг.2) содержит элементы ЗИ 21, и 21j, элементы 2ШШ 22 и 222., триггер 23, элемент 2И 24, инверторы 25 и 254., элемент 26 задержки, реверсивный счетчик 27 и многовходовый элемент ИЛИ 28.

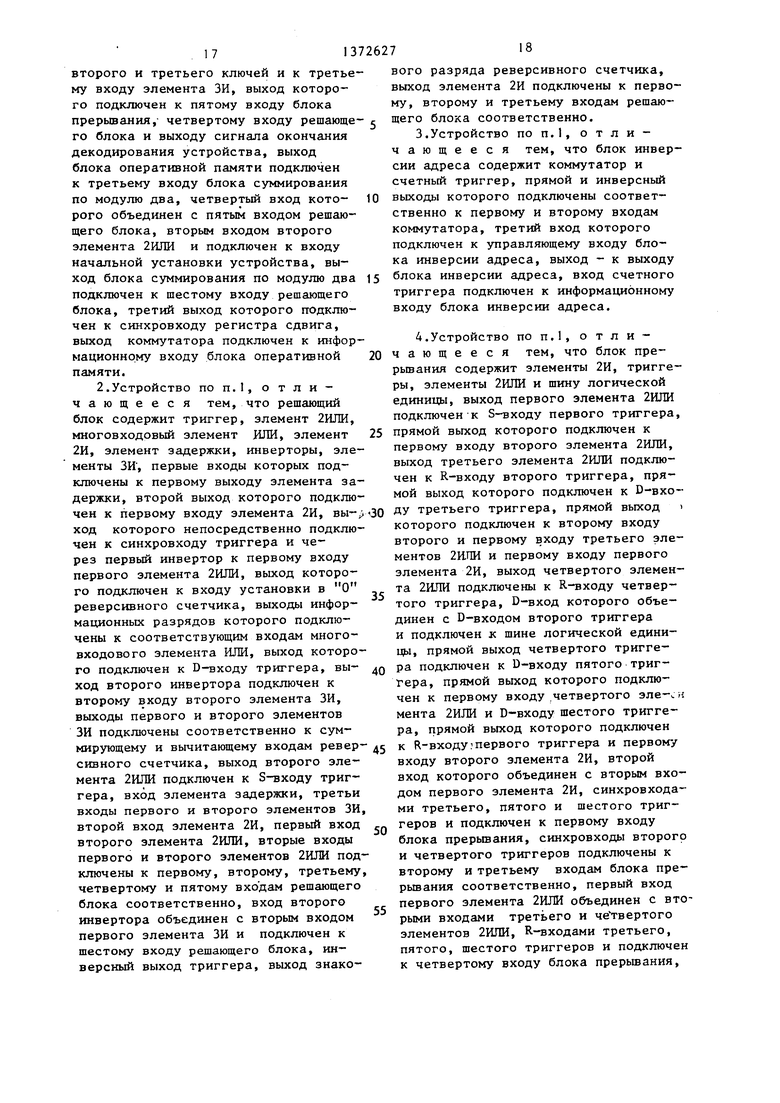

Блок 8 прерьшания (фиг.З) содержит элементы 2ИЛИ 29,-29, элементы 2И 30, и 30. и триггеры ЗЦ- 31.

Устройство работает следующим образом.

Текущее состояние выхода блока 18 определяет номер куба блока 4 памяти (первый или второй), к которому разрешен доступ в текущий момент времени. При этом в процессе декодирования доступ разрешен к одному из кубов блока 4 памяти, а в процессе

приема элемента кодового слова - к другому.

С момента окончания приема очередного кодового слова в один из кубов блока 4 памяти импульс, поступивший с третьего входа устройства от системы цикловой синхронизации Сфиг.4в), поступает на третий вход блока 8, После этого на первой выхо- де блока 8 устанавливается потенциал, запрещающий работу первого буферного регистра 14 и разрешающий работу запоминающего блока 3. Потенциал с первог го выхода блока 8 открьшает ключ 10

(фиг.4) и устанавливает коммутатор 9 в состояние, когда к его выходу

(а следовательно, к входу блока 4) подключен младший разряд регистра 7, а информационный вход устройства от- ключен. Этот же потенциал с первого выхода блока 8 поступает на управляющий вход блока 18. Одновременно с изменением потенциала на третьем входе блока 8 на его третьем выходе

(фиг.4ж) формируется импульс, который поступает через первый вход второго элемента 2ИЛИ на вход установки в О первого счетчика 2 и устанавлиг вает все его разряды в нулевое сое- тояние. Этот же импульс с третьего выхода блока 8 поступает на вход блока 18, в результате на его выходе устанавливается потенциал, разрешающий доступ к тому кубу блока 4 памя- ти, в который записано принятое кодовое слово. Блок 5, решающий блок 6 и все разряды второго счетчика 1 установлены в нулевое состояние при окончании декодирования предыдущего кодового слова.

Тактовьш импульс, поступивший с первого входа устройства, через откры тый первый ключ 10 (фиг.4з) осуществляет своим передним фронтом запись состояния второго счетчика 1 (нулевое) во второй буферный регистр 13, а своим задним фронтом увеличивает состояние второго счетчика 1 на 1. Состояние второго буферного регистра

13 поступает на адресные входы запоминающего блока 3, и на его адресных выходах появляется код адреса элемент та кодового слова, хранящегося в блоке 4, который является первым элементом первого проверочного уравнения для первого информационного символа. С этого момента начинается выполнение программы декодирования, храня

5

0 5

О 5 д

j Q

5

щейся в запоминающем блоке 3. Значение символа, считанное из блока 4, поступает на вход блока 5, в котором осуществляется последовательное сложе ние по модулю два элементов, входящих в решаемое в данный момент проверочное уравнение. Второй ключ 11 при этом открыт, а третий ключ 12 закрыт.

Если данный символ не является последним в проверочном уравнении, .на первом выходе блока 3 сигнал не появляется и состояние блока 5 не передается в решающий блок 6. В противном случае на первом информационном выходе запоминающего блока 3 одновременно с адресом последнего символа данного проверочного управления появляется сигнал, которьй поступает на второй вход решающего блока 6 и на второй вход блока 5. В результате состояние блока 5 поступает в решающий блок 6, после чего осуществляется установка блока 5 в нулевое состояние. Далее устройство переходит к решению очередного проверочного уравнения. Если символ, считываемый из блока 4, является последним символом в последнем уравнении системы для данного информационного символа, вместе с кодом адреса этого символа на адресных выходах и сигналом на первом информационном выходе запоминающего блока 3 на его втором информационном вьпсоде появляется сигнал, который поступает на третий вход решающего блока 6. Состояние блока 5 поступает в решающий блок 6. В зтот момент в последнем оказьюаются принятыми результаты решения (блоком 5) всех проверочных уравнений для данного информационного символа.

Решающий блок 6 выносит решение по принципу большинства о значении данного информационного символа. Это значение с второго выхода решающего блока 6 поступает на информационный вход регистр 7, после чего на тре- тьем выходе решающего блока 6 формируется импульс, который поступает на синхровход регистра 7, и результат декодирования данного информационного символа переписывается в первый разряд регистра 7 (в регистре 7 происходит сдвиг на один разряд). Если в кодовом слове произошла неисправимая ошибка (число проверочных уравнений в системе, решение которых рав

но О, равно числу уравнений, решение которых равно I), на первом выходе решающего блока 6 появляется сигнал, который поступает на выход устройства и Свидетельствует о неисправимой опгабке, произошедшей в кодовом слове.

Если значение декодированного информационного символа используется в проверочных уравнениях для других информационных символов (это имеет место, например, при декодировании кодов Рида-Маллера), этот символ за- письшается в блок 4 в тот же куб памяти, в который записано декодируемо кодовое слово. Для этого в следующий тактовьш момент времени (следующее за считьшанием последнего символа из блока 4 состояние первого счетчика 1) на адресных выходах запоминающего блока 3 формируется код адреса ячейки блока 4, в которую записано значение декодированного информационного символа. На первом и втором информационных выходах запоминающего блока 3 -сигналы не появляются, а на его третьем информационном выходе формируется сигнал, закрывающий второй ключ 11 (фиг.4з) и открывающий третий ключ 12. Тактовый импульс с выхода первого ключа 10 через открытый третий ключ 12 и первый вход первого элемента 2ИЛИ 15 поступает на вход формирователя 17 импульса записи и на его выходе, с задержкой на время, необходимое для подготовки блока 4 к приему информации, формируется импульс (фиг.4и), поступающий на вход С1шхронизации записи в блок 4. В результате действия этого импульса состояние младщего разряда регистра 7, поступившее через первый вход коммутатора 9 на вход блока 4, записывается в блок 4 в ячейку с адр сом, сформированном на адресных выходах запоминающего блока 3. После этого устройство переходит к декодированию очередного информационного сиьтола.

Если значение декодированного информационного символа не участвует в проверочных уравнениях для других информационных символов (что имеет место для кодов с раздельными проверками) , его значение не записывается в блок 4 и устройство сразу переходи к декодированию следующего информационного символа. Таким образом, дек

0

5

0

5

5

0

5

0

0

5

дирование осуществляеься по программе, хранящейся в запоминающем блоке 3. Текущее состояние программы определяется состоянием второго буферного регистра 13 (которое определяется состоянием второго счетчика 1). Такто вые импульсы, поступающие с выхода е первого ключа 10, осуществляют перезапись текущего состояния второго t счетчика 1 во второй буферный регистр 13 и увеличивают состояние второго счетчика 1 на 1. На адресных выходах запоминающего блока 3 формируются коды адресов ячеек блока 3, а на его трех информационных выходах формируется информация, управляющая работой блока 5, решающего блока 6 и третьего ключа 12. В последнем такте программы (когда на адресных выходах запоминающего блока 3 сформирован код адреса последнего символа в последнем уравнении системы для последнего информационного символа) на всех трех информационных выходах запоминающего блока 3 формируются сигналы, которые открьшают элемент ЗИ 16, и на его выходе формируется сигнал, которьш поступает на выход окончания декодирования устройства и на пятый вход блока 8, свидетельствуя об окончании процесса декодирования данного кодового слова. В результате на четвертом выходе блока 8 формируется импульс, который поступает на вход установки в О второго счетчика 1, устанавливая все его разряды в нулевое состояние. Сигнал с выхода элемента ЗИ 16 поступает также на четвертый вход решающего блока 6. В результате этого сигнала происходит сброс сигнала-о неисправимой ошибке на соответствующем выходе решающего блока 6, если этот сигнал установлен в процессе декодирования.

В процессе выполнения программы декодирования сигнал на выходе элемента ЗИ 16 появиться не может, так как запись в блок 4 значения декодированного информационного символа осуществляется в следующем после вынесения решения такте декодирования.

Запись в блок 4 кодовых слов, поступающих из канала связи, происходит следующим образом. Поскольку элементы кодовых слов поступают из канала связи нспрерьшно, а процесс декодирования в силу своего последовательно- . го характера не может быть вьшолнен

в течение одного периода импульсов системы тактовой синхронизации, им- ггульсы кодового слова, поступающего из канала связи, записываются в блок 4 во время декодирования предыдущего кодового слова. Емкость блока 4 может условно разделяться на два куба памяти, доступ к которым определяется состоянием выхода блока 18. -При этом в процессе декодирования разрешен доступ к одному кубу блока 4 памяти, а в процессе записи элемента кодового слова с информационного входа устройства - к другому кубу блока 4 памяти.

Импульс от системы тактовой синхронизации поступает на второй вход устройства и на второй вход блока 8. Появление зтого импульса свидетель- ствует о том, что на информационный вход устройства поступил очередной элемент принимаемого кодового слова.

Появление импульса на втором входе блока 8 переводит его в режим ожидания окончания текущего такта декодирования (фиг.46, е). С прихо- дом очередного тактового импульса на первый вход блока 8 (фиг.4а) (текущий такт выполнения программы декоди рования окончен) он переходит в режим прерьшания. При этом на его первом выходе формируется потенциал (фиг.4д), который закрывает первый ключ 10, запрещает работу запоми нающего блока 3, разрешает работу е первого буферного регистра 14, переключает комь утатор 9, т.е. отключает от выхода коммутатора 9 выход младше го разряда регистра 7 и подключает к выходу коммутатора 9 информационный вход устройства. Кроме того, этот потенциал поступает на управляющий вход блока 18 (переключает коммутатор 21) и изменяет состояние его выхода на противоположное, изменяя тем самым состояние старшего адресного входа блока 4 и разрешая доступ к другому кубу блока 4 памяти. При таком состоянии первого выхода блока 8 все младшие адресные разряды блока 4 оказываются подключенными к выходам первого буферного регистра 14.

Одновременно с изменением потенциала на первом выходе блока 8 (фиг.4д) на его втором выходе формируется импульс (фиг.4е), по переднему фронту которого осуществляется перезапись состояния первого счетчика 2 в первый буферный регистр 14, а по заднему фронту - изменение состояние первого счетчика 2 на I. Этот импульс поступает через второй вход второго элемента 2 ИЛИ 15 на вход формирователя 17 импульса записи, и через время, необходимое для подготовки блока 4 к приему информации, на выходе формирователя 17«импульса записи появляется импульс (фиг.4и), поступающий на вход синхронизации записи блока 4. В результате значе- йие элемента принимаемого кодового слова, поступившее на вход блока 4 с информационного входа устройства через коммутатор 9, записьшается в блок 4 по адресу, сформированному на выходах второго буферного регистра 14 в куб блока 4 памяти, противоположный тому, в котором хранится декодируемое кодовое слово.

С приходом следующего тактового импульса на первый вход блока 8 (фиг.4а) состояние его первого выхода принимает первоначальное состояние (фиг.4д). При этом вновь открывается первый ключ 10, запрещается работа первого буферного регистра 14, разрешается работа запоминающего блока 3, коммутатор 9 отключает от своего выхода информационный вход устройства и подключает к своему выходу выход младшего разряда регистра 7, а состояние блока 18 вновь меняется на противоположное (переключается коммутатор 20 блока 18),что разрешает доступ к тому кубу памяти, в котором хранится декодируемое кодовое слово. Тактовый импульс с выхода открытого первого ключа 10 своим передним фронтом переписывает текущее состояние второго счетчика 1 во второй буферный регистр 13 и задним фронтом увеличивает состояние второго счетчика 1 иа 1. В устройстве продолжается процесс выполнения программы декодирования .

В момент окончания программы декодирования на всех трех информационны выходах запоминающего блока 3 появятся сигналы, и сигнал появится на выходе элемента ЗИ 16. Этот сигнал поступает на выход окончания декодиро устройства, свидетельствуя об окончании процесса декодирования. К этому моменту времени процесс приема нового кодового слова может оказать ся не оконченным и оставшиеся кодовые символы должны быть записаны в блок 4. Сигнал с выхода элемента ЗИ 16 поступает на четвертый вход решающего блока 6 и на 5 вход блока 8, в результате чего на его первом выходе устанавливается потенциал (фиг.4д), закрьшающий первый ключ 10, запрещающий работу запоминающего блока 3 и разрешающий работу первого буферного регистра 14. Этот же Лотенциал переключает коммутатор 9 в состояние, когда к его выходу подключен информационный вход устройства и изменяет

состояние выхода блока 18 на противо- и блока 8 формируется импульс (фиг.4ж).

положное (переключает коммутатор 20 блока 18). Этот потенциал на первом выходе блока 8 сохраняется неизменным до прихода импульса на его третий вход от системы цикловой синхронизации (фиг.4в). На втором выходе блока 8 импульсы появляются с приходом очередного импульса на второй вход блока 8 (от системы тактовой синхронизации), который переходит в режим ожидания, с приходом очередного тактового импульса на его первый вход на его втором выходе формируется импульс (фиг.9е), по переднему фронту которого осуществляется запись текущего состояния первого счетчика 2 в первый буферный регистр 14, а по заднему фронту - изменение состояния первого счетчика 2 на 1. Этот же импульс поступает через второй вход второго элемента 2ИЛИ 15, на вход формирователя 17 импульса записи, и через время, необходимое для подготовки блока 4 к приему информации, на выходе формирователя 17 импульса записи появляется импульс, который поступает на вход синхронизации записи блока 4.

Таким образом, осуществляется запись очередного символа принимаемого кодового слова, поступившего с информационного входа устройства через коммутатор 9 на вход блока 4, в ячейку блока 4 по адресу, сформированому на выходах первого буферного ре- 50 извольным и они должны быть подготовгистра 14 и на выходе блока 18.

С рриходом очередного тактового импульса на третий вход блока 8 (от системы цикловой синхронизации (фиг.9в), что свидетельствует о том, что все принимаемое кодовое слово принято в блок 4) устройство перез:о- дит в режим декодирования. При этом на первом выходе блока 8 формируется

лены к решению системы проверочных уравнений.

С этой целью на вход начальной установки устройства подается сигнал 55 Установка перед приемом первого кодового слова (фиг.Зг). Этот сигнал через второй вход второго элемента 2ИШ. 15 поступает на вход установки в О первого счетчика 2 и устанавли7262710

потенциал (фиг.4д), который переключает коммутатор 9 (отключает от выхода коммутатора 9 информационньй вход устройства и подключает к выходу коммутатора 9 выход старшего разряда регистра 7), открывает первый ключ 10, запрещает работу первого буферного регистра 14, разрешает работу запоми- 10 нающего блока 3. Этот же потенциал поступает на управляющий вход блока 18 (переключает коммутатор 20 блока 18).

Одновременно на третьем выходе

который поступает на вход блока 18, на вход счетного триггера 19 и инвертирует его состояние. Таким образом, в блоке 18 выполняются две операции

инверсии (с поступлением импульса на вход блока 18 с третьего выхода блока 8 и с изменением потенциала на его управляющем входе), состояние его выхода не изменяется, т.е. разрешается доступ к тому кубу блока 4

памяти, в который записано подлежащее декодированию кодовое слово. Запись следующего кодового слова осуществляется в противоположный куб памяти.

С третьего выхода блока 8 импульс поступает через первый вход второго элемента 2ИЛИ I5 на вход установки в О первого счетчика 2 и устанавливает все его разряды в нулевое состоя-

ние. Второй счетчик 1 устанавливается в нулевое состояние импульсом с четвертого выхода блока 8 после окончания программы декодирования. Далее процесс декодирования повторяется.

Решающий блок 6 и блок 5 подготовлены к решению новой системы проверочных уравнений после обработки последнего символа последнего уравнения системы для последнего информационного символа декодированного кодового слова. Однако в начале декодирования первого кодового слова (после включения устройства) состояние решающего блока 6 и блока 5 может оказаться пролены к решению системы проверочных уравнений.

С этой целью на вход начальной установки устройства подается сигнал 55 Установка перед приемом первого кодового слова (фиг.Зг). Этот сигнал через второй вход второго элемента 2ИШ. 15 поступает на вход установки в О первого счетчика 2 и устанавливает все его разряды в нулевое состояние ,

Решающий блок 6 работает следующим образом.

Сигнал, поступивший на пятый вход решающего блока 6, через второй вход первого элемента 2Ш1И 22, поступает .. на вход установки в О реверсивного счетчика 27, устанавливая все его разряды в нулевое состояние. Этот же сигнал с пятого входа через второй вход второго элемента 2ИЛИ 22 посту пает на S-вход триггера 23 и устанавливает его в единичное состояние (на его инверсном выходе устанавливается нулевой потенциал). Сигнал с шестого входа решающего блока 6 поступает на вход первого элемента ЗИ 2I непосредственно, а на вход второго элемента ЗИ 21 через второй инвертор 25,. Если сигнал на шестом входе решающего блока 6 имеет единичное значение, на первом входе первого элемента ЗИ 21, устанавливается единичный потенциал, а на первом входе вто рого элемента ЗИ 21 - нулевой потен циал. Если сигнал на входе решающего блока 6 примет нулевое значение, потенциалы на первых входах первого и второго элементов ЗИ 21, и 21 изменятся на противоположные. При установлении единичного потенциала на втором входе решающего блока 6 единичные потенциалы установятся на вторых входах обоих элементов ЗИ 21 и 2J и импульс с первого выхода элемента 26 задержки поступит на сумми- рующрий вход реверсивного счетчика 27, если на шестом входе решающего блока 6 установлен единичный потенциал, или на вычитающий вход реверсивного счетчика 27, если на шестом входе решающего блока 6 установлен нулевой потенциал. На первом выходе элемента задержки сигнал появляется с задержкой относительно появления сигнала на его входе на время, необходимое для формирования сигнала на шестом входе решающего блока 6. Это время складывается из времени приема во второй буферный регистр 13 устройства (фиг.1) состояния второго счетчика 1, времени срабатьшания запоминающего блока 3, времени считывания информации из блока 4 и времени выполнения одной операции сложения по модулю два в блоке 5 суммирования.

7262712

Таким образом, результаты решения проверочных уравнений блоком 5 накапливаются реверсивным счетчиком 27 с решающего блока 6. ЕдиничньШ потенциал, поступивший с третьего входа решающего блока 6, поступает на второй вход элемента 2И 24. На втором выходе элемента 26 задержки сигнал 10 появляется с задержкой относительно появления сигнала на его первом выходе на время, необходимое для срабатывания реверсивного счетчика 27. Сигнал с второго выхода элемента 26 1Г задержки через первый вход открытой схемы 2И 24 поступает на третий выход решающего блока 6. К этому моменту времени в реверсивном счетчике

27осуществлено накопление результа- 20 тов решений всех проверочных уравнений решаемой системы проверочных уравиений. Состояние знакового разряда .реверсивного счетчика 27 соответствует результату решения этой систе-

25 мы проверочных уравнений по принципу большинства. Если все разряды, кроме знакового, реверсивного счетчика 21 находятся в нулевом состоянии, это свидетельствует о том, что в декоди30 руемом кодовом слове произошла неисправимая ошибка, т.е. число импульсов, поступивших на суммирующий вход реверсивного счетчика 27, равно числу импульсов, поступивших на его вычи-г

35 тающий вход. В результате на всех входах многовходового элемента ИЛИ

28установятся нулевые потенциалы и нулевой потенциал установится на ее выходе. Импульс, поступивший с выхо40 да схемы 2И 24, поступает на синхро- вход триггера 23 и устанавливает его в кулевое состояние, так как на его D-входе установлен нулевой потенциал с выхода многовходового элемента

45 ИЛИ 28. Единичный потенциал с инверсного выхода триггера 23 поступит на первый выход решающего блока 6. Такое состояние триггера 23 сохраняется неизменным до прихода сигнала с чет50 вертого входа решающего блока 6 (процесс декодирования данного кодового слова закончен). Этот сигнал через первый вход схемы 2ШШ 22 поступит на S-вход триггера 23 и установит его

55 в единичное состояние.

1&1пульс с выхода элемента 2И 24 через первый инвертор 254 и первый вход первого элемента 2ИЛИ 22 поступает на вход установки в О реверсивного счетчика 27, устанавливая все его разряды в нулевое состояние. Таким образом, по переднему фронту импульса, действующего на выходе схемы 2И 24, осуществляется прием состояния знакового разряда (значение декодированного информационного символа) в регистр 7 устройства (фиг.1), а по заднему фронту этого импульса - сброс реверсивного счетчика 27 решающего блока 6 в нулевое состояние. После этого цикл работы решающего блока 6 повторяется.

Блок 8 прерывания работает еле- дующим образом.

Сигнал Установка поступает с четвертого входа блока 8 (фиг.Зг) и через первьш вход первого элемента 2ИЛИ 29, поступает на четвертый вы- ход блока 8 и далее на вход установки в О второго счетчика 1 устройства (фиг.1) , этот же импульс поступает на S-гвход первого триггера 31, блока 8 и устанавливает его в единичное состояние, все остальные триггеры. 31 устанавливаются в нулевое состояние. Оба элемента 2И 30 оказьшаются закрытыми нулевыми потенциалами на своих первых входах. Сиг- нал с выхода первого триггера 31 через второй вход второго элемента 2ИЛИ 29 поступает на первый выход блока 8 (фиг.5д). Импульс, поступивший с второго входа блока 8 (фиг.Зб) поступает на синхровход второго триггера 31 и устанавливает его в единичное состояние. С приходом очередного тактового импульса на первый вход блока 8 в единичное состояние переключается третий триггер ЗЦ, а второй триггер 31 сбрасывается в нулевое состояние сигналом, поступившим с выхода третьего триггера 31, через первый вход третьего элемента 2ИЛИ 293 на R-вход второго триггера 31J. Единичный потенциал с выхода третьеготриггера ЗЦ открывает первый элемент 2И 31 единичным потенциалом на его первом входе и такто- вый импульс с первого входа блока 8 проходит на его второй выход (фиг.Зе Следующий и myльc с первого входа блока 8 устанавливает третий тригге 313 в нулевое состояние, так как на его D-входе установился нулевой потенциал с выхода второго триггера З. Первый элемент 2И 30, закрывается нулевым потенциалом на своем первом входе. С приходом следующего импульса на второй вход блока 8 {фиг.Зд) описанный процесс повторяется .

Импульс, поступивший с третьего входа блока 8 (фиг.Зв), устанавливает четвертый триггер 314 в единичное состояние. Импульс с первого входа блока 8 (фиг.За) устанавливает в единичное состояние пятый триггер 31 5, так как на его D-входе установ- лен единичньш потенциал с выхода четвертого триггера З. Единичный потенциал с выхода пятого триггера 31f поступает через первый вход четвертого элемента 2ИЛИ 294 четвертого триггера 31 и устанавливает его в нулевое состояние. Следующий импульс с первого входа блока 8 устанавливает в единичное состояние триггер 31g, а триггер 31 устанавливается в нулевое состояние. Единичный потенциал с выхода триггера 31 открьшает элемент 2И 30 единичным потенциалом на его первом входе и сигнал с первого входа блока 8 по ступает на его третий выход (фиг.Зж, 4д, ж). Одновременно единичный потенциал с вькода триггера 31g поступает на R-вход триггера 31, и устанавливает его в нулевое состояние. В результате на первом выходе блока 8 устанавливается нулевой потенциал

(фиг.Зд, 4б), так как на обеих входах второго элемента 2ИЛИ 29 устанавливаются нулевые потенциалы с выходов первого и третьего триггеров 31, и 31,.

Устройство (фиг.1) переходит к процессу декодирования. Следующий такто вьш импульс с первого входа блока 8 устанавливает шестой триггер 31 в нулевое состояние и закрьюает второй элемент 2И 30 нулевым потенциалом на его втором входе. Цепочка последовательно включенных второго и третьего триггеров 31i и ЗЦ обеспечивает режим ожидания блока 8 окончания текущего такта вьтолнения программы декодирования устройства (фиг.1, 46, д, е). При установке третьего триггера ЗЦ блока 8 в единичное состояние, единичный потенциал поступает через второй вход второго элемента 2ИЛИ 29г на первый выход блока 8

(фиг.4б), во время выполнения программы декодирования устройства

(фиг.1) первый триггер 31 блока 8

находится в нулевом состоянии. Все остальные процессы, вызванные установкой триггера ЗЦ в единичное состояние, протекают аналогично описанному. Цепочка последовательно включенных четвертого, пятого, шестого триггеров 314-31б необходима на тот случай, когда импульсы на втором и

третьем входах блока 8 появятся одно-10 минающего блока, синхровходу первого

временно. В этом случае переключение блока 8 на режим декодирования должно произойти в тактовый момент времени, следующий за тактом записи последнего символа принимаемого кодового слова в блок 4 устройства (фиг.1), импульс . на третьем выходе блока 8 должен появиться позже, чем импульс на его втором входе.

Сигнал, поступивший на пятый вход блока 8 (фиг.4г) , вызьшает в нем процессы, аналогичные действиям сигнала Установка на его четвертом входе. Отличие заключается лишь в том, что при действии сигнала на пя- том входе блока 8 .нет необходимости в установке в нулевое состояние вто рого, четвертого, третьего, пятого, шестого триггеров .

Формула изобретения

кодов, в него введены блок инверсии адреса, ключи, буферные регистры, блок оперативной памяти, блок суммирования по модулю два, элемент ЗИ, элементы 2Ш1И, формирователь импулыг са записи и блок прерывания, первый, второй, третий и четвертый входы которого являются первым, вторым, третьим сиихровходами и входом началь

ной установки устройства соответственно, первый выход подключен к управляющим входам блока инверсии адреса, коммутатора и первого ключа, информационный вход которого подключен к первому синхровходу устройства, второй выход блока прерьшания подключен к управляющему входу запо

0 5

0

5

0

j

0

5

буферного регистра, информационному входу первого счетчика и первому входу первого элемента 2ИЛИ, третий выход блока прерывания подключен к первому входу второго элемента 2ИЛИ и к информационному входу блока инверсии адреса, выход которого подключен к старшему адресному входу блока оперативной памяти, выход второго эл(;мента 2ИЛИ подключен к вхо- ду установки в О первого счетчика, вькоды которого подключены к соответствующим информационным входам первого буферного регистра, четвертый выход блока прерывания подключен к входу установки в О второго счетчика, информационный вход которого объединен с синхровходом второго буферного регистра и информационными входами второго и третьего ключей и подключен к выходу первого ключа, выходы разрядов второго счетчика подключены к соответствующим информационным входам второго буферного регистра, выходы которого подключены к соответствующим адресным вх входам запоминающего блока, адресные выходы которого объединены с соответствующими выходами первого буферного регистра и подключены к соответствующим адресным входам блока оперативной памяти, выход второго ключа подключен к первым входам блока суммирования по модулю два и решающего блока, выход третьего ключа подключен к второму входу первого элемента 2Ш1И, выход которого через формирователь импульса записи подключен к синхровходу оперативной памяти, первый информационный вькод запоминающего блока подключен к вторым входам ; блока суммирования по модулю два и решающего блока и к первому входу элемента ЗИ, второй информационный выход запоминающего блока подключен к третьему входу решающего блока и второму входу элемента ЗИ, третий информационный выход запоминающего блока подключен к управляющим входам

171372627

второго и третьего ключей и к третьему входу элемента ЗИ, выход которого подключен к пятому входу блока

прерьшания, четвертому входу решающе- с щего блока соответственно.

го блока и выходу сигнала окончания декодирования устройства, выход блока оперативной памяти подключен к третьему входу блока суммирования по модулю два, четвертый вход которого объединен с пятым входом решающего блока, вторым входом второго элемента 2ИЛИ и подключен к входу начальной установки устройства, вы3.Устройство по П.1, о чающееся тем, что сии адреса содержит коммут счетный триггер, прямой и 10 выходы которого подключены ственно к первому и втором коммутатора, третий вход к подключен к управляющему в ка инверсии адреса, выход

ход блока суммирования по модулю два 15 блока инверсии адреса, вход счетного

триггера подключен к информационному входу блока инверсии адреса.

рьтания содержит элементы 2И, триггеры, элементы 2ИЛИ и шину логической единицы, выход первого элемента 2ИЛИ подключен к S-входу первого триггера, 25 прямой выход которого подключен к первому входу второго элемента 2ИЛИ, выход третьего элемента 2ИЛИ подключен к R-входу второго триггера, прямой выход которого подключен к D-BXOподключен к шестому входу решающего блока, третий выход которого подключен к синхровходу регистра сдвига, выход коммутатора подключен к информационному входу блока оперативной 20 чающееся тем, что блок пре- памяти.

элемента 2И, выход четвертого элемента 2ИЛИ подключены к R-входу четвертого триггера, D-вход которого объединен с D-входом второго триггера и подключен к щине логической единицу, прямой выход четвертого тригге- 40 ра подключен к D-входу пятого триггера, прямой выход которого подключен к первому входу .четвертого мента 2ИЛИ и D-входу шестого триггера, прямой выход которого подключен пирующему и вычитающему входам ревер- к R-входу;первого триггера и первому сивного счетчика, выход второго эле- входу второго элемента 2И, второй мента 2ИЛИ подключен к S-входу триг- вход которого объединен с вторым вхопервого элемента 2ИЛИ, выход которого подключен к входу установки в О реверсивного счетчика, выходы информационных разрядов которого подключены к соответствующим входам много- входового элемента ИЛИ, выход которого подключен к D-входу триггера, выход второго инвертора подключен к второму входу второго элемента ЗИ, выходы первого и второго элементов ЗИ подключены соответственно к сум35

гера, вход элемента эадержки, третьи входы первого и второго элементов ЗИ,

второй вход элемента 2И, первый вход . геров и подключен к первому входу

второго элемента 2ИЖ, вторые входы первого и второго элементов 2ИЛИ подключены к первому, второму, третьему, четвертому и пятому входам решающего блока соответственно, вход второго инвертора объединен с вторым входом первого элемента ЗИ и подключен к шестому входу решающего блока, инверсный выход триггера, выход знако55

блока прерьшания, синхровходы втор и четвертого триггеров подключены второму и третьему входам блока рьтания соответственно, первый вх первого элемента 2ИЛИ объединен с рыми входами третьего и че тверто элементов 2Ш1И, R-входами третьег пятого, шестого триггеров и подклю к четвертому входу блока прерьшан

18

вого разряда реверсивного счетчика, выход элемента 2И подключены к первому, второму и третьему входам решаю-

триггера подключен к информационному входу блока инверсии адреса.

чающееся тем, что блок пре-

ющееся тем, что блок пре

рьтания содержит элементы 2И, триггеры, элементы 2ИЛИ и шину логической единицы, выход первого элемента 2ИЛИ подключен к S-входу первого триггера, прямой выход которого подключен к первому входу второго элемента 2ИЛИ, выход третьего элемента 2ИЛИ подключен к R-входу второго триггера, прямой выход которого подключен к D-BXOчающееся тем, что блок пре-

ДУ третьего триггера, прямой выход которого подключен к второму входу второго и первому входу третьего эле- ментов 2ИПИ и первому входу первого

дом первого элемента 2И, синхровхода- ми третьего, пятого и шестого триг5

блока прерьшания, синхровходы второго и четвертого триггеров подключены к второму и третьему входам блока пре- рьтания соответственно, первый вход первого элемента 2ИЛИ объединен с вторыми входами третьего и че твертого элементов 2Ш1И, R-входами третьего, пятого, шестого триггеров и подключен к четвертому входу блока прерьшания.

19

второй вход первого элемента 2ИЛИ подключен к пятому входу блока прерывания, выходы второго элемента 2ИЛИ, первого и второго элементов 2И, пер137

Фиг.З

ы, 137262720

вого элемента 2ИЛИ подключены к первому, второму, третьему и четвертому выходам блока прерывания соответственно.

Фиг. 2.

I

hnpn ппрп ПППППП,

in .

| Колесник В.Д., Мирончиков Е.Г | |||

| Декодирование циклических кодов.- М.: Связь, 1968, с | |||

| Способ обработки грубых шерстей на различных аппаратах для мериносовой шерсти | 1920 |

|

SU113A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Мажоритарное декодирующее устройство корректирующего кода Рида-Маллера | 1980 |

|

SU902283A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-19—Подача