Изобретенуе относится к импульсной технике и может быть использовано в автоматизированных системах управления технологическими процессами в следящих преобразователях типа фаза - перемещение и т.д.

Целью изобретения является расширение динамического диапазона и повышение надежности преобразования.

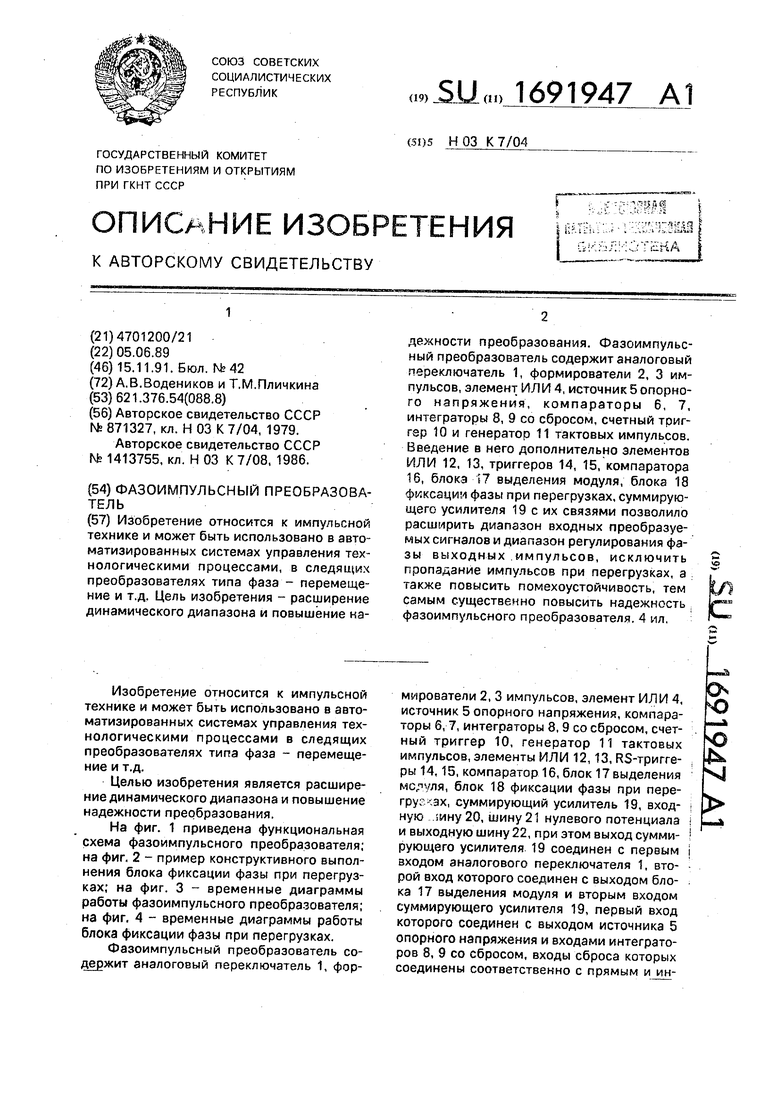

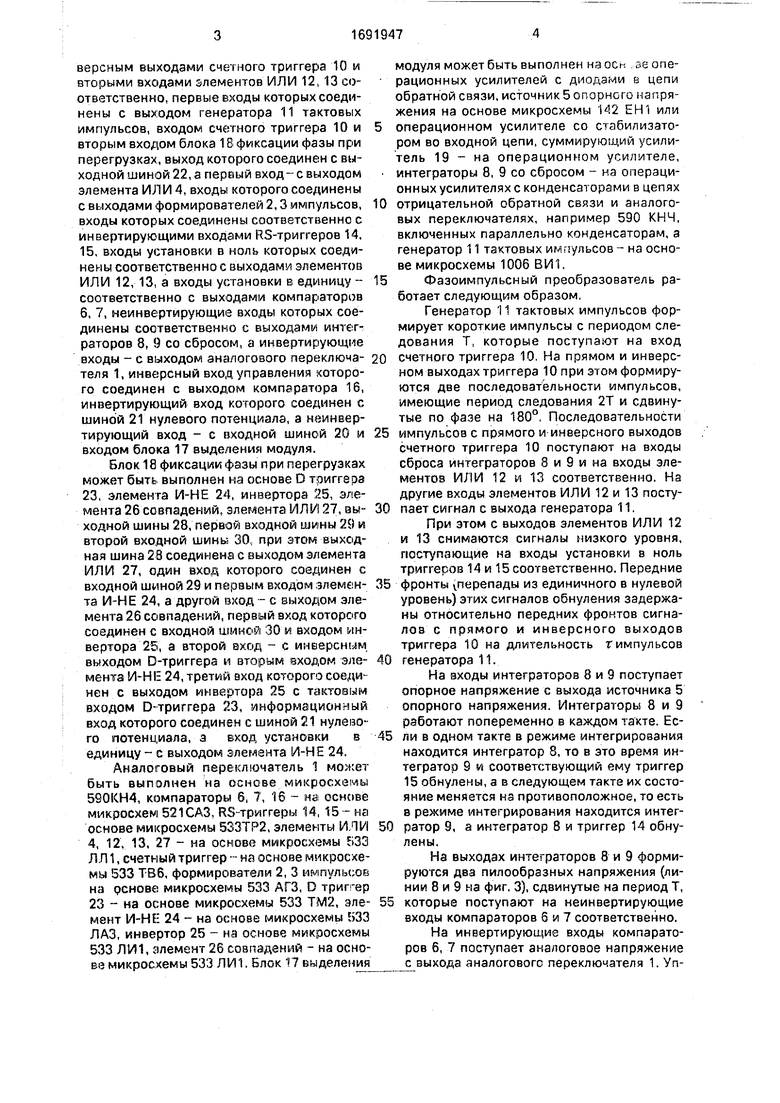

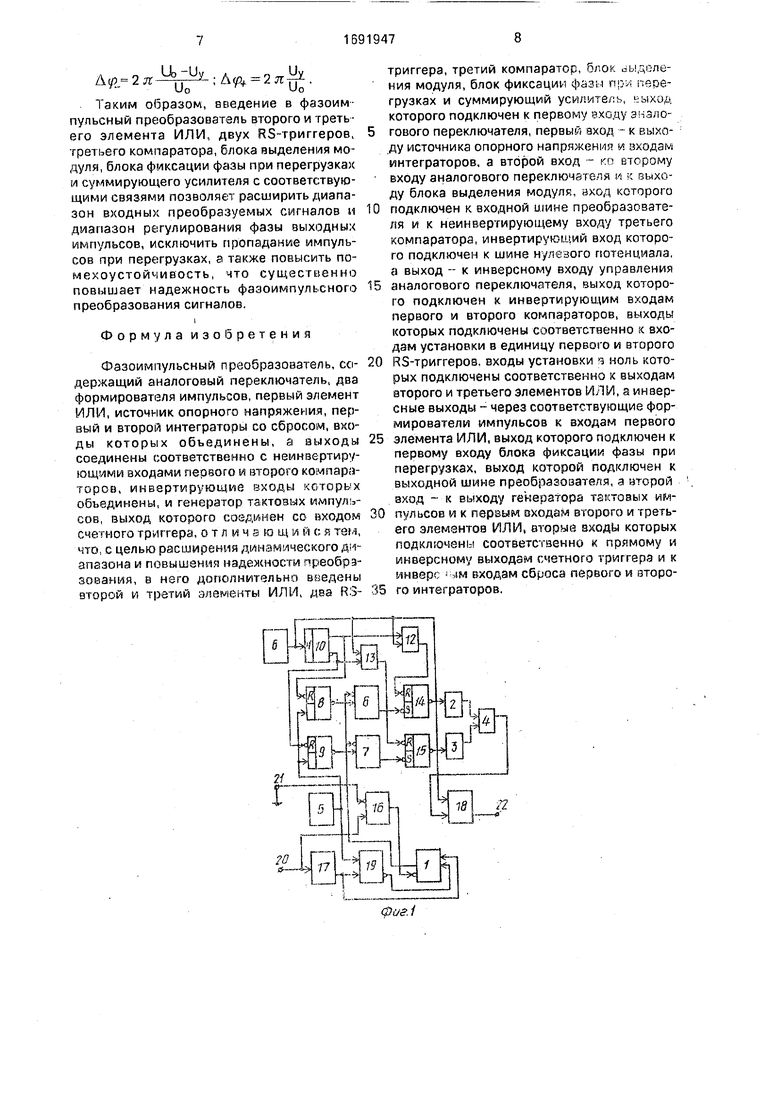

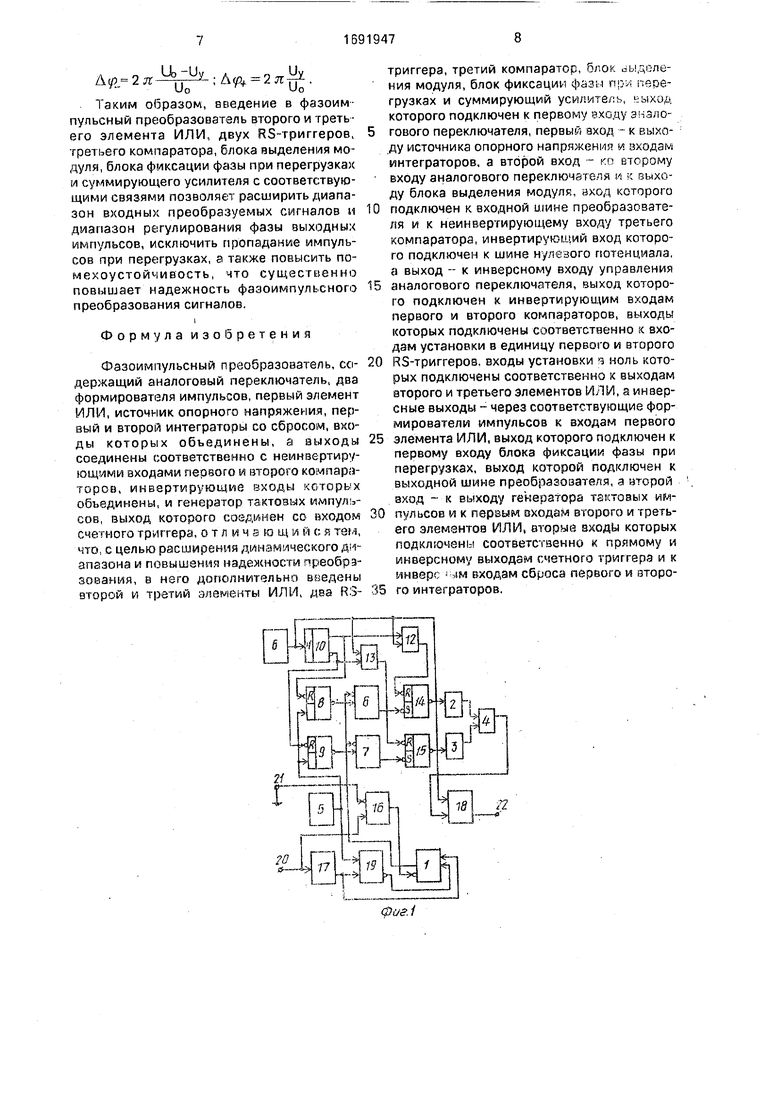

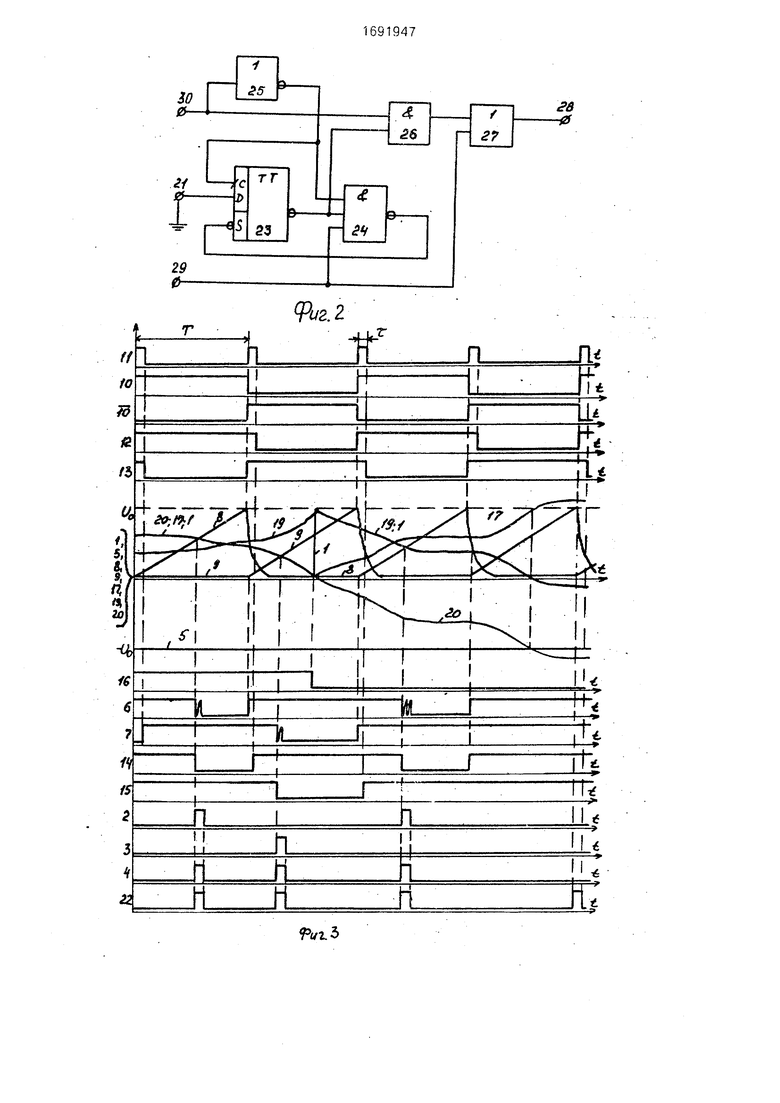

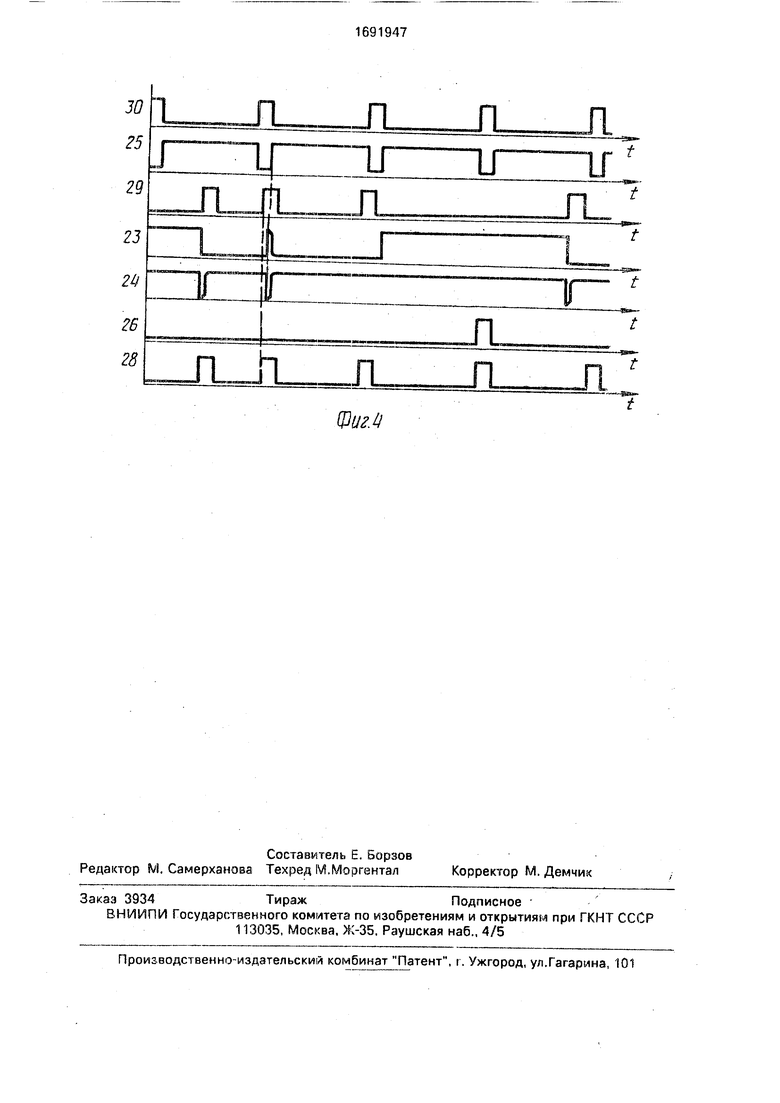

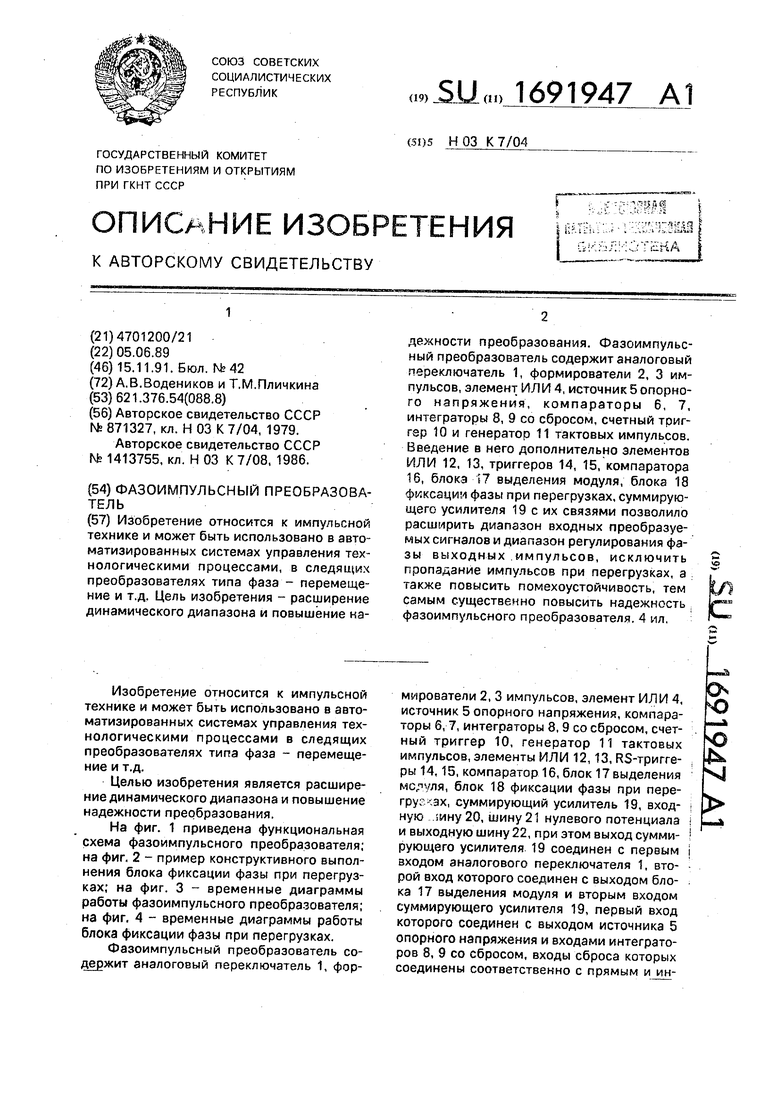

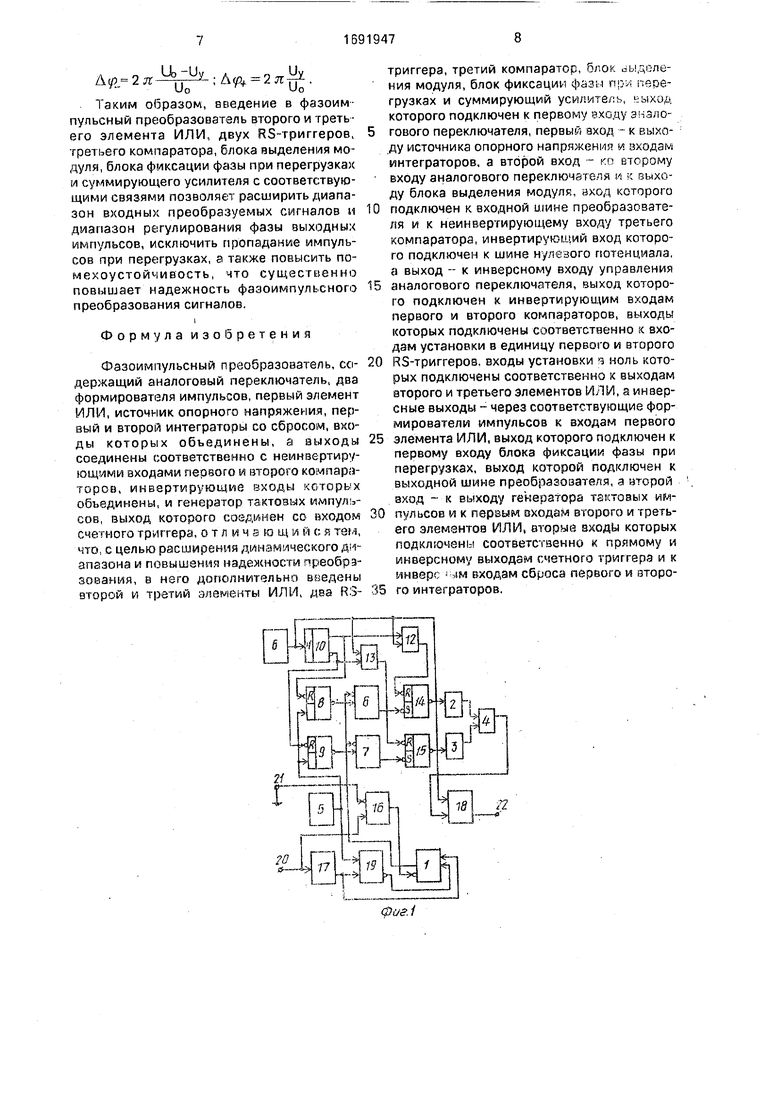

На фиг. 1 приведена функциональная схема фазоимпульсного преобразователя; на фиг. 2 - пример конструктивного выполнения блока фиксации фазы при перегрузках; на фиг. 3 - временные диаграммы работы фазоимпульсного преобразователя; на фиг. 4 - временные диаграммы работы блока фиксации фазы при перегрузках.

Фазоимпульсный преобразователь содержит аналоговый переключатель 1, формирователи 2, 3 импульсов, элемент ИЛИ 4, источник 5 опорного напряжения, компараторы 6,7, интеграторы 8, 9 со сбросом, счетный триггер 10, генератор 11 тактовых импульсов, элементы ИЛИ 12,13, RS-тригге- ры 14,15, компаратор 16, блок 17 выделения модуля, блок 18 фиксации фазы при пере- гругох, суммирующий усилитель 19, входную ину20, шину 21 нулевого потенциала и выходную шину 22, при этом выход суммирующего усилителя 19 соединен с первым входом аналогового переключателя 1, второй вход которого соединен с выходом блока 17 выделения модуля и вторым входом суммирующего усилителя 19, первый вход которого соединен с выходом источника 5 опорного напряжения и входами интеграторов 8, 9 со сбросом, входы сброса которых соединены соответственно с прямым и инО

о

6

версным выходами счетного триггера 10 и вторыми входами элементов ИЛИ 12, 13 соответственно, первые входы которых соединены с выходом генератора 11 тактовых импульсов, входом счетного триггера 10 и вторым входом блока 18 фиксации фазы при перегрузках, выход которого соединен с выходной шиной 22, а первый вход- с выходом элемента ИЛИ 4, входы которого соединены с выходами формирователей 2,3 импульсов, входы которых соединены соответственно с инвертирующими входами RS-триггеров 14, 15, входы установки в ноль которых соединены соответственно с выходами элементов ИЛИ 12, 13, а входы установки в единицу - соответственно с выходами компараторов 6, 7, неинвертирующие входы которых соединены соответственно с выходами интеграторов 8, 9 со сбросом, а инвертирующие входы - с выходом аналогового переключа- теля 1, инверсный вход управления которого соединен с выходом компаратора 16, инвертирующий вход которого соединен с шиной 21 нулевого потенциала, а неинвертирующий вход - с входной шиной 20 и входом блока 17 выделения модуля.

Блок 18 фиксации фазы при перегрузках может быть выполнен на основе D триггера 23, элемента И-НЕ 24, инвертора 25, элемента 26 совпадений, элемента ИЛИ 27, вы- ходной шины 28, первой входной шины 29 и второй входной шины 30, при этом выходная шина 28 соединена с выходом элемента ИЛИ 27, один вход которого соединен с входной шиной 29 и первым входом элемен- та И-НЕ 24, а другой вход - с выходом элемента 26 совпадений, первый вход которого соединен с входной шиной 30 и входом инвертора 25, а второй вход - с инверсным выходом D-триггера и вторым входом эле- мента И-НЕ 24, третий вход которого соединен с выходом инвертора 25 с тактовым входом D-триггера 23, информационный вход которого соединен с шиной 21 нулевого потенциала, а вход установки в единицу - с выходом элемента И-НЕ 24.

Аналоговый переключатель 1 может быть выполнен на основе микросхемы 590КН4, компараторы 6, 7, 16 - на основе микросхем 521 САЗ, RS-триггеры 14, 15- на основе микросхемы 533ТР2, элементы ИЛИ 4, 12, 13, 27 - на основе микросхемы 533 ЛЛ1, счетный триггер - на основе микросхемы 533 ТВ6, формирователи 2, 3 импульсов на основе микросхемы 533 АГЗ, D триггер 23 - на основе микросхемы 533 ТМ2, эле- мент И-НЕ 24 - на основе микросхемы 533 ЛАЗ, инвертор 25 - на основе микросхемы 533 ЛИ1, элемент 26 совпадений - на основе микросхемы 533 ЛИ1. Блок 17 выделения

модуля может быть вы полней наос« зе операционных усилителей с диодами в цепи обратной связи, источник 5 опорного напряжения на основе микросхемы 142 ЕН1 или операционном усилителе со стабилизатором во входной цепи, суммирующий усилитель 19 - на операционном усилителе, интеграторы 8, 9 со сбросом - на операционных усилителях с конденсаторами в цепях отрицательной обратной связи и аналоговых переключателях, например 590 КНЧ, включенных параллельно конденсаторам, а генератор 11 тактовых импульсов - на основе микросхемы 1006 ВИ1.

Фазоимпульсный преобразователь работает следующим образом.

Генератор 11 тактовых импульсов формирует короткие импульсы с периодом следования Т, которые поступают на вход счетного триггера 10. На прямом и инверсном выходах триггера 10 при этом формируются две последовательности импульсов, имеющие период следования 2Т и сдвинутые по фазе на 180°. Последовательности импульсов с прямого и инверсного выходов счетного триггера 10 поступают на входы сброса интеграторов 8 и 9 и на входы элементов ИЛИ 12 и 13 соответственно. На другие входы элементов ИЛИ 12 и 13 поступает сигнал с выхода генератора 11.

При этом с выходов элементов ИЛИ 12 и 13 снимаются сигналы низкого уровня, поступающие на входы установки в ноль триггеров 14 и 15 соответственно. Передние фронты (Перепады из единичного в нулевой уровень) этих сигналов обнуления задержаны относительно передних фронтов сигналов с прямого и инверсного выходов триггера 10 на длительность г импульсов генератора 11.

На входы интеграторов 8 и 9 поступает опорное напряжение с выхода источника 5 опорного напряжения. Интеграторы 8 и 9 работают попеременно в каждом такте. Если в одном такте в режиме интегрирования находится интегратор 8, то в это время интегратор 9 и соответствующий ему триггер 15 обнулены, а в следующем такте их состояние меняется на противоположное, то есть в режиме интегрирования находится интегратор 9, а интегратор 8 и триггер 14 обнулены.

На выходах интеграторов 8 и 9 формируются два пилообразных напряжения (линии 8 и 9 на фиг. 3), сдвинутые на период Т, которые поступают на неинвертирующие входы компараторов 6 и 7 соответственно.

На инвертирующие входы компараторов 6, 7 поступает аналоговое напряжение с выхода аналогового переключателя 1. Управление переключателем 1 осуществляется сигналом с компаратора 16. При положительном значении напряжения на входной шине 20 с выхода компаратора 16 на вход управления переключателя 1 поступает сигнал единичного уровня, а при отрицательном - сигнал нулевого уровня. Соответ- ственно на выход аналогового переключатели 1 в первом случае поступает сигнал с блока 17 выделения модуля, а во втором - с выхода суммирующего усилителя 19.

Как только уровень сигналов с интеграторов 8 или 9 превысит уровень сигнала с переключателя 1, то на инверсных выходах компараторов 6 или 7 соответственно появляется сигнал нулевого уровня, переключающий в единичное состояние RS-триггеры 14 или 15. Если при наличии помех компараторы 6 или 7 переключаются несколько раз в течение периода, то триггеры 14 и 15 воспринимают только первое переключение, чем предотвращается формирование нескольких импульсов в одном периоде. Формирователи 2 и 3 по перепадам из единичного в нулевой уровень на инверсных выходах RS-триггеров 14 и 15 вырабатывают импульсы с длительностью, соответствующей длительности сигналов на выходе генератора 11.

Сигналы с выходов формирователей 2 и 3, сформированные в разные периоды, объединяются на элементе ИЛИ 4 и поступают на вход блока 18 фиксации фазы при перегрузках, на другой вход которого приходит сигнал с выхода генератора 11. Блок 18 фиксации фазы служит для исключения пропадания выходного сигнала преобразователя на выходной шине 22 при перегрузках по входу (превышении значения модуля напряжения входного сигнала (UBx) на входной шине 20 значения модуля напряжения источника опорного напряжения (Uo), так как а этом случае на выходах формирователей 2 и 3 импульсы не формируются. Поэтому при перегрузках для исключения сбоя в работе блока 18 фиксации фазы пропускает на выходную шину 22 импульсы с задающего генератора 11 импульсов. Работа блока 18 фиксации фазы (фиг. 2) при перегрузках поясняется на временной диаграмме (фиг. 4) и происходит следующим образом.

Начальная установка D-триггера не требуется, так как сразу же после окончания первого импульса (с генератора 11) на входной шине 30 D-триггера 23 устанавливается в кулевое состояние, при котором на инверсном выходе устанавливается единичный уровень, поступающий на вход элемента И- НЕ 24 и на вход элемента 26 совпадений.

Нулевой уровень, поступающий на вход элемента И-НЕ 24 запрещает на время действия входного сигнала установку триггера 23 в единичное состояние. Если перегрузки по 5 входу не было, то в данный период между импульсами на входной шине 30 на шину 29 поступает импульс (с выхода элемента ИЛИ 4), который через элемент ИЛИ 27 выдается на выходную шину 28 блока, а также посту10 пает на вход элемента И-НЕ 24, на выходе которого появляется сигнал нулевого уровня, устанавливающий триггер 23 в единичное состояние. Сигнал нулевого уровня с инверсного выхода триггера 23 поступает

5 на вход элемента 26 совпадения и запрещает прохождение на его выход и на выход элемента ИЛИ 27 сигнала, приходящего с генератора 11 на входную шину 30 блока фиксации фазы.

0 Если же в каком-то периоде произошла перегрузка по входу, то в данном периоде сигнал на шине 29 не появляется, триггер 23 остается в нулевом состоянии, при котором единичный уровень с его инверсного выхода

5 разрешает прохождение сигнала, приходящего с генератора 11 на шину 30 блока, на выход элемента 26 совпадений и далее на выход элемента ИЛИ 27 и на выходную шину 28 блока фиксации фазы при перегруз0 ках.

Таким образом, при перегрузках по входу сигнал на выходной шине 22 фазоимпуль- сного преобразователя сохраняется и его работоспособность не нарушается. В нор5 мальных же условиях при изменении напряжения входного управляющего сигнала на шине 20 в диапазоне отрицательных значений от - Uo до 0 и в диапазоне положительных значений от 0 до Uo (Uo - значение

0 модуля опорного напряжения) задержка At переднего фронта выходного сигнала на шине 22 фазоимпульсного преобразователя относительно переднего фронта сигнала задающего генератора определяется соответ5 ственно по формуле

Al.,+ .TЈ.

где i - период импульсов с генератора так- 0 товых импульсов 11;

Uy - значение модуля управляющего напряжения на входной шине 20;

Uo - значение модуля опорного напряжения с выхода источника опорного напря- 5 жения.

Соответственно фаза выходного сигнала в радианах относительно опорного в указанных диапазонах определяется по формулам

Ay,-2 я: U,,Uy :Ayv 2tt.

Таким образом, введение в фазоим- пульсный преобразователь второго и третьего элемента ИЛИ, двух RS-триггеров, третьего компаратора, блока выделения модуля, блока фиксации фазы при перегрузках и суммирующего усилителя с соответствующими связями позволяет расширить диапазон входных преобразуемых сигналов и диапазон регулирования фазы выходных импульсов, исключить пропадание импульсов при перегрузках, а также повысить помехоустойчивость, что существенно повышает надежность фазоимпульсного преобразования сигналов. i

Формула изобретения

Фазоимпульсный преобразователь, содержащий аналоговый переключатель, два формирователя импульсов, первый элемент ИЛИ, источник опорного напряжения, первый и второй интеграторы со сбросом, входы которых объединены, а выходы соединены соответственно с неинвертирующими входами первого и второго компараторов, инвертирующие входы которых объединены, и генератор тактовых импульсов, выход которого соединен со входом счетного триггера, отличающийся тем, что, с целью расширения динамического диапазона и повышения надежности преобразования, в него дополнительно введены второй и третий элементы ИЛИ, два RSтриггера, третий компаратор, блок оыделе- ния модуля, блок фиксации фазы прл перегрузках и суммирующий усилитель, чыход которого подключен к первому входу зналогового переключателя, первый вход - к выходу источника опорного напряжения и входам интеграторов, а второй вход - ко второму входу аналогового переключателя и к выходу блока выделения модуля, вход которого

подключен к входной шине преобразователя и к неинвертирующему входу третьего компаратора, инвертирующий вход которого подключен к шине нулевого потенциала, а выход - к инверсному входу управления

аналогового переключателя, выход которого подключен к инвертирующим входам первого и второго компараторов, выходы которых подключены соответственно к входам установки в единицу первого и второго

RS-триггеров, входы установки в ноль которых подключены соответственно к выходам второго и третьего элементов ИЛИ, а инверсные выходы - через соответствующие формирователи импульсов к входам первого

элемента ИЛИ, выход которого подключен к первому входу блока фиксации фазы при перегрузках, выход которой подключен к выходной шине преобразователя, а второй вход - к выходу генератора тактовых импульсов и к первым входам второго и третьего элементов ИЛИ, вторые входы которых подключены соответственно к прямому и инверсному выходам счетного триггера и к инверс г JM входам сброса первого и второго интеграторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОГО СОПРОТИВЛЕНИЯ ТОЧЕК АКУПУНКТУРЫ | 1992 |

|

RU2027403C1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1986 |

|

SU1451863A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2018180C1 |

| Фазометр | 1990 |

|

SU1797076A1 |

Изобретение относится к импульсной технике и может быть использовано в автоматизированных системах управления технологическими процессами, в следящих преобразователях типа фаза - перемещение и т.д. Цель изобретения - расширение динамического диапазона и повышение надежности преобразования. Фазоимпульсный преобразователь содержит аналоговый переключатель 1, формирователи 2, 3 импульсов, элемент ИЛ И 4, источник 5 опорного напряжения, компараторы 6. 7, интеграторы 8, 9 со сбросом, счетный триггер 10 и генератор 11 тактовых импульсов. Введение в него дополнительно элементов ИЛИ 12, 13, триггеров 14, 15, компаратора 16, блока 17 выделения модуля, блока 18 фиксации фазы при перегрузках, суммирующего усилителя 19 с их связями позволило расширить диапазон входных преобразуемых сигналов и диапазон регулирования фа- зы выходных импульсов, исключить пропадание импульсов при перегрузках, а также повысить помехоустойчивость, тем самым существенно повысить надежность фазоимпульсного преобразователя. 4 ил.

фиг. 2

22

Vz.3

| Фазоимпульсной модулятор | 1979 |

|

SU871327A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 1413755, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-15—Публикация

1989-06-05—Подача