Изобретение относится к накоплению информации.

Известно устройство, состоящее из генератора внешних сигналов и говорящей куклы, содержащей центральный процессорный блок и синтезатор речи, который включает в себя цифроаналоговый преобразователь сигналов, с которым связан портативный динамик для воспроизведений сообщений в речевой форме, запоминающее устройство для хранения речевых сообщений в цифровой форме, радиоприемник, связанный с процессорным блоком, и воспринимающий командные сигналы на выборку из ЗУ требуемого речевого сообщения от генератора внешних сигналов [1].

Недостатком является необходимость управления выбором речевых сообщений, что снижает занимательность, и отсутствие возможности оперативной записи в память речевых сообщений.

Известно устройство для цифровой записи - воспроизведения речевой информации, выбираемое за прототип, содержащее блок ЗУ, элемент И, два АЦП, формирователь управляющего импульса, адресный счетчик, дешифратор, счетчик времени интервала, шину тактового сигнала, адресный мультиплексор, три элемента ИЛИ, триггер записи, коммутатор [2].

Недостатком является то, что функционирование устройства требует большого объема памяти, что приводит к ограничению области использования по массе габаритным показателям.

Цель изобретения - упрощение устройства и повышение его занимательности.

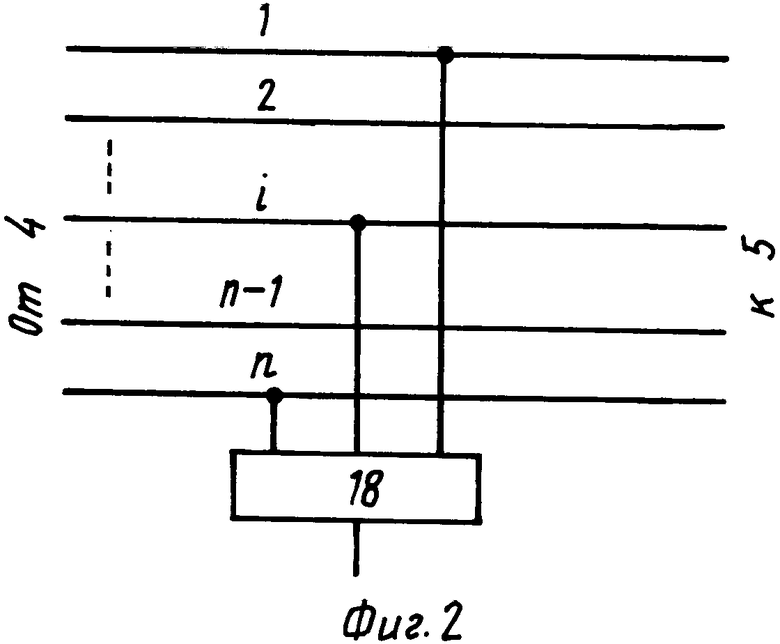

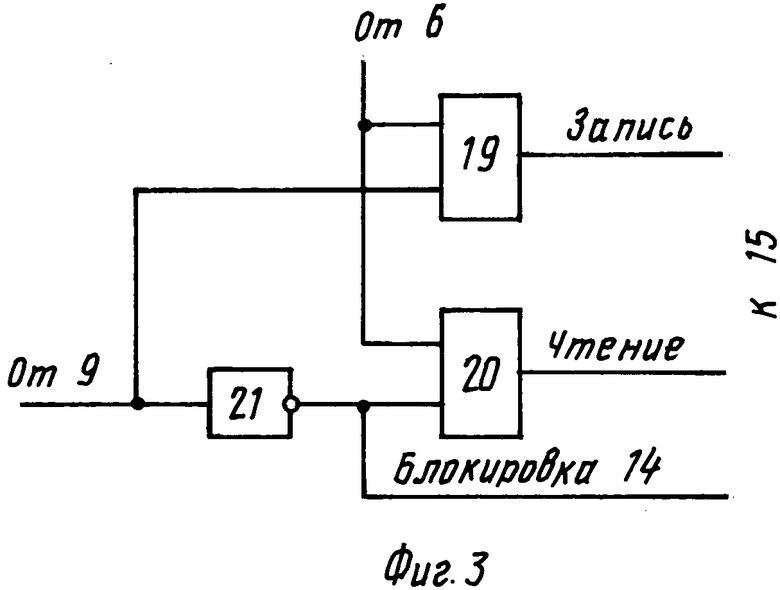

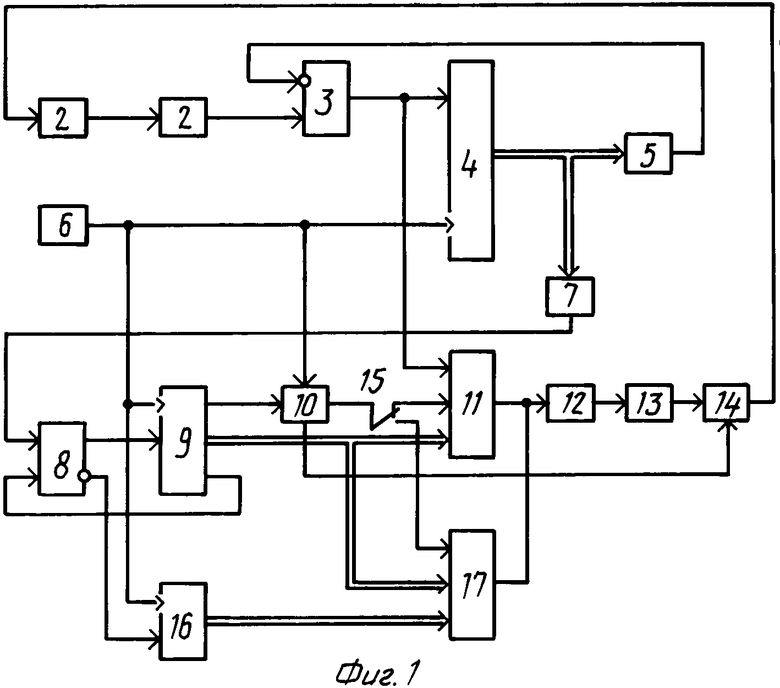

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - пороговая схема; на фиг.3 - схема управления памятью.

Устройство содержит звуковой преобразователь 1, усилитель 2 записи, компаратор 3, реверсивный счетчик 4, цифроаналоговый преобразователь 5, генератор 6, пороговую схему 7, триггер 8, первый счетчик 9 адреса, схему 10 управления памятью, первый блок 11 дискретной памяти, интегратор 12, фильтр 13 нижних частот, усилитель 14 воспроизведения, переключатель 15 режима, второй счетчик 16 адреса и второй блок 17 дискретной памяти.

Схема 7 выполнена на многовходовом элементе И 18.

Схема 10 содержит элементы И 19 и 20 и инвертор 21.

Устройство работает следующим образом.

В первом режиме производится периодическая запись и воспроизведение речевой информации из блока 11 памяти, во втором режиме устройством производится только воспроизведение речевой информации из блока 17 памяти. В процессе работы в первом режиме устройство последовательно находится в следующих состояниях: ожидания, записи и воспроизведения.

Акустический речевой сигнал преобразуется преобразователем 1 в электрический, усиливается усилителем 2 записи и поступает на прямой вход компаратора 3, если напряжение этого сигнала больше по величине напряжения на инверсном входе компаратора, то на выходе последнего устанавливается сигнал высокого уровня и импульсы, поступающие с генератора 6 на вход реверсивного счетчика 4, суммируются в нем, напряжение на выходе цифроаналогового преобразователя 5 увеличивается, в противном случае на выходе компаратора устанавливается сигнал низкого уровня, счетчик 4 работает на вычитание, а напряжение на выходе преобразователя 5 уменьшается. Таким образом, устройство стремится к компенсации входного сигнала, отслеживая его изменения. До тех пор, пока уровень входного сигнала с звукового преобразователя 1 не превышает порогового значения, устройство находится в ожидании.

При повышении уровня входного сигнала пороговая схема 7 вырабатывает импульс, изменяющий состояние триггера 8, с выхода которого поступает разрешение на первый счетчик 9 адреса, устройство переходит в состояние записи. Усилитель 14 воспроизведения при записи блокируется сигналом со схемы 10 управления. Под воздействием пульсов с генератора первый счетчик адреса производит последовательный перебор адресов блока 11 памяти, схема 10 формирует сигнал записи и в память записываются характеристики импульсов с выхода компаратора. Длительность этих импульсов, величина пауз между ними и их частота следования содержит информацию о амплитуде и частоте входного речевого сигнала. Запись продолжается до тех пор, пока счетчик 9 адреса не заканчивает перебор всех адресов адресного пространства блока 11 памяти, после чего устройство переходит в состояние воспроизведения.

Схема 10 формирует сигналы чтения, счетчик 9 производит последовательный перебор адресов, дискретные сигналы с выхода первого блока памяти с помощью интегратора 12 и фильтра 13 нижних частот восстанавливаются в исходный аналоговый сигнал, который через усилитель 14 воспроизведения поступает на звуковой преобразователь 1, который преобразует его в акустический речевой сигнал.

После перебора всех адресов импульс со старшего разряда первого счетчика адреса переключает триггер 8, который блокирует первый счетчик адреса и переводит устройство в состояние ожидания. Устройство ждет речевой сигнал, при поступлении которого весь цикл работы повторяется.

Перевод работы устройства во второй режим производится переключателем 15, в этом случае сигналы со схемы 10 управления подаются на блок 17 памяти, а не на блок 11 памяти.

В начале устройство находится в состоянии ожидания. Разрешение с инверсного выхода триггера 8 поступает на второй счетчик 15 адреса, который производит перебор старших адресов блока 17 памяти под воздействием импульсов с выхода генератора 5, работа остальной части устройства в состоянии ожидания описана выше. Как и в первом режиме устройство ждет выходной сигнал, уровень которого выше порогового значения, при поступлении такого сигнала счетчик 16 блокируется, а на счетчик 9 поступает разрешение. Устройство переходит в состояние паузы.

В состоянии паузы первый счетчик адреса производит перебор адресов, но в отличии от первого режима запись информации не производится, так как блок 17 памяти не имеет информационного входа и не воспринимает сигналы записи со схемы 10 управления. Пауза длится до тех пор, пока счетчик 9 адреса не заканчивает перебор всех адресов, после чего устройство переходит в состояние воспроизведения.

В блоке 17 памяти речевая информация записана фразами, выбор той или иной фразы определяется старшими разрядами адреса, т.е. состоянием счетчика 16. Так как поступление входного сигнала не синхронизировано с работой второго счетчика адреса, то выбор фразы происходит случайным образом. При воспроизведении схема 10 формирует сигналы чтения, счетчик 9 производит последовательный перебор адресов, дискретные сигналы с выхода второго блока памяти с помощью интегратора 12 и фильтра 13 нижних частот восстанавливаются в исходный аналоговый сигнал, который через усилитель 14 воспроизведения поступает на звуковой преобразователь 1, который преобразует его в акустический речевой сигнал, устройство воспроизводит одну из фраз.

После перебора всех адресов импульс со старшего разряда первого счетчика адреса переключает триггер 8, который блокирует первый счетчик адреса, разрешает счет второму счетчику адреса и переводит устройство в состояние ожидания. Устройство ждет речевой сигнал, при поступлении которого весь цикл работы повторяется.

Схема 7, например, может быть реализована на элементе И 18, входы которого подключены к выходам реверсивного счетчика таким образом, что число К, появление кода которого на выходах реверсивного счетчика вызывает установление на выходе элемента И уровня логической единицы, выбрано больше некоего числа М, код которого соответствует пороговому уровню входного речевого сигнала.

Схема 10 управления памятью может быть реализована на двух элементах И 19 и 20 и инверторе 21. Первые входы элементов И подключены к выходу генератора, а вторые входы - к выходу первого счетчика адреса, причем подключение входа элемента И 20 произведено через инвертор 21, с выхода которого также снимается сигнал блокировки усилителя воспроизведения. Выход первого счетчика адреса для подключения схемы управления памятью соответствует разряду А, который выбран таким, что (А-1)-разряды полностью перекрывают адресную сетку первого блока дискретной памяти.

Уменьшение аппаратных затрат в устройстве достигается тем, что звуковой преобразователь выполняет две функции как микрофона, так и динамика, при этом при записи для уменьшения помех блокируется усилитель 14 воспроизведения, кроме того, преобразование сигнала из аналоговой формы в цифровую при записи и из цифровой в аналоговую при воспроизведении производится с помощью построенного на компараторе 3 реверсивном счетчике 14, цифроаналоговом преобразователе 5 и интеграторе 12, дельта-модулятора-демодулятора, который обеспечивает сокращение объема памяти при записи речевого сообщения, так как записывается не абсолютное значение цифрового представления амплитуды сигнала, а относительное (приращение), причем при каждом отсчете записывается только один бит, имеющий единичное логическое значение, если сигнал в данном отсчете увеличивается по отношению к предыдущему отсчету, или имеющий нулевое значение, если сигнал уменьшается.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Устройство для индикации однократных сигналов | 1984 |

|

SU1275519A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| УСТРОЙСТВО ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКА | 1992 |

|

RU2036519C1 |

| Устройство для магнитной записи-воспроизведения звуковых сигналов | 1989 |

|

SU1712957A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для охранной сигнализации | 1990 |

|

SU1783561A1 |

| Устройство для формирования речевых сообщений | 1979 |

|

SU942118A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

Изобретение относится к накопителю информации. Сущность изобретения: с целью упрощения устройства и повышения его занимательности в устройство, содержащее звуковой преобразователь 1, усилитель 2 записи, компаратор 3, реверсивный счетчик 4, цифроаналоговый преобразователь 5, генератор 6, схему 10 управления памятью, первый блок 11 дискретной памяти, интегратор 12, фильтр 13 нижних частот, усилитель 14 воспроизведения, введены переключатель 15 режима, второй счетчик 16 адреса, второй блок 17 дискретной памяти с соответствующей совокупностью связей. 3 ил.

УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ, содержащее звуковой преобразователь, усилитель записи, компаратор, реверсивный счетчик, цифроаналоговый преобразователь, генератор, пороговую схему, триггер, первый счетчик адреса, схему управления памятью, первый блок дискретной памяти, интегратор, фильтр нижних частот и усилитель воспроизведения, выход которого подключен к звуковому преобразователю, сигнальный вход - к выходу фильтра нижних частот, а разрешающий вход - к второму выходу схемы управления памятью, первый вход которой подсоединен к генератору, а второй вход - к первому выходу первого счетчика адреса, счетный вход которого подсоединен к генератору, а вход разрешения - к прямому выходу триггера, вход установки нуля которого связан с выходом пороговой схемы, вход которой, также как и вход цифроаналогового преобразователя, связан с выходом реверсивного счетчика, счетный вход которого подключен к генератору, а вход направления счета подсоединен, так же как и информационный вход первого блока дискретной памяти, к выходу компаратора, инверсный вход которого связан с выходом цифроаналогового преобразователя, а прямой вход - с выходом усилителя записи, вход которого подключен к выходу звукового преобразователя, причем вход установки нуля триггера подключен к третьему выходу первого счетчика адреса, а второй выход связан с адресным входом первого блока дискретной памяти, отличающееся тем, что в него введены переключатель режима, второй счетчик адреса и второй блок дискретной памяти, причем вход переключателя режима подключен к первому выходу схемы управления памятью, первый выход - к управляющему входу первого блока дискретной памяти, а второй выход - к управляющему входу второго блока дискретной памяти, вход младших разрядов адреса которого, так же как и адресный вход первого блока памяти, связан с вторым выходом первого счетчика адреса, причем вход старших разрядов адреса второго блока дискретной памяти связан с выходом второго счетчика адреса, счетный вход которого подключен к генератору , а вход разрешения к инверсному выходу триггера, выходы первого и второго блоков дискретной памяти подключены к входу интегратора, выход которого связан с входом фильтра нижних частот.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1985 |

|

SU1272355A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1994-08-15—Публикация

1992-07-24—Подача