Изобретение относится к вычисли- ельния технике и может быть исполь йовано при построении устройства для Отображения графической информации.

Цель изобретения - расширение области применения генератора за счет увеличения числа воспроизводимых форматов символов.

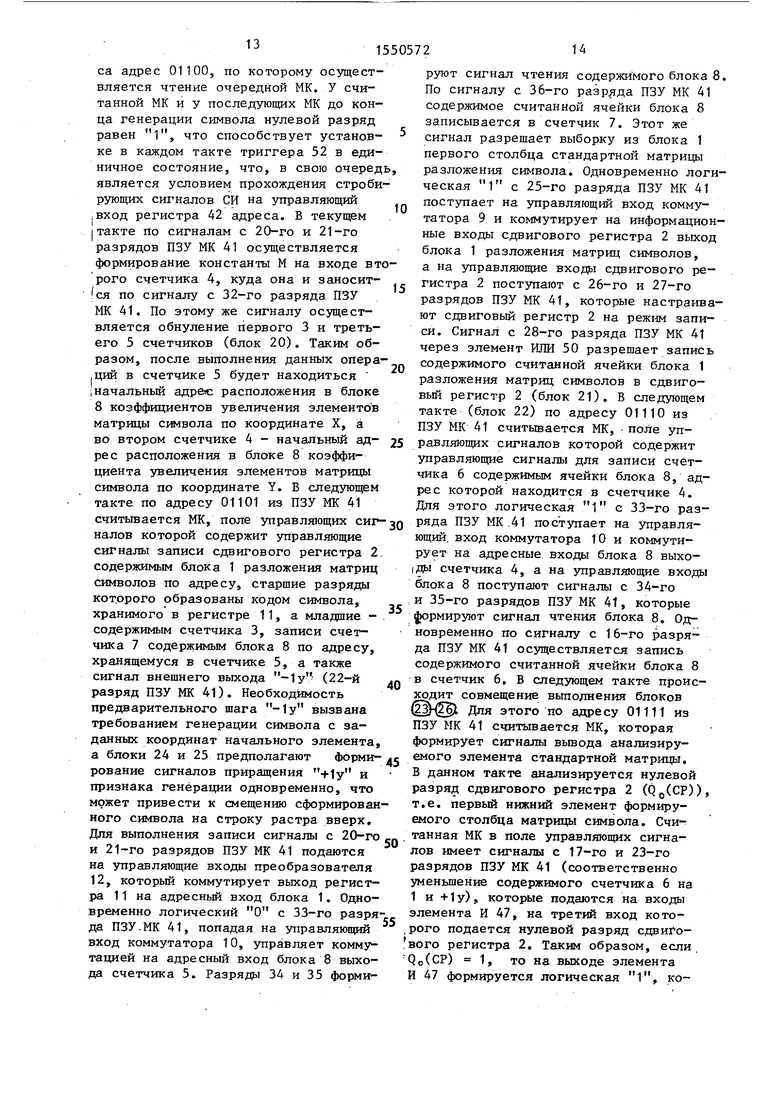

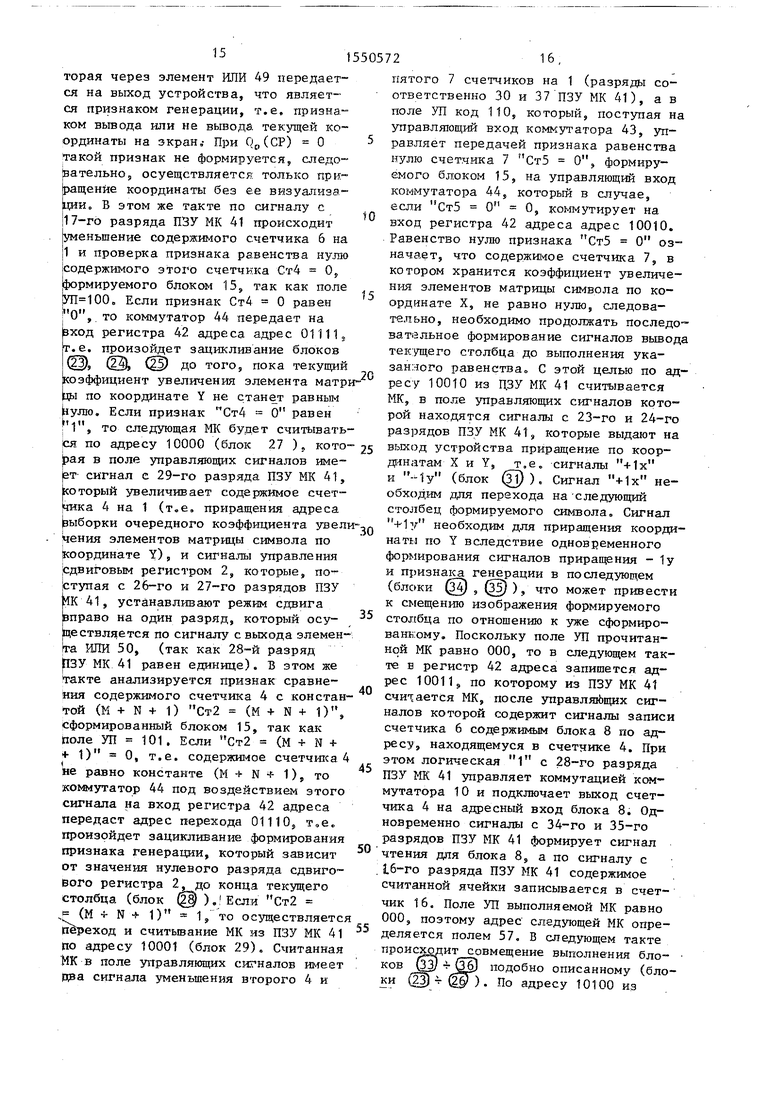

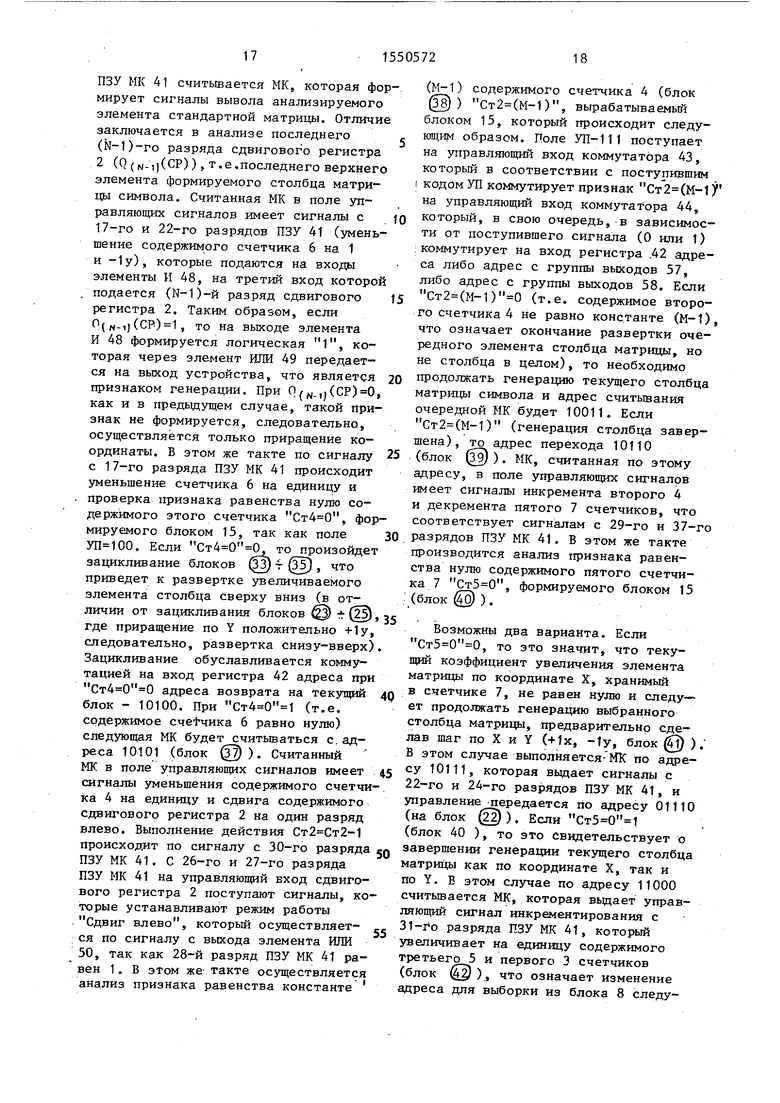

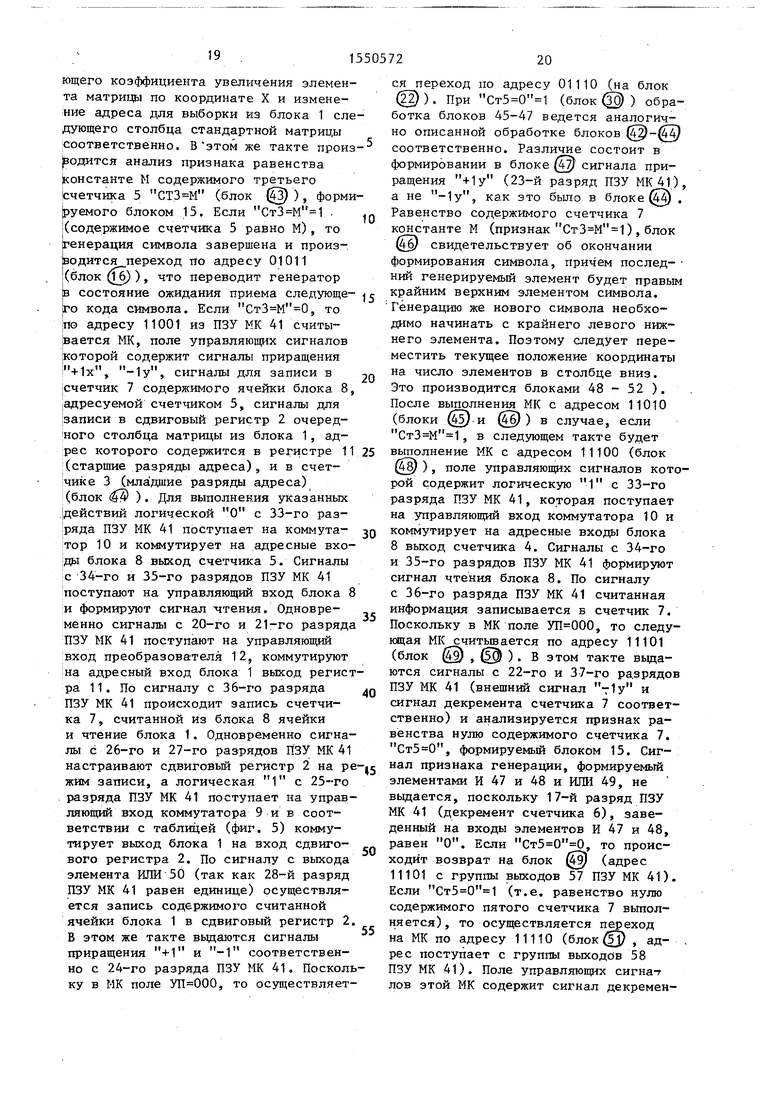

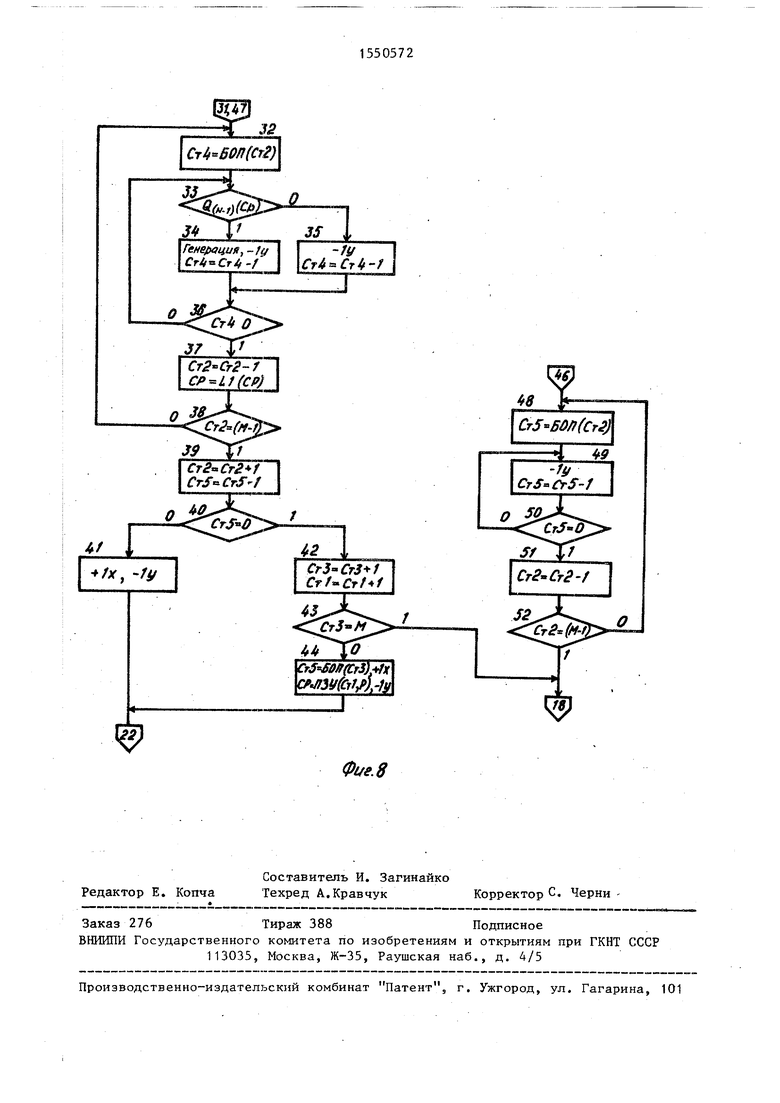

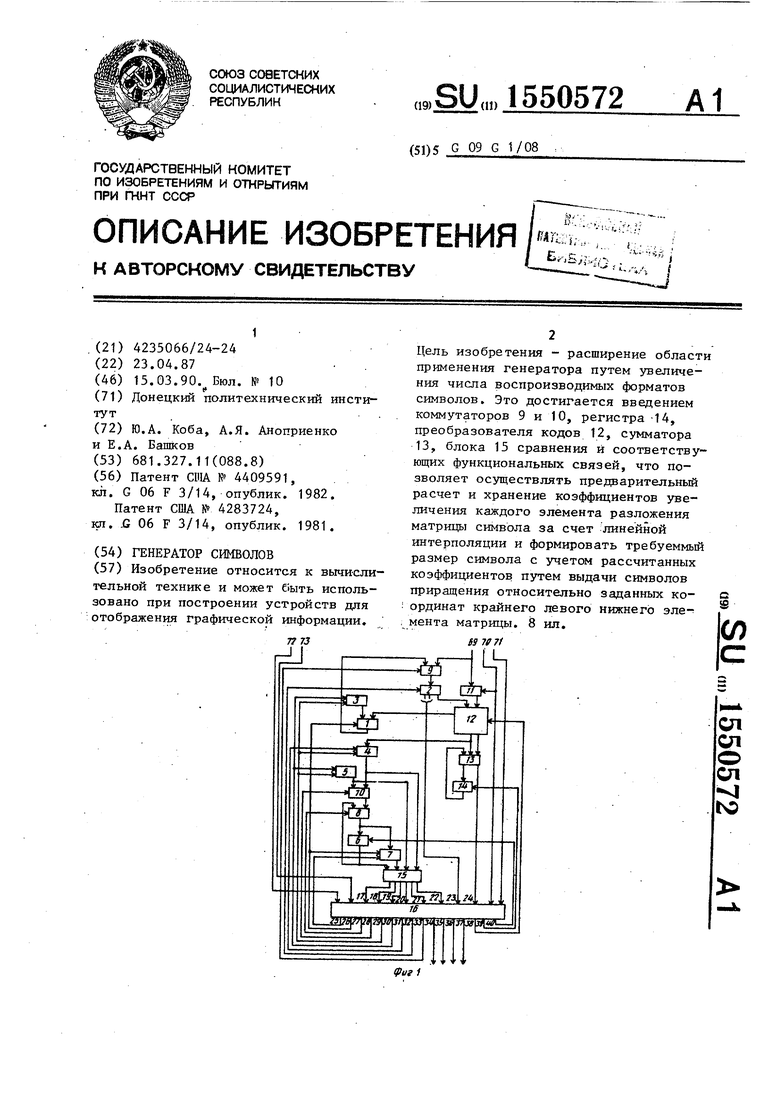

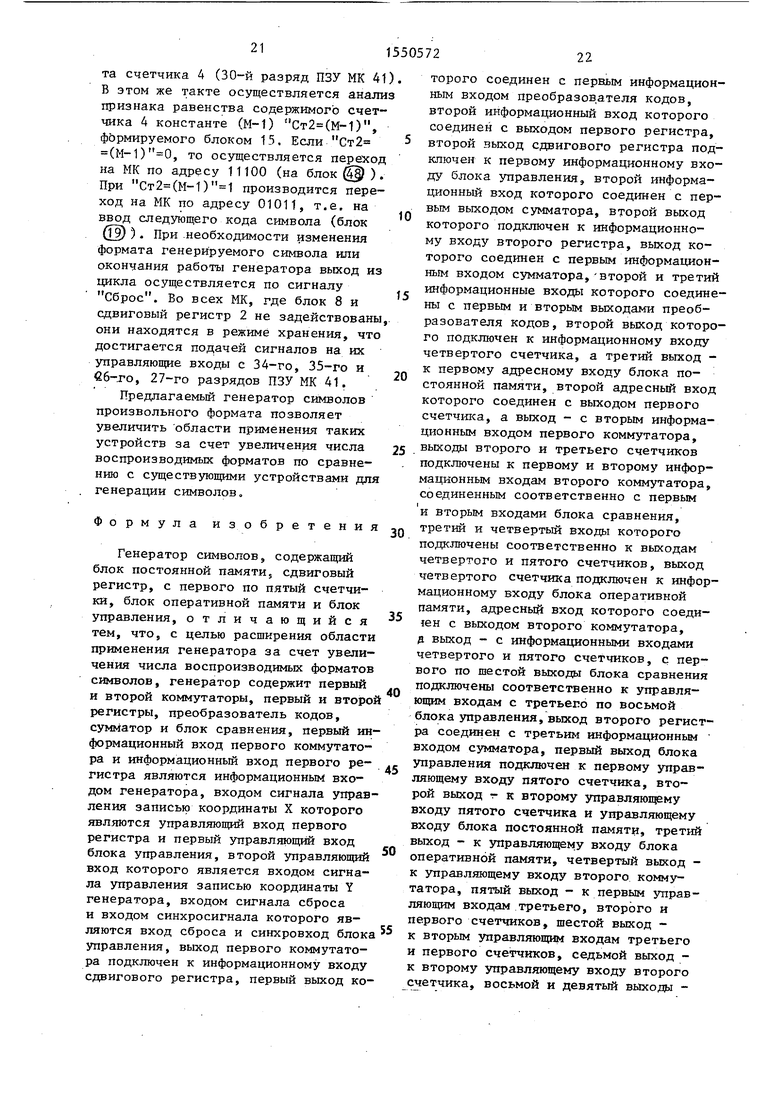

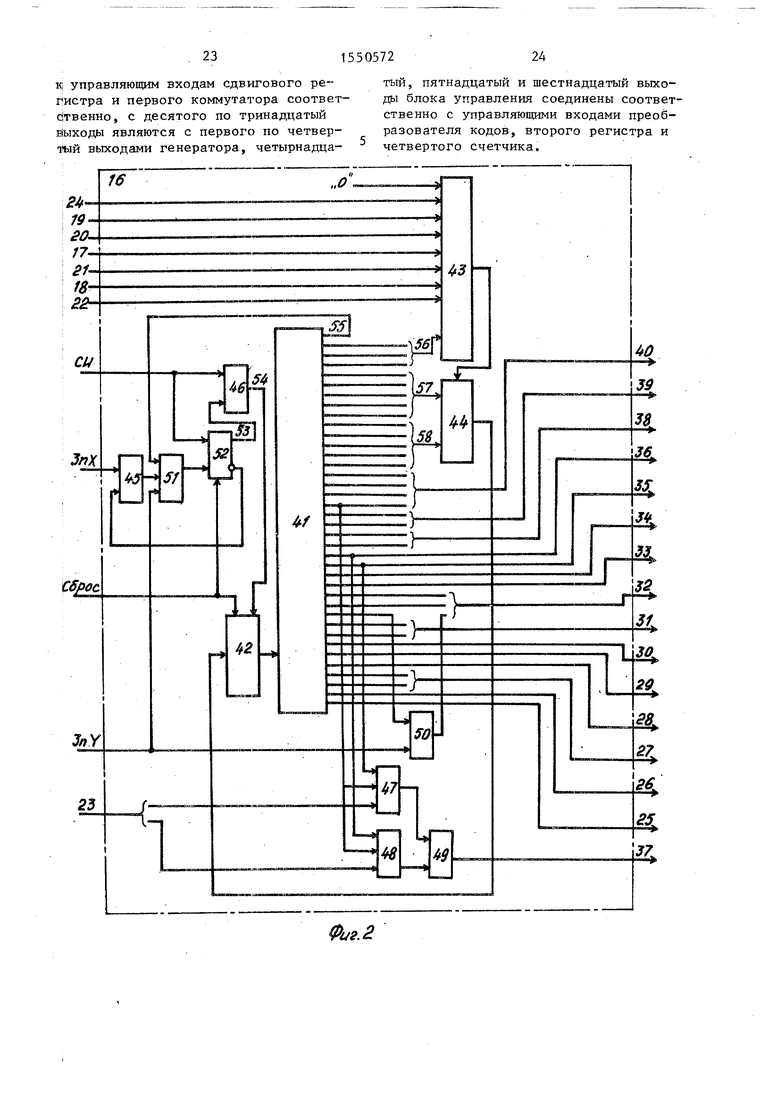

На фиг. 1 представлена структурная схема генератора| на фиг„ 2 - структурная схема блока управления; ia фиг. 3 - структурная схема преобразователя кодовj на фиг, 4 - структурная схема блока сравнения на фиг. 5 - таблица прожига ПЗУ микрокоманд блока управления| на фиг. 6-8- кикропрограмма работы устройства.

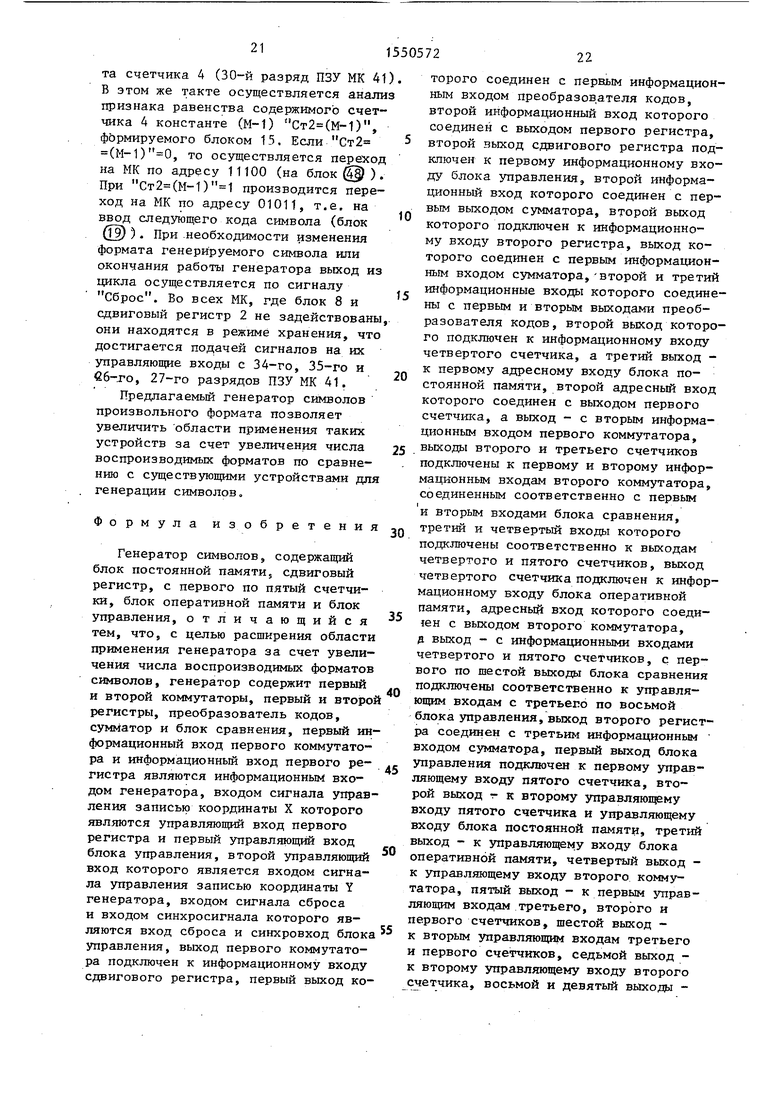

Генератор символов содержит блок постоянной памяти (разложения матриц символов), сдвиговый регистр 2, первый 3, второй 4, третий 5, четвер- Авй 6 и пятый 7 счетчики, блок 8 оперативной памяти (параметры генериру- символа),, первый 9 и второй 10 коммутаторы, первый регистр 11, преоб- р|азователь 12 кодов, сумматор 13, вто- р|ой регистр 14, блок 15 сравнения, блок 16 управления.

Позициями 17-24 обозначены соот- &|етствующие входы, а 25-40 - соответствующие выходы блока 16 управления.

Блок 16 управления содержит ПЗУ 41 м икрокоманд, регистр 42 адреса, ком- м(утаторы 43 и 44, элементы И 45-48, элементы ИЛИ 49-51, триггер 52.

Позициями 53-58 обозначены соот- в тствующие входы и выходы в блоке 16,

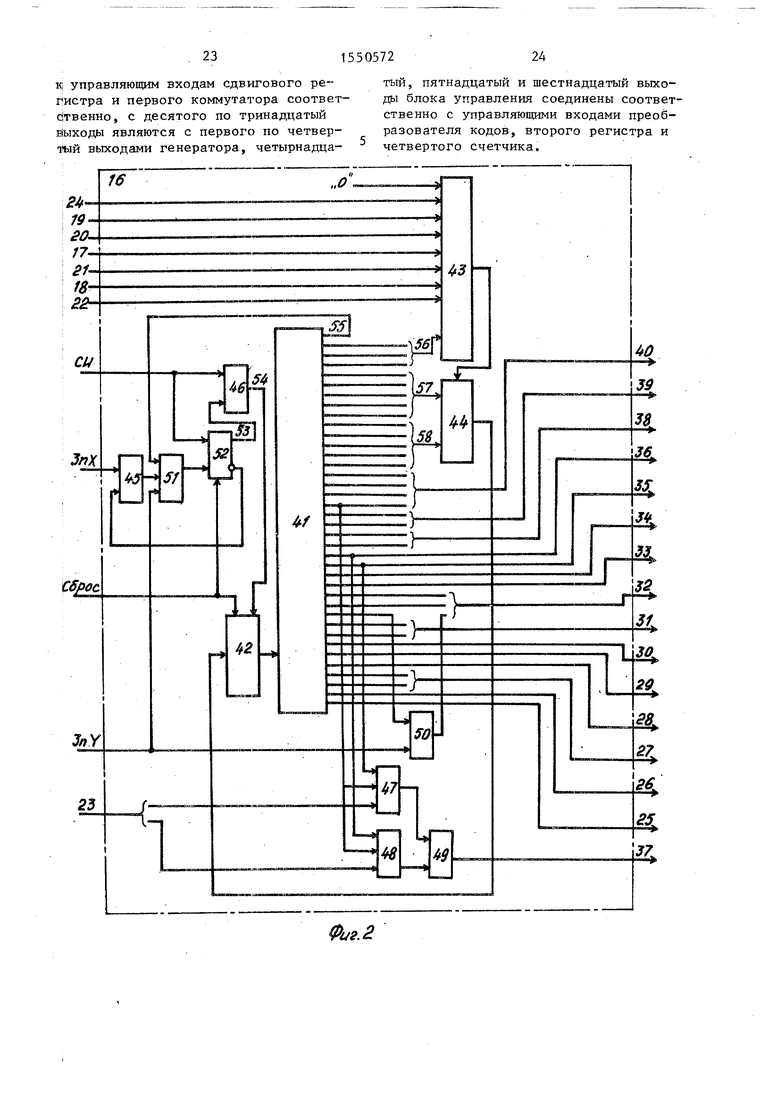

Преобразователь 12 кодов содержит фЬрмирователь 59 константы М, формирователь 60 константы N, коммутатор 61, формирователь 62 обратного кода, Позициями 63 и 64 обозначены входы кЬммутатора 61.

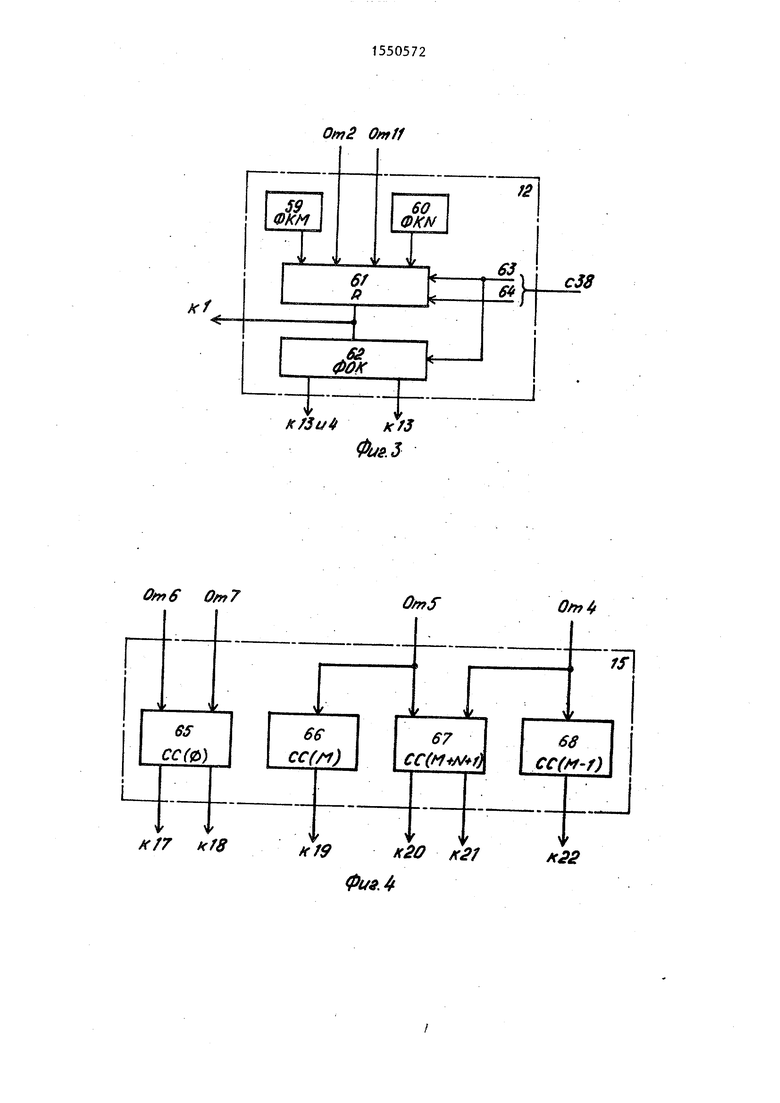

Блок 15 соавнения содержит узел 65 сравнения с нулем, узел 66 сравнения с константой М, узел 67 сравнения с константой (М + N + 1) я узел 68 сравнения с константой (М-1).

Блок 1 постоянной памяти предназначен для хранения битового разложения матриц всех генерируемых символов с возможностью считывания при подаче соответствующего адреса и управляющего сигнала.

Сдвиговый регистр 2 служит для приема и хранения размера символа в единицах растра по вертикали, а т.&кже приема, хранения и сдвига впра

5

0

5

0

5

0

5

0

5

во-влево считанной информации из блока 1. Все действия выполняются по сигналу, формируемому элементом ИЛИ 50.

Первый счетчик 3 представляет собой счетчик по модулю М и предназначен для формирования младших разрядов адреса блока 1 разложения матриц символов,

Второй 4 и третий 5 счетчики служат для формирования адреса считывания-записи блока 8 оперативной памяти.

Четвертый 6 и пятый 7 счетчики являются вычитающими и предназначены для приема из блока 8 оперативной памяти масштабного коэффициента по координате Y и X соответственно и его последовательного уменьшения на единицу.

Блок 8 оперативной памяти служит для приема и хранения масштабных коэффициентов каждого элемента матрицы разложения по координатам X и Y. Емкость его составляет (М + N) ячеек памяти.

Позициями 69-73 обозначены соответственно информационный вход, входы сигналов управления записью координат X и Y, вход сигнала сброса и вход синхросигнала генератора.

Коммутатор 9 предназначен для коммутации на сдвиговый регистр 2 информации, поступающей либо с входа 69, либо с выхода блока 1 под действием управляющего сигнала с выхода 33. блока 1 6.

Коммутатор 10 служит для1 коммутации -адреса считывания-записи блока 8 оперативной памяти, поступающего либо с выхода счетчика 4, либо с выхода счетчика 5 под действием управляющего сигнала с выхода 28 блока 16 управления.

Регистр 11 осуществляет прием и хранение размера символа в единицах растра по горизонтали, а также прием и хранение кода генерируемого символа, который служит в качестве старших разрядов адреса блока 1 разложения матриц символов.

Преобразователь 12 кодов предназначен для формирования коснтант М и N, коммутации коммутатором 61 под действием управляющих сигналов с блока 16 управления информации с четырех направлений на одно со сдвигово-

го регистра 2, регистра 11, формирователей 59 и 60 констант М и N, а также получения обратного кода числа и возникающего переноса с помощью формирователя 62 обратного кода под действием управляющего сигнала с входа 63.

Сумматор 13 служит для суммирования информации, поступающей с преобразователя 12 и регистра 14 с учетом переноса.

Регистр 14 осуществляет запись и хранение результата суммирования, поступающего с сумматора 13.

Блок 15 сравнения предназначен для формирования признаков выполнения операций, которые анализируются в блоке 16 управления, причем узел 65 сравнения с нулем вырабатывает признаки и . узел 66 сравнения с константой М - признак , узел 67 сравнения с констанВ исходное состояние генератор устанавливается по входу 72 сигналом Сброс. При этом обнуляется триггер 15 52 и регистр 42 адреса микрокоманд (МК), что приводит к установлению логического О на управляющем входе регистра 42 М и считыванию с нулевой ячейки ПЗУ МК 41 первого слова МК (фиг. 5). Поскольку нулевой разряд МК равен нулю, , , то на информационном входе триггера 52 элементом ИЛИ 51 формируется логический О, который будет записываться по переднему фронту сигнала СИ в каждом последующем такте, что приведет к удержанию логического О на управляющем входе регистра 42 адреса до прихода сигналов ЗпХ, 3nY по вхо25

той (М + N + 1) формирует признаки СтЗ(М + NM- I) и Ст2(М + N+ 1), а узел 68 сравнения с константой (М-1) - признак Ст2(М-1). В блоке 15 вырабатывается сигнал в результате суммирования поступающей информации на сумматоре 13 и является знаком 30 Дам 70 и 71. С инверсного выхода этой суммы Зн5 .триггера 52 логическая 1 подается

на вход элемента И 45, разрешая передачу сигнала ЗпХ на вход элемента ИЛИ 51. Таким образом, генератор перейдет в состояние ожидания прихода внешних сигналов ЗпХ, 3nY. Коммутатор 43 подключает на свой выход один из восьми информационных сигналов

35

Блок 16 управления необходим для управления работой генератора путем выдачи управляющих сигналов с учетом анализа сформированных признаков.

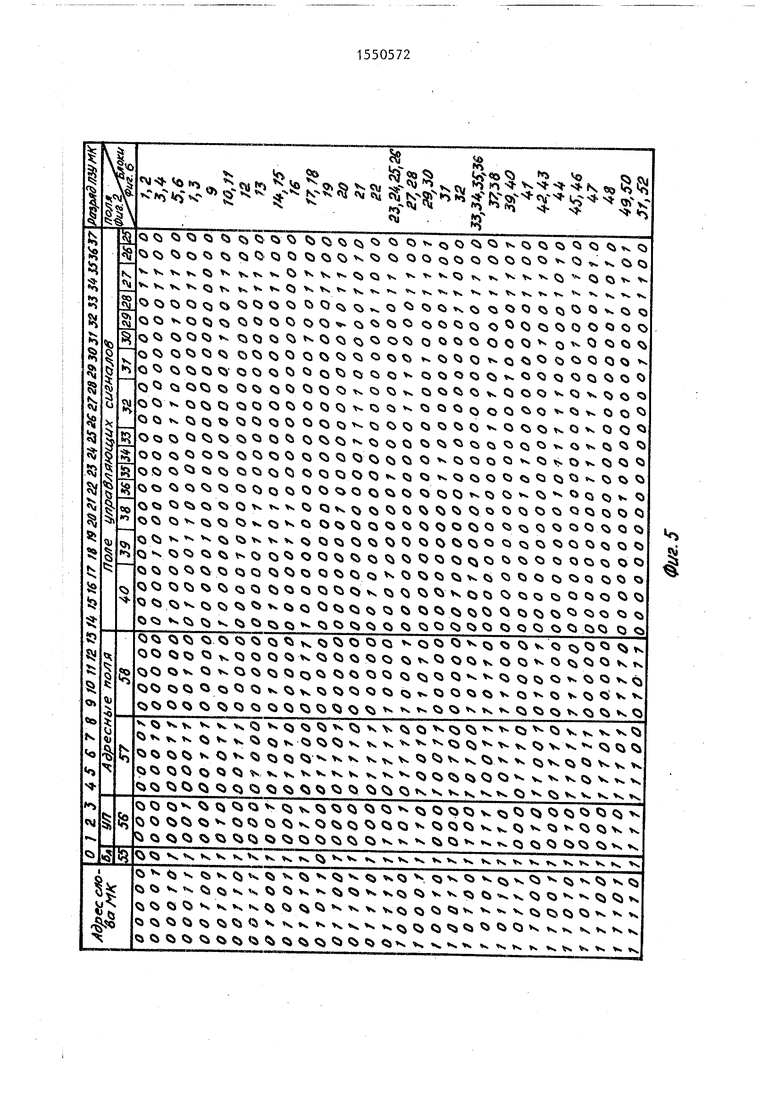

Таблица прожига ПЗУ МК 41 представлена на фиг. 5.

Устройство работает следующим образом.

В основу процесса определения ко- 40 эффициентов увеличения каждого элемента разложения матрицы символа по координате X положена линейная интерполяция диагонали прямоугольника со сторонами по горизонтали и вертикали 45 Соответственно ДХ и М, где ЛХ - размер поля генерируемого символа; М - размер стандартной матрицы этого символа, хранимый в блоке 1, по горизонтали в единицах растра. Опреде- 50 ление коэффициентов увеличения каждого элемента разложения матрицы символа по координате Y производится аналогично, но для диагонали прямоугольника со стороны соответственно 55 N и ДУ, где N - размер стандартной матрицы, хранимой в блоке 1; ДУ - размер поля генерируемого символа по вертикали в единицах растра. Под

О, 24, 19, 20, 17, 21, 18, 22 в зависимости от управляющего поля (УП) МК (разряды - 1-3 ПЗУ МК 41, фиг. 5). Поскольку в нулевой ячейке ПЗУ МК 41-УП-ООО, то коммутатор 43 выдает на свой выход логический О. Коммутатор 44 под действием этого сигнала подключит на свои выходы адресное поле (входы) 57, т.е. адрес следующей МК 00001, который будет удерживаться на входе регистра 42 адреса до прихода переднего фронта сигнала с выхода 54 элемента И 46.

Установка размера поля генерируемого символа осуществляется следу- ющим образом (фиг. 6, блок 2). По приходу сигнала ЗпХ, который как и 3nY может быть асинхронным по отношению с СИ, на информационном вхо- |Де триггера 52 через элементы И 45 и ИЛИ 51 устанавливается логическая

0

полем генерируемого символа понимается прямоугольная область экрана с размерами сторон dX, ДУ, в которую необходимо вписать символ. Очередной шаг интерполяции выбирается при анализе знака оценочной функции F: если на i-м шаге F; О, то делается шаг по X и F ;4, F - Y; если F; О, то шаг по Y и F .+1 FJ + /JX.

В исходное состояние генератор устанавливается по входу 72 сигналом Сброс. При этом обнуляется триггер 5 52 и регистр 42 адреса микрокоманд (МК), что приводит к установлению логического О на управляющем входе регистра 42 М и считыванию с нулевой ячейки ПЗУ МК 41 первого слова МК (фиг. 5). Поскольку нулевой разряд МК равен нулю, , , то на информационном входе триггера 52 элементом ИЛИ 51 формируется логический О, который будет записываться по переднему фронту сигнала СИ в каждом последующем такте, что приведет к удержанию логического О на управляющем входе регистра 42 адреса до прихода сигналов ЗпХ, 3nY по вхо0

5

0 Дам 70 и 71. С инверсного выхода триггера 52 логическая 1 подается

35

О, 24, 19, 20, 17, 21, 18, 22 в зависимости от управляющего поля (УП) МК (разряды - 1-3 ПЗУ МК 41, фиг. 5). Поскольку в нулевой ячейке ПЗУ МК 41-УП-ООО, то коммутатор 43 выдает на свой выход логический О. Коммутатор 44 под действием этого сигнала подключит на свои выходы адресное поле (входы) 57, т.е. адрес следующей МК 00001, который будет удерживаться на входе регистра 42 адреса до прихода переднего фронта сигнала с выхода 54 элемента И 46.

Установка размера поля генерируемого символа осуществляется следу- ющим образом (фиг. 6, блок 2). По приходу сигнала ЗпХ, который как и 3nY может быть асинхронным по отношению с СИ, на информационном вхо- |Де триггера 52 через элементы И 45 и ИЛИ 51 устанавливается логическая

1, которая записывается в триггер 52 по бпижайшему переднему фронту сигнала СИ (фиг. 7), что ведет к формированию на информационном входе Триггера 52 логического О, так как Инверсный выход этого трштеоа 52 запрещает действие сигнапа ЗпХ„ а нулевой разряд считанной по адресу 00000 МК равен 0„ Одновременно логп- веская 1 с выхода 53 триггера 52 раз- решает прохождение сигнала СИ через элемент И 46 По переднему фронту сформированного импульса в регистр 42 адреса записывается адрес 00001, йо которому осуществляется выборка Следующей МК из ПЗУ МК 41. Носколъ- |су УД-000, то коммутатор 43 передает на управляющий вход коммутатора 44 Логический О, который -год действи- Јм этого сигнала формирует на входе регистра 42 адреса адресе 00010. По переднему фронту сигнала ЗпХ осуществляется запись значения ДХ, установленного ранее на входе 69, регистр 11 В этом же такте осуществляется обнуление регистра 14 по сигналу с 18-го разряда ПЗУ МК 41 (блок 4, фиг. 6), Шо переднему фронту очередного сигнала СИ з триггер 52 запишется логичес- кий О, который запретит подачу СИ управляющий вход регистра 42 адре- Са - генератор переходит в состояние фжидания. По приходу сигнала 3nY (блок 5) на выходе элемента ИЛИ 51 формируется логическая , которая Записывается в триггер 52 по переднему фронту сигнала СИ, что разрешает его подачу на управляющий вход регистра 42 адреса, куда записывается адрес 00010. По этому адресу из ПЗУ МК 41 Считывается очередная MKS у которой кулевой разряд равен 1./Этот сигнал через элемент ИЛИ 51 передается на информационный вход триггера 52. Одновременно коммутатор 9 под действи ftM управляющего сигнала с 25-го разряда ПЗУ МК 41 (логический О) в Соответствии с фяг. 5 коммутирует на информационный вход сдвигового регистра 2 информацию с входа 69. На управляющий вход этого регистра поступают Сигналы с 26-го и разряда ПЗУ МК 41, которые настраивают сдвиговый регистр 2 на режим записи. По сигналу ft выхода элемента ИЛИ 50, равному 1 (так как ), UY, скоммутирован- ное на вход сдвигового регистра 2 коммутатором 9, записывается в сдвиго--

0

5

0

25 -JQ„

35

45

50

55

вый регистр 2 (блок 6, фиг. 6). Одновременно по сигналам с 14-го и разряда ПЗУ МК 41 обнуляются четвертый 6 и третий 5 счетчики, а по сигналам с 20-го и 21-го разрядов преобразователь 12 осуществляет коммутацию с выхода регистра 11 на вход сумматора 13, где и происходит суммирование. Указанная коммутация производится следующим образом. Сигналы с 20-го и 21-го разрядов ПЗУ МК 41, объединенные в третью группу выходов 38 блока 16 управления, поступают на управляющие входы 63 и 64 (фиг. 3) коммутатора 61, который осуществляет коммутацию выхода регистра 11 на вход формирователя 62 обратного кода. Поскольку сигнал с 20-го разряДа ПЗУ МК 41 (управляющий вход 63) равен О, то формирование обратного кода и переноса не производится и формирователь 62 передает скоммутированный код на вход сумматора 13 без изменения. Результат суммирования по сигналу с 19-го разряда ПЗУ МК 41 записывается в регистр 4„ В следующем такте по переднему фронту сигнала СИ в триггер 52 записывается 1, что разрешает подачу СИ на управляющий вход регистра 42 адреса, куда записывается 00011. По этому адресу из ПЗУ МК 41 считывается МК, поле управляющих сигналов которой содержит управляющие сигналы для преобразователя 12, сдвигового регистра 2 и счетчика 6. Преобразователь 12 коммутирует на вход сумматора 13 обратный код константы М с сформированным переносом, который .используется для получения на сумматоре 13 дополнительного кода константы М в процессе суммирования

с содержимым регистра 14.

Коммутация и формирование обратного кода с переносом производится следующим образом. Сигналы с 20-го и 21-го разрядов ПЗУ Ж 41 поступают на управляющие входы 63 и 64 (фиг. 3) коммутатора 61, который осуществляет коммутацию выхода формирователя 59 константы М на вход формирователя 62 обратного кода. Поскольку сигнал с 20-го разряда ПЗУ МК 41 (управляющий вход 63) равен 1, то происходит формирование обратного кода константы М и переноса, которые поступают на соответствующие входы сумматора 13. В результате суммирова

ния обратного кода константы М, переноса и содержимого регистра 14 суммы получается разность регистр 14 суммы - формирователь кода М (РС-ФКМ кбторая по сигналу с 19-го разряда ПЗУ МК 41 запишется в регистр 14. По сигналу с 15-го разряда ПЗУ МК 41 к содержимому счетчика 6 прибавляется 1 (блок 7, фиг. 6). В этом же такте знак суммы (Зн51) с выхода сумматора 13 поступает в блок 16 управления на вход коммутатора 42, который передает его на управляющий вход коммутатора 44, (так как ). Если Зн S 0 (результат суммирования положительный) , то коммутатор 44 скомму- тирует на вход регистра 42 адреса адресное поле, соответствующее группе выходов 57 ПЗУ МК 41 и равное 00011, т.е. происходит зацикливание блока 7 (фиг. б) до достижения условия (результат суммирования отрицательный). Если Зн 1, то коммутатор 44 передает на вход регистра 42 адреса адрес 00100, что соответствует переходу на блок 9. В следующем такте после считывания из ПЗУ МК 41 по адресу 00100 очередной МК осуществляется запись содержимого счетчика 6 в блок 8 оперативной памяти по адресу, хранящемуся в счетчике 5, а также прибавление содержимого регистра 14 с содержимым регистра 1 1 и запись результата суммирования в регистр 14. Выполнение блока 9 означает окончание вычисления очередного (в данном случае первого) коэффициента увеличения для элемента стандартной матрицы символа по координа- те X. Это достигается формированием сигнала записи БОП 8 коммутацией коммутатора 10, коммутацией преобразователя 12 и формированием сигнала записи регистра 14 на 19-м разряде ПЗУ МК 41 В следующем такте (блок 10) очередная МК считается по адресу 00101, где происходит обнуление счетчика 6 по сигналу с 14-го разряда ПЗУ МК 41 и прибавление +1 к счетчику 5 по сигналу с 31-го разряда ПЗУ МК 41. В этом же такте содержимое счетчика 5 поступает в блок 15, где вырабатывается признак , который поступает на вход коммутатора 43. УП 010, этот признак передается на управляющий вход коммутатора 44. Если признак равен нулю (т.е. содержимое ), то коммута

10

15

20

, 25 .Q

30

35

45

0

5

тор 44 передает на вход регистра 42 адреса адрес 00011, что соответствует зацикливанию до окончания счета всех коэффициентов увеличения элементов разложения матрицы символа по координате X (блок 11). Если признак , то передается адрес 00110, что соответствует началу счета коэффициентов увеличения по координате Y. После считывания из ПЗУ МК 41 очередной МК по адресу 00110 происходит обнуление регистра 14 (блок 12) по сигналу с 18-го разряда ПЗУ МК 41. В следующем такте (блок 13) из ПЗУ МК 41 считывается МК по адресу 00111, поле управляющих сигналов которой содержит управляющие сигналы для выполнения операции вычитания содержимого сдвигового регистра 2 из содержимого регистра 14 и запись значения результата в регистр 14. Это достигается выдачей управляющих сигналов на преобразователь 12 с целью коммутации обратного кода содержимого сдвигового регистра 2 на вход сумматора 13 и формирования переноса для получения дополнительного кода этого числа на сумматоре 13, а также выдачей сигнала записи сдвигового регистра 2 с 19-го разряда ПЗУ МК 41. В следующем такте МК, считанная по адресу 01000, выдает управляющие сигналы для выполнения блока 14, а именно: управляющие сигналы для передачи константы N на вход сумматора 13, сигнал записи результата суммирования содержимого регистра 14 и константы N в регистр 14 - 19-й разряд РЭУ МК 41, сигнал увеличения содержимого счетчика 6 на 1 - 15-й разряд ПЗУ МК 41. В этом же также осуществляется анализ знака результата суммирования ЗнЕ (блок 15). Если знак (знак результата суммирования отрицательный), то следующим адресом считывания МК будет адрес 01000, т.е. осуществляется зацикливание выполнения блока 14 до выполнения условия Зн S 0 (знак результата суммирования положительный). Если Зн 5 0, то осуществляется переход по адресу 01001, т.е. на выполнение блока 16. Условие равенства нулю знака результата суммирования означает, что счет очередного (в данном случае первого) коэффициента увеличения элемента разложения матрицы по координате Y закончен. Величина коэффициента при этом находится в четвертом счетчике 6, Следо- ватапъно, результатом выполнения блока 16 должно стать занесение содержимого счетчика 6 в блок по адресу, хранящемуся в счетчике 5 генератора. Это достигается выдачей упрагляющего сигнала с 33-го разряда ПЗУ МК 41 (логический О) нд второй коммутатор 10, который коммутирует на адресный вход бпока 8 выход счетчика 5. На управляющий вход блока 8 с 34-го и разрядов ПЗУ МК 41 выдается сигнал записи. Одновременно на преобразователь 12 поступают управляющие сигналы, которые коммутируют нз вход сумматора 13 обратный код содержимого сдвигового регистра 2 и формируют перенос для получения дополнительного кода этого числа на сумматоре 13, суммирования эго с содержимым регистра 14. В результате суммирования на выходе сумматора 13 образуется разность содержимых регистра 14 и сдвигового регистра 2, которая по сигналу с 19-го разряда ПЗУ МК 41 записывается в регистр 14. В следующем такте по адресу 01010 из ПЗУ Ж 41 считывается МК, поле управляющих сигналов которой содерзкит управляющие сигналы обнуления счетчика 6- 14-й разряд ПЗУ МК 41, увеличение содержимого счетчика 5 на 1 - 31-й раз™ ряд ПЗУ МК 41 (блок 17). В этом же такте признак сравнения содержимого 1 счетчика 5 и константы (М + N 1) Ст32 (М + N + 1), вырабатываемый блоком 15, передается через коммутатор 43 (так как УП 011) на управляющий вход коммутатора 44, управляя передачей на вход регистра 42 адреса либо адреса 01000, если признак СтЗ (M+N+1)0 (т,а, содержимое счетчика 5 не равно константе (М f + N + 1), что соответствует переходу на счет следующего коэтфчциента увеличения элемента разложения матрицы по координате Y на блок 14), либо адреса 01011, если признак СтЗ (М + + N + 1) 1, что свидетельствует об окончании счета коэффициентов увеличения элементов разложения матрицы по координате Т и завершения счета коэффициентов в целом В следующем такте по адресу 01011 из ПЗУ МК 41 считывается МК, нулевой разряд которой равен нулю. Этот разряд формирует на информационном входе триггера 52 логический О Поскольку УП 000

0

5

0

5

0

5

0

5

то на выход коммутатора 43 коммутируется логический О, который подается на управляющий вход коммутатора 44, который, в свою очередь, подает на вход регистра 42 адреса содержимое поля адреса 57, Таким образом, на входе регистра 42 адреса формируется адрес перехода на следующую МК По приходу переднего фронта сигнала СИ в триггер 52 записывается логический О, который, поступая на вход схемы И 46, блокирует прохождение синхроимпульсов СИ на управляющий вход регистра 42 адреса, таким образом переводя генератор в состояние ожидания. На этом расчет коэффициентов увеличения по X и Y заканчивается

При выходе из состояния ожидания генератор принимает код генерируемого символа и последовательно формирует сигналы вывода точечного изображения этого символа, хранимого в блоке 1, с учетом рассчитанных коэффициентов увеличения каждого элемента разложения матрицы по двум координатам X и Y, которые хранятся в блоке 8, Формирование сигналов последовательного вывода элементов матрицы производится в виде приращений координат нэ одну единицу растра по каждой из осей (по оси X только в положительном направлении) или по одной из них. Поэтому предлагается, что абсолютные координаты начального элемента матрицы символа (крайний левый нижний элемент) известны заранее.

. При наличии на входе 69 кода генерируемого символа по сигналу ЗпХ генератор (блок 19) выводится из состояния ожидания и осуществляется запись поступившего кода в регистр 11 по сигналу ЗпХ. Одновременно сигнал ЗпХ через элементы И 45 и ИЛИ- 51 передается на информационный вход триггера 52, (так как инверсный выход триггера в данный момент равен 1) к записывается по переднему фронту сигнала СИ, устанавливая в единичное состояние выход 53, что способствует прохождению сигналов СИ на управляющий вход регистра 42 адреса. С инверсного выхода триггера 52 логический 0м поступает на вход элемента И 45 s тем самым блокируя прохождение сигнала ЗпХ на информационный вход триггера 52. Сформированный передний фронт сигнала с выхода 54 элемента И 46 записывается в регистр 42 адре,-

ca адрес 01100, по которому осуществляется чтение очередной МК. У считанной МК и у последующих МК до конца генерации символа нулевой разряд равен 1, что способствует установ ке в каждом такте триггера 52 в единичное состояние, что, в свою очеред является условием прохождения строби рующих сигналов СИ на управляющий ,вход регистра 42 адреса. В текущем I такте по сигналам с 20-го и 21-го разрядов ПЗУ МК 41 осуществляется формирование константы М на входе втрого счетчика 4, куда она и заносит- ся по сигналу с 32-го разряда ПЗУ МК 41. По этому же сигналу осуществляется обнуление первого 3 и третьего 5 счетчиков (блок 20). Таким образом, после выполнения данных опера- ,ций в счетчике 5 будет находиться ,начальный адре« расположения в блоке 8 коэффициентов увеличения элементов матрицы символа по координате X, а во втором счетчике 4 - начальный ад- рее расположения в блоке 8 коэффициента увеличения элементов матрицы символа по координате Y. В следующем такте по адресу 01101 из ПЗУ МК 41 считывается МК, поле управляющих сигналов которой содержит управляющие сигналы записи сдвигового регистра 2 содержимым блока 1 разложения матриц символов по адресу, старшие разряды которого образованы кодом символа, хранимого в регистре 11, а младшие - содержимым счетчика 3, записи счетчика 7 содержимым блока 8 по адресу, хранящемуся в счетчике 5, а также

сигнал внешнего выхода -1у (22-й

40

разряд ПЗУ МК 41). Необходимость предварительного шага -1у вызвана требованием генерации символа с заданных координат начального элемента, а блоки 24 и 25 предполагают форми- д рование сигналов приращения 41у и признака генерации одновременно, что может привести к смещению сформированного символа на строку растра вверх. Для выполнения записи сигналы с 20-го и 21-го разрядов ПЗУ МК 41 подаются на управляющие входы преобразователя 12, который коммутирует выход регистра 11 на адресный вход блока 1. Одновременно логический О с 33-го разряда ПЗУ-МК 41, попадая на управляющий вход коммутатора 10, управляет коммутацией на адресный вход блока 8 выхода счетчика 5. Разряды 34 и 35 форми50

55

5

fO

15

, 25 зо

35

40

д 50

55

руют сигнал чтения содержимого блока 8. По сигналу с 36-го разряда ПЗУ МК 41 содержимое считанной ячейки блока 8 записывается в счетчик 7. Этот же сигнал разрешает выборку из блока 1 первого столбца стандартной матрицы разложения символа. Одновременно логическая 1 с 25-го разряда ПЗУ МК 41 поступает на управляющий вход коммутатора 9 и коммутирует на информационные входы сдвигового регистра 2 выход блока 1 разложения матриц символов, а на управляющие входы сдвигового регистра 2 поступают с 26-го и 27-го разрядов ПЗУ МК 41, которые настраивают сдвиговый регистр 2 на режим записи. Сигнал с 28-го разряда ПЗУ МК 41 через элемент ИЛИ 50 разрешает запись содержимого считанной ячейки блока 1 разложения матриц символов в сдвиговый регистр 2 (блок 21). В следующем такте (блок 22) по адресу 01110 из ПЗУ МК 41 считывается МК, поле управляющих сигналов которой содержит управляющие сигналы для записи счетчика 6 содержимым ячейки блока 8, адрес которой находится в счетчике 4. Для этого логическая 1 с 33-го разряда ПЗУ МК 41 поступает на управляющий вход коммутатора 10 и коммутирует на адресные входы блока 8 выхо- 1ды счетчика 4, а на управляющие входы блока 8 поступают сигналы с 34-го и 35-го разрядов ПЗУ МК 41, которые формируют сигнал чтения блока 8. Одновременно по сигналу с 16-го разряда ПЗУ МК 41 осуществляется запись содержимого считанной ячейки блока 8 в счетчик 6. В следующем такте происходит совмещение выполнения блоков (ОН|51 Для этого по адресу 01111 из ПЗУ МК 41 считывается МК, которая формирует сигналы вывода анализируемого элемента стандартной матрицы. В данном такте анализируется нулевой разряд сдвигового регистра 2 (Q0(CP)), т.е. первый нижний элемент формируемого столбца матрицы символа. Считанная МК в поле управляющих сигналов имеет сигналы с 17-го и 23-го разрядов ПЗУ МК 41 (соответственно уменьшение содержимого счетчика 6 на 1 и + 1у), которые подаются на входы элемента И 47, на третий вход кото- ,рого подается нулевой разряд сдвиго- вого регистра 2. Таким образом, если. Q0(CP) 1, то на выходе элемента И 47 формируется логическая 1, ко10

торая через элемент ИЛИ 49 передает- ся на выход устройства, что является признаком генерации, т.е. признаком вывода или не вывода текущей координаты на экран . При 0Р(СР) О такой признак не формируется, следовательно, осуещствляется только при- Ьащение координаты без ее визуализации. В этом же такте по сигналу с |17-го разряда ПЗУ МК 41 происходит Уменьшение содержимого счетчика 6 на 1 и проверка признака равенства нулю содержимого этого счетчика Ст4 О, Нормируемого блоком 15, так как поле . Если признак Ст4 0 равен , то коммутатор 44 передает на вход регистра 42 адреса адрес 01111, т.е. произойдет зацикливание блоков СШ ©Х (Ц) Д° того, пока текущий Коэффициент увеличения элемента матрицы по координате Y не станет равным |нулю. Если признак Ст4 0 равен k 1, то следующая МК будет считываться по адресу 10000 (блок 27 )„ которая в поле управляющих сигналов имеет сигнал с 29-го разряда ПЗУ МК 41, соторый увеличивает содержимое счетчика 4 на 1 (. приращения адреса

75

25

пятого 7 счетчиков на 1 (разряды соответственно 30 и 37 ПЗУ МК 41), а в поле УП код 110, который, поступая на управляющий вход коммутатора 43, управляет передачей признака равенства нулю счетчика 7 Ст5 0, формируемого блоком 15, на управляющий вход когчмутатора 44s который в случае, если Ст5 0 0, коммутирует на вход регистра 42 адреса адрес 10010. Равенство нулю признака Ст5 0 означает, что содержимое счетчика 7, в котором хранится коэффициент увеличения элементов матрицы символа по координате X, не равно нулю, следовательно, необходимо продолжать последовательное формирование сигналов вывода текущего столбца до выполнения указанного равенства С этой целью по адресу 10010 из ДЗУ МК 41 считывается МК, в поле управляющих сигналов которой находятся сигналы с 23-го и 24-го разрядов ПЗУ МК 41, которые выдают на выход устройства приращение по координатам X и Y, т.е. сигналы +1х и --1у (блок (Ц)), Сигнал -Их необходим для перехода на следующий столбец формируемого символа. Сигнал

выборки очередного коэффициента увели-,д -Ну необходим для приращения координаты по Y вследствие одновременного формирования сигналов приращения - 1у и признака генерации в последующем (блоки Q34) , (35/ ), что может привести к смещению изображения формируемого 35 столбца по отношению к уже сформированному. Поскольку поле УП прочитанной МК равно 000, то в следующем такте в регистр 42 адреса запишется адрес 10011, по которому из ПЗУ МК 41 считается МК, после управляющих сигналов которой содержит сигналы записи счетчика 6 содержимым блока 8 по ад- ре cv, находящемуся в счетчике 4. При

чения элементов матрицы символа по Координате Y), и сигналы управления сдвиговым регистром 2, которые, по- тупая с 26-го и 27-го разрядов ПЗУ |ИК 41, устанавливают режим сдвига вправо на один разряд, который осу- цествляется по сигналу с выхода элемента ИЛИ 50, (так как 28-й разряд ПЗУ МК 41 равен единице). В этом же такте анализируется признак сравнения содержимого счетчика 4 с константой (М + N + 1) Ст2 (М + N + 1), сформированный блоком 15, так как поле УП 101. Если Ст2 (М + N + 1) - 0, т.е. содержимое счетчика 4 не равно константе (М + N + 1), то коммутатор 44 под воздействием этого сигнала на вход регистра 42 адреса передаст адрес перехода 01110, т„е. произойдет зацикливание формирования признака генерации, который зависит от значения нулевого разряда сдвигового регистра 2, до конца текущего столбца (блок (|jj) ). Если Ст2 (М -г N + 1) 1 то осуществляется

наты по Y вследствие одновременного формирования сигналов приращения - 1у и признака генерации в последующем (блоки Q34) , (35/ ), что может привест к смещению изображения формируемого 35 столбца по отношению к уже сформированному. Поскольку поле УП прочитанной МК равно 000, то в следующем так те в регистр 42 адреса запишется адрес 10011, по которому из ПЗУ МК 41 считается МК, после управляющих сигналов которой содержит сигналы запис счетчика 6 содержимым блока 8 по ад- ре cv, находящемуся в счетчике 4. При

40

45

50

этом логическая 1 с 28-го разряда ПЗУ МК 41 управляет коммутацией коммутатора 10 и подключает выход счетчика 4 на адресный вход блока 8. Одновременно сигналы с 34-го и 35-го разрядов ПЗУ МК 41 формирует сигнал чтения для блока 8, а по сигналу с 16-го разряда ПЗУ МК 41 содержимое считанной ячейки записывается в счетчик 16. Поле УП выполняемой МК равно 000, поэтому адрес следующей МК опре

П реход и считывание МК из ПЗУ МК 41 D деляется полем 57. В следующем такте

по адресу 10001 (блок 29). Считанная МК в поле управляющих сигналов имеет два сигнала уменьшения второго 4 и

происходит совмещение выполнения бло ков Ш/ S& подобно описанному (бло ки (23)(2(эГ). По адресу 10100 из

5

пятого 7 счетчиков на 1 (разряды соответственно 30 и 37 ПЗУ МК 41), а в поле УП код 110, который, поступая на управляющий вход коммутатора 43, управляет передачей признака равенства нулю счетчика 7 Ст5 0, формируемого блоком 15, на управляющий вход когчмутатора 44s который в случае, если Ст5 0 0, коммутирует на вход регистра 42 адреса адрес 10010. Равенство нулю признака Ст5 0 означает, что содержимое счетчика 7, в котором хранится коэффициент увеличения элементов матрицы символа по координате X, не равно нулю, следовательно, необходимо продолжать последовательное формирование сигналов вывода текущего столбца до выполнения указанного равенства С этой целью по адресу 10010 из ДЗУ МК 41 считывается МК, в поле управляющих сигналов которой находятся сигналы с 23-го и 24-го разрядов ПЗУ МК 41, которые выдают на выход устройства приращение по координатам X и Y, т.е. сигналы +1х и --1у (блок (Ц)), Сигнал -Их необходим для перехода на следующий столбец формируемого символа. Сигнал

-Ну необходим для приращения координаты по Y вследствие одновременного формирования сигналов приращения - 1у и признака генерации в последующем (блоки Q34) , (35/ ), что может привести к смещению изображения формируемого столбца по отношению к уже сформированному. Поскольку поле УП прочитанной МК равно 000, то в следующем такте в регистр 42 адреса запишется адрес 10011, по которому из ПЗУ МК 41 считается МК, после управляющих сигналов которой содержит сигналы записи счетчика 6 содержимым блока 8 по ад- ре cv, находящемуся в счетчике 4. При

этом логическая 1 с 28-го разряда ПЗУ МК 41 управляет коммутацией коммутатора 10 и подключает выход счетчика 4 на адресный вход блока 8. Одновременно сигналы с 34-го и 35-го разрядов ПЗУ МК 41 формирует сигнал чтения для блока 8, а по сигналу с 16-го разряда ПЗУ МК 41 содержимое считанной ячейки записывается в счетчик 16. Поле УП выполняемой МК равно 000, поэтому адрес следующей МК определяется полем 57. В следующем такте

происходит совмещение выполнения блоков Ш/ S& подобно описанному (блоки (23)(2(эГ). По адресу 10100 из

ПЗУ МК 41 считывается МК, которая формирует сигналы вывела анализируемого элемента стандартной матрицы. Отличие заключается в анализе последнего (N-l)-ro разряда сдвигового регистра 2 (Q (N-,j(CP)), т.е.последнего верхнего элемента формируемого столбца матрицы символа. Считанная МК в поле управляющих сигналов имеет сигналы с 17-го и 22-го разрядов ПЗУ 41 (уменьшение содержимого счетчика 6 на 1 и -1 у), которые подаются на входы элементы И 48, на третий вход которой подается (№-1)-й разряд сдвигового регистра 2. Таким образом, если 0( N,j(CP)1, то на выходе элемента И 48 формируется логическая 1, которая через элемент ИЛИ 49 передается на выход устройства, что является признаком генерации. При 0(N,,j(CP)0, как и в предыдущем случае, такой признак не формируется, следовательно, осуществляется только приращение координаты. В этом же такте по сигналу с 17-го разряда ПЗУ МК 41 происходит уменьшение счетчика 6 на единицу и проверка признака равенства нулю содержимого этого счетчика , формируемого блоком 15, так как поле . Если , то произойдет зацикливание блоков (53) т (ЗТ), что приведет к развертке увеличиваемого элемента столбца сверху вниз (в отличии от зацикливания блоков Q$ (Is), где приращение по Y положительно +1у, следовательно, развертка снизу-вверх) Зацикливание обуславливается коммутацией на вход регистра 42 адреса при адреса возврата на текущий блок - 10100. При (т.е. содержимое счетчика 6 равно нулю) следующая МК будет считываться с адреса 10101 (блок (37)). Считанный МК в поле управляющих сигналов имеет сигналы уменьшения содержимого счетчика 4 на единицу и сдвига содержимого сдвигового регистра 2 на один разряд влево. Выполнение действия Ст2 Ст2-1 происходит по сигналу с 30-го разряда ПЗУ МК 41. С 26-го и 27-го разряда ПЗУ МК 41 на управляющий вход сдвигового регистра 2 поступают сигналы, которые устанавливают режим работы Сдвиг влево, который осуществляет- ся по сигналу с выхода элемента ИЛИ 50, так как 28-й разряд ПЗУ МК 41 равен 1. В этом же такте осуществляется анализ признака равенства константе

(М-1) содержимого счетчика 4 (блок (38) ) Ст2(М-О, вырабатываемый блоком 15, который происходит следующим образом. Поле УП-111 поступает на управляющий вход коммутатора 43, который в соответствии с поступившим кодом УП коммутирует признак Ст2(М-1 на управляющий вход коммутатора 44, который, в свою очередь, в зависимости от поступившего сигнала (0 или 1) коммутирует на вход регистра 42 адреса либо адрес с группы выходов 57, либо адрес с группы выходов 58. Если Ст2(М-1)0 (т.е. содержимое второго счетчика 4 не равно константе (М-1 что означает окончание развертки очередного элемента столбца матрицы, но не столбца в целом), то необходимо продолжать генерацию текущего столбца матрицы символа и адрес считывания очередной МК будет 10011. Если Ст2(М-1) (генерация столбца завершена), то адрес перехода 10110 (блок (39/ ). МК, считанная по этому адресу, в поле управляющих сигналов имеет сигналы инкремента второго 4 и декремента пятого 7 счетчиков, что соответствует сигналам с 29-го и 37-г разрядов ПЗУ МК 41. В этом же такте производится анализ признака равенства нулю содержимого пятого счетчика 7 , формируемого блоком 15 (блок @ ) .

Возможны два варианта. Если , то это значит, что текущий коэффициент увеличения элемента матрицы по координате X, хранимый в счетчике 7, не равен нулю и следует продолжать генерацию выбранного столбца матрицы, предварительно сделав шаг по X и Y (+1х, -1у, блок j) ) В этом случае выполняется МК по адресу 10111, которая выдает сигналы с 22-го и 24-го разрядов ПЗУ МК 41, и управление передается по адресу 01110 (на блок (22)). Если (блок 40 ), то это свидетельствует о завершении генерации текущего столбца матрицы как по координате X, так и по Y. В этом случае по адресу 11000 считывается МК, которая выдает управляющий сигнал инкрементирования с 31-го разряда ПЗУ МК 41, который увеличивает на единицу содержимого третьего 5 и первого 3 счетчиков (блок ( ), что означает изменение адреса для выборки из блока 8 следу

ющего коэффициента увеличения элемента матрицы по координате X и изменение адреса для выборки из блока 1 следующего столбца стандартной матрицы соответственно. В этом же такте произ родится анализ признака равенства константе М содержимого третьего счетчика 5 (блок (43) ), формируемого блоком 15. Если (содержимое счетчика 5 равно М), то Генерация символа завершена и производится переход по адресу 01011 (блок () ) , что переводит генератор |в состояние ожидания приема следующе- го кода символа. Если , то по адресу 11001 из ПЗУ МК 41 считывается МК, поле управляющих сигналов которой содержит сигналы приращения +1х, -1у, сигналы для записи в счетчик 7 содержимого ячейки блока 8, адресуемой счетчиком 5, сигналы для записи в сдвиговый регистр 2 очередного столбца матрицы из блока 1, адрес которого содержится в регистре 11 (старшие разряды адреса), и в счетчике 3 (младшие разряды адреса) (блок (Ј$ ). Для выполнения указанных действий логической О с 33-го разряда ПЗУ МК 41 поступает на коммутатор 10 и коммутирует на адресные входы блока 8 выход счетчика 5. Сигналы с 34-го и 35-го разрядов ПЗУ МК 41 поступают на управляющий вход блока 8 и формируют сигнал -чтения. Одновременно сигналы с 20-го и 21-го разряда ПЗУ МК 41 поступают на управляющий вход преобразователя 12, коммутируют на адресный вход блока 1 выход регистра 11. По сигналу с 36-го разряда ПЗУ МК 41 происходит запись счетчика 7 , считанной из блока 8 ячейки и чтение блока 1. Одновременно сигналы с 26-го и 27-го разрядов ПЗУ МК 41 настраивают сдвиговый регистр 2 на pe жим записи, а логическая 1 с 25-го разряда ПЗУ МК 41 поступает на управляющий вход коммутатора 9 и в соответствии с таблицей (фиг. 5) коммутирует выход блока 1 на вход сдвигового регистра 2. По сигналу с выхода элемента ИЛИ 50 (так как 28-й разряд ПЗУ МК 41 равен единице) осуществляется запись содержимого считанной ячейки блока 1 в сдвиговый регистр 2 В этом же такте выдаются сигналы приращения +1 и -1 соответственно с 24-го разряда ПЗУ МК 41. Поскольку в МК поле , то осуществляет

0

-Q 25 40|j 30

35

50

55

ся переход по адресу 01110 (на блок (22) ). При (блок @) ) обработка блоков 45-47 ведется аналогично описанной обработке блоков (4Ј)-(Ј4) соответственно. Различие состоит в формировании в блоке 7) сигнала приращения +1у (23-й разряд ПЗУ МК41), а не -1у, как это было в блоке (44) . Равенство содержимого счетчика 7 константе М (признак ), блок (Јнр свидетельствует об окончании формирования символа, причем последний генерируемый элемент будет правым крайним верхним элементом символа. Генерацию же нового символа необходимо начинать с крайнего левого нижнего элемента. Поэтому следует переместить текущее положение координаты на число элементов в столбце вниз. Это производится блоками 48-52 ). После выполнения МК с адресом 11010 (блоки (45) и (46) ) в случае, если , в следующем такте будет выполнение МК с адресом 11100 (блок (48) ) , поле управляющих сигналов которой содержит логическую 1 с 33-го разряда ПЗУ МК 41, которая поступает на управляющий вход коммутатора 10 и коммутирует на адресные входы блока 8 выход счетчика 4. Сигналы с 34-го и 35-го разрядов ПЗУ МК 41 формируют сигнал чтения блока 8. По сигналу с 36-го разряда ПЗУ МК 41 считанная информация записывается в счетчик 7. Поскольку в МК поле , то следующая МК считывается по адресу 11101 (блок 9) , (5у) ). В этом такте выдаются сигналы с 22-го и 37-го разрядов ПЗУ МК 41 (внешний сигнал т1у и сигнал декремента счетчика 7 соответственно) и анализируется признак равенства нулю содержимого счетчика 7. , формируемый блоком 15. Сигнал признака генерации, формируемый элементами И 47 и 48 и ИЛИ 49, не выдается, поскольку 17-й разряд ПЗУ МК 41 (декремент счетчика 6), заведенный на входы элементов И 47 и 48, равен О. Если , то происходит возврат на блок 9) (адрес 11101 с группы выходов 57 ПЗУ МК 41). Если (т.е. равенство нулю содержимого пятого счетчика 7 выполняется), то осуществляется переход на МК по адресу 11110 (блок (5j) , адрес поступает с группы выходов 58 ПЗУ МК 41). Поле управляющих сигнат лов этой МК содержит сигнал декремента счетчика 4 (30-й разряд ПЗУ МК 41 В этом же такте осуществляется анали признака равенства содержимого счетчика 4 константе (М-1) Ст2(М-1), формируемого блоком 15, Если Ст2 (М-1)0, то осуществляется переход на МК по адресу 11100 (на блок @) ). При Ст2(М-1)1 производится переход на МК по адресу 01011, т.е. на ввод следующего кода символа (блок (Т9)). При необходимости изменения формата генерируемого символа или окончания работы генератора выход из цикла осуществляется по сигналу Сброс. Во всех МК, где блок 8 и сдвиговый регистр 2 не задействованы они находятся в режиме хранения, что достигается подачей сигналов на их управляющие входы с 34-го, 35-го и Сб-го, 27-го разрядов ПЗУ МК 41.

Предлагаемый генератор символов произвольного формата позволяет увеличить области применения таких устройств за счет увеличения числа воспроизводимых форматов по сравнению с существующими устройствами для генерации символов.

Формула изобретения

Генератор символов, содержащий блок постоянной памятиs сдвиговый регистр, с первого по пятый счетчики, блок оперативной памяти и блок управления, отличающийся тем, что, с целью расширения области применения генератора за счет увеличения числа воспроизводимых форматов символов, генератор содержит первый и второй коммутаторы, первый и второй регистры, преобразователь кодов, сумматор и блок сравнения, первый информационный вход первого коммутатора и информационный вход первого ре- гистра являются информационным входом генератора, входом сигнала управления записью координаты X которого являются управляющий вход первого регистра и первый управляющий вход блока управления, второй управляющий вход которого является входом сигнала управления записью координаты Y генератора, входом сигнала сброса и входом синхросигнала которого являются вход сброса и синхровход блока управления, выход первого коммутатора подключен к информационному входу сдвигового регистра, первый выход ко

0

5

0

5

0

5

.. ,

0

торого соединен с первым информационным входом преобразователя кодов, второй информационный вход которого соединен с выходом первого регистра, второй выход сдвигового регистра подключен к первому информационному входу блока управления, второй информационный вход которого соединен с первым выходом сумматора, второй выход которого подключен к информационному входу второго регистра, выход которого соединен с первым информационным входом сумматора,-второй и третий информационные входы которого соединены с первым и вторым выходами преобразователя кодов, второй выход которого подключен к информационному входу четвертого счетчика, а третий выход - к первому адресному входу блока постоянной памяти, второй адресный вход которого соединен с выходом первого счетчика, а выход - с вторым информационным входом первого коммутатора, выходы второго и третьего счетчиков подключены к первому и второму информационным входам второго коммутатора, соединенным соответственно с первым

и вторым входами блока сравнения, третий и четвертый входы которого подключены соответственно к выходам четвертого и пятого счетчиков, выход четвертого счетчика подключен к информационному входу блока оперативной памяти, адресный вход которого соединен с выходом второго коммутатора, д выход - с информационными входами четвертого и пятого счетчиков, с первого по шестой выходы блока сравнения подключены соответственно к управляющим входам с третьего по восьмой блока управления, выход второго регистра соединен с третьим информационным входом сумматора, первый выход блока управления подключен к первому управляющему входу пятого счетчика, второй выход - к второму управляющему входу пятого счетчика и управляющему входу блока постоянной памяти, третий выход - к управляющему входу блока оперативной памяти, четвертый выход - к управляющему входу второго коммутатора, пятый выход - к первым управляющим входам третьего, второго и первого счетчиков, шестой выход - к вторым управляющим входам третьего и первого счетчиков, седьмой выход - к второму управляющему входу второго счетчика, восьмой и девятый выходы к управляющим входам сдвигового регистра и первого коммутатора соответственно, с десятого по тринадцатый выходы являются с первого по четвертый выходами генератора, четырнадцатый, пятнадцатый и шестнадцатый выходы блока управления соединены соответственно с управляющими входами преобразователя кодов, второго регистра и четвертого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275520A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для сопряжения вычислительнойМАшиНы C ТЕРМиНАлАМи | 1979 |

|

SU798786A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1605279A2 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для отображения графической информации. Цель изобретения - расширение области применения генератора путем увеличения числа воспроизводимых форматов символов. Это достигается введением коммутаторов 9 и 10, регистра 14, преобразователя кодов 12, сумматора 13, блока 15 сравнения и соответствующих функциональных связей, что позволяет осуществлять предварительный расчет и хранение коэффициентов увеличения каждого элемента разложения матрицы символа за счет линейной интерполяции и формировать требуемый размер символа с учетом рассчитанных коэффициентов путем выдачи символов приращения относительно заданных координат крайнего левого нижнего элемента матрицы. 8 ил.

Фиг.2.

Otn2 Offfff

к Я и 4 Kt3 ФшЗ

Отб От7

65 СС(0)

6ff СС(/1)

К/7

v /с/9

OmS

Ofn4

67 CC()

68 CC(M-f)

f к2О к21

v 22

Фю.4

f

N

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Патент США № 4283724, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1990-03-15—Публикация

1987-04-23—Подача