СЛ

Ч

кл

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВИДЕОСИГНАЛА | 1989 |

|

RU2042185C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для отображения информации | 1987 |

|

SU1513439A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Устройство для отображения информации | 1983 |

|

SU1193722A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1986 |

|

SU1336108A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1994 |

|

RU2116674C1 |

| УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1998 |

|

RU2141737C1 |

Изобретение относится к вычислительной технике и может быть использовано для реализации многооконной машинной графики. Целью изобретения является повышение быстродействия устройства. Устройство содержит блок 1 управления, формирователь 2 управляющих сигналов, блок 3 коммутации, блок 4 постоянной памяти блок 5 оперативной памяти, блок 6 сопряжения, вычислитель 7 числа фрагментов изображения, вычислитель 8 номеров фрагментов изображения и формирователь 9 адреса с соответствующими связями. Введение блока 3 коммутации, формирователя 7 числа фрагментов, вычислителя 8 номеров фрагментов и формирователя 9 начального адреса позволило повысить быстродействие устройства за счет аппаратурной поддержки режима формирования многооконной графической информации. 7 ил.

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано для реализации многооконной машинной графики.

Цель изобретения - повышение быстродействия устройства,

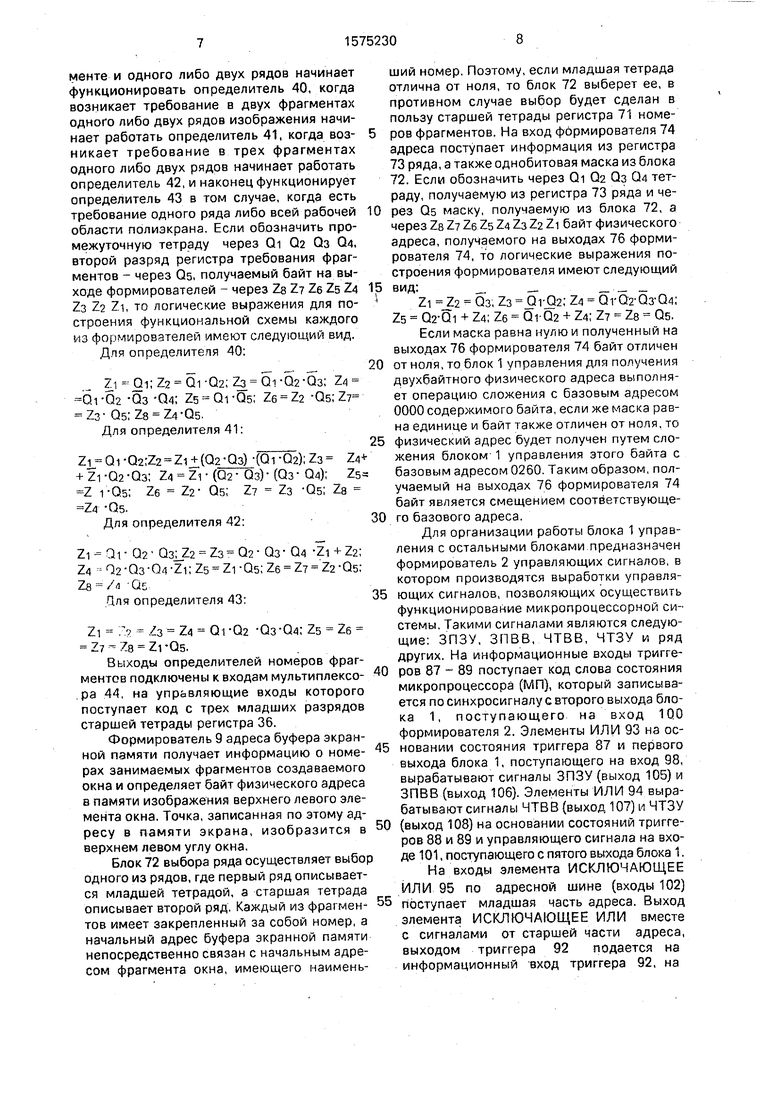

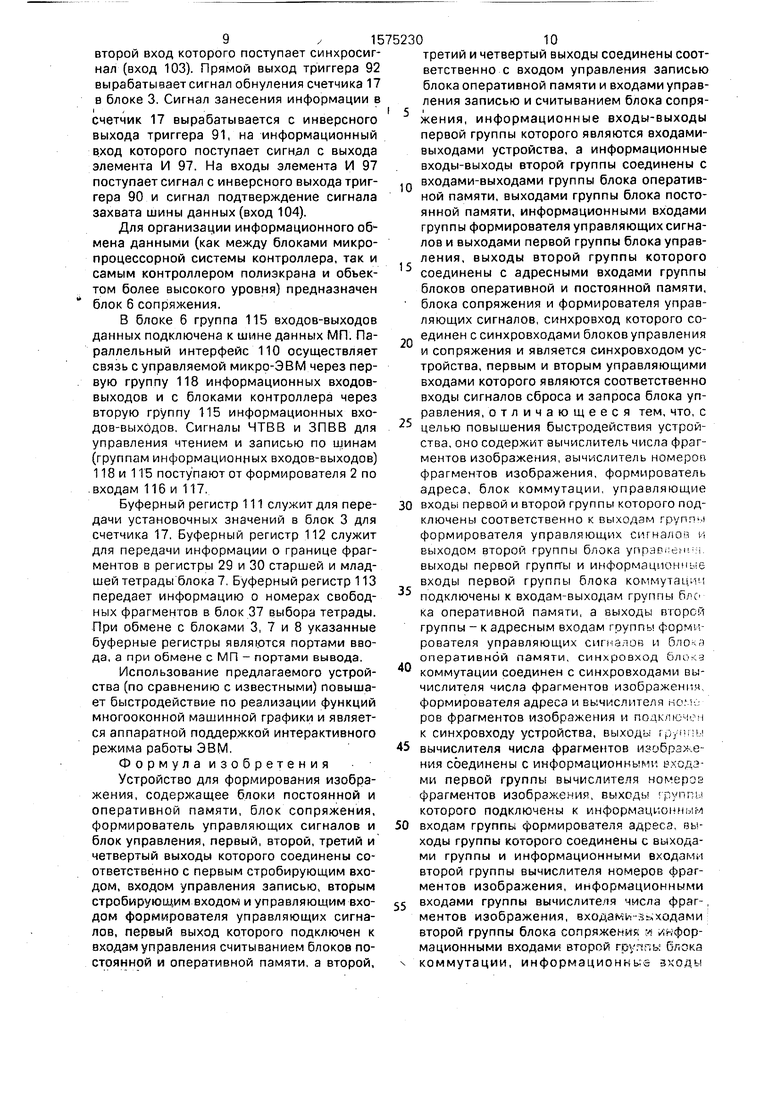

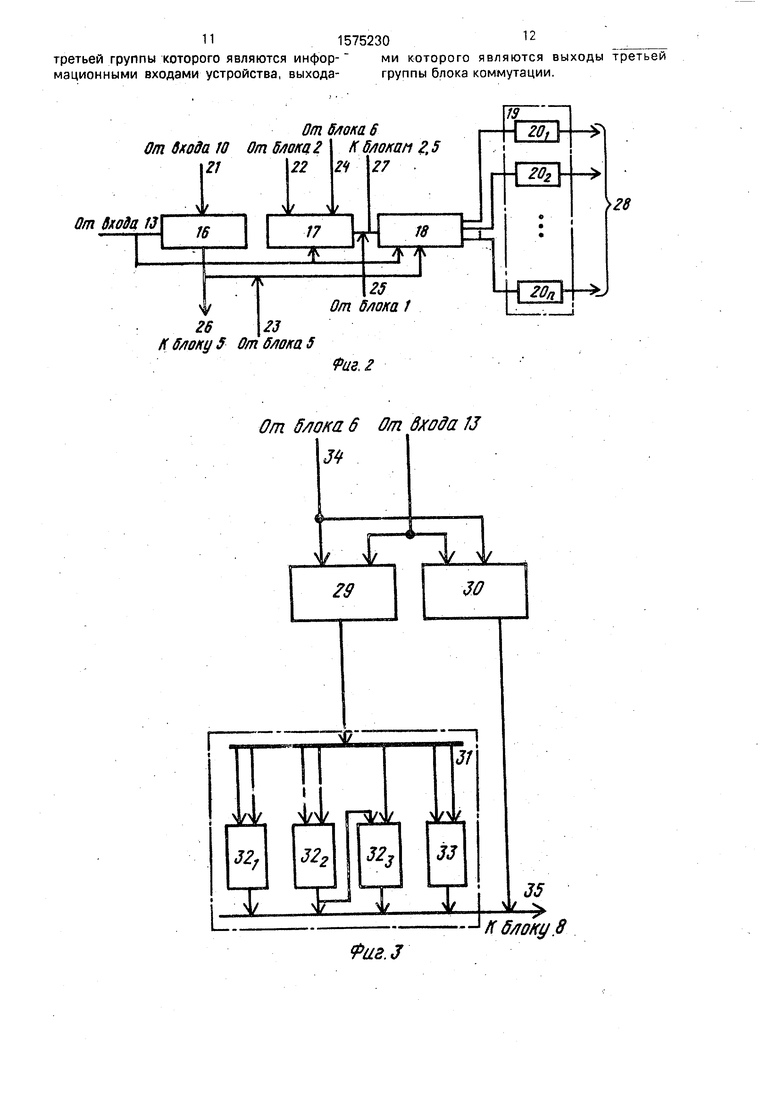

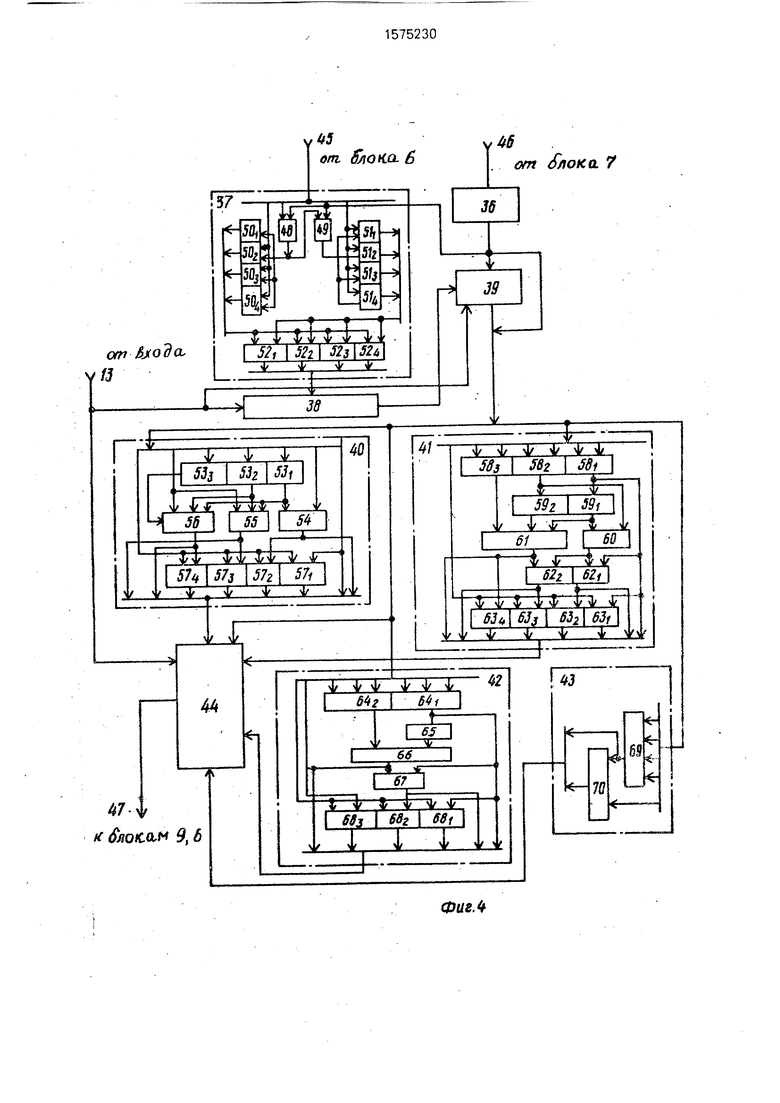

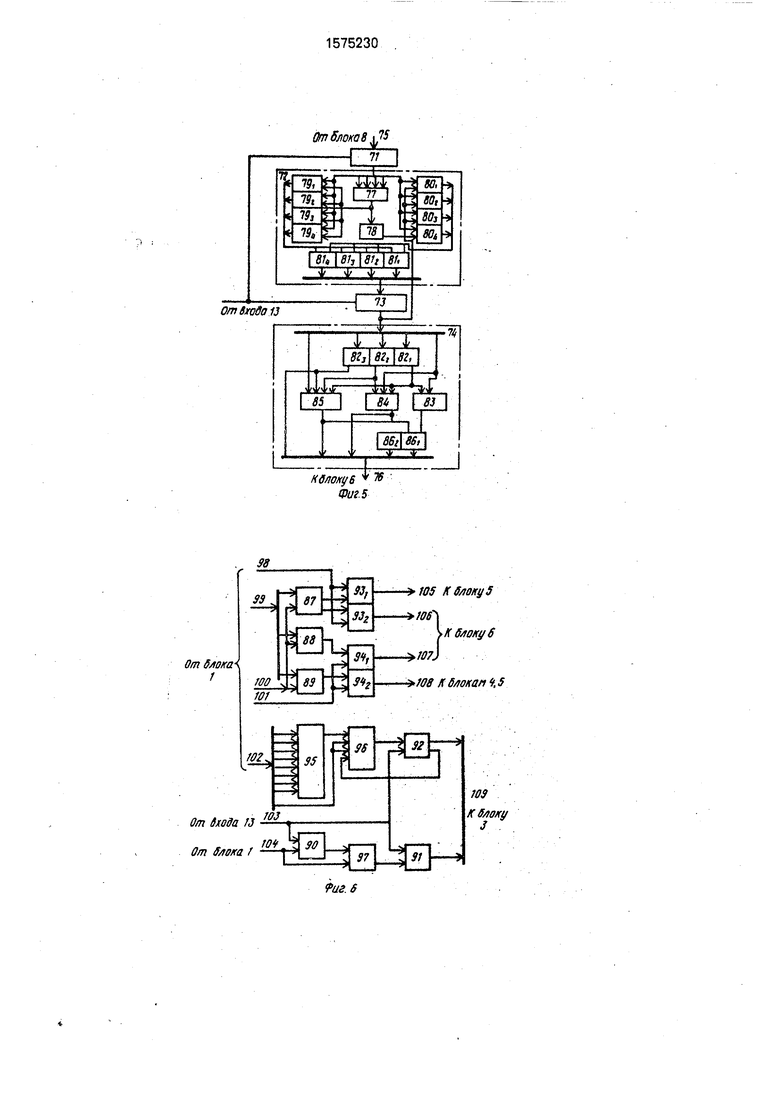

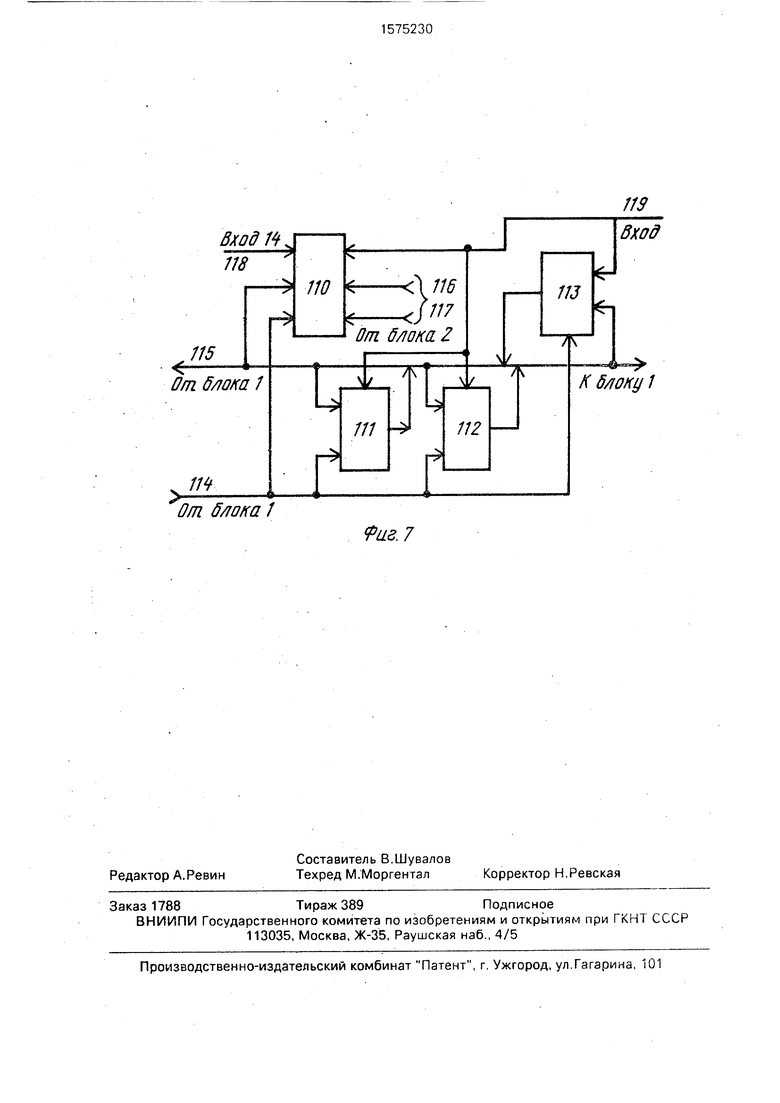

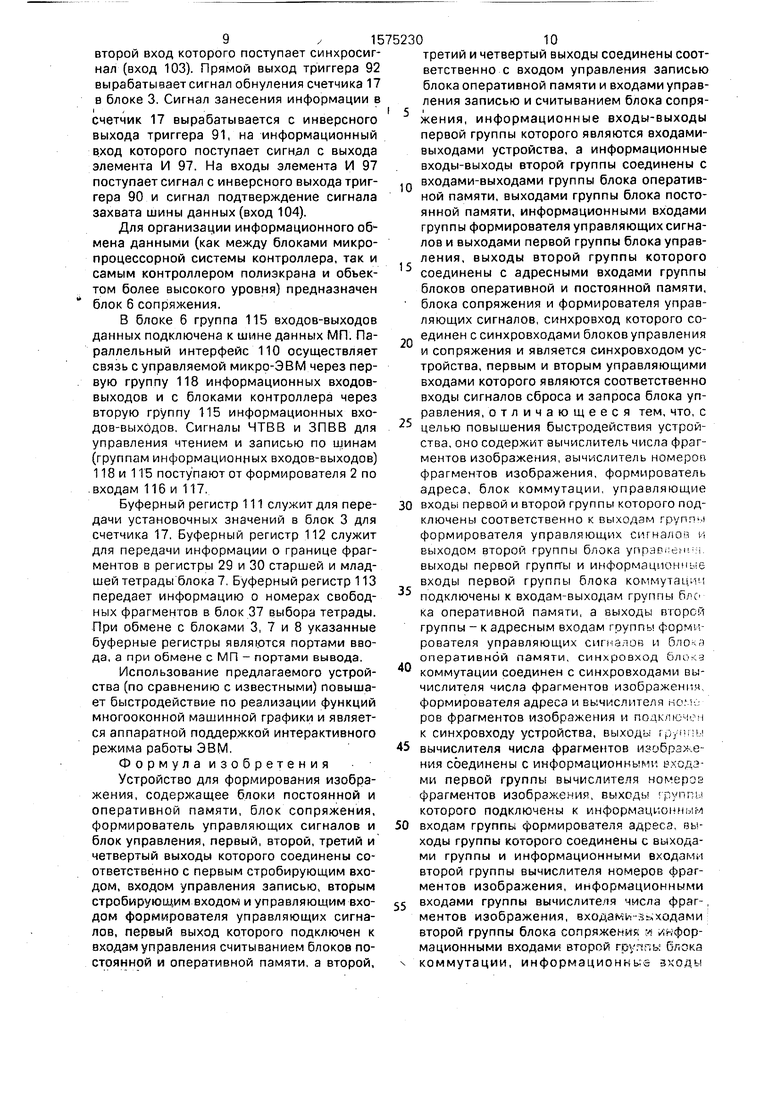

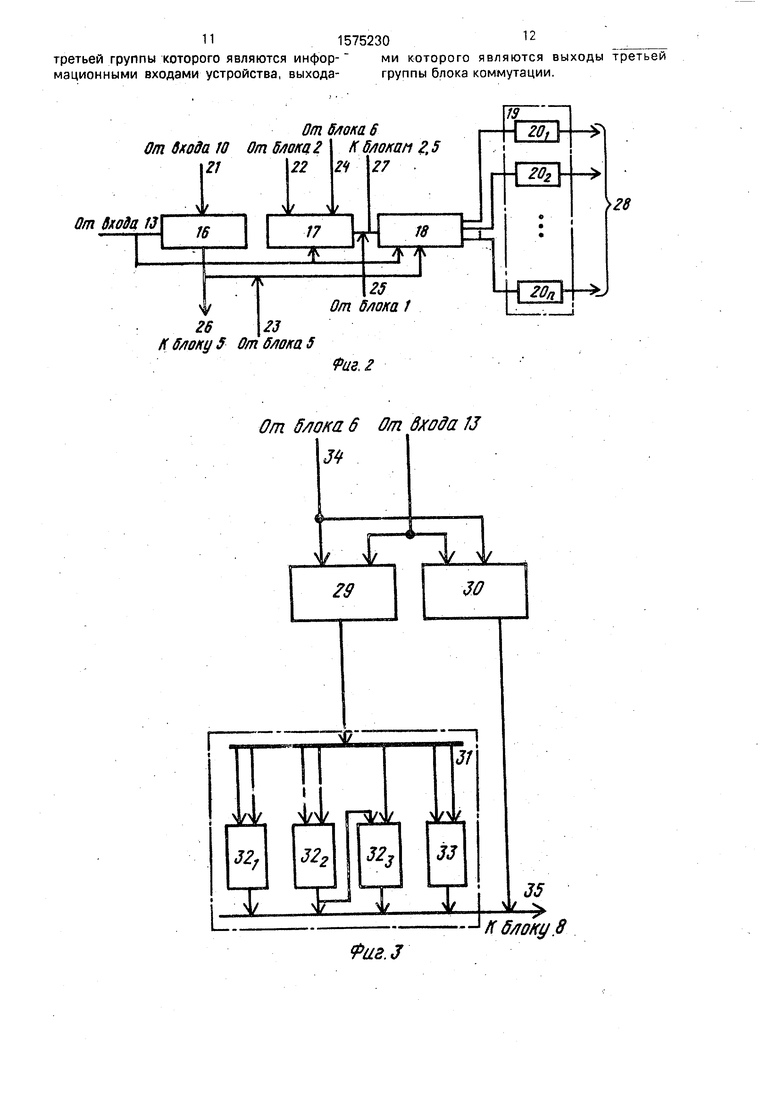

На фиг.1 изображена блок-схема предлагаемого устройства; на фиг.2 - структура блока коммутации; на фиг.З - вычислитель числа фрагментов изображения; на фиг.4 - вычислитель номеров фрагментов изображения; на фиг.5 - формирователь адреса; на фиг.6 - формирователь управляющих сигналов; на фиг.7 - блок сопряжения.

Устройство содержит блок 1 управления, формирователь 2 управляющих сигналов, блок 3 коммутации, блок 4 постоянной памяти, блок 5 оперативной памяти, блок 6 сопряжения, вычислитель 7 числа фрагментов изображения, вычислитель 8 номеров фрагментов изображения, формирователь 9 адреса, группу 10 информационных входов, группу 11 выходов, первый управляющий вход 12, вход 13 синхронизации, входы-выходы 14 и второй управляющий вход 15.

БлокЗ коммутации содержит регистр 16 командной информации, счетчик 17, первый демультиплексор 18, группу 19 регистров 20i - 20П ввода, причем входы 21-25 являются соответственно третьей группой информационных, первой группой управляющих, первой и второй группой информационных и второй группой управляющих входов блока, объединенные синхровходы регистра 16, счетчика 17 и первого демуль- типлексора 18 являются синхровходом блока, выходы 26 - 28 являются соответственно первой, второй и третьей группой выходов блока коммутации.

Вычислитель 7 числа фрагментов изображения содержит регистры 29 и 30 соответственно старшей и младшей тетрады, формирователь 31 числа фра ментов по горизонтали, включающий в себя элементы ИЛИ-НЕ 32i - 32з и первый элемент И 33, причем вход 34 является группой информационных входов, объединенные синхровходы регистров 29 и 30 являются сиНхров- ходом, а выход 35 - группой выходов формирователя.

Вычислитель 8 номеров фрагментов изображения содержит регистр 36 требования фрагментов, блок 37 выбора тетраты, регистр 38 тетрады, второй демультиплексор 39, первый 40, второй 41, третий 42 и четвертый 43 определители номеров фрагментов, мультиплексор 44, вторую 45 и первую 46 группы информационных входов, группу 47 выходов, второй элемент И 48, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 49,

первую группу элементов ИЛИ 50i - 504, вторую группу элементов ИЛИ 511 - 514, первую группу элементов И 52i - 524, первую группу элементов НЕ 53i - 53з, третий

54, четвертый 55 и пятый 56 элементы И, вторую 57i - 574 и третью 58i - 58з группы элементов И, элементы НЕ 59i и 592, шестой 60 и седьмой 61 элементы И, элементы ИЛИ 62i и 622, четвертую 63i - 634 и пятую 64ч и

0 64а группы элементов И, первый элемент 65 НЕ, восьмой элемент 66 И, первый элемент ИЛИ 67, элементы И 681 - 683, девятый 69 и десятый 70 элементы И, причем объединенные синхровходы блоков 38, 39 и 44 являют5 ся синхровходом блока 8.

Формирователь 9 адреса содержит регистр 71 номеров фрагментов, блок 72 выбора ряда, регистр 73 ряда, блок 74 формирования адреса, группу 75 информа0 ционных входов, группу 76 выходов, второй элемент ИЛИ 77, второй элемент НЕ 78 седьмую 791 - 794 и восьмую 80i - 804 группы элементов И, элементы ИЛИ 81 ч - 814, элементы НЕ 821 - 82з, одиннадцатый 83,

5 двенадцатый 84 и тринадцатый 85 элементы И и элементы ИЛИ 86i и 862, причем объединенные синхровходы блоков 71 и 73 являются синхровходом формирователя.

Формирователь 2 управляющих сигна0 лов содержит первый 87, второй 88, третий 89, четвертый 90, пятый 91 и шестой 92 триггеры, шестую 93i и 932 и седьмую 94i и 942 группы элементовИЛИ, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 95, четырнадцатый 96 vi

5 пятнадцатый 97 элементы И, первый стро- бирующий вход 98, группу 99 информац он- ных входов, вход 100 записи, второй стробирующий вход 101, группу 102 адресных входов, синхровход 103, управляющий

0 вход 104, второй 105, третий 106, четвертый 107 и первый 108 выходы, а также группу 109 выходов,

Блок 6 сопряжения содержит программируемый параллельный интерфейс 110,

5 первый 111, второй 112 и третий 113 буферные регистры, группу 114 адресных входов, вторую группу 115 информационных входов-выходов, вход 116 сигналов считывания, вход 117 сигналов записи, первую

0 группу 118 информационных входов-выходов и синхровход 119.

Устройство работает следующим образом.

Основным блоком устройства является

5 блок 1 управления, реализованный на базе микропроцессора и регулирующий процесс обмена информацией, При этом рабочая область изображения разбивается на N одинаковых по размерам областей, расположенных в два ряда и именуемых фрагментами. Фрагменты имеют собственные номера и в определенный момент времени могут принадлежать только одному окну либо быть не занятыми. Окно может занимать целое число фрагментов - от одного до N. Для создания окна требуется некоторая командная информация, для обработки которой, а также для хранения, учета и контроля информации о созданных ранее и создаваемых окнах служит устройство. Первоначально в блок 3 коммутации от внешнего контроллера прямого доступа к памяти поступает командная информация создаваемого окна, которая записывается в карту памяти изображения, хранящуюся в блоке 5 оперативной памяти. В свою очередь карта памяти изображения содержит карты окон изображения.

Блок 3 коммутации служит как для записи информации в карту окна полиэкрана, так и для передачи параметров разворачиваемого окна, что позволяет ускорить обмен данными по сравнению с программным способом обмена.

8 регистр 16 командной информации поступают данные от контроллера прямого доступа и памяти, эти данные затем записываются по адресам, сформированным счетчиком 17, в блок 5 оперативной памяти. Эти же данные поступают на информационные входы первого демультиплексора 18, управляемого четырьмя младшими разрядами счетчика 17. В зависимости от кода, представляемого на управляющих входах первого демультиплексора 18, выбирается соответствующий регистр 20 ввода. Тем самым осуществляется распараллеливание двух процессов:

запись информации в карту окна изображения;

запись параметров окна в группу 19 регистров 20 ввода.

Если окно было ранее создано и его необходимо развернуть, то из карты окна изображения на первую группу входов 23 параметрической информации поступают данные из блока 5 оперативной памяти. Далее эти данные поступают на информационную группу демультиплексора 18, управление работой которого осуществляется данными, поступающими на вход 25 от блока 1 управления.

В блоке 3 через входы 24 передается установочное значение счетчика 17 от блока 6. Через входы 22 передаются от формирователя 2 сигналы занесения информации в счетчик 17 блока 3 и обнуление счетчика 17.

Вычислитель 7 служит для создания требований в фрагментах, необходимых для создания окон.

В регистр 29 старшей тетрады из блока 6 поступает информация о границе фрагментов в количестве точек строки, а в регистр 30 младшей тетрады 30 из того же

5 блока 6 поступает информация о границе фрагментов по количеству строк.

Формирователь 31, получив информацию о границе фрагментов по точкам строки, преобразует ее в тетраду данных,

0 содержащих требование в количестве фрагментов по горизонтали.

Границы фрагментов по точкам строки могут принимать следующие значения: 80io(50i6): 160ю (A0i6); 240ю(01б);

5 320ю (0140ie).

Для первого случая формирователь 31 выбирает один фрагмент, для второго случая -два фрагмента, для третьего -три и для четвертого - четыре фрагмента или целый

0 ряд. Для исключения избыточности на вход формирователя 31 из регистра 29 поступает старшая тетрада младшего байта границы фрагмента по количеству точек строки. Если обозначить разряды тетрады границы фраг5 ментов через Qs Q Qe Qs, а разряды тетрады, получаемой на выходе формирователя 31, через Ze Z Ze Zs, то работа блока 31 осуществляется в соответствии с логическими выражениями:

ТП37;25

0 Ze QS + Qe: Z Qy-Qe, Ze Qs

- LJ8

Границы фрагментов по количеству строк могут принимать следующие значения: 90ю(5А1б}; 180ю(В41б).

5В первом случае будет выбран один ряд

экрана, а во втором - два ряда.

Вычислитель 8 служат для получения номеров фрагментов, занимаемых создаваемым окном.

0В регистр 36 требования фрагментов

записывается результат работы вычислителя 7, в результате чего в блок 37 выбора тетрады поступает информация о номерах незанятых фрагментов. Блок37осуществля5 ет выбор тетрады информации о номерах незанятых фрагментов, еслх содержится требование одного ояда фрагментов .-.зо- бражения или позволяет получить промежуточную тетраду в случае, если: разво- ,

0 рачиваемое окно хочет занять фрагменты двух рядов. Информация с выходов блока 37 записывается в регистр 38 тетрады, откуда поступает на информационные входы второго демультиплексора 39, управление

5 работой которого осуществляет код, получаемый с четырех старших разрядов регистра 36. В результате промежуточная тетрада попадает на вход одного из определителей 40 - 43 номеров фрагментов. В том Cflysae, когда возникает требование в одном фрагменте и одного либо двух рядов начинает функционировать определитель 40, когда возникает требование в двух фрагментах одного либо двух рядов изображения начинает работать определитель 41, когда возникает требование в трех фрагментах одного либо двух рядов начинает работать определитель 42, и наконец функционирует определитель 43 в том случае, когда есть требование одного ряда либо всей рабочей области полиэкрана. Если обозначить промежуточную тетраду через СИ 02 Оз 04, второй разряд регистра требования фрагментов - через Об, получаемый байт на выходе формирователей - через Z$ Z Ze Zs Z4 Zs Z2 Zi, то логические выражения для построения функциональной схемы каждого из формирователей имеют следующий вид. Дня определителя 40:

Zi Qi;Z2 Qi-Q2;Z3 QrQ2-Q3; ZA QrQ2 -Оз -04; Z5 QrQs; Ze Z2 -Q5;Z7 Zs- Qs;Z8 Z4-Q5.

Для определителя 41:

, Z2 Zi + (Q2-Q3) -(QrQ2):Z3 ZA + ZrQ2-Q3; Z4 Zr (Q2-ОзНОз-04); Zs Z rOs: Ze Z2- Qs; Zi Zs -Qs; Za

Z4 -Q5.

Для определителя 42:

Q21 Q3iZ2 Qs- U4 -Zi + Z2; Z4 - 02-Q3-Q4-Zi; Zs Zi -Qs; Ze Z7 Zz-Qs: Za /a Qc

П.ля определителя 43:

Zi Л - /3 Z4 QrQ2 -03-04; Zs Z6 Z - 7.8 Zi -Qs.

Выходы определителей номеров фрагментов подключены к входам мультиплексо- ра 44, на управляющие входы которого поступает код с трех младших разрядов старшей тетрады регистра 36.

Формирователь 9 адреса буфера экранной памяти получает информацию о номе- pax занимаемых фрагментов создаваемого окна и определяет байт физического адреса в памяти изображения верхнего левого элемента окна. Точка, записанная по этому адресу в памяти экрана, изобразится в верхнем левом углу окна.

Блок 72 выбора ряда осуществляет выбор одного из рядов, где первый ряд описывается младшей тетрадой, а старшая тетрада описывает второй ряд. Каждый из фрагмен- тов имеет закрепленный за собой номер, а начальный адрес буфера экранной памяти непосредственно связан с начальным адресом фрагмента окна, имеющего наимень0

5

i

0

5

5

0

0

5 0

5

ший номер. Поэтому, если младшая тетрада отлична от ноля, то блок 72 выберет ее, в противном случае выбор будет сделан в пользу старшей тетрады регистра 71 номеров фрагментов. На вход формирователя 74 адреса поступает информация из регистра 73 ряда, а также однобитовая маска из блока 72. Если обозначить через Qi Q2 Оз CU тетраду, получаемую из регистра 73 ряда и через Qs маску, получаемую из блока 72, а через Ze 2.1 Z& Zs ZA Zs Z2 Zi байт физического адреса, получаемого на выходах 76 формирователя 74, то логические выражения построения формирователя имеют следующий вид:

Zi Z2 Оз, Zs .Qi;Q2; Z4 QrQrQa-CU; Zs QrQi + Z4; Ze Qi-Q2 + ZA Zi Ze Qs.

Если маска равна нулю и полученный на выходах 76 формирователя 74 байт отличен от ноля, то блок 1 управления для получения двухбайтного физического адреса выполняет операцию сложения с базовым адресом 0000 содержимого байта, если же маска равна единице и байт также отличен от ноля, то физический адрес будет получен путем сложения блоком 1 управления этого байта с базовым адресом 0260. Таким образом, получаемый на выходах 76 формирователя 74 байт является смещением соответствующего базового адреса.

Для организации работы блока 1 управления с остальными блоками предназначен формирователь 2 управляющих сигналов, в котором производятся выработки управляющих сигналов, позволяющих осуществить функционирование микропроцессорной системы. Такими сигналами являются следующие: ЗПЗУ, ЗПВВ, ЧТВВ, ЧТЗУ и ряд других. На информационные входы триггеров 87 - 89 поступает код слова состояния микропроцессора (МП), который записывается по синхросигналу с второго выхода блока 1, поступающего на вход 100 формирователя 2. Элементы ИЛИ 93 на основании состояния триггера 87 и первого выхода блока 1, поступающего на вход 98, вырабатывают сигналы ЗПЗУ (выход 105) и ЗПВВ (выход 106). Элементы ИЛИ 94 вырабатывают сигналы ЧТВВ (выход 107) и ЧТЗУ (выход 108) на основании состояний триггеров 88 и 89 и управляющего сигнала на входе 101, поступающего с пятого выхода блока 1.

На входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 95 по адресной шине (входы 102) поступает младшая часть адреса. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ вместе с сигналами от старшей части адреса, выходом триггера 92 подается на информационный вход триггера 92, на

второй вход которого поступает синхросигнал (вход 103). Прямой выход триггера 92 вырабатывает сигнал обнуления счетчика 17 в блоке 3. Сигнал занесения информации в

счетчик 17 вырабатывается с инверсного выхода триггера 91, на информационный вход которого поступает сигнал с выхода элемента И 97. На входы элемента И 97 поступает сигнал с инверсного выхода триггера 90 и сигнал подтверждение сигнала захвата шины данных (вход 104).

Для организации информационного обмена данными (как между блоками микропроцессорной системы контроллера, так и самым контроллером полиэкрана и объектом более высокого уровня) предназначен блок 6 сопряжения.

В блоке 6 группа 115 входов-выходов данных подключена к шине данных МП. Параллельный интерфейс 110 осуществляет связь с управляемой микро-ЭВМ через первую группу 118 информационных входов- выходов и с блоками контроллера через вторую группу 115 информационных входов-выходов. Сигналы ЧТВВ и ЗПВВ для управления чтением и записью по шинам (группам информационных входов-выходов) 118 и 115 поступают от формирователя 2 по входам 116 и 117.

Буферный регистр 111 служит для передачи установочных значений в блок 3 для счетчика 17. Буферный регистр 112 служит для передачи информации о границе фрагментов в регистры 29 и 30 старшей и младшей тетрады блока 7. Буферный регистр 113 передает информацию о номерах свободных фрагментов в блок 37 выбора тетрады. При обмене с блоками 3, 7 и 8 указанные буферные регистры являются портами ввода, а при обмене с МП - портами вывода.

Использование предлагаемого устройства (по сравнению с известными) повышает быстродействие по реализации функций многооконной машинной графики и является аппаратной поддержкой интерактивного режима работы ЭВМ.

Формула изобретения

Устройство для формирования изображения, содержащее блоки постоянной и оперативной памяти, блок сопряжения, формирователь управляющих сигналов и блок управления, первый, второй, третий и четвертый выходы которого соединены соответственно с первым стробирующим входом, входом управления записью, вторым стробирующим входом и управляющим входом формирователя управляющих сигналов, первый выход которого подключен к входам управления считыванием блоков постоянной и оперативной памяти, а второй,

5

10

15

20

25

30

35

40

45

50

5

третий и четвертый выходы соединены соответственно с входом управления записью блока оперативной памяти и входами управления записью и считыванием блока сопряжения, информационные входы-выходы первой группы которого являются входами- выходами устройства, а информационные входы-выходы второй группы соединены с входами-выходами группы блока оперативной памяти, выходами группы блока постоянной памяти, информационными входами группы формирователя управляющих сигналов и выходами первой группы блока управления, выходы второй группы которого соединены с адресными входами группы блоков оперативной и постоянной памяти, блока сопряжения и формирователя управляющих сигналов, синхровход которого соединен с синхровходами блоков управления и сопряжения и является синхровходом устройства, первым и вторым управляющими входами которого являются соответственно входы сигналов сброса и запроса блока управления, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержат вычислитель числа фрагментов изображения, вычислитель номеров фрагментов изображения, формирователь адреса, блок коммутации, управляющие входы первой и второй группы которого подключены соответственно к выходам групп.) формирователя управляющих сигналов i- выходом второй группы блока упрагч н1 - выходы первой группы и информациенн1 е входы первой группы блока коммутации подключены к входам-выходам группы блс ка оперативной памяти, а выходы вюрсй группы - к адресным входам группы формирователя управляющих спп а,ов и бло г оперативной памяти, синхровход Ьл.-з коммутации соединен с синхровходами вычислителя числа фрагментов изображения формирователя адреса и вычислителя HC ров фрагментов изображения и к синхровходу устройства, выходы гг0п и вычислителя числа фрагментов изображения соединены с информационными ми первой группы вычислителя номеров фрагментов изображения, выходы групгм которого подключены к информационном входам группы формирователя адреса, выходы группы которого соединены с выходами группы и информационными входами второй группы вычислителя номеров фрагментов изображения, информационными входами группы вычислителя числа фраг-, ментов изображения, входами-х,ходами второй группы блока сопряжения и информационными входами второй грулпь. блока коммутации, информационные зходы

третьей группы которого являются инфор- ми которого являются выходы третьей мационными входами устройства, выхода-группы блока коммутации.

V4tf от. 6/iQK.a. В

от Ахода- Y/J

53j S3z

Ф vf

JLJ

Сд

Я

V

57ц

3C

W &V |/

57j J72 57f

44

i/ Ф Ф

i ; i it, i

9,5

i r

I j Iffgg I Mi

т г

от SnoK.0. 7

42

-

r

70

|Ґ

т г

w с

Фаг А

ГОР 10J

Ч0Ъ

юг.

От бхода /J

103

От f/fffffa f

Wf

zQ-S-

+ 105 К 6/1 он у 5

10f

К 6локу 6

107)

Ю8 Кблокап Ъ,5

109

К блоку 3

Вход М.

т

по

гЈ

115

От блока 1

т

От блока 1

111

r4J

Вход

$ т

блока 2

т

7

Н h

К блоку 1

112

гЈ

Фиг. 7

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-01-11—Подача