I

Изобретение относится к автоматике и вычислительной технике и может быть использовано для визуального контроля параметров различных процессов .

Цель изобретения - расширение области применения устройства путем . формирования в реальном масштабе времени совмещенного в одном кадре изображения текущей и ретроспективной информации и быстропротекающих процессах.

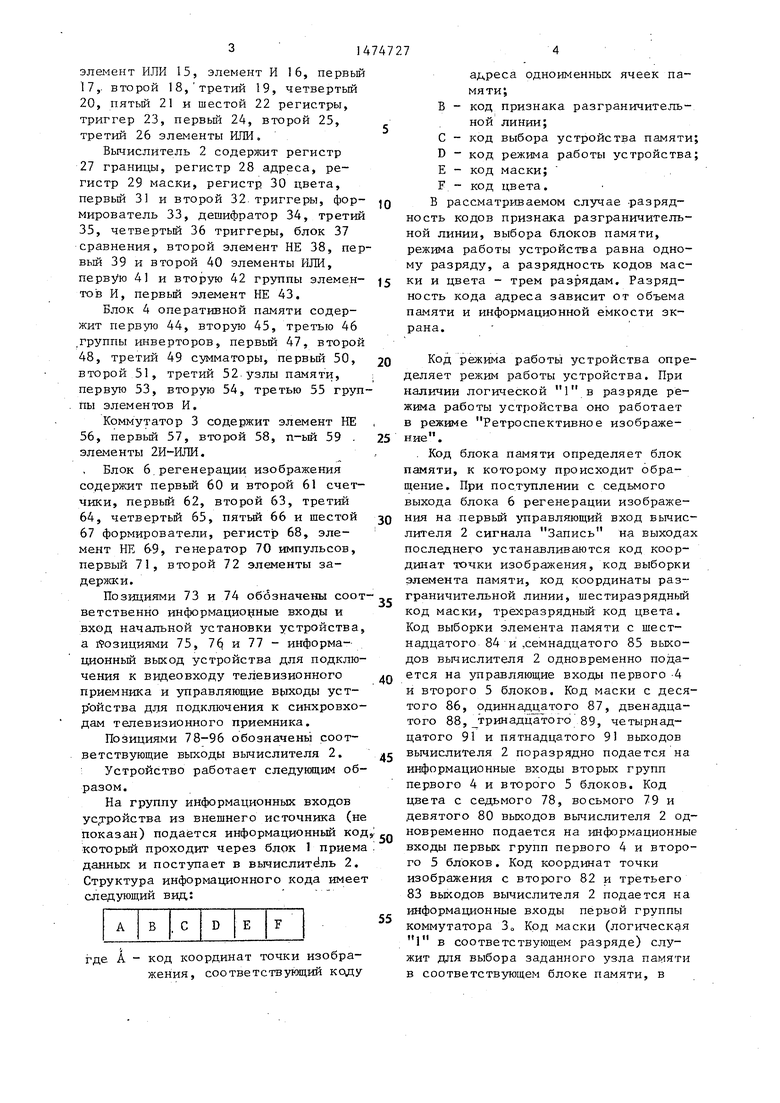

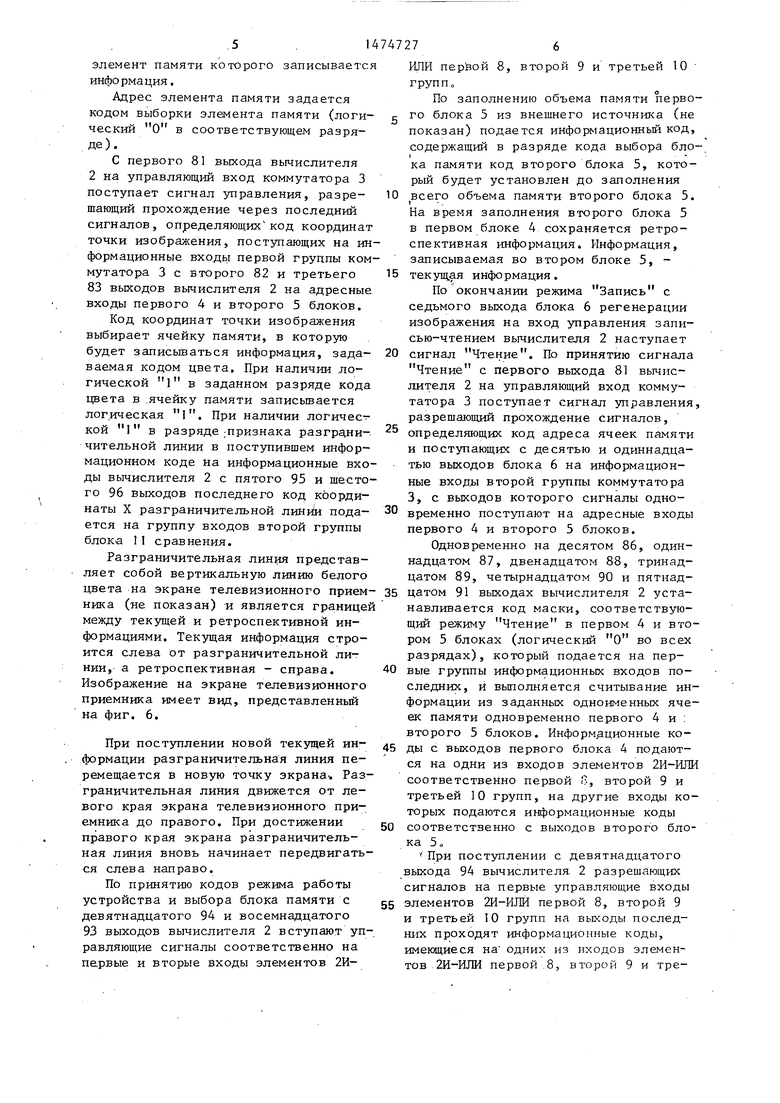

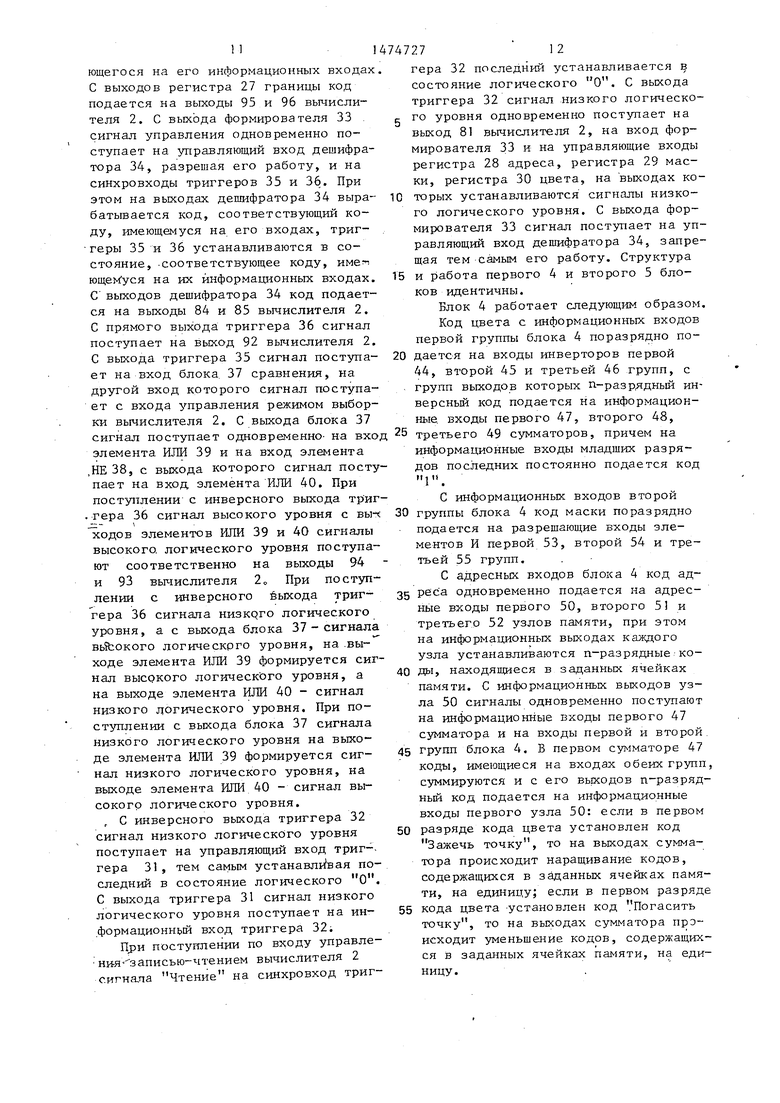

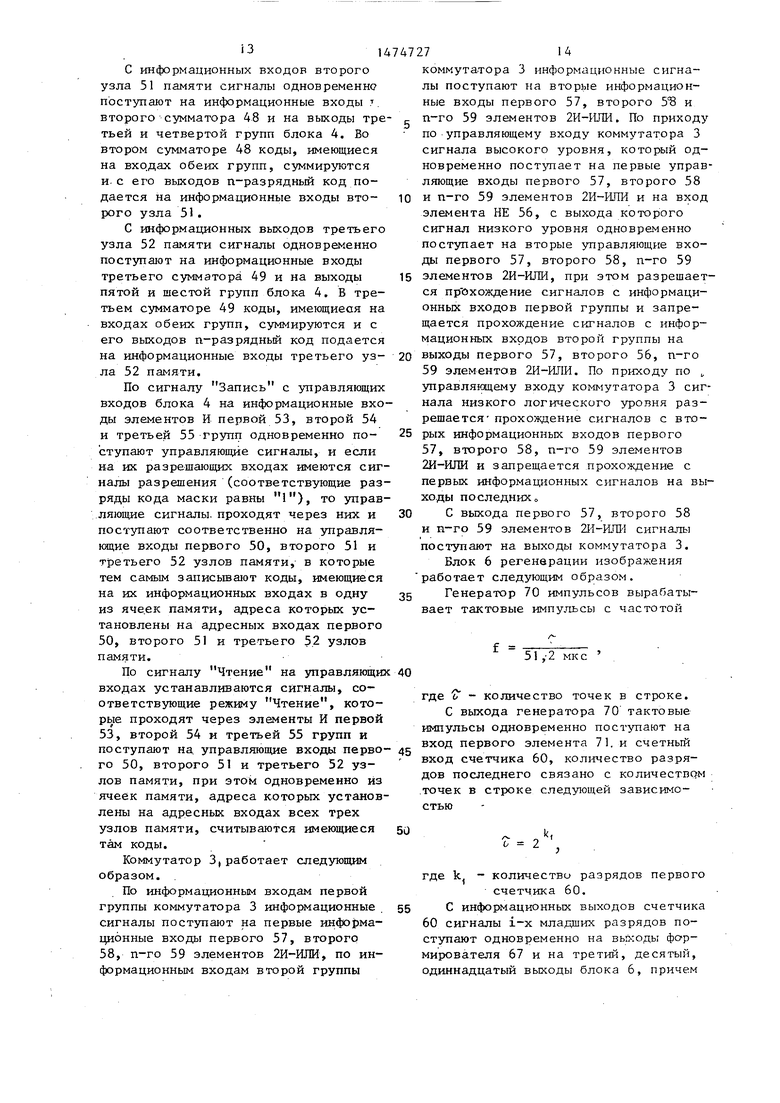

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - блок-схема вычисления; на фиг. 3 - блок-схема первого блока оперативной памяти;

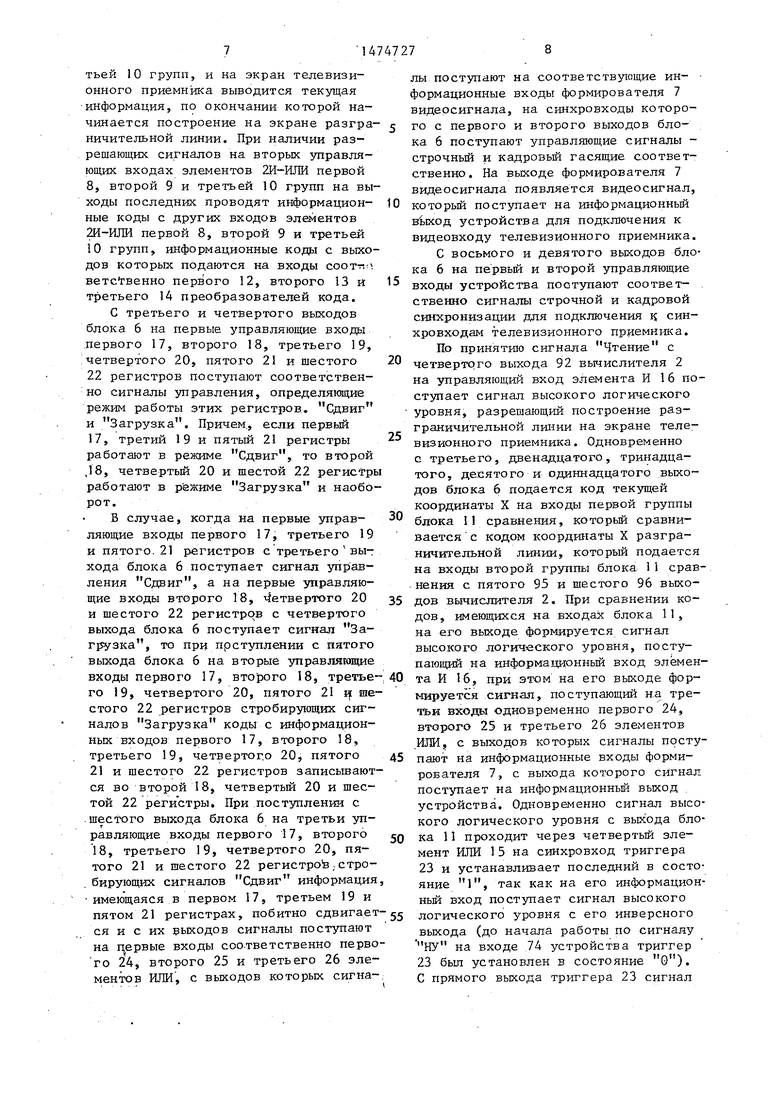

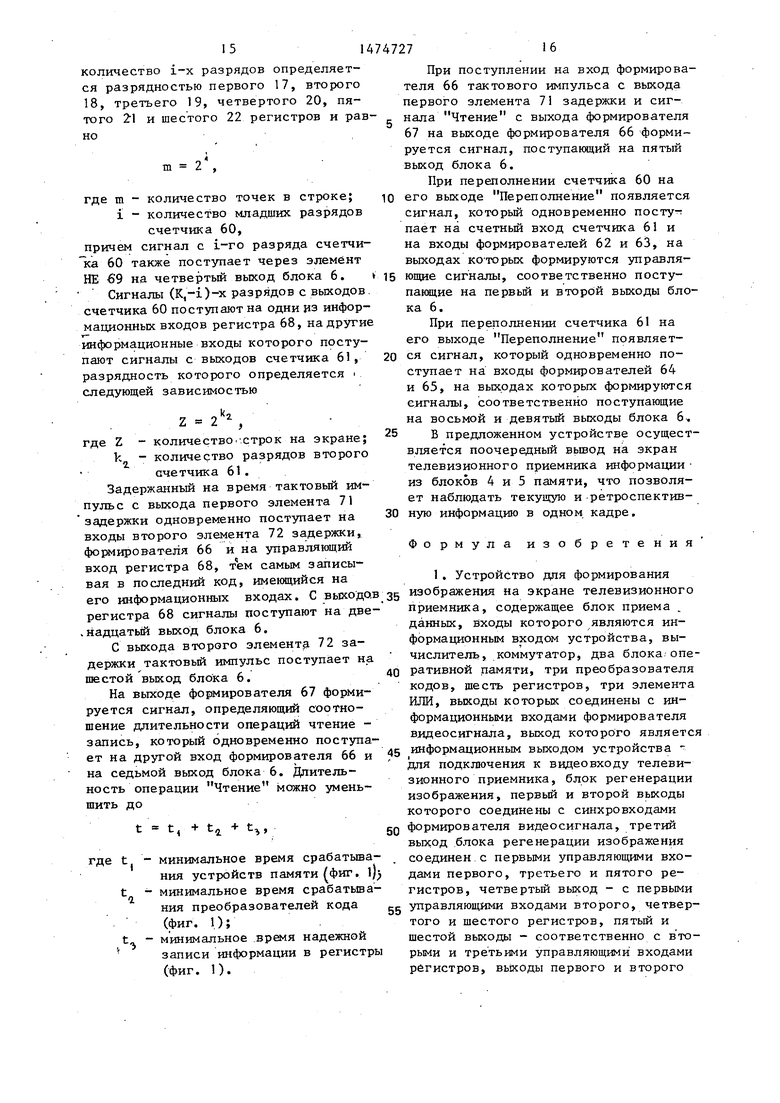

на фиг. 4 - блок-схема коммутатора; на фиг. 5 - блок-схема блока регенерации; на фиг. 6 - отображение на экране телевизионного приемника текущей и ретроспективной информации, хранящейся в блоках оперативной памяти.

Устройство содержит блок 1 приема данных, вычислитель 2, коммутатор 3, первый 4, второй 5 блоки оперативной памяти, блок 6 регенерации изображения, формирователь 7 видеосигнала, первую 8, вторую 9 и третью 10 группы элементов 2И-ИЛИ, блок 11 сравнения, первьй 12, второй 13 и третий 14 преобразователи кодов, четвертый

4 Јъ ГчЭ

элемент ИЛИ 15, элемент И 16, первьй 17, второй 18, третий 19, четвертый 20, пятьй 21 и шестой 22 регистры, триггер 23, первьй 24, второй 25, третий 26 элементы ИЛИ.

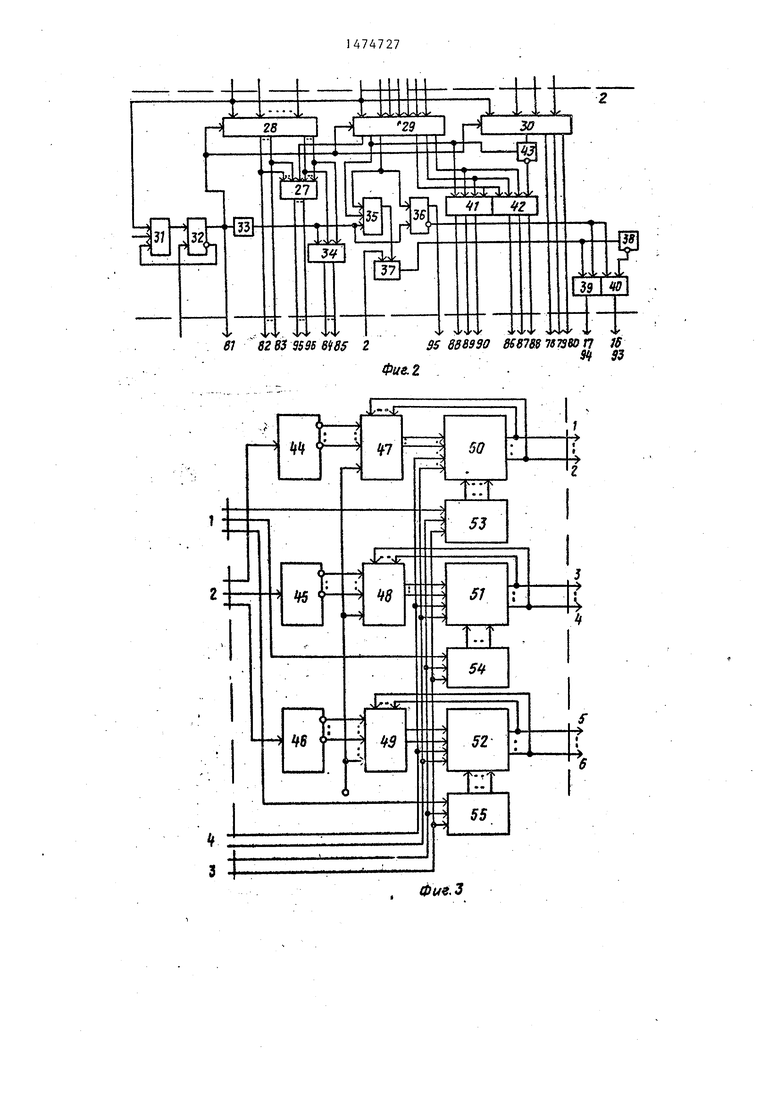

Вычислитель 2 содержит регистр 27 границы, регистр 28 адреса, регистр 29 маски, регистр 30 цвета, первьй 31 и второй 32 триггеры, формирователь 33, дешифратор 34, третий 35, четвертый 36 триггеры, блок 37 сравнения, второй элемент НЕ 38, первый 39 и второй 40 элементы ИЛИ, первую 41 и вторую 42 группы элементов И, первьй элемент НЕ 43.

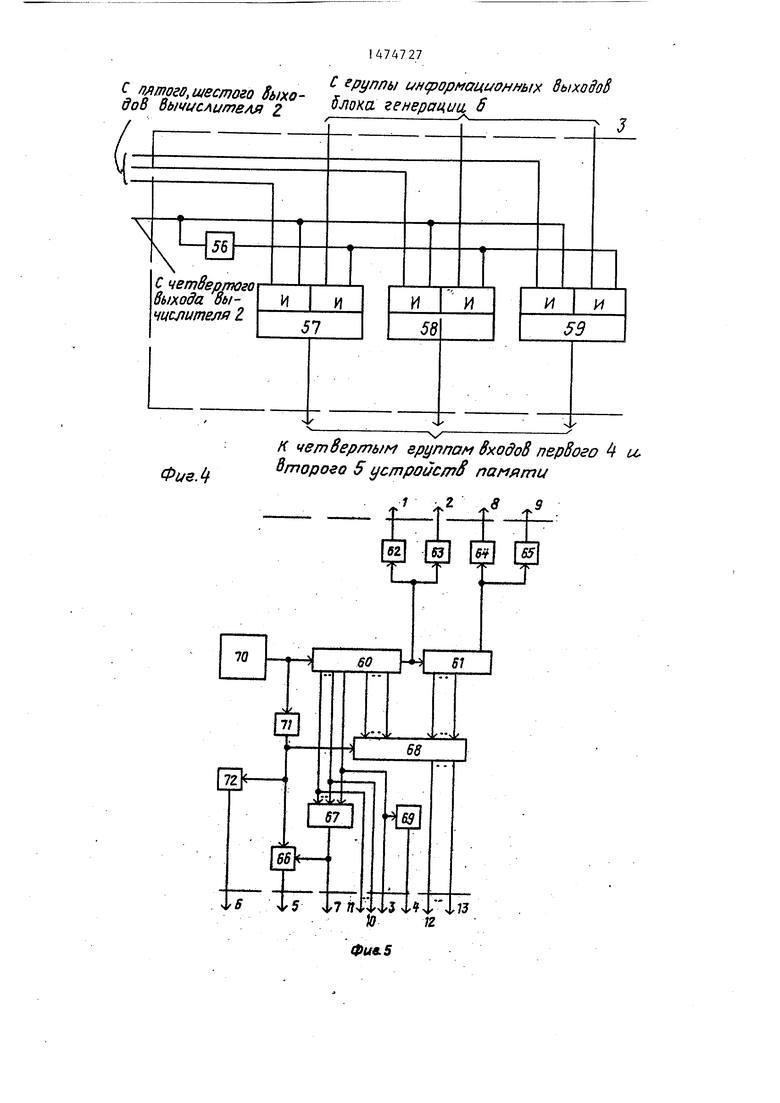

Блок 4 оперативной памяти содержит первую 44, вторую 45, третью 46 .группы инверторов, первьй 47, второй 48, третий 49 сумматоры, первьй 50, второй 51, третий 52 узлы памяти, первую 53, вторую 54, третью 55 группы элементов И.

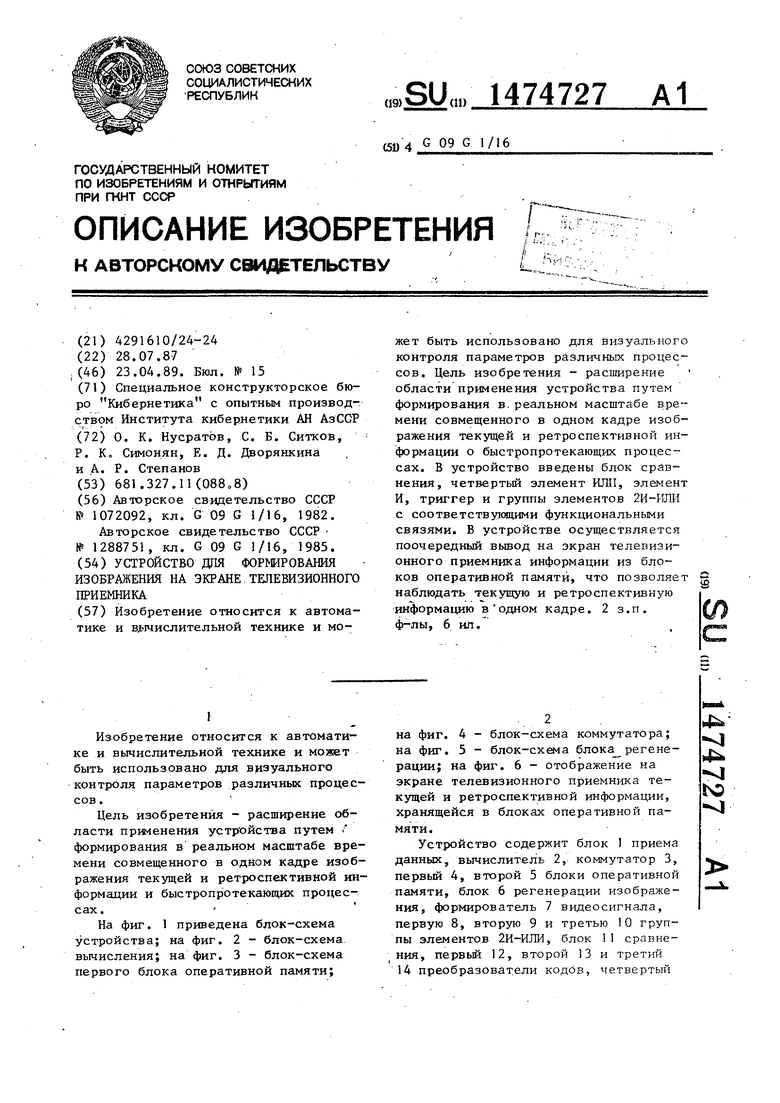

Коммутатор 3 содержит элемент НЕ 56, первьй 57, второй 58, п-ый 59 . элементы 2И-ИЛИ.

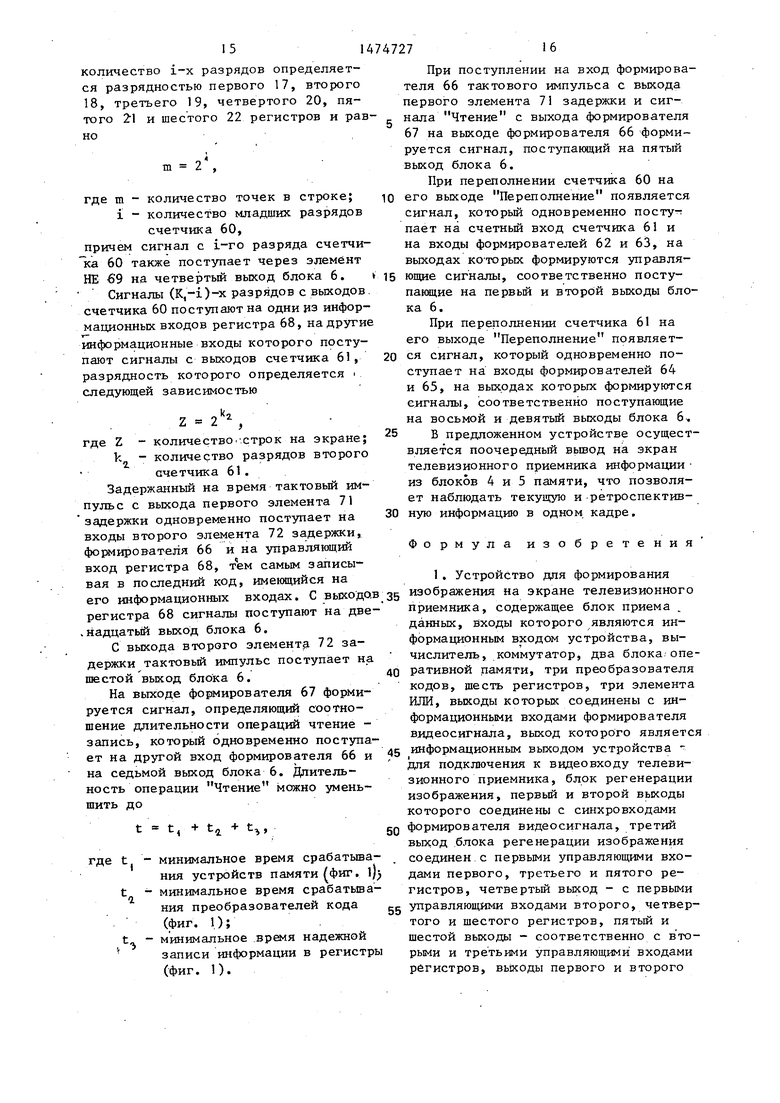

Блок 6 регенерации изображения содержит первьй 60 и второй 61 счетчики, первьй 62, второй 63, третий 64, четвертьй 65, пятый 66 и шестой 67 формирователи, регистр 68, элемент НЕ 69, генератор 70 импульсов, первый 71, второй 72 элементы задержки.

Позициями 73 и 74 обозначены соответственно информационные входы и вход начальной установки устройства, а позициями 75, 76, и 77 - информационный выход устройства для подключения к видеовходу телевизионного приемника и управляющие выходы уст- р ойства для подключения к синхровхо- дам телевизионного приемника.

Позициями 78-96 обозначены соответствующие выходы вычислителя 2.

Устройство работает следующим образом.

На группу информационных входов устройства из внешнего источника (не

0

5

0

5

В С D

Е F

адреса одноименных ячеек памяти;

код признака разграничительной линии;

код выбора устройства памяти; код режима работы устройства; код маски; код цвета. В рассматриваемом случае -разрядность кодов признака разграничительной линии, выбора блоков памяти, режима работы устройства равна одному разряду, а разрядность кодов мас- 5 ки и цвета - трем разрядам. Разрядность кода адреса зависит от объема памяти и информационной емкости экрана.

0Код режима работы устройства определяет режим работы устройства. При наличии логической 1 в разряде режима работы устройства оно работает в режиме Ретроспективное изображе5 ние.

Код блока памяти определяет блок памяти, к которому происходит обращение. При поступлении с седьмого выхода блока 6 регенерации изображения на первьй управляющий вход вычислителя 2 сигнала Запись на выходах последнего устанавливаются код координат точки изображения, код выборки элемента памяти, код координаты разграничительной линии, шеетиразрядный код маски, трехразрядньй код цвета. Код выборки элемента памяти с шестнадцатого 84 и .семнадцатого 85 выходов вычислителя 2 одновременно подается на управляющие входы первого 4 и второго 5 блоков. Код маски с десятого 86, одиннадцатого 87, двенадцатого 88, тринадцатого 89, четырнадцатого 91 и пятнадцатого 91 выходов вычислителя 2 поразрядно подается на информационные входы вторых групп первого 4 и второго 5 блоков. Код цвета с седьмого 78, восьмого 79 и девятого 80 выходов вычислителя 2 од

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Устройство для генерации векторов на индикаторе с растровой разверткой | 1980 |

|

SU922719A1 |

| Устройство для генерации векторов на индикаторе с черезстрочной разверткой | 1980 |

|

SU922718A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для формирования изображения | 1988 |

|

SU1575230A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1990 |

|

SU1718265A1 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| Декодер линейного кода | 1986 |

|

SU1432786A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для визуального контроля параметров различных процессов. Цель изобретения- расширение области применения устройства путем формирования в реальном масштабе времени совмещенного в одном кадре изображения текущей и ретроспективной информации о быстропротекающих процессах, которая достигается введением блока сравнения, четвертого элемента ИЛИ, элемента И, триггера, трех групп элементов 2И-ИЛИ с соответствующими функциональными связями. В устройстве осуществляется поочередный вывод на экран телевизионного приемника информации из блока оперативной памяти, что позволяет наблюдать текущую ретроспективную информацию в одном кадре. 2 з.п. ф-лы, 6 ил.

показан) подается информационный код ,0 повременно подается на информационные

который проходит через блок 1 приема данных и поступает в вычислитель 2. Структура информационного кода имеет следующий вид:

входы первых групп первого 4 и второго 5 блоков. Код координат точки изображения с второго 82 и третьего 83 выходов вычислителя 2 подается на информационные входы первой группы коммутатора 30 Код маски (логическая 1 в соответствующем разряде) служит для выбора заданного узла памяти в соответствующем блоке памяти, в

где А - код координат точки изображения, соответствующий коду

повременно подается на информационные

входы первых групп первого 4 и второго 5 блоков. Код координат точки изображения с второго 82 и третьего 83 выходов вычислителя 2 подается на информационные входы первой группы коммутатора 30 Код маски (логическая 1 в соответствующем разряде) служит для выбора заданного узла памяти в соответствующем блоке памяти, в

в соответствующем разряэлемент памяти которого записывается информация.

Адрес элемента памяти задается кодом выборки элемента памяти (логический О де).

С первого 81 выхода вычислителя 2 на управляющий вход коммутатора 3 поступает сигнал управления, разрешающий прохождение через последний сигналов, определяющих код координат точки изображения, поступающих на информационные входы первой группы коммутатора 3 с второго 82 и третьего 15 текущая информация.

83 выходов вычислителя 2 на адресные По окончании режима Запись с

входы первого 4 и второго 5 блоков. Код координат точки изображения выбирает ячейку памяти, в которую

будет записываться информация, зада- 20 сигнал Чтение. По принятию сигнала

ваемая кодом цвета. При наличии логической 1 в заданном разряде кода цвета в ячейку памяти записывается логическая 1. При наличии логической 1 в разряде признака разграничительной линии в поступившем информационном коде на информационные входы вычислителя 2 с пятого 95 и шестого 96 выходов последнего код координаты X разграничительной линии подается на группу входов второй группы блока 11 сравнения.

Разграничительная линия представОдновременно на десятом 86, одиннадцатом 87, двенадцатом 88, тринадцатом 89, четырнадцатом 90 и пятнадщий режиму Чтение в первом 4 и втором 5 блоках (логический О во всех

ляет собой вертикальную линию белого

цвета на экране телевизионного прием- 35 цатом 91 выходах вычислителя 2 устаника (не показан) и является границей навливается код маски, соответствуюмежду текущей и ретроспективной информациями. Текущая информация строразрядах), который подается на пер- 40 вые группы информационных входов последних, и выполняется считывание информации из заданных одноименных ячеек памяти одновременно первого 4 и второго 5 блоков. Информационные ко- 45 ды с выходов первого блока 4 подаются на одни из входов элементов 2И-ИЛИ соответственно первой 8, второй 9 и третьей 10 групп, на другие входы которых подаются информационные коды соответственно с выходов второго блоится слева от разграничительной линии, а ретроспективная - справа. Изображение на экране телевизионного приемника имеет вид, представленный на фиг. 6.

При поступлении новой текущей информации разграничительная линия перемещается в новую точку экрана-. Разграничительная линия движется от левого края экрана телевизионного приемника до правого. При достижении правого края экрана разграничительная линия вновь начинает передвигаться слева направо.

По принятию кодов режима работы устройства и выбора блока памяти с девятнадцатого 94 и восемнадцатого 93 выходов вычислителя 2 вступают управляющие сигналы соответственно на первые и вторые входы элементов 2И50

ка 5 о

При поступлении с девятнадцатого выхода 94 вычислителя 2 разрешающих сигналов на первые управляющие входы 55 элементов 2И-ИЛИ первой 8, второй 9 и третьей 10 групп на выходы последних проходят информационные коды, имеющиеся на одних ия входов элементов 2И-ИЛИ первой 8, второй 9 и тре

47276

ИЛИ первой 8, второй 9 и третьей 10 трупп„

По заполнению объема памяти перво- с го блока 5 из внешнего источника (не показан) подается информационный код, содержащий в разряде кода выбора блока памяти код второго блока 5, который будет установлен до заполнения 10 всего объема памяти второго блока 5. На время заполнения второго блока 5 в первом блоке 4 сохраняется ретроспективная информация. Информация, записываемая во втором блоке 5, седьмого выхода блока 6 регенерации изображения на вход управления записью-чтением вычислителя 2 наступает

5

0

Чтение с первого выхода 81 вычислителя 2 на управляющий вход коммутатора 3 поступает сигнал управления, разрешающий прохождение сигналов, определяющих код адреса ячеек памяти и поступающих с десятью и одиннадцатью выходов блока 6 на информационные входы второй группы коммутатора 3, с выходов которого сигналы одновременно поступают на адресные входы первого 4 и второго 5 блоков.

Одновременно на десятом 86, одиннадцатом 87, двенадцатом 88, тринадцатом 89, четырнадцатом 90 и пятнадщий режиму Чтение в первом 4 и втором 5 блоках (логический О во всех

навливается код маски, соответствуюразрядах), который подается на пер- вые группы информационных входов последних, и выполняется считывание информации из заданных одноименных ячеек памяти одновременно первого 4 и второго 5 блоков. Информационные ко- ды с выходов первого блока 4 подаются на одни из входов элементов 2И-ИЛИ соответственно первой 8, второй 9 и третьей 10 групп, на другие входы которых подаются информационные коды соответственно с выходов второго бло

ка 5 о

При поступлении с девятнадцатого выхода 94 вычислителя 2 разрешающих сигналов на первые управляющие входы элементов 2И-ИЛИ первой 8, второй 9 и третьей 10 групп на выходы последних проходят информационные коды, имеющиеся на одних ия входов элементов 2И-ИЛИ первой 8, второй 9 и третьей 10 групп, и на экран телевизионного приемника выводится текущая информация, по окончании которой начинается построение на экране разгра- ничительной линии. При наличии разрешающих сигналов на вторых управляющих входах элементов 2И-ИЛИ первой 8, второй 9 и третьей 10 групп на выходы последних проводят информацией- ные коды с других входов элементов 2И-ИЛИ первой 8, второй 9 и третьей 10 групп, информационные коды с выходов которых подаются на входы COOT-. % ветственно первого 12, второго 13 и третьего 14 преобразователей кода. С третьего и четвертого выходов блока 6 на первые управляющие входы первого 17, второго 18, третьего 19, четвертого 20, пятого 21 и шестого 22 регистров поступают соответственно сигналы управления, определяющие режим работы этих регистров. Сдвиг и Загрузка. Причем, если первый

17,третий 19 и пятый 21 регистры работают в режиме Сдвиг, то второй ,18, четвертый 20 и шестой 22 регистры работают в режиме Загрузка и наоборот.

В случае, когда на первые управ- ляющие входы первого 17, третьего 19 и пятого 21 регистров с третьего выхода блока 6 поступает сигнал управления Сдвиг, а на первые управляющие входы второго 18, Четвертого 20 и шестого 22 регистров с четвертого выхода блока 6 поступает сигнал Загрузка, то при прступлении с пятого выхода блока 6 на вторые управляющие входы первого 17, второго 18, третье- го 19, четвертого 20, пятого 21 щ шестого 22 регистров стробирующих сигналов Загрузка коды с информационных входов первого 17, второго 18, третьего 19, четвертого 20, пятого 21 и шестого 22 регистров записываются во второй 18, четвертый 20 и шестой 22 регистры. При поступлении с шестого выхода блока 6 на третьи управляющие входы первого 17, второго

18,третьего 19, четвертого 20, пятого 21 и шестого 22 регистров,стробирующих сигналов Сдвиг информация, имеющаяся в первом 17, третьем 19 и пятом 21 регистрах, побитно сдвигается и с их выходов сигналы поступают

на цервые входы соответственно первого 24, второго 25 и третьего 26 элементов ИЛИ, с выходов которых сигналы поступают на соответствующие информационные входы формирователя 7 видеосигнала, на синхровходы которого с первого и второго выходов блока 6 поступают управляющие сигналы - строчный и кадровый гасящие соответственно. На выходе формирователя 7 видеосигнала появляется видеосигнал, который поступает на информационный устройства для подключения к видеовходу телевизионного приемника.

С восьмого и девятого выходов блока 6 на первьй и второй управляющие входы устройства поступают соответственно сигналы строчной и кадровой синхронизации для подключения к. син- хровходам телевизионного приемника.

По принятию сигнала Чтение с четвертого выхода 92 вычислителя 2 на управляющий вход элемента И 16 поступает сигнал высокого логического уровня, разрешающий построение разграничительной линии на экране телевизионного приемника. Одновременно с третьего, двенадцатого, тринадцатого, десятого и одиннадцатого выходов блока 6 подается код текущей координаты X на входы первой группы блока 11 сравнения, которьй сравнивается с кодом координаты X разграничительной линии, которьй подается на входы второй группы блока 11 сравнения с пятого 95 и шестого 96 выходов вычислителя 2. При сравнении кодов, имеющихся на входах блока 11, на его выходе формируется сигнал высокого логического уровня, поступающий на информационный вход элемента И 16, при этом на его выходе формируется сигнал, поступающий на третьи входы одновременно первого 24, второго 25 и третьего 26 элементов ИЛИ, с выходов которых сигналы поступают на информационные входы формирователя 7, с выхода которого сигнал поступает на информационный выход устройства. Одновременно сигнал высокого логического уровня с выхода блока 1 1 проходит через четвертый элемент ИЛИ 15 на синхровход триггера 23 и устанавливает последний в состояние 1, так как на его информационный вход поступает сигнал высокого логического уровня с его инверсного выхода (до начала работы по сигналу НУ на входе 74 устройства триггер 23 был установлен в состояние О). С прямого выхода триггера 23 сигнал

поступает на вход управления режимом выборки вычислителя 2. При этом в последнем на девятнадцатом 94 и восемнадцатом 93 выходах изменяются третий и четвертый управляющие сигналы, разрешая вывод содержимого объема памяти второго блока 5 на экран телевизионного приемника, и на нем строится ретроспективное изображение. При поступлении с первого выхода блока 6 на вход четвертого элемента ИЛИ 15 строчного гасящего импульса на выходе последнего формируется сигнал,, поступающий на синхро- вход триггера 23 и устанавливающий его в состояние О. После этого сигнал с прямого выхода триггера 23 поступает на вход управления выборки

25

вычислителя 2 и устанавливает в пер- 20 трех младших разрядов регистра 29 воначальное состояние третий и чет-маски, проходит через элемент И первертый управляющие сигналы, вырабатывающиеся на выходах 94 и 93 вычислителя 2.

Следующая строка выводится на экран телевизионного приемника аналогично предыдущей

Вычислитель 2 работает следующим образом.

С информационных входов вычислите- 30 кого уровня информационный код, пода- ля 2 на информационные входы регистра ющийся с трех младших разрядов регистра 29 маски, проходит через элементы И 42 группы на выходы 86 - 88 вычислителя 2, а на выходах -элементов 35 И первой 41 группы формируются сигвой 41 группы на выходы 89-91 вычислителя 2, а на выходах элементов И второй 42 группы формируются сигналы низкого логического уровня, которые поступают на выходы 86 - 88 вычислителя 2. При поступлении выхода разряда кода выбора блока памяти регистра 29 маски сигнала низкого логичес28 адреса, регистра 29 маски, регистра 30 цвета поразрядно подается п- раэрядный код.

Одновременно на синхровход триггера 31, синхровходы регистра 28 адреса, регистра 29 маски, регистра 30 цвета по первому информационному входу вычислителя 2 поступает синхросигнал, тем самым записывая в регистр 28 адреса, регистр 29 маски, регистр 30 цвета имеющиеся,на их информационных входах коды и устанавливая триггер 31 в состояние логической 1

налы низкого логического уровня, которые поступают на выходы 89-91 вычислителя 2.

С выхода разряда кода режима рабо- 40 ты устройства сигнал высокого логического уровня поступает одновременно на управляющий вход триггера 35, устанавливая его в состояние логической 1, и информационный вход тригге(на информационный вход первого триг- 45 ра 36.

гера 31 постоянно подается сигнал высокого логического уровня).

Выход триггера 31 подключен к информационному входу триггера 32. При поступлении по входу управления записью-чтением вычислителя 2 сигнала Запись на синхровход триггера 32 . последний устанавливается в состояние логической 1 и с его прямого выхода сигнал высокого логического уровня одновременно поступает на четвертый выход вычислителя 2, на вход формирователя 33 и управляющие входы регистра 28 адреса, регистра 29

маски, регистра 30 цвета, тем самым разрешая выдачу на их выходы хранящихся там кодов.° С выхода регистра 30 код цвета поразрядно подается на выходы 78, 69 и 80 вычислителя 2.

С выхода разряда кода выбора блока памяти регистра 29 маски сигнал одновременно поступает на информационный вход триггера 35, управляющие входы элементов первой 41 группы и вход элемента НЕ 43, с выхода которого сигнал поступает на управляющие вхо5 ды элементов И второй 42 группы. При поступлении с выхода разряда кода выбора блока памяти регистра 29 маски сигнала высокого логического уровня информационный код, подающийся с

вой 41 группы на выходы 89-91 вычислителя 2, а на выходах элементов И второй 42 группы формируются сигналы низкого логического уровня, которые поступают на выходы 86 - 88 вычислителя 2. При поступлении выхода разряда кода выбора блока памяти регистра 29 маски сигнала низкого логичесра 36.

налы низкого логического уровня, которые поступают на выходы 89-91 вычислителя 2.

С выхода разряда кода режима рабо- ты устройства сигнал высокого логического уровня поступает одновременно на управляющий вход триггера 35, устанавливая его в состояние логической 1, и информационный вход триггеС выходов регистра 28 адреса код одновременно подается на выходы 82 и 83 вычислителя 2 и на информационные входы первой группы 27 регистра границы. С информационных выходов регистра 28 адреса код одновременно подается на входы дешифратора 34 и на информационные входы второй группы регистра 27, на управляющий вход которого с выхода разряда кода признака разграничительной линии регистра 29 маски поступает сигнал высокого логического уровня и разрешает запись в регистр 27 границы кода, имеющегося на его информационных входах С выходов регистра 27 границы код подается на выходы 95 и 96 вычислителя 2. С выхода формирователя 33 сигнал управления одновременно поступает на управляющий вход дешифратора 34, разрешая его работу, и на синхровходы триггеров 35 и 36. При этом на выходах дешифратора 34 вырабатывается код, соответствующий коду, имеющемуся на его входах, триггеры 35 и 36 устанавливаются в состояние, соответствующее коду, име-ч ющемуся на их информационных входах. С выходов дешифратора 34 код подается на выходы 84 и 85 вычислителя 2. С прямого выхода триггера 36 сигнал поступает на выход 92 вычислителя 2. С выхода триггера 35 сигнал поступает на вход блока 37 сравнения, на другой вход которого сигнал поступает с входа управления режимом выборки вычислителя 2. С выхода блока 37

сигнал поступает одновременно на вход 25 третьего 49 сумматоров, причем на элемента ИЛИ 39 и на вход элементаинформационные входы младших разря,НЕ 38, с выхода которого сигнал поступает на вход элемента ИЛИ 40. При поступлении с инверсного выхода триг-С информационных входов второй

.гера 36 сигнал высокого уровня с вы 30 группы блока 4 код маски поразрядно

дов последних постоянно подается код м 1 it

ходов элементов ИЛИ 39 и 40 сигналы высокого логического уровня поступают соответственно на выходы 94 и 93 вычислителя 2„ При поступлении с инверсного выхода триггера 36 сигнала низкрго логического уровня, а с выхода блока 37 - сигнала высокого логического уровня, на выходе элемента ИЛИ 39 формируется сигнал высокого логического уровня, а на выходе элемента ИЛИ 40 - сигнал низкого логического уровня. При поступлении с выхода блока 37 сигнала низкого логического уровня на выходе элемента ИЛИ 39 формируется сигнал низкого логического уровня, на выходе элемента ИЛИ 40 - сигнал высокого логического уровня.

г С инверсного выхода триггера 32 сигнал низкого логического уровня поступает на управляющий вход триггера 31, тем самым устанавливая последний в состояние логического О. С выхода триггера 31 сигнал низкого логического уровня поступает на информационный вход триггера 32.

При поступлении по входу управле- ния- записьк -чтением вычислителя 2 Чтение на синхровход триггера 32 последний устанавливается в состояние логического О. С выхода триггера 32 сигнал низкого логическо- го уровня одновременно поступает на выход 81 вычислителя 2, на вход формирователя 33 и на управляющие входы регистра 28 адреса, регистра 29 маски, регистра 30 цвета, на выходах которых устанавливаются сигналы низкого логического уровня. С выхода формирователя 33 сигнал поступает на управляющий вход дешифратора 34, запрещая тем самым его работу. Структура

5 и работа первого 4 и второго 5 блоков идентичны.

Блок 4 работает следующим образом. Код цвета с информационных входов первой группы блока 4 поразрядно по0 дается на входы инверторов первой 44, второй 45 и третьей 46 групп, с групп выходов которых n-разрядный инверсный код подается на информационные входы первого 47, второго 48,

5 третьего 49 сумматоров, причем на информационные входы младших разряС информационных входов второй

дов последних постоянно подается код м 1 it

подается на разрешающие входы элементов И первой 53, второй 54 и третьей 55 групп.

С адресных входов блока 4 код адреса одновременно подается на адресные входы первого 50, второго 5 и третьего 52 узлов памяти, при этом на информационных выходах каждого узла устанавливаются n-разрядные коДы, находящиеся в заданных ячейках памяти. С информационных выходов узла 50 сигналы одновременно поступают на информационные входы первого 47 сумматора и на входы первой и второй

групп блока 4. В первом сумматоре 47 коды, имеющиеся на входах обеих групп, суммируются и с его выходов n-разрядный код подается на информационные входы первого узла 50: если в первом

разряде кода цвета установлен код Зажечь точку, то на выходах сумматора происходит наращивание кодов, содержащихся в заданных ячейках памяти, на единицу; если в первом разряде

кода цвета установлен код Погасить точку, то на выходах сумматора происходит уменьшение кодов, содержащихся в заданных ячейках памяти, на единицу.

С информационных входов второго узла 51 памяти сигналы одновременна поступают на информационные входы т второго сумматора 48 и на выходы тре тьей и четвертой групп блока 4. Во втором сумматоре 48 коды, имеющиеся на входах обеих групп, суммируются и с его выходов n-разрядный код подается на информационные входы вто- рого узла 51.

С информационных выходов третьего узла 52 памяти сигналы одновременно поступают на информационные входы третьего сумматора 49 и на выходы

пятой и шестой групп блока 4. В третьем сумматоре 49 коды, имеющиеая на входах обеих групп, суммируются и с его выходов n-разрядный код подается на информационные входы третьего уз- ла 52 памяти.

По сигналу Запись с управляющих входов блока 4 на информационные входы элементов И первой 53, второй 54 и третьей 55 групп одновременно по- ступают управляющие сигналы, и если на их разрешающих входах имеются сигналы разрешения (соответствующие разряды кода маски равны 1), то управляющие сигналы, проходят через них и поступают соответственно на управляющие входы первого 50, второго 51 и третьего 52 узлов памяти, в которые тем самым записывают коды, имеющиеся на их информационных входах в одну из ячеек памяти, адреса которых установлены на адресных входах первого 50, второго 51 и третьего 52 узлов памяти.

По сигналу Чтение на управляющих входах устанавливаются сигналы, соответствующие режиму Чтение, которые проходят через элементы И первой 53, второй 54 и третьей 55 групп и поступают на управляющие входы перво- го 50, второго 51 и третьего 52 узлов памяти, при этом одновременно из ячеек памяти, адреса которых установлены на адресных входах всех трех узлов памяти, считываются имеющиеся там коды.

Коммутатор 3(работает следующим образом.

По информационным входам первой группы коммутатора 3 информационные сигналы поступают на первые информационные входы первого 57, второго 58, п-го 59 элементов 2И-ИЛИ, по информационным входам второй группы

коммутатора 3 информационные сигналы поступают на вторые информационные входы первого 57, второго 5°8 и п-го 59 элементов 2И-ИЛИ. По приходу по управляющему входу коммутатора 3 сигнала высокого уровня, который одновременно поступает на первые управляющие входы первого 57, второго 58 и п-го 59 элементов 2И-ШТИ и на вход элемента НЕ 56, с выхода которого сигнал низкого уровня одновременно поступает на вторые управляющие входы первого 57, второго 58, п-го 59 элементов 2И-ИЛИ, при этом разрешается прохождение сигналов с информационных входов первой группы и запрещается прохождение сигналов с информационных входов второй группы на выходы первого 57, второго 56, п-го 59 элементов 2И-ИЛИ. По приходу по „ управляющему входу коммутатора 3 сигнала низкого логического уровня разрешается1 прохождение сигналов с вторых информационных входов первого 57, второго 58, п-го 59 элементов 2И-ИЛИ и запрещается прохождение с первых информационных сигналов на выходы последних о

С выхода первого 57, второго 58 и п-го 59 элементов 2И-ИЛИ сигналы поступают на выходы коммутатора 3.

Блок 6 регенерации изображения работает следующим образом.

Генератор 70 импульсов вырабатывает тактовые импульсы с частотой

f

51,-2 мкс

где о - количество точек в строке. С выхода генератора 70 тактовые импульсы одновременно поступают на вход первого элемента 71. и счетный вход счетчика 60, количество разрядов последнего связано с количеством точек в строке следующей зависимостью

Ј 2

kt

где k - количество разрядов первого

счетчика 60.

С информационных выходов счетчика 60 сигналы 1-х младших разрядов поступают одновременно на выходы формирователя 67 и на третий, десятый, одиннадцатый выходы блока 6, причем

15147

количество i-x разрядов определяется разрядностью первого 17, второго 18, третьего 19, четвертого 20, пятогоно

21 и шестого 22 регистров и рав

m - 2 ,

где m - количество точек в строке; i - количество младших разрядов

счетчика 60,

причем сигнал с 1-го разряда счетчика 60 также поступает через элемент НЕ 69 на четвертый выход блока 6.

Сигналы (K,-i)-x разрядов с выходов счетчика 60 поступают на одни из информационных входов регистра 68, на другие информационные входы которого поступают сигналы с выходов счетчика 61, разрядность которого определяется следующей зависимостью

Z 2

где Z - количество строк на экране; k - количество разрядов второго счетчика 61.

25 В предложенном устройстве осуществляется поочередный вывод на экран телевизионного приемника информации из блоков 4 и 5 памяти, что позволяет наблюдать текущую и ретроспектив30 ную информацию в одном кадре.

Формула изобретения 1. Устройство для формирования

Задержанный на время тактовый импульс с выхода первого элемента 71 задержки одновременно поступает на входы второго элемента 72 задержки, формирователя 66 и на управляющий вход регистра 68, тем самым записывая в последний код, имеющийся на его информационных входах. С выходов 35 изображения на экране телевизионного регистра 68 сигналы поступают на две- приемника, содержащее блок приема .

данных, входы которого являются информационным входом устройства, вычислитель, коммутатор, два блока опе- 40 ративной памяти, три преобразователя кодов, шесть регистров, три элемента ИЛИ, выходы которых соединены с информационными входами формирователя видеосигнала, выход которого является 45 информационным выходом устройства - для подключения к видеовходу телевизионного приемника, блок регенерации изображения, первый и второй выходы которого соединены с синхровходами

: t + t4 + t,QQ формирователя видеосигнала, третий

выход бпока регенерации изображения

-минимальное время срабатыва- соединен с первыми управляющими вхо- ния устройств памяти (фиг. 1)) дами первого, третьего и пятого ре-минимальное время срабатыва- гистров, четвертый выход - с первыми ния преобразователей кода ,.,. управляющими входами второго, четвер- (фиг. 1);того и шестого регистров, пятый и

-минимальное время надежнойшестой выходы - соответственно с вто- записи информации в регистры рыми и третьими управляющими входами (фиг. 1).регистров, выходы первого и второго

.надцатый выход блока 6.

С выхода второго элемента 72 задержки тактовый импульс поступает на шестой выход блока 6.

На выходе формирователя 67 формируется сигнал, определяющий соотношение длительности операций чтение - запись, который одновременно поступает на другой вход формирователя 66 и на седьмой выход блока 6. Длительность операции Чтение можно уменьшить до

где t

16

При поступлении на вход формирователя 66 тактового импульса с выхода первого элемента 71 задержки и сигнала Чтение с выхода формирователя 67 на выходе формирователя 66 формируется сигнал, поступающий на пятый выход блока 6.

При переполнении счетчика 60 на

его выходе Переполнение появляется сигнал, который одновременно поступает на счетный вход счетчика 61 и на входы формирователей 62 и 63, на выходах которых формируются управляющие сигналы, соответственно поступающие на первьй и второй выходы блока 6.

При переполнении счетчика 61 на его выходе Переполнение появляется сигнал, который одновременно поступает на входы формирователей 64 и 65, на выходах которых формируются сигналы, соответственно поступающие на восьмой и девятый выходы блока 6.

В предложенном устройстве осуществляется поочередный вывод на экран телевизионного приемника информации из блоков 4 и 5 памяти, что позволяет наблюдать текущую и ретроспективную информацию в одном кадре.

изображения на экране телевизионного приемника, содержащее блок приема .

Формула изобретения 1. Устройство для формирования

изображения на экране телевизионного приемника, содержащее блок приема .

1 7

регистров подключены к первому и второму входам первого элемента ИЛИ, выходы третьего и четвертого регист- ров - к первому и второму входам второго элемента ИЛИ, выходы пятого и шестого регистров - к первому и второму входам третьего элемента ИЛИ, выходы первого преобразователя кодов соединены с информационными входами первого и второго регистров, выходы второго преобразователя кодов - с информационными входами третьего и четвертого регистров, выходы третьего преобразователя кодов - с информационными входами пятого и шестого регистров, первый выход вычислителя соединен с управляющим входом коммутатора адреса, а второй и .третий выходы - к информационным входам первой группы коммутатора адреса, седьмой выход блока регенерации изображения соединен с входом управления записью-чтением вычислителя, а восьмой и девятый выходы являются управляющими выходами устройства для подключения к синхровходам телевизионного приемника, десятый и одиннадцатые выходы подключены к информационным входам второй группы коммутатора адреса, выходы которого соединены с адресными входами блоков оперативной памяти, информационные входы вычислителя соединены с вьЕходами блока приема данных, отличающееся тем, чтоэ с целью расши- рения области применения устройства путем формирования в реальном масштабе времени совмещенного в одном

4

кадре изображения текущей и ретроспе- 40 ры адреса, маски и цвета, информа- ктивной информации о быстропротекаю-ционные входы и синхровходы которых

щих процессах, оно содержит три группы элементов 2И - ИЛИ, блок сравнеи синхровход первого триггера являю ся информационными входами вычислителя, выход первого триггера соединия, четвертый элемент ИЛИ, элемент И и триггер, прямой выход которого соединен с входом управления режимами выборки вычислителя, а инверсный выход - с информационным входом триггера, вход установки нуля триггера является входом начальной установки устройства, а синхровход триггера соединен с выходом четвертого элемента ИЛИ, первый вход которого

5Q входом первого триггера, а прямой выход соединен с входом формирователя импульсов и управляющими входами регистров адреса, маски и цвета и является первым выходом вычислителя,

соединен с первым выходом блока регенерации изображения, второй вход чет- 55 выход формирователя импульсов подклю- вертого элемента ИЛИ подключен к вы-чен к управляющему входу дешифратора

ходу блока сравнения, соединенному си синхровходам третьего и четвертого

первым входом элемента И, второй вход триггеров, прямой выход которого яв- которого подключен к четвертому выхо- ляется четвертым выходом вычислителя.

472718

ду вычислителя, выход элемента И соединен с третьими входами с первого по третий элементов ИЛИ, пятый и шестой выходы вычислителя соединены с информационными входами первой группы блока сравнения, информационные входа второй группы которого подключены к десятому, одиннадцатому, двенадцатому

10 тринадцатому и третьему выходам блока регенерации изображения, седьмой, восьмой и девятый выходы вычислителя соединены с информационными входами первых групп первого и второго блоков

15 оперативной памяти, информационные входи второй группы первого блока оперативной памяти подключены к десятому, одиннадцатому и двенадцатому выходам, а информационные входы вго-°

20 Р°й группы второго блока оперативной памяти - к тринадцатому, четырнадцатому и пятнадцатому выходам вычислителя, шестнадцатый и семнадцатый выходы которого соединены с первыми п

25 вторыми управляющими входами блоков оперативной памяти, восемнадцатый и девятнадцатый выходы вычислителя подключены к первым и вторым входам элементов 2И-ИЛИ групп, выходы пер30 вой, второй и третьей групп первого блока оперативной памяти соединены с входами первых групп элементов 2И- ИЛИ групп, входы вторых групп которых подключены соответственно к пыхо35 дам первой, второй и тропой групп второго блока опер.п памяти.

входом первого триггера, а прямой выход соединен с входом формирователя импульсов и управляющими входами регистров адреса, маски и цвета и является первым выходом вычислителя,

выход формирователя импульсов подклю- чен к управляющему входу дешифратора

первый выход регистра маски соединен с управляющим входом регистра гранит цы, второй выход - с информационным входом третьего триггера, первым входом элементов И первый группы и входом первого элемента НЕ, а третий выход - с управляющим входом третьего триггера и информационным входом четвертого триггера, выход третьего триггера соединен с первым входом блока сравнения, второй вход которого является входом управления режимами выборки вычислителя, а выход

соединен с первым входом первого эле- 15 и второго -формирователей импульсов,

мента ИЛИ,и входом второго элемента НЕ, выход которого соединен с первым входом второго элемента ИЛИ, вторые входы элементов ИЛИ подключены к инверсному выходу четвертого триггера, выходы элементов ИЛИ являются соответственно девятнадцатым и восемнадцатым выходами вычислителя, выход первого элемента НЕ соединен с первым входом элементов И второй rpynnbij 25 управляющим входом пятого формировавходы группы которых и входы группы элементов И первой группы подключены к выходам группы регистра маски, выходы элементов И первой группы явля

.ются соответственно тринадцатым, че- 30 дом блока является выхот; шестого фортырнадцатым и пятнадцатым выходами вычислителя, десятым, одиннадцатым и двенадцатым выходами которого являются выходы элементов И второй

группы, выходы регистра цвета являют- gg первого счетчика, которые являются ся седьмым, восьмым и девятым выхода- третьим, двенадцатым и тринадцатым ми вычислителя, выходы первой группывыходами блока, вход элемента НЕ соерегистра адреса являются вторым идинен с третьим выходом блока, выход

третьим выходами вычислителя и сое-элемента НЕ является четвертым выходинены с информационными входами пер- 40 Д°м блока, десятым и одиннадцатым

вой группы регистра границы, информационные входы второй группы которого соединены с выходами второй группы регистра адреса, подключенными к информационным входам дешифратора, выходы которого являются шест

надцатым и семнадцатым выходами вычислителя, пятым и шестым выходами которого являются выходы регистра границы.

выходы которых являются первым и вторым выходами блока, выход переполнения второго счетчика соединен с входами третьего и четвертого форми- рователей импульсов, выходы которых являются восьмым и девятым выходами блока, выход первого элемента задержки соединен с синхровходом регистра, входом второго элемента задержки и

теля импульсов, выход которого является пятым выходом блока, шестым выходом ко торого является выход второго элемента задержки, седьмым выхо-

мирователя импульсов, подключенный к информационному входу пятого формирователя импульсов, входы которого соединены с выходами первой группы

выходами блока являются выходы регистра, информационные входы первой группы которого соединены с выходами второй группы первого счетчика, а ин- формационные входы второй группы - с выходами группы второго счетчика.

г см г

J

1

ЧГ

е$ its

gt и oasiSL mass oesaffp ssг $9№ SBSB & zs is

С пятого, шестого выходов Вычислителя 2

С группы информационных 8ыходо& длока генерации 6

С четвертого выхода 061- чцсяителя 2.

Фив.Ц

К четвертым аруппам Входов nepSoeo 4 и. Второго 5 устройств папяти

j so НЧ 61 (

4,5

5 Ф7 ТЫ-ФФЗ

to /z

И

И

И

И

58

59

Фив. 5

20

25

Фиг.6

Ю

t5

| Устройство для формирования изображений на экране телевизионного приемника | 1982 |

|

SU1072092A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-28—Подача