СП

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель частоты заполнения пачек импульсов | 1986 |

|

SU1337798A1 |

| Измеритель частоты импульсов | 1985 |

|

SU1357862A1 |

| Устройство для определения интегральных характеристик периодического сигнала | 1982 |

|

SU1069151A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Способ стабилизации толщины изоляции кабеля и устройство для его реализации | 1982 |

|

SU1302248A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2300112C2 |

| Измеритель средней частоты импульсов | 1987 |

|

SU1487661A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1991 |

|

RU2010286C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1992 |

|

RU2013795C1 |

Изобретение относится к технике элек- трорадиоизмерений и может применяться, например, в гидроакустике для определения параметров частотно-модулированных сигналов. Измеритель частоты заполнения пачек импульсов содержит формирователь 1 импульсов, элемент И 2, счетчик 4 периодов измеряемой частоты, арифметический блок 5, счетчик 6 периодов опорной частоты, формирователь 7 интервалов, формирователь 8 импульсов и генератор 9 опорной частоты. Введение в измеритель элемента И 3, регистра 13 хранения и новых связей позволило за счет разбиения пачки импульсов на уменьшенные и равночисленные повысить быстродействие измерений и расширить функциональные возможности. 1 з.п. ф-лы, 2 ил.

о : а а

5

Изобретение относится к электроради- оизмерениям и может применяться, например, в гидроакустике для определения параметров частотно-модулированных сигналов.

Цель изобретения - повышение быстродействия и расширение функциональных возможностей.

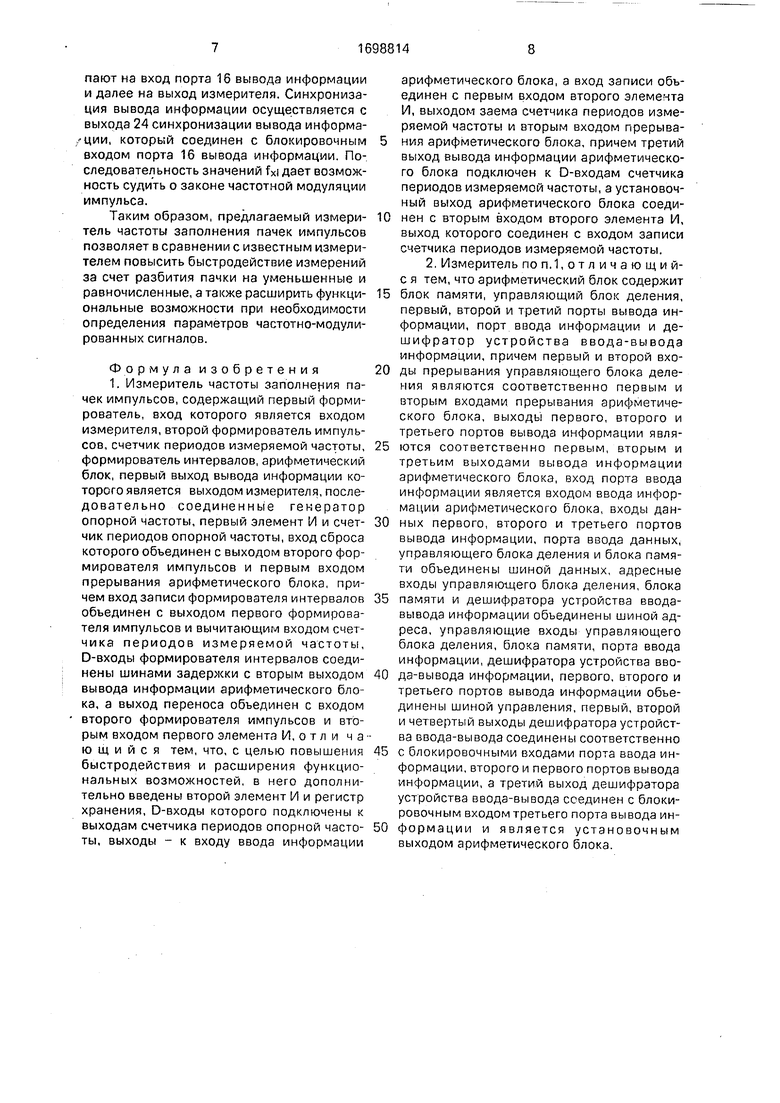

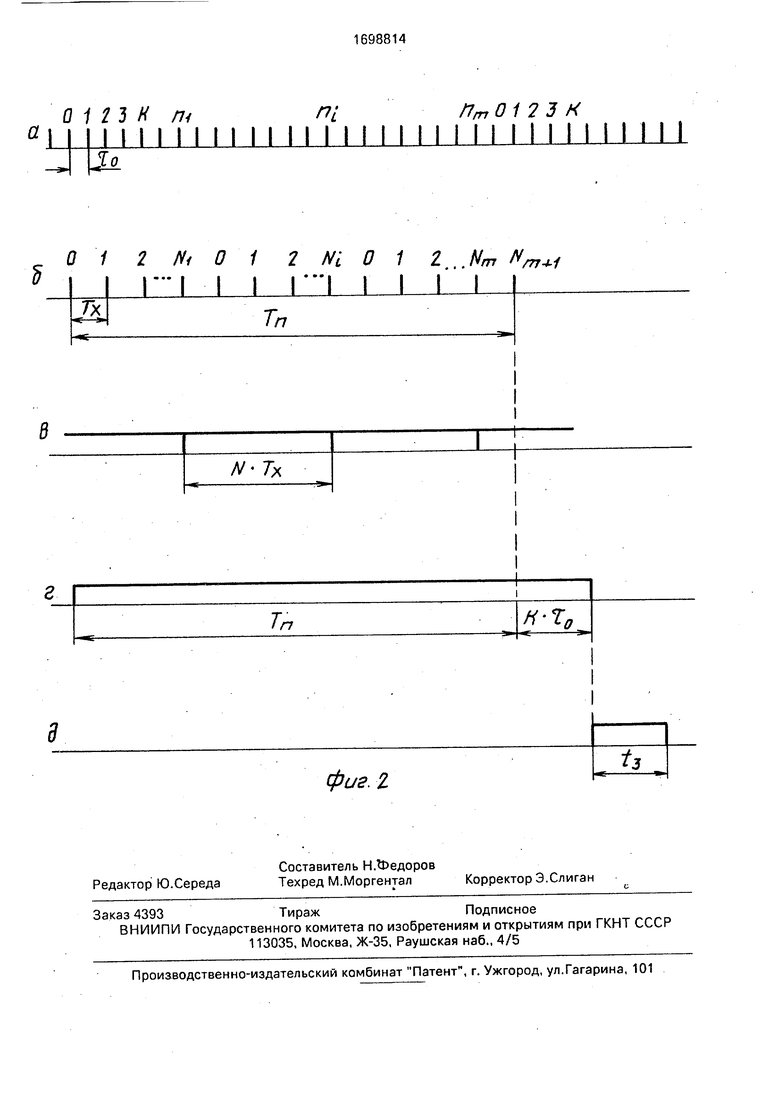

На фиг.1 представлена структурная схема измерителя; на фиг,2 - временные диаграммы, поясняющие его работу.

Измеритель частоты заполнения пачек импульсов содержит формирователь 1 импульсов, элементы И 2-3, счетчик 4 периодов измеряемой частоты, арифметический блок 5, счетчик 6 периодов опорной частоты, формирователь 7 интервалов, формирователь 8 импульсов, генератор 9 опорной частоты, третий выход 10 вывода информации, вход 11 ввода информации, второй выход 12 вывода информации арифметического блока 5,регистр 13 хранения.

Арифметический блок 5 содержит дешифратор 14 устройства ввода-вывода информации, порт 15 ввода информации, порты вывода информации 16-18, шину 19 данных, шину 20 адреса, шину21 управления, управляющий блок 22 деления и блок 23 памяти.

Выход генератора 9 опорной частоты через последовательно соединенные элементы И 2, счетчик 6, регистр 13 и вход 11 ввода информации подключен к входу порта 15 ввода информации, а выход формирователя 1, вход которого является входом измерителя частоты, объединен с вычитающим входом счетчика 4 и входом записи формирователя 7 интервалов, вычитающий вход которого соединен с выходом элемента И 2, а выход переноса объединен с входом формирователя 8 импульсов и вторым входом элемента И 2. Выходы портов 17 и 18, явля- ющиеся выходами информации арифметического блока 5 подключены, соответственно, к D-входам формирователя 7 интервалов и счетчика 4, выход заема которого объединен с входом записи регистра 13, вторым входом запросов прерывания арифметического блока 5 и через элемент И 3 подключен к входу записи счетчика 4, выход формирователя 8 подключен к входу сброса счетчика б и первому входу запросов прерывания арифметического блока 5. Первый, второй и четвертый выходы дешифратора 14 соединены соответственно с блокировочными входами портов 15,17 и 16, выход которого является выходом измерителя, а третий выход дешифратора 14 обье- динен с вторым входом элемента И 3 и блокировочным входом порта 18.

Первый и второй входы запросов прерываний арифметического блока 5 являются одноименными входами управляющего блока 22, а выходы портов 17 и 18 вывода информации являются соответственно выходами 12 и 10 вывода информации арифметического блока 5. Входы данных портов 15-18 управляющего блока 22 деления и блока 23 памяти объединены шиной 19 данных, адресные входы управляющего блока 22, блока 23 памяти и дешифратора объединены шиной 20 адреса, а управляющие входы портов 15-18, дешифратора 14, блока 23 памяти и управляющего блока 22 деления

объединены шиной 21 управления.

Измеритель частоты заполнения пачек импульсов работает следующим образом.

В исходном состоянии, т.е. в отсутствие входных импульсов при инициализации

арифметического блока 5,с третьего выхода дешифратора 14 поступает импульс на блокировочный вход порта 18 вывода информации, который отрицательным фронтом записывает код числа N в порт 18, при этом

уровнем логического 0 этого же импульса записывается код числа N в счетчик 4 периодов измеряемой частоты. Аналогично код коэффициента задержки К записывается в порт 17.

Счетчик 6 периодов опорной частоты находится в нулевом состоянии.

Генератор 9 опорной частоты вырабатывает импульсы с периодом г0 (фиг,2а). Формирователь 7 интервалов находится в

нулевом состоянии, при этом логический 0 с выхода заема формирователя 7 поступает на второй вход элемента И 2 и запрещает прохождение импульсов опорной частоты с выхода генератора 9 через элемент И 2 на

вычитающий счетный вход формирователя 7 интервала, а на D-входах параллельной загрузки формирователя 7 всегда присутствует код коэффициента задержки К, т.е. формирователь 7 запрограммирован на коэффициент деления К, причем код коэффициента К поступает с выхода порта 17 вывода информации арифметического блока 5 на D-входы формирователя 7 и его знаТх

чение выбирается из условий К -

При поступлении на вход измерителя пачки с неизвестной частотой заполнения на выходе формирователя 1 образуются импульсы, период следования которых Тх равен пери- оду частоты входного сигнала, а общая длительность такой пачки импульсов равна Тп (фиг.2б).

Эти импульсы поступают на цычитаю- щий счетный вход счетчика 4 периодов измеряемой частоты и вход записи формирователя 7 интервалов. Счетчик 4 осуществляет деление измеряемой частоты на N, т.е. через каждые N импульсов измеряемой частоты на выходе заема счетчика 4 вы рабаты- вается отрицательный импульс, который через элемент И 3 поступает на вход записи счетчика 4, перезагружая его числом N, a также на вход записи регистра 13 хранения (фиг.2в)и второй вход запросов прерываний арифметического блока 5. Формирователь 7 интервалов осуществляет задержку импульсов измеряемой частоты на величину К коэффициента задержки. Задержка осуществляется следующим образом. Пере- дним фронтом первого импульса измеряемой частоты формирователь 7 интервалов устанавливается в состояние К, поскольку на его D-входах присутствует соответствующий код из арифметического блока 5. При этом на его выходе заема появится сигнал логической 1, который, поступая на вход элемента И 2, разрешает прохождение через него импульсов генератора 9 на вычитающий счетный вход формирователя 7 интервалов и суммирующий счетный вход СЧР- чика 6 периодов опорной частоты. Если перипд Тх импульсов измеряемой частоты входного сигнала удовлетворяет условию Тх К Г0, что обеспечивается соответствующим коэффициентом К, то на выходе заема формирователя 7 в течение всей пачки импульсов будет сигнал логической 1, а сигнал логического 0 на его выходе заема появится через время Кг0 относительно переднего фронта последнего импульса пачки (фиг.2г). С выхода заема формирователя 7 интервалов вырабатывается импульс длительностью Tn+КТ0 . Счетчик 6 периодов опорной частоты осуществляет в течение длительно- сти этого импульса подсчет импульсов опорной частоты генератора 9 (фиг 2г).

Содержимое счетчика 6 периодов опорной частоты положительным фронтом импульса с выхода заема счетчика 4 периодов измеряемой частоты, который вырабатывается через каждые N периодов измеряемой частоты, записывается в регистр 13 хранения, Импульсы с выхода заема счетчика 4 измеряемой частоты также поступают на второй вход запросов прерывания управляющего блока 22 деления,осуществляя запрос на прерывание.

Управляющий блок 22 осуществляет обработку запросов прерывания, поступаю- щих на второй вход запросов прерываний, подавая соответствующие коды по шинам 21 управления, по шинам 20 адреса на дешифратор 14 устройства ввода-вывода информации, порты 16-18 вывода информации и порт 15 ввода информации, что обеспечивает считывание содержимого счетчика 6 периодов опорной частоты через регистр 13 и порт 15 ввода информации в соответствующую ячейку памяти блока 23 памяти. При этом в ячейках блока 23 памяти будет

храниться содержимое счетчика 6: ni

mnm в кодах, соответствующее последовательным интервалам времени Tx-N,... TxIN.... Тх m N,

где i - номер импульса запроса прерывания, вырабатываемого счетчиком 4;

m - число импульсов запроса прерываний, вырабатываемых счетчиком 4, причем m - целая часть отношения Тп/ Тх N, т.е. rrr - число интервалов, на которых измеряется значение частоты заполнения f Xi импульса длительностью Тп.

Формирователь 8 вырабатывает импульс (фиг.2д), передний фронт которого совладеет с задним фронтом импульса на выходе заема формирователя 7 интервалов, а задний фронт задержан относительно него на время t3, необходимое для обработки информации, хранящейся в блоке 23 памяти, по запросу поступающего на первый вход запроса прерывания блока 22. Этот импульс делает запрос на прерывание, а поступая на вход сброса счетчика 6, устанавливает его в нулевое состояние.

Управляющий блок 22 деления при поступлении переднего фронта импульса с формирователя 8 производит вычисление m элементов массива fxi значений частоты заполнения импульса по формуле

fN

Тх| ( п, - п, - 1 ) г0 где N - коэффициент деления счетчика 4;

т0 - период импульсов генератора 9;

гм, пи - содержимое счетчика 6 в моменты времени Тх i N и Тх (i-1) N; i - номер запроса прерывания, принимает значение от 1 до т.

В результате вычислений управляющий блок 22 последовательно записывает m значений измеряемой частоты в блок 23 памяти. Затем управляющий блок 22 определяет максимальное fx макс,минимальное fx мин и среднее fx cp значения частоты заполнения импульса и на основе полученных значений частот заполнения он вырабатывает признак частотного заполнения импульса: простой импульс, если нет максимального и минимального значений; сложный импульс, в противном случае.

После этого коды, соответствующие значениям частот fx Мин,гх cp, fx макс, fxi. последовательно по шине 19 данных постулают на вход порта 16 вывода информации и далее на выход измерителя. Синхронизация вывода информации осуществляется с выхода 24 синхронизации вывода информаии, который соединен с блокировочным входом порта 16 вывода информации. Последовательность значений fxi дает возможность судить о законе частотной модуляции импульса.

Таким образом, предлагаемый измеритель частоты заполнения пачек импульсов позволяет в сравнении с известным измерителем повысить быстродействие измерений за счет разбития пачки на уменьшенные и равночисленные, а также расширить функциональные возможности при необходимости определения параметров частотно-модулированных сигналов.

Формула изобретения 1. Измеритель частоты заполнения пачек импульсов, содержащий первый формирователь, вход которого является входом измерителя, второй формирователь импульсов, счетчик периодов измеряемой частоты, формирователь интервалов, арифметический блок, первый выход вывода информации которого является выходом измерителя, после- довательно соединенные генератор опорной частоты, первый элемент И и счетчик периодов опорной частоты, вход сброса которого объединен с выходом второго формирователя импульсов и первым входом прерывания арифметического блока, причем вход записи формирователя интервалов объединен с выходом первого формирователя импульсов и вычитающим входом счетчика периодов измеряемой частоты, D-входы формирователя интервалов соединены шинами задержки с вторым выходом вывода информации арифметического блока, а выход переноса объединен с входом второго формирователя импульсов и вторым входом первого элемента И, о т л и чающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей, в него дополнительно введены второй элемент И и регистр хранения, D-входы которого подключены к выходам счетчика периодов опорной частоты, выходы - к входу ввода информации

арифметического блока, а вход записи объединен с первым входом второго элемента И, выходом заема счетчика периодов измеряемой частоты и вторым входом прерывания арифметического блока, причем третий выход вывода информации арифметического блока подключен к D-входам счетчика периодов измеряемой частоты, а установочный выход арифметического блока соединен с вторым входом второго элемента И, выход которого соединен с входом записи счетчика периодов измеряемой частоты.

блок памяти, управляющий блок деления, первый, второй и третий порты вывода информации, порт ввода информации и дешифратор устройства ввода-вывода информации, причем первый и второй входы прерывания управляющего блока деления являются соответственно первым и вторым входами прерывания арифметического блока, выходы первого, второго и третьего портов вывода информации являются соответственно первым, вторым и третьим выходами вывода информации арифметического блока, вход порта ввода информации является входом ввода информации арифметического блока, входы данных первого, второго и третьего портов вывода информации, порта ввода данных, управляющего блока деления и блока памяти объединены шиной данных, адресные входы управляющего блока деления, блока

памяти и дешифратора устройства ввода- вывода информации объединены шиной адреса, управляющие входы управляющего блока деления, блока памяти, порта ввода информации, дешифратора устройства ввода-вывода информации, первого, второго и третьего портов вывода информации объединены шиной управления, первый,второй и четвертый выходы дешифратора устройства ввода-вывода соединены соответственно

с блокировочными входами порта ввода информации, второго и первого портов вывода информации, а третий выход дешифратора устройства ввода-вывода соединен с блокировочным входом третьего порта вывода информации и является установочным выходом арифметического блока.

/7т О 1 2 J X

о 1 г з и /цn-L

а I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I

-J U

N7

фиг.1

/7т О 1 2 J X

I I I I I I I I

Ъ

| Измеритель частоты заполнения пачек импульсов | 1986 |

|

SU1337798A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-12-15—Публикация

1989-03-09—Подача