Изобретение относится к вычислительной технике и может быть использовано для .контроля сложных цнфровьгх устройств и микропроцессорных систем

Целью изобретения является повышение быстродействия анализатора.

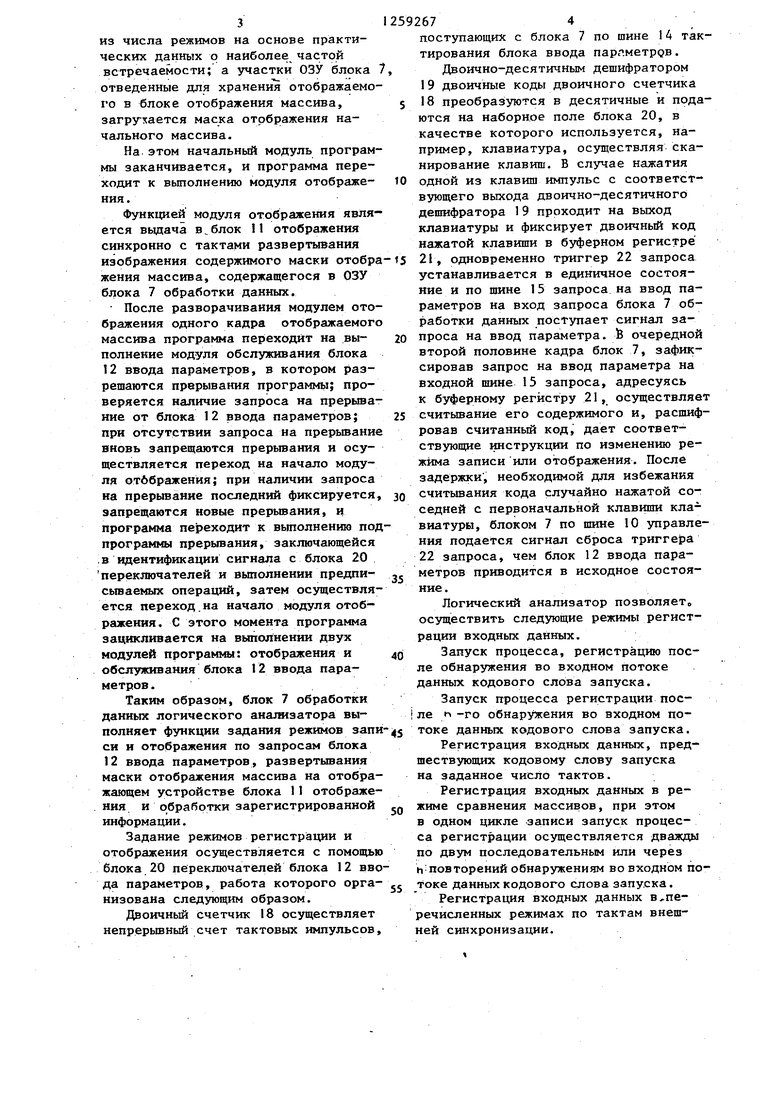

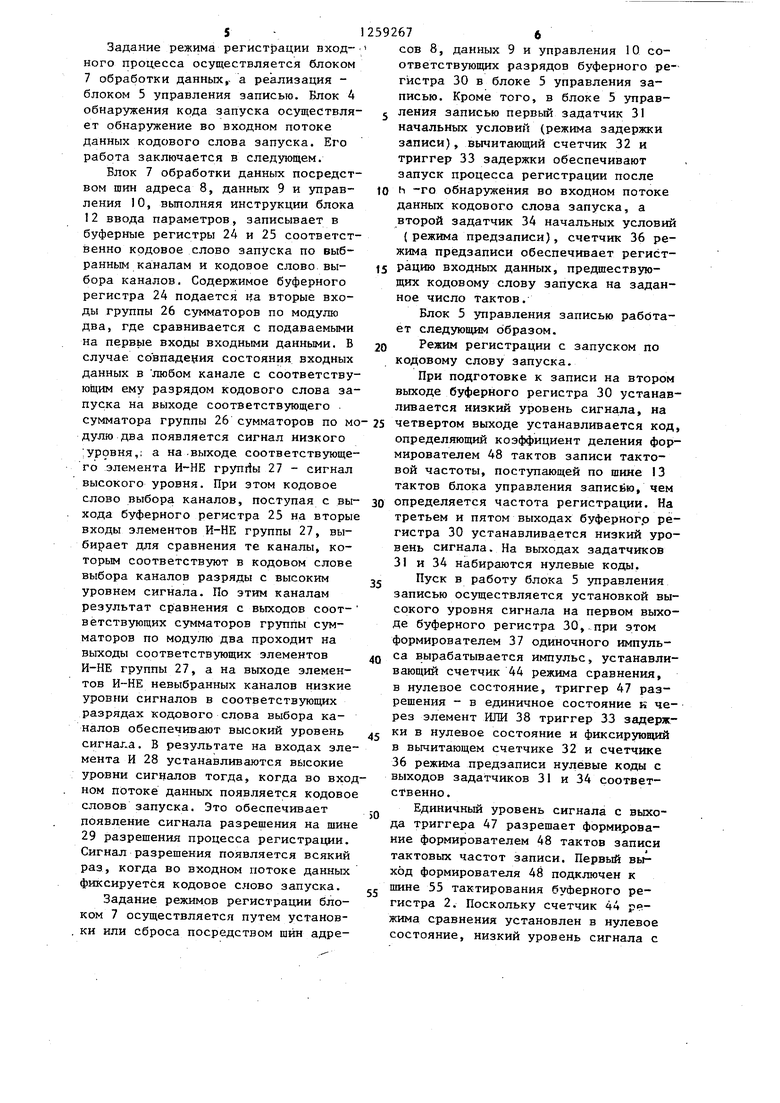

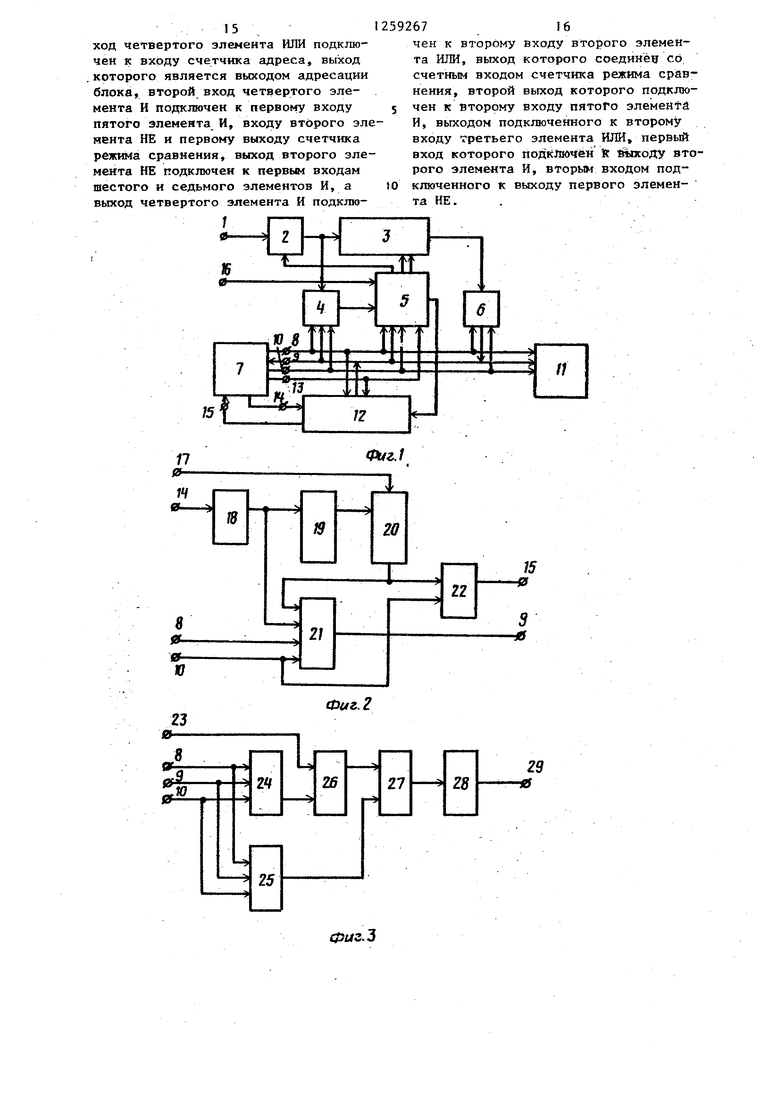

На фиг. 1 представлена блок-схема логического анализатора; на фиг.2 - схема блока ввода параметров; на

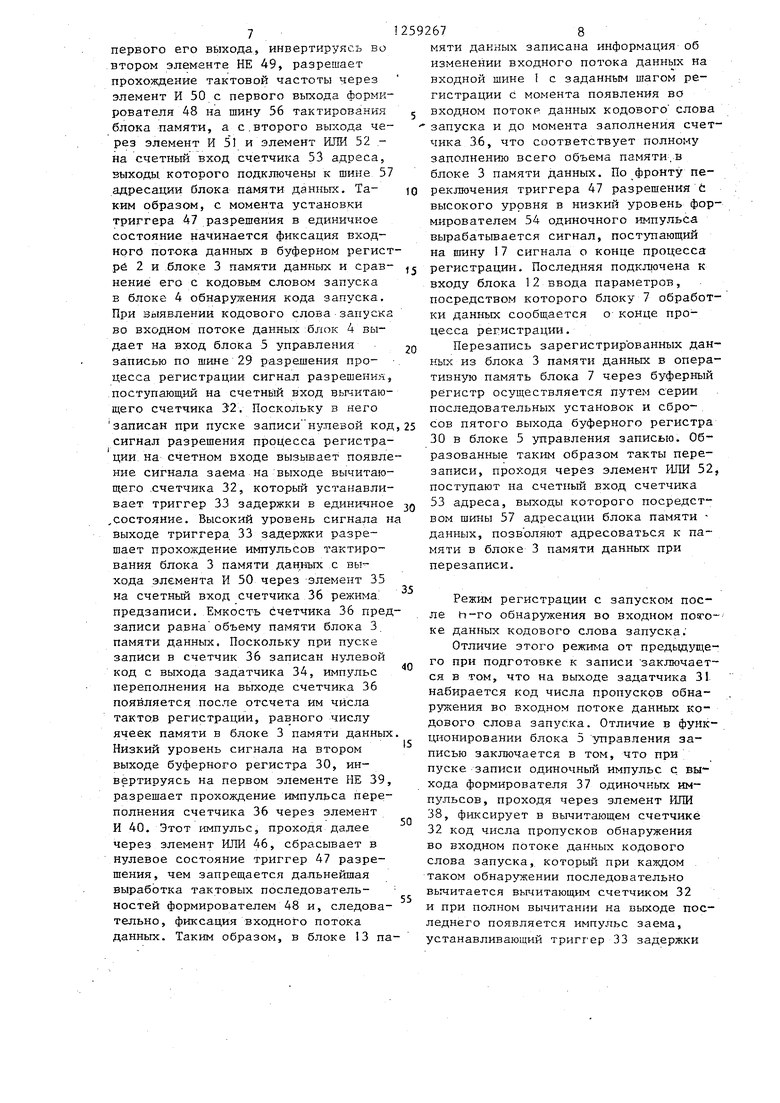

фиг. 3 - схема блока обнаружения кода Ю щую систему стандартного типа и в

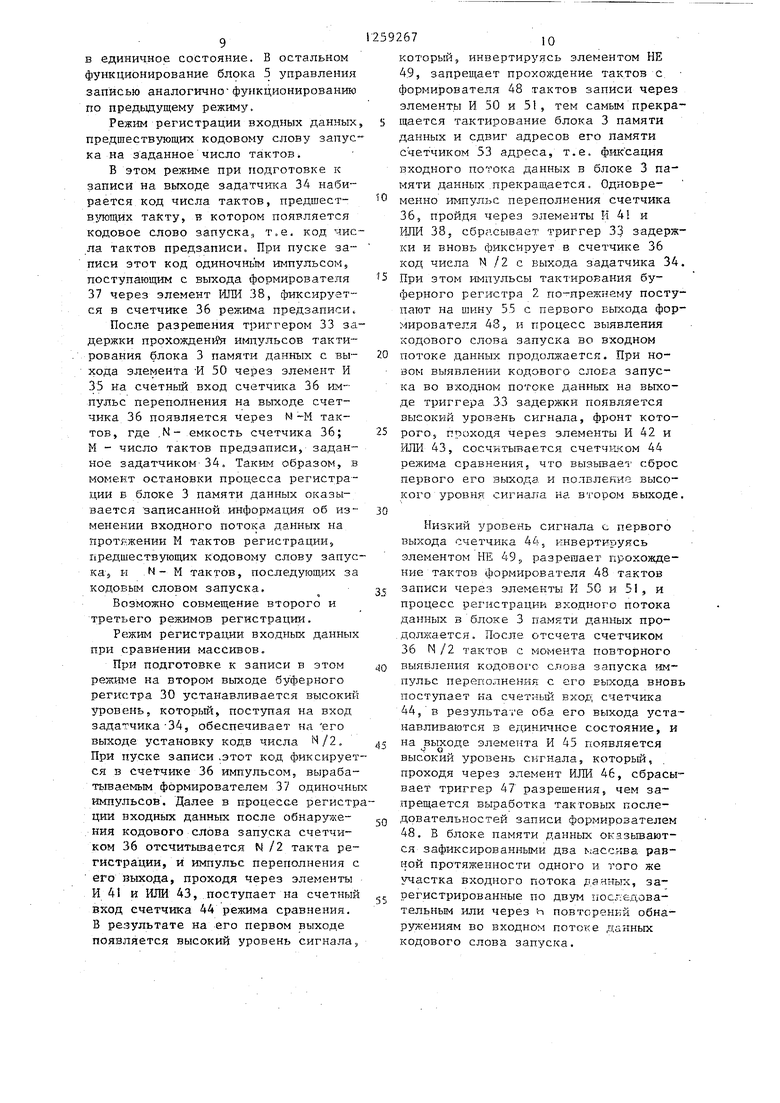

запуска; на фиг. 4 - схема блока управления записью.

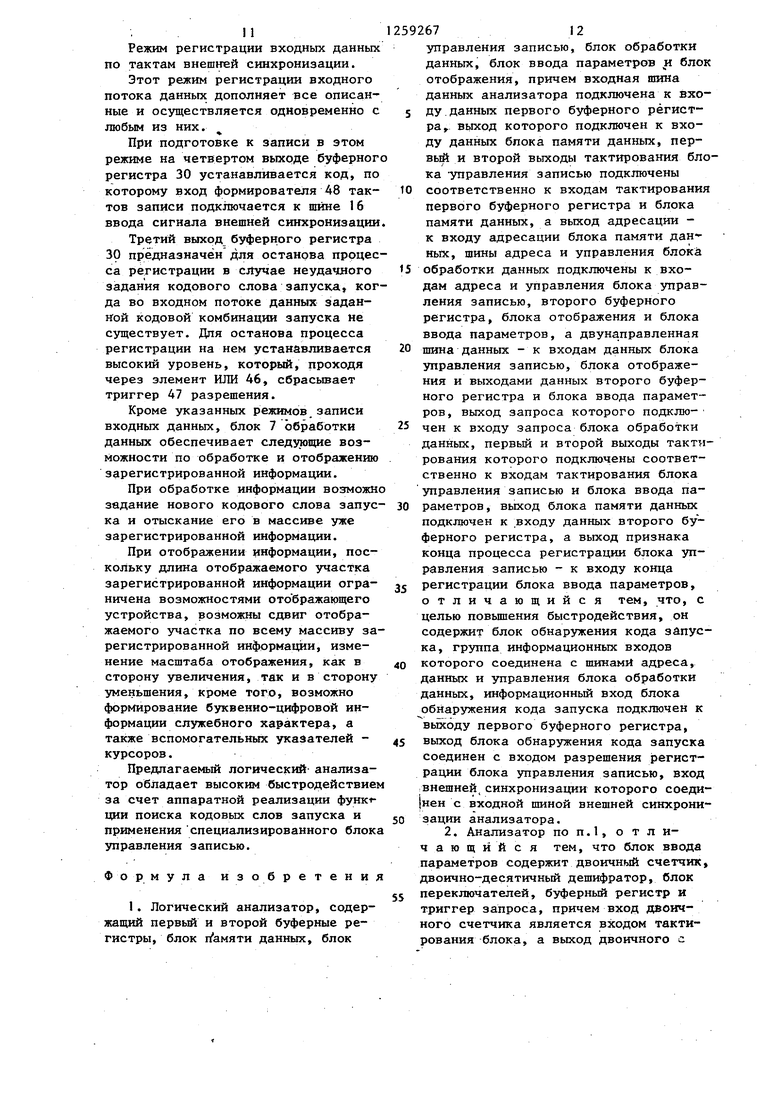

Логический анализатор (фиг.1) содержит входную шину 1 данных, пер- вьй буферный регистр 2, блок 3 памяти данных, блок 4 обнаружения кода запуска, блок 5 управления записью, второй буферт 1Й регистр 6, блок 7 обработки данных, шины адреса 8, данных 9 и управления 10, блок И бражения, блок , 12 ввода параметров, пмну 13 тактов блока управления записью, шину 14 тактирования блока ввода параметров, шину 15 запроса на ввод параметров и входную шину I6 .внешней синхронизации.

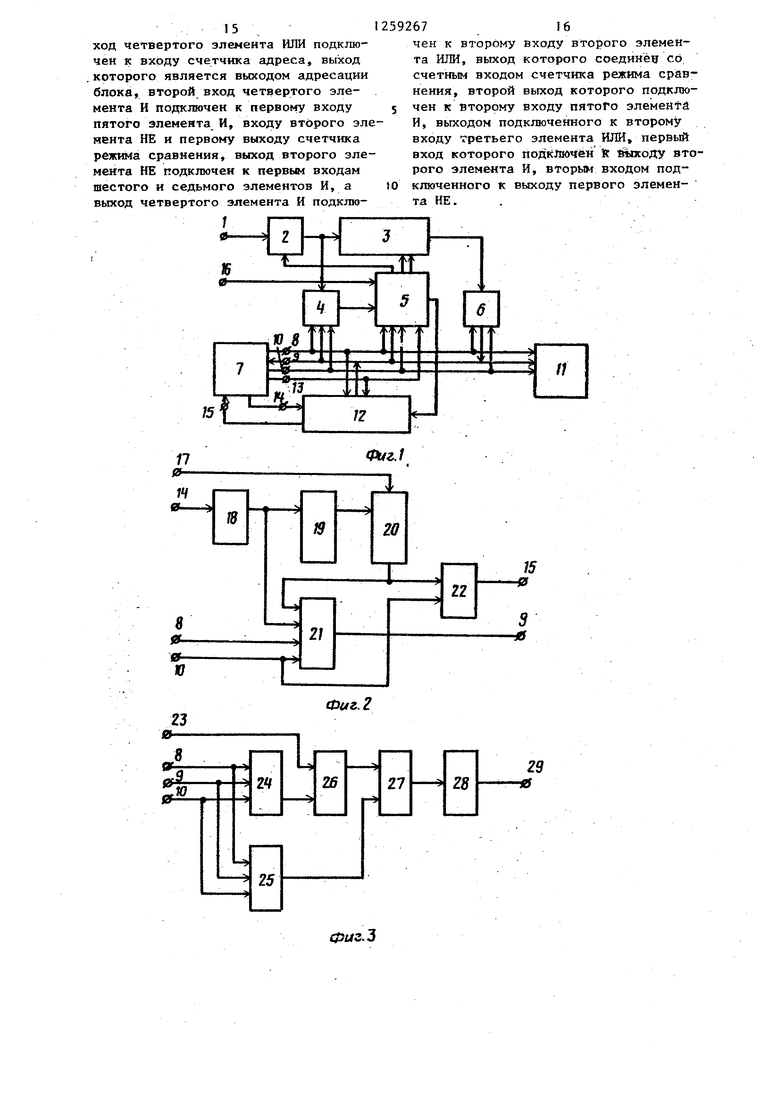

Блок ввода .параметров (фиг. 2) содержит шину 17 ввода сигнала о конце процесса регистрации, двоичный счетчик .18, двоично-десятичный де- папЬратор 19, блок 20 переключателей, буферный регистр 21, триггер 22 запроса на ввод параметров и шину 15 запроса на ввод параметров.

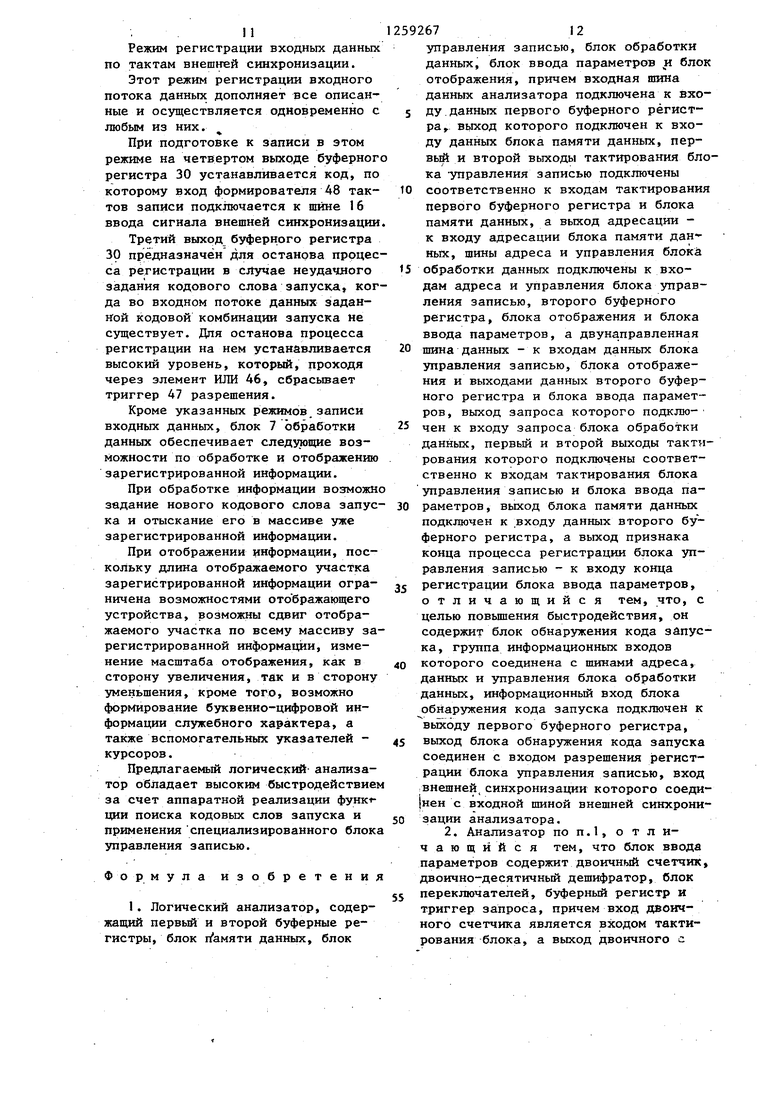

Блок обнаружения кода запуска (фиг. 3) содержит шину 23 входных данных, буферною регистры 24 и 25, группу 26 су маторов по модулю два, группу 27 элементов И-НЕ, элемент И 28 и выходную шину 29 разрешения регистрации.

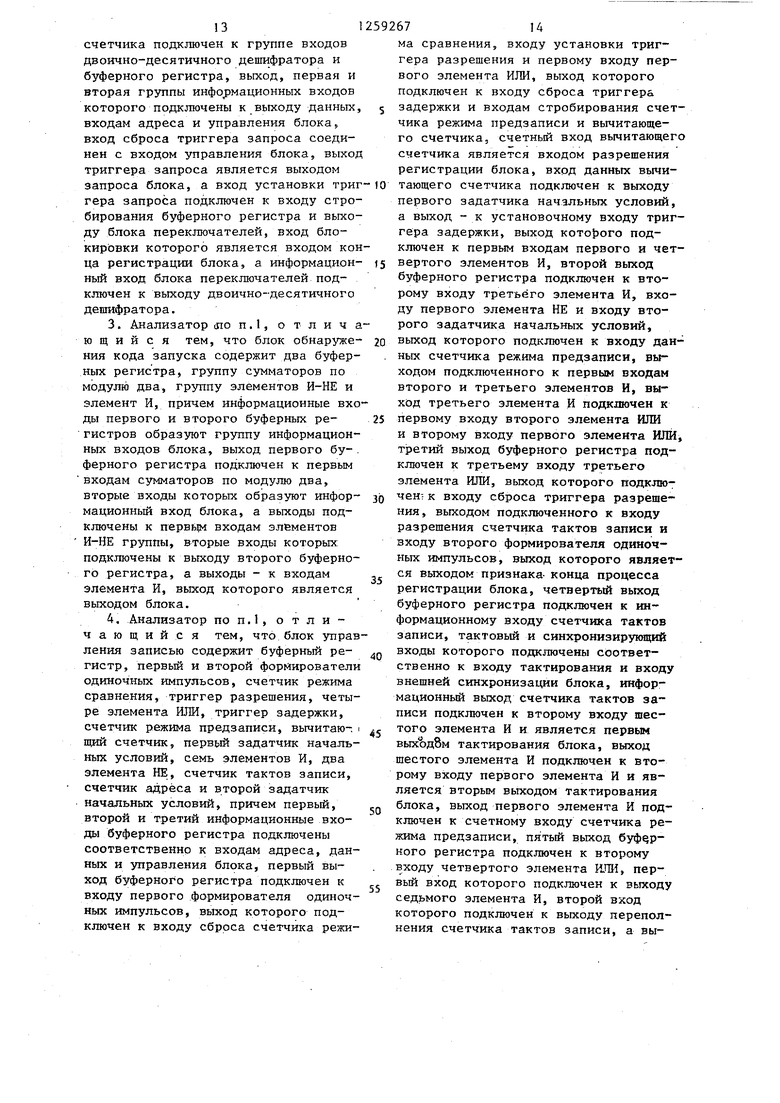

Блок управления записью (фиг.4)содержит буферный регистр 30, первый задатчик 31 начальных условий, вычитающий счетчик 32, триггер 33 режима задержки записи, второй задатчик 34 начальных условий, первый элемент И 35, счетчик 36 режима предзаписи, первьй формирователь 37 одиночных импульсов, первьй элемент ИЛИ 38, первый элемент НЕ 39, второй, третий и четвертый элементы И 40-42, второй элемент ИЛИ 43, счетчик 44 режима сравнеюш, пятый эпемект И 45, третий элемент ИЛИ 46, триггер 47 разрешения тактирования, формирователь 48 тактов записи, второй элемент НЕ 49, шестой и седьмой элементы.И

15

20

25

30

минимальной конфигурации содержит г-гакропродессор, ОЗУ и ПЗУ, а также порты ввода-вывода, .

Работа логического анализатора ганизована таким образом, что его схемы обеспечивают задание режимов регистрации н отображения, регистр цию состояния входных шин I, перез пись записанного массива данных в оперативную память блока 7 обработ данных, отображение данных в блоке 11 отображения под общим управлени блока 7, работающего по программе, содержащейся в его памяти программ

Программа работы блока 7 обрабо ки данных построена таким образом, чтобы обеспечить непрерывное отобр жение информации в блоке 11 отобра ния. Длительность кадра 20 м подел на так, что первые 10 м блок 7 осу (ществляет развертку информации на отображающем устройстве блока 11 о бражения и обработку вспомогательн информации, задаваемой служебными указателями - курсорами. Во вторые 10 мс кадра разрешается задание но режимов регистрации и отображения, которое осуществляется по запросам блока 12 ввода параметров, поступа щим по шине 15 запроса на ввод пар метров, а также пуск записи и пере пись зарегистрированных данных из блока 3 памяти данных через второй буферный регистр 6 в оперативную п 45 мять блока 7 обработки данных.

Включение питания логического анализатора автоматически выводит программу на начальный модуль, в к тором запрещаются прерьгеания прогр мы; программируются на необходимый режим работы программируемые порты ввода-вьгоода; проводится тестирова ние ОЗУ блока 7 обработки данных; проводится Настройка блока 5 управ ления записью и блока I1 отображен на типовые режимы записи и отображ ния соответственно, причем типовые режимы записи и отображения выбран

35

40

50

55

2592671

50 и 5, четвертый элемент ИЛИ 52, счетчик 53 адреса, второй формирователь 54 одиночных импульсов, шину 55 тактирования первого буферного ре- 5 гистра, шину 56 тактирования блока памяти данных и шину 57 адреса блока памяти данных.

Блок 7 обработки данных представляет собой микропроцессорную управляю

0

5

0

минимальной конфигурации содержит г-гакропродессор, ОЗУ и ПЗУ, а также порты ввода-вывода, .

Работа логического анализатора организована таким образом, что его схемы обеспечивают задание режимов регистрации н отображения, регистрацию состояния входных шин I, перезапись записанного массива данных в оперативную память блока 7 обработки данных, отображение данных в блоке 11 отображения под общим управлением блока 7, работающего по программе,, содержащейся в его памяти программ.

Программа работы блока 7 обработки данных построена таким образом, чтобы обеспечить непрерывное отображение информации в блоке 11 отображения. Длительность кадра 20 м поделена так, что первые 10 м блок 7 осу- (ществляет развертку информации на отображающем устройстве блока 11 отображения и обработку вспомогательной информации, задаваемой служебными указателями - курсорами. Во вторые 10 мс кадра разрешается задание новых режимов регистрации и отображения, которое осуществляется по запросам блока 12 ввода параметров, поступающим по шине 15 запроса на ввод параметров, а также пуск записи и перезапись зарегистрированных данных из блока 3 памяти данных через второй буферный регистр 6 в оперативную па- 5 мять блока 7 обработки данных.

Включение питания логического анализатора автоматически выводит программу на начальный модуль, в котором запрещаются прерьгеания программы; программируются на необходимый режим работы программируемые порты ввода-вьгоода; проводится тестирование ОЗУ блока 7 обработки данных; проводится Настройка блока 5 управления записью и блока I1 отображения на типовые режимы записи и отображения соответственно, причем типовые режимы записи и отображения выбраны

5

0

0

5

из числа режимов на основе практических данных о наиболее частой встречаемости; а участки ОЗУ блока отведенные для хранений отображаемого в блоке отображения массива, загрукается маска отображения начального массива.

На этом начальный модуль программы заканчивается, и программа переходит к выполнению модуля отображения .

Функцией модуля отображения является вьщача в„блок 11 отображения синхронно с тактами развертывания изображения содержимого маски отобра жения массива, содержащегося в ОЗУ блока 7 обработки данных.

После разворачивания модулем отображения одного кадра отображаемого массива программа переходит на выполнение модуля обслуживания блока 12 ввода параметров, в котором разрешаются прерывания nporpar ibi; проверяется наличие запроса на прерывание от блока 12 ввода параметров; при отсутствии запроса на прерывание вновь запрещаются прерывания и осуществляется переход на начало модуля отббраженйя; при наличии запроса на прерьтание последний фиксируется, запрещаются новые прерьгоания, и программа переходит к вьшолнению подпрограммы прерывания, заключающейся в идентификации сигнала с блока 20 переключателей и выполнении предписываемых операций, затем осуществляется переход.иа начало модуля отображения. С зтого момента программа зацикливается на выполнении двух модулей программы: отображения и обслуживания блока Г2 ввода параметров.

Таким образом, блок 7 обработки данных логического анатжзатора выполняет функции задания режимов запи си и отображения по запросам блока 12 ввода параметров, развертывания маски отображения массива на отображающем устройстве блока I1 отображения и обработки зарегистрированной информации.

Задание режимов регистрации и отображения осуществляется с помощью блока 20 переключателей блока 12 вво

да параметров, работа которого орга- токе данных кодового слова запуска.

низована следующим образом.

Двоичный счетчик 18 осуществляет непрерьшный счет тактовых импульсов.

Регистрация входных данных в,п речисленных режимах по тактам вне ней синхронизации.

10

20

25

t5

з

2592674

поступающих с блока 7 по шине 14 тактирования блока ввода параметров.

Двоично-десятичным дешифратором 19 двоичные коды двоичного счетчика 18 преобразуются в десятичные и подаются на наборное поле блока 20, в качестве которого используется, например, клавиатура, осуществляя сканирование клавиш. В случае нажатия одной из клавиш импульс с соответст- вующего выхода двоично-десятичного дешифратора 19 проходит на выход клавиатуры и фиксирует двоичный код нажатой клавиши в буферном регистре 21, одновременно триггер 22 запроса устанавливается в единичное состояние и по щине 15 запроса на ввод параметров на вход запроса блока 7 обработки данных поступает сигнал запроса на ввод параметра, fe очередной второй половине кадра блок 7, зафиксировав запрос на ввод параметра на входной шине 15 запроса, адресуясь к буферному регистру 21, осуществляет считывание его содержимого и, расшифровав считанный код, дает соответствующие инструкции по изменению режима записи или отображения. После задержки , необходимой для избежания считывания кода случайно нажатой соседней с первоначальной клавиши клавиатуры, блоком 7 по щине 10 управления подается сигнал сброса триггера 22 запроса, чем блок 12 ввода параметров приводится в исходное состояние.

Логический анализатор позволяете осуществить следующие режимы регистрации входных данных.

Запуск процесса, регистрацию после обнаружения во входном потоке данных кодового слова запуска.

Запуск процесса регистрации после обнаружения во входном потоке данных кодового слова запуска.

Регистрация входных данных, предшествующих кодовому слову запуска на заданное число тактов.

Регистрация входных данных в режиме сравнения массивов, при этом в одном цикле записи запуск процесса регистрации осуществляется дважды по двум последовательньм или через h-повторений обнаружениям во входном по30

5

0

0

токе данных кодового слова запуска.

Регистрация входных данных в,перечисленных режимах по тактам внешней синхронизации.

Задание режима регистрации входного процесса осуществляется блоком 7 обработки данных,- а реализация - блоком 5 управления записью. Блок 4 обнаружения кода запуска осуществляет обнаружение во входном потоке данных кодового слова запуска. Его работа заключается в следующем.

Блок 7 обработки данных посредством шин адреса 8, данных 9 и управления 10, выполняя инструкции блока 12 ввода параметров, записывает в буферные регистры 24 и 25 соответственно кодовое слово запуска по выбранным каналам и кодовое слово выбора каналов, Содержимое буферного регистра 24 подается на вторые входы группы 26 сумматоров по модулю два, где сравнивается с подаваемыми на первые входы входными данными. В случае совпадения состояния входных данных в любом канале с соответствующим ему разрядом кодового слова запуска на выходе соответствующего сумматора группы 26 сумматоров по модулю два появляется сигнал низкого ;уровня,; а на .выходе соответствующего элемента И-НЕ группы 27 - сигнал высокого уровня. При этом кодовое слово выбора каналов, поступая с выхода буферного регистра 25 на вторые входы элементов И-НЕ группы 27, выбирает для сравнения те каналы, которым соответствуют в кодовом слове выбора каналов разряды с высоким уровнем сигнала. По этим каналам результат сравнения с выходов соот- ветствующих сумматоров группы сумматоров по модулю два проходит на выходы соответствующих элементов И-НЕ группы 27, а на выходе элементов И-НЕ невыбранных каналов низкие уровни сигналов в соответствующих разрядах кодового слова выбора каналов обеспечивают высокий уровень сигнала. В результате на входах элемента И 28 устанавливаются высокие уровни сигналов тогда, когда во вхоном потоке данных появляется кодово слонов запуска. Это обеспечивает появление сигнала разрешения на шин 29 разрешения процесса регистрации. Сигнал разрешения появляется всякий раз, когда во входном потоке данных фиксируется кодовое слово запуска.

Задание режимов регистрации блоком 7 осуществляется путем установ- , ки или сброса посредством шин адресов 8, данных 9 и управления 10 соответствующих разрядов буферного ре-- гйстра 30 в блоке 5 управления записью. Кроме того, в блоке 5 управ- 5 ления записью первый задатчик 31 начальных условий (режима задержки записи), вьтчитающий счетчик 32 и триггер 33 задержки обеспечивают запуск процесса регистрации после

0 h -го обнаруясения во входном потоке данных кодового слова запуска, а второй задатчик 34 начальных условий ( режима предзаписи), счетчик 36 режима предзаписи обеспечивает регист5 рацию входных данных, предшествующих кодовому слову запуска на заданное число тактов.

Блок 5 управления записью работает следующим образом.

0 Режим регистрации с запуском по кодовому слову запуска.

При подготовке к записи на втором выходе буферного регистра 30 устанавливается низкий уровень сигнала, на

5 четвертом выходе устанавливается код, определяющий коэффициент деления формирователем 48 тактов записи тактовой частоты, поступающей по шине 13 тактов блока управления записйю, чем

0 определяется частота регистрации. На третьем и пятом выходах буферногр регистра 30 устанавливается низкий уровень сигнала. На выходах задатчиков 31 и 34 набираются нулевые коды.

, Пуск в работу блока 5 управления записью осуществляется установкой высокого уровня сигнала на первом выходе буферного регистра 30,.при этом формирователем 37 одиночного импульса вырабатывается импульс, устанавливающий счетчик 44 режима сравнения, в нулевое состояние, триггер 47 разрешения - в единичное состояние к через элемент ИЛИ 38 триггер 33 задержки в нулевое состояние и фиксирующий в вычитающем счетчике 32 и счетчике 36 режима предзаписи нулевые коды с выходов задатчиков 31 и 34 соответственно.

Единичный уровень сигнала с выхода триггера 47 разрешает формирование формирователем 48 тактов записи

J

тактовых частот записи. Первый выход формирователя 48 подключен к , шине 55 тактирования буферного регистра 2. Поскольку счетчик 44 режима сравнения установлен в нулевое состояние, низкий уровень сигнала с

0

первого его выхода, инвертируясь во втором элементе НЕ 49, разрешает прохождение тактовой частоты через элемент И 50 с первого выхода формирователя 48 на шину 56 тактирования блока памяти, а с.второго выхода через элемент И S l и элемент ИЛИ 52 - на счетный вход счетчика 53 адреса, выходы, которого подключены к шине 57 адресации блока памяти данных. Таким образом, с момента установки триггера 47 разрешения в единичное состояние начинается фиксация входного потока данных в буферном регистре 2 и блоке 3 памяти данных и сравнение его с кодовым словом запуска в блоке 4 обнаружения кода запуска, При выявлении кодового слова запуска во входном потоке данных ;блок 4 выдает на вход блока 5 управления записью по шине 29 разрешения про- десса регистрации сигнал разрешения, .поступающий на счетный вход вычитающего счетчика 32. Поскольку в него записан при пуске записи нулевой код сигнал разрешения процесса регистрации, на счетном входе вызывает появление сигнала заема на выходе вычитающего счетчика 32, который устанавливает триггер 33 задержки в единичное ,состояние. Высокий уровень сигнала н выходе триггера. 33 задержки разрешает прохождение импульсов тактирования блока 3 памяти данных с вы- хода элемента И 50 через элемент 35 на счетный вход счетчика 36 режима, предзаписи. Емкость счетчика 36 пред записи равна объему памяти блока 3. памяти данных. Поскольку при пуске записи в счетчик 36 записан нулевой код с выхода задатчика 34, импульс переполнения на выходе счетчика 36 появляется после отсчета им числа тактов регистрации, равного числу ячеек памяти в блоке 3 памяти данных Низкий уровень сигнала на втором выходе буферного регистра 30, инвертируясь на первом элементе НЕ 39, разрешает прохождение импульса переполнения счетчика 36 через элемент И 40. Этот импульс, проходя далее через элемент ИЛИ 46, сбрасывает в нулевое состояние триггер 47 разрешения, чем запрещается дальнейшая выработка тактовых последовательностей формирователем 48 и, следовательно, фиксация входного потока данных. Таким образом, в блоке 13 па

5

10

15

20

25JQ

2592678

мяти данных записана информация об изменении входного потока данных на входной шине 1 с заданным шагом регистрации с момента появления во входном потоке, данных кодового слова запуска и до момента заполнения счетчика 36, что соответствует полному заполнению всего объема памяти.в блоке 3 памяти данных. По фронту переключения триггера 47 разрешения fc высокого уровня в низкий уровень формирователем 54 одиночного импульса вырабатьшается сигнал, поступающий на шину i 7 сигнала о конце процесса регистрации. Последняя подключена к входу блока 12 ввода параметров, посредством которого блоку 7 обработки данных сообщается о конце процесса регистрации.

Перезапись зарегистрированных данных из блока 3 памяти данных в оперативную память блока 7 через буферный регистр осуществляется п.утем серии последовательных установок и сбро- . сов пятого выхода буферного регистра 30 в блоке 5 управления записью. Образованные таким образом такты перезаписи, проходя через элемент ИЛИ 52, поступают на счетный вход счетчика 53 адреса, выходы которого посредством шины 57 адресации блока памяти - данных, позволяю.т адресоваться к памяти в блоке 3 памяти данных при перезаписи.

25JQ

35

40

15

0

5

Режим регистрации с запуском после h-ro обнаружения во входном nosro- ке данных кодового слова запуска.

Отличие этого режима от предыдущего при подготовке к записи заключается в том, что на выходе задатчика 31 набирается код числа пропусков обнаружения во входном потоке данных кодового слова запуска. Отличие в функционировании блока 5 управления записью заключается в том, что при пуске записи одиночный импульс с выхода формирователя 37 одиночных импульсов, проходя через элемент 1-ШИ 38, фиксирует в вычитающем счетчике 32 код числа пропусков обнаружения во входном потоке данных кодового слова запуска, который при каждом таком обнаружении последовательно вычитается вычитающим счетчиком 32 и при полном вычитании на выходе последнего появляется импульс заема, устанавливающий триггер 33 задержки

9

в единичное состояние. В остальном функционирование блока 5 управления записью аналогично функционированию по предыдущему режиму.

Режим регистрации входных данных предшествующих кодовому слову запус ка на заданное число тактов,

В этом режиме при подготовке к записи на выходе задатчика 34 набирается код числа тактов, предшест- в тощих такту, в котором появляется кодовое слово запуска, т,е, код числа тактов предзаписи. При пуске записи этот код одиночнь м импульсом, поступающим с выхода формирователя 37 через элемент ИЛИ 38, фиксируется в счетчике 36 режима предзаписи

После разрешения триггером 33 задержки прохождения импульсов тактирования блока 3 памяти данных с выхода элемента И 50 через элемент И 35 на счетный вход счетчика 36 HIM- пульс переполнения на выходе счетчика 36 появляется через N-М тактов, где ,N- емкость счетчика 36; М - число тактов предзаписи, заданное задатчиком 34. Таким образом, в момент остановки процесса регистрации в блоке 3 памяти данных оказывается записанной информация об изменении входного потока данных на протяжении М тактов регистрации, предшествующих кодовому слову запус каз и ,N- М тактов, последующих за кодовым словом запуска.

Возможно совмещение второго и третьего режимов регистрации.

Режим регистрации входных данных при сравнении массивов.

При подготовке к записи в этом режш- е на втором вьиоде буферного регистра 30 устанавливается высокий уровень, который, поступая на вход задатчика -34, обеспечивает на его выходе установку кодв числа М/2. При пуске записи .этот код фиксируется в счетчике 36 импульсом, выраба- тывас мым формирователем 37 одиночны Импульсов. Далее в процессе регистр циИ входных данных после обнаруже- . ния кодового слова запуска счетчиком 36 отсчитьшается N /2 такта регистрации, и импульс переполнения с его выхода, проходя через элементы И 41 и ИЖ 43, .поступает на счетный вход счетчика 44 режима сравнения. В результате на его первом выходе появляется высокий уровень сигнала.

5926710

который, инвертируясь элементом НЕ 4.9, запрещает прохолодение тактов с. формирователя 48 тактов записи через элемент.ы И 50 и 51, тем самым прекра- S щается тактирование блока 3 памяти данных и сдвиг адресов его памяти счетчиком 53 адреса, т.е. фиксация входного потока данных в блоке 3 памяти данных .прекращается. Одновре0 менно импульс переполнения счетчика 36, пройдя через элементы И 41 и ИЛИ 38, сбрасывает триггер 33 задержки и вновь фнксрфует в счетчике 36 код числа N /2 с выхода задатчика 34.

5 При этом импульсы тактирования буферного регистра 2 по-прежнему поступают на шину 55 с первого выхода формирователя 43, и процесс выявления кодового слова запуска во входном

20 потоке данных продолжается. При новом выявлении кодового слова запуска во входном потоке данных на выходе триггера 33 задержки появляется высокий уровень сигнала, фронт кото5 poros проходя через элементы И 42 и ИЛИ 43, сосчитывается счетчш ом 44 режима сравнения, что вызьшает сброс первого его выхода и полвление высокого уровня сигнала на втором выходе.

0

Низкий уровень сигнала с первого выхода счетчика 44, инвертируясь элементом НЕ 49 разрешает прохождение тактов формирователя 48 тактов

5 записи через элементы И 50 и 51, и процесс регистрацкк входного потока данных в блоке 3 памяти данных про- .должается. После отсчета счетчиком 36 N/2 тактов с момента повторного

0 выявления кодовoi c слова запуска импульс переполнения с его выхода вновь поступает на счетный вход счетчика 44, в результате оба его выхода устанавливаются в единичное состояние, и

5 на выходе элемента И 45 появляется высокий уровень сигнала, которьй, проходя через элемент ИЛИ 46, сбрасывает триггер 47 разрешения, чем запрещается выработка тактовых после0 довательностей записи формирователем 48. В блоке памяти данных окззьшают- ся зафиксированными два к ассива равной протяженности одного и того же участка входного потока данных, за.j регистрированные по двум последовательным или через ь повторений обнаружениям во входном потоке данных кодового слова запуска.

. 11

Режим регистрации входных данных по тактам внешней синхронизации.

Этот режим регистрации входного потока данных дополняет все описанные и осуществляется одновременно с любым из них.

При подготовке к записи в этом режиме на четвертом выходе буферног регистра 30 устанавливается код, по которому вход формирователя 48 тактов записи подключается к шине 16 ввода сигнала внешней синхронизации

Третий выход буферного регистра 30 предназначен для останова процесса регистрации в случае неудачного задания кодового слова запуска, когда во входном потоке данных задан- н ой кодовой комбинации запуска не существует. Дпя останова процесса регистрации на нем устанавливается высокий уровень, который, проходя через элемент ИЛИ 46, сбрасьгоает триггер 47 разрешения.

Кроме указанных режимов.записи входных данных, блок 7 обработки данных обеспечивает следующие возможности по обработке и отображению зарегистрированной информации.

При обработке информации возможно задание нового кодового слова запуска и отыскание его в массиве уже зарегистрированной информации.

При отображении информации, поскольку длина отображаемого участка зарегистрированной информации ограничена возможностями отображающего устройства, возможны сдвиг отображаемого участка по всему массиву зарегистрированной информации, изменение масштаба отображения, как в сторону увеличения, так и в сторону уменьшения, кроме того, возможно формирование буквенно-цифровой информации служебного характера, а также вспомогательных указателей - курсоров.

Предлагаемый логический анализатор обладает высоким быстродействием за счет аппаратной реализации функ1- ции поиска кодовых слов запуска и применения специализированного блока управления записью.

Формула изобретения

1. Логический анализатор, содержащий первый и второй буферные регистры, блок памяти данных, блок

25926712

управления записью, блок обработки данных, блок ввода параметров и блок отображения, причем входная шина данных анализатора подключена к вхо- 5 ду данных первого буферного регистра,, выход которого подключен к входу данных блока памяти данных, пер- Bbrii и второй выходы тактирования блока -управления записью подключены 10 соответственно к входам тактирования первого буферного регистра и блока памяти данных, а выход адресации - к входу адресации блока памяти дан- ных, шины адреса и управления блока 15 обработки данных подключены к входам адреса и управления блока управления записью, второго буферного регистра, блока отображения и блока

ввода параметров, а двунаправленная 20 шина данных - к входам данных блока управления записью, блока отображения и выходами данных второго буферного регистра и блока ввода параметров, выход запроса которого подклю- 25 чен к входу запроса блока обработки данных, первый и второй выходы тактирования которого подключены соответственно к входам тактирования блока управления записью и блока ввода па- 0 раметров, выход блока памяти данных подключен к входу данных второго буферного регистра, а выход признака конца процесса регистрации блока управления записью - к входу конца

5 регистрации блока ввода параметров, отличающийся тем, что, с целью повьш1ения быстродействия, он содержит блок обнаружения кода запуска, группа информационных входов

0 которого соединена с шинами адреса, данных и управления блока обработки данных, информационный вход блока обнаружения кода запуска подключен к выходу первого буферного регистра,

5 выход блока обнаружения кода запуска соединен с входом разрешения регистрации блока управления записью, вход внешней синхронизации которого соеди- |нен с входной шиной внешней синхрони0 зации анализатора.

2. Анализатор по п.1, о т л и- чающийся тем, что блок ввода параметров содержит двоичный счетчик, двоично-десятичный дешифратор, блок

переключателей, буферный регистр и триггер запроса, причем вход двоичного счетчика является входом тактирования-блока, а выход двоичного с

13

счетчика подключен к группе входов двоично-десятичного дешифратора и буферного регистра, выход, первая и вторая группы информационных входов которого подключены к выходу данных, входам адреса и управления блока,, вход сброса триггера запроса соединен с входом управления блока, выход триггера запроса является выходом запроса блока, а вход установки триг гера запроса подключен к входу стро- бирования буферного регистра и выходу блока переключателей, вход блокировки которого является входом кон ца регистрации блока, а информационный вход блока переключателей подключен к выходу двоично-десятичного дешифратора.

3.Анализатор яо п.1, о т л и ч а ю щ и и с я тем, что блок обнаружения кода запуска содержит два буферных регис тра, группу сумматоров по модулю два, группу элементов И-НЕ и элемент И, причем информационные входы первого и второго буферных регистров образуют группу информационных входов блока, выход первого буферного регистра подключен к первым

входам сумматоров по модулю два, вторые входы которых образуют информационный вход блока, а выходы подключены к первь м входам элементов И-НЕ группы, вторые входы которых: подключены к выходу второго буферного регистра, а выходы - к входам элемента И, выход которого является выходом блока.

4,Анализатор по п.1, о т л и - чающийся тем, что блок управ ления записью содержит буферный регистр, первый и второй формирователи одиночных импульсов, счетчик режима сравнения, триггер разрешения, четыре элемента ИЖ, триггер задержки, счетчик режима предзаписи, вычитаю-, щий счетчик, первьй задатчик начальных условий, семь элементов И, два элемента НЕ, счетчик тактов записи, счетчик адреса и второй задатчик начальных условий, причем первый, второй и третий информационные входы буферного регистра подключены соответственно к входам адреса, данных и управления блока, первьй выход буферного регистра подключен к входу первого формирователя одиночных импульсов, выход которого подключен к входу сброса счетчика режи

5926714

ма сравнения, входу установки триггера разрешения и первому входу первого элемента ИЛИ, выход которого подключен к входу сброса триггера

5 задержки и входам стробирования счетчика режима предзаписи и вычитающего счетчика, счетный вход вьмитающего счетчика является входом разрешения регистрации блока, вход данных вычи- 10 тающего счетчика подключен к выходу первого задатчика начальных условий, а выход - к установочному входу триггера задержки, выход кото{)ого подключен к первым входам первого и вертого элементов И, второй выход буферного регистра подключен к второму входу третьего элемента И, входу первого элемента НЕ и входу второго задатчика начальных условий,

20 выход которого подключен к входу дан- . ных счетчика режима предзаписи, выходом подключенного к первым входам второго и третьего элементов И, вы ход третьего элемента И подключен к

25 первому входу второго элемента ИЛИ и второму входу первого элемента ИЛИ, третий выход буферного регистра подключен к третьему входу третьего элемента ИЛИ, выход которого подклю30 чен7 к входу сброса триггера разрешения, выходом подключенного к входу разрешения счетчика тактов записи и входу второго формироватеня одиночных импульсов, выход которого является выходом признака- конца процесса регистрации блока, четвертый выход буферного регистра подключен к информационному входу счетчика тактов записи, тактовый и синхронизирующий

Р входы которого подключены соответственно к входу тактирования и входу внешней синхронизации блока, информационный выход счетчика тактов записи подключен к второму входу шес-, того элемента И и является первым выходвм тактирования блока, выход шестого элемента И подключен к второму входу первого элемента И и является вторым выходом тактирования

блока, выход первого элемента И подключен к счетному входу счетчика режима предзаписи, пятый выход ного регистра подключен к второму входу четвертого элемента ЕПИ, первый вход которого подключен к выходу седьмого элемента И, второй вход которого подключен к выходу переполнения счетчика тактов записи, а вы15 I

ход четвертого элемента ИЛИ подключен к входу счетчика адреса, выход которого является выходом адресации блока, второй вход четвертого элемента И подключен к первому входу пятого элемента И, входу второго эле нента НЕ и первому выходу счетчика режима сравнения, выход второго элемента НЕ подключен к первым входам шестого и седьмого элементов И, а выход четвертого элемента И подклю

W

Фиг. 2

26

фиг. 5

5926716

чен к второму входу второго элемента ИЛИ, выход которого соединён со счетным входом счетчика режима cpiaa- нения, второй выход которого прдклю- 5 чен к второму входу пятоГо элемента

И, выходом подключенного к второму входу третьего элемента ИЛИ, первый вход которого подключён If ыходу второго элемента И, вторым входом под- 10 ключенного к выходу первого элемента НЕ.

27

Z8

Z9 чет

Mi

с: 5

iJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Логический анализатор | 1985 |

|

SU1357958A1 |

| Логический анализатор | 1986 |

|

SU1363211A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| Запоминающее устройство | 1981 |

|

SU1018150A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Многоканальное устройство для ввода аналоговых данных | 1988 |

|

SU1501025A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля сложных цифровых устройств и микропроцессорных систем. Целью изобретения является повышение быстродействия. Логический анализатор содержит два буферных регистра, блок памяти данных, блок обнаружения кода запуска, блок управления записью, блок ввода параметров, блок обработки данных и блок отображения. Логический анализатор позволяет осуществлять следующие режимы регистрации входных данных: запуск регистрации по заданному кодовому слову запуска; запуск регистрации после h-ro обнаружения кодового слова запуска; регистрация данных, предшествующих кодовому слову на заданное число тактов; регистрация данных в режиме сравнения массивов; регистрация данных по тактам внеш- - ней синхронизации. Высокое быстродействие логического анализатора обеспечивается за счет аппаратной реализации функции поиска кодовых слов запуска и применение специализированного блока управления записью. 3 з.п. ф-лы, 4 ил. i (Л tc СП СО ю Од

Редактор 0. Юрковецкая

Составитель С. Старчихин

Техред И.Попович Корректор Л. Пилипенко

Заказ 5123/47Тираж 671Подписное

ВШШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Управляющие системы и машины (УСиМ), 1982, W 3, с | |||

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1986-09-23—Публикация

1984-12-18—Подача