(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1628203A1 |

| Синтезатор частот | 1987 |

|

SU1555862A1 |

| Синтезатор частот | 1988 |

|

SU1698988A1 |

| Синтезатор частот | 1987 |

|

SU1631720A1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2024 |

|

RU2827940C1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Синтезатор частот | 1987 |

|

SU1543545A1 |

| Синтезатор частот | 1989 |

|

SU1646053A1 |

| Широкодиапазонный синтезатор с фазовой автоподстройкой частоты управляемого генератора с переключаемыми резонаторами | 2023 |

|

RU2804407C1 |

Изобретение относится к радиотехнике и может быть использовано в приемопередающих устройствах и измерительной технике. Целью изобретения является уменьшение уровня нежелательных составляющих. Синтезатор частот содержит импульсно-фазовый детектор (ИФД) 1, фильтр 2 нижних частот, управляемый генератор 3, делитель 4 частоты с дробным переменным коэффициентом деления, цифрозналоговый преобразователь 5. ИФД 1 содержит RS- триггер б, ключи 7,8,9 и 10, повторители 11, 12 и 13 напряжения, источник 14 тока и конденсаторы 15,16 и 17. Делитель 4 содержит блок 18 суммирования и блок 19 деления. В синтезаторе отсутствует ограничение снизу на величину длительности сигнала на выходе делителя 4, что при равной крутизне ИФД 1 приводит к расширению уровней напряжений на выходе ИФД 1. 2 ил.

о ю

00

о

00

чэ

Изобретение относится к радиотехнике и может быть использовано в приемопередающих устройствах и измерительной технике.

Целью изобретения является уменьше- ние уровня нежелательных составляющих.

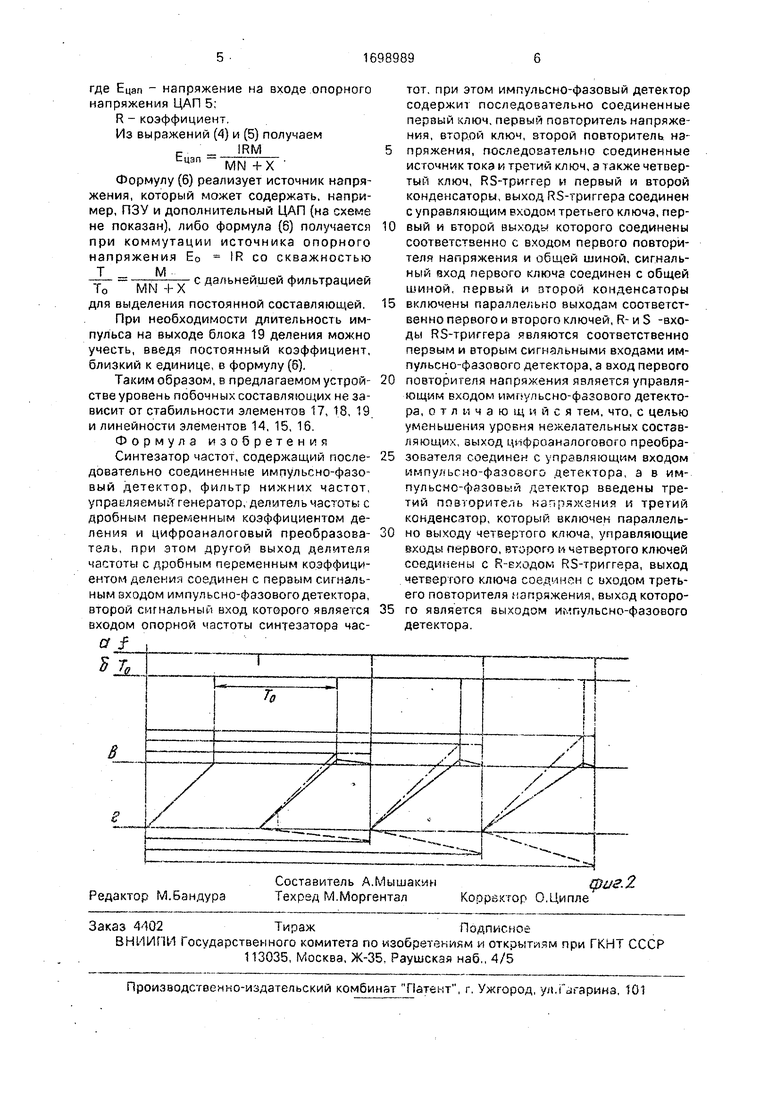

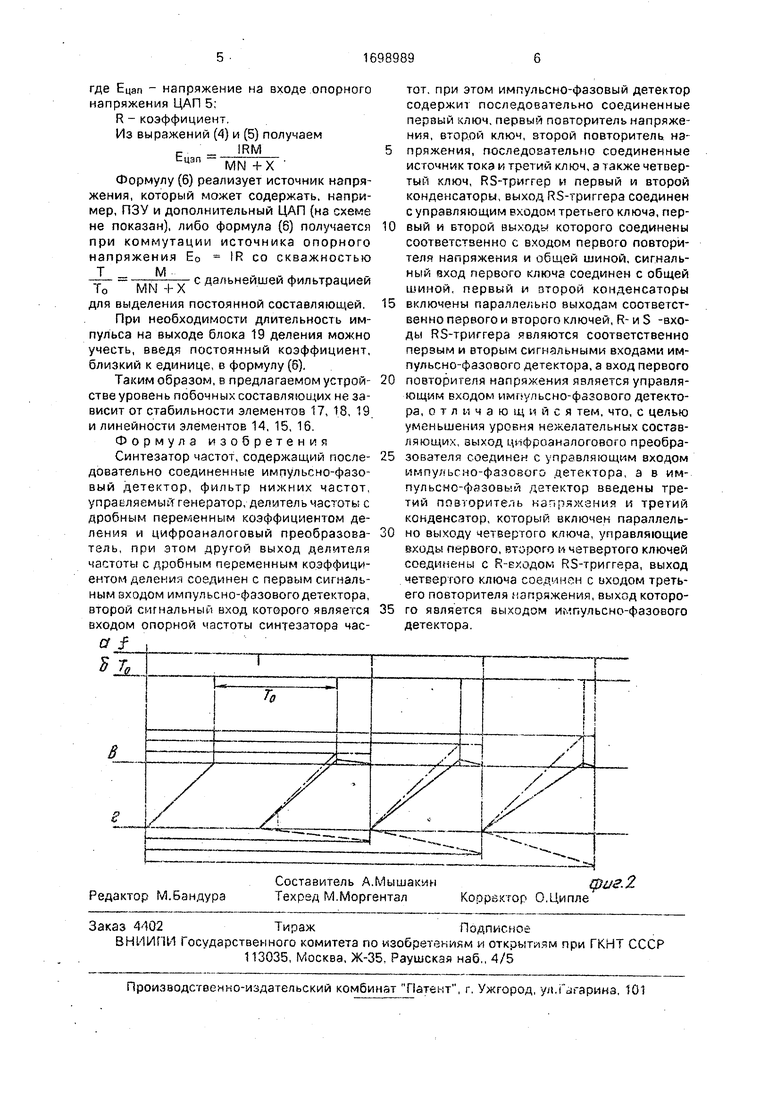

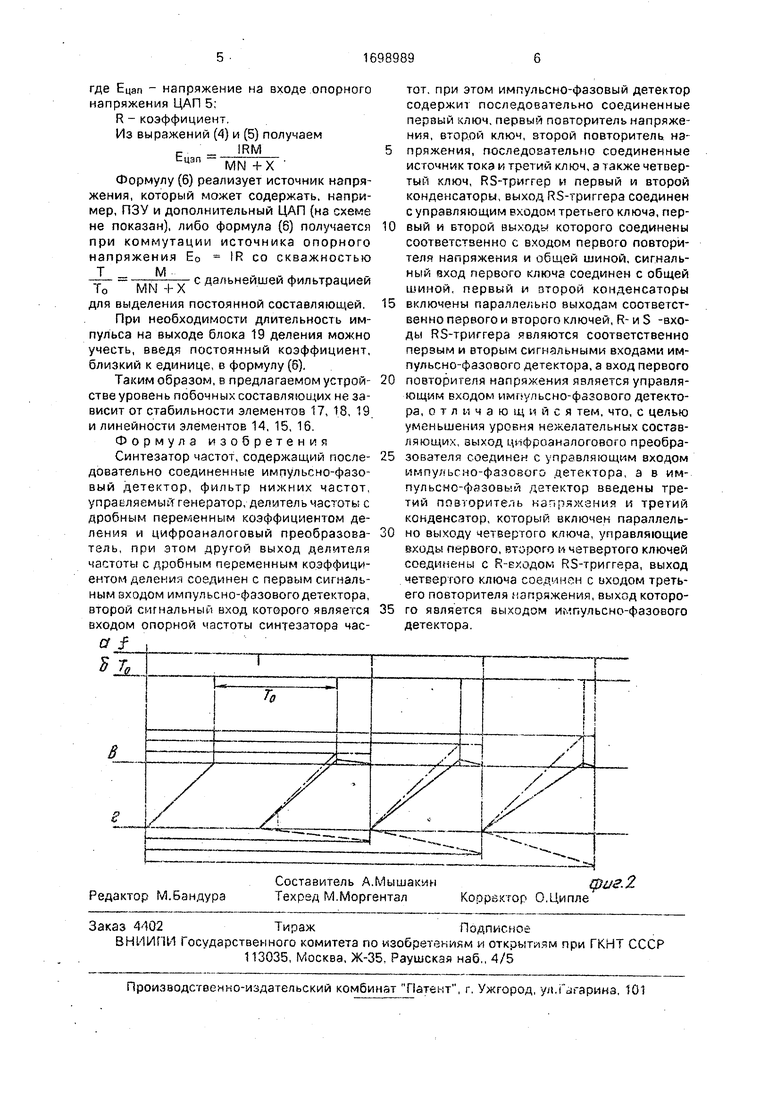

На фиг.1 приведена электрическая структурная схема синтезатора частот; на фиг.2 а, б, в, г - диаграммы работы.

Синтезатор частот содержит импульс- но-фазовый детектор (ИФД) 1, фильтр 2 нижних частот, управляемый генератор (УГ) 3, делитель 4 частоты с дробным переменным коэффициентом деления (ДДПКД), цифроаналоговый преобразователь (ЦАЛ) 5.

ИФД 1 содержит RS-трштер б, первый, второй, третий и четвертый ключи 7 8, 0 и 10, первый, второй и третий повторители 11, 12 и 13 напряжения, источник 14 тока и первый, аторой и третий конденсаторы 15, 16 и 17. ДДПКД 4 содержит блдк 18 суммирования и блок 19 деления.

Синтезатор частот работает следующим образом.

Период эталонной частоты на входе эта- лонной частоты Т0 и период управляемого генератора 3 Т связаны между собой следу- ющим образом:

т - мт°m

Т MN+X Ш

где М - информационная емкость блока 18 суммирования;.

N - коэффициент деления блока 19 деления;

X - числовое значение кода на входе управления, определяющее дробную часть выходной частоты.

Наличие дробной части приводит к непрерывному фазовому сдвигу выходной частоты управляемого генератора 3 по отношению к сигналу на входе эталонной частоты (см. эпюру 2,а - сигнал на выходе блока 19 деления, эпюре 2,6 - сигнал на вход эталонной частоты). Как только фазовый сдвиг выходного сигнала УГ 3 достигает целого периода, на выходе переноса блока 18 суммирования появляется сигнал, по которому в блоке 19 деления вырезается один импульс сигнала УГ 3. Таким образом, фазовый сдвиг сигнала на выходе блока 19 деле- ния имеет пилообразный характер. Компенсация фазового сдвига осуществляется током ЦАП 5 (эпюра 2,в - штриховая линия - напряжение на первом конденсаторе 15 от тока ЦАП 5, штрихпунктиркай ли- ния-напряжение от тока источника 14тока, сплошная линия - суммарное напряжение).

По переднему фронту короткого импульса на выходе блока 19 деления, изменяется значение кода на выходе блока 18 суммирования и соответственно на выходе ДДПКД 4 и в соответствии с новым кодом, отличающимся на X от предыдущих, устанавливается новый выходной ток ЦАП 5. Первый ключ 7 при этом замыкается, разряжая первый конденсатор 15. По заднему фронту короткого импульса на выходе блока 19 деления сигнал на выходе RS-триггера 6, который может быть выполнен в виде D- триггера, переключает третий ключ 9 и разность токов от источника 14 тока и ЦАП 5 начинает заряжать первый конденсатор 15. Напряжение с первого конденсатора 15 через замкнутый второй ключ 8 передается на второй конденсатор 16. По приходу короткого импульса на вход эталонной частоты RS- тригтер б устанавливается в единичное состояние, ток источника 14 тока замыкается на общую шину через первый аход третьего ключа 9. Первый конденсатор 15 разряжается током ЦАП 5. При появлении переднего фронта второго короткого импульса на выходе блока 19 деления размыкается второй ключ 8, замыкается первый и четвертый ключи 7 и 10. Первый конденсатор 15 разряжается, напряжение с второго конденсатора 16 через четвертый ключ 10 передается на третий повторитель 13 и далее на вход фильтра 2. Первый, второй и третий повторители 11, 12 и 13 с высоким входным сопротивлением препятствует разряду первого, второго и третьего конденсаторов 15, 16 и 17.

При появлении заднего фронта первый и четвертый ключи 7 и 10 размыкаются, второй ключ 8 замыкается.

Для компенсации, учитывая, что длительность импульса на выходе блока 19 де-. ления много меньше Т0, необходимо

Т0Д1 1ДТ,

(2)

где ДТ - разность между Т0 и выходе блока 19 деления;

I - ток источника 14 тока;

Д - приращение тока ЦА Так как

X TO

;х X;I ДТ MN +X

то

Д ругой

Д

IX

MN+X С другой стороны

1цап X ЕцапХ

М

RM

где Ецап - напряжение на входе опорного напряжения ЦАП 5;

R - коэффициент.

Из выражений (4) и (5) получаем IRM

Формулу (6) реализует источник напряжения, который может содержать, например, ПЗУ и дополнительный ЦАП (на схеме не показан), либо формула (5) получается при коммутации источника опорного напряжения Е0 IR со скважностью

Л -Мс дальнейшей фильтрацией

То MN + X для выделения постоянной составляющей.

При необходимости длительность импульса на выходе блока 19 деления можно учесть, введя постоянный коэффициент, близкий к единице, в формулу (б).

Таким образом, в предлагаемом устройстве уровень побочных составляющих не зависит от стабильности элементов 17, 18, 19. и линейности элементов 14,15,16.

Формула изобретения

Синтезатор частот, содержащий последовательно соединенные импульсно-фазо- вый детектор, фильтр нижних частот, управляемый генератор, делитель частоты с дробным переменным коэффициентом деления и цифроаналоговый преобразователь, при этом другой выход делителя частоты с дробным переменным коэффициентом деления соединен с первым сигнальным входом импульсно-фэзового детектора, второй сигнальный вход которого является входом опорной частоты синтезатора часa f $

тот. при этом импульсно-фазовый детектор содержит последовательно соединенные первый ключ, первый повторитель напряжения, второй ключ, второй повторитель напряжения, последовательно соединенные источник токэ и третий ключ, а также четвертый ключ, RS-триггер и первый и второй конденсаторы, выход RS-триггера соединен с управляющим входом третьего ключа, первый и второй выходы которого соединены соответственно с входом первого повторителя напряжения и общей шиной, сигнальный вход первого ключа соединен с общей шиной, первый и второй конденсаторы

включены параллельно выходам соответственно первого и второго ключей, R- и S -входы RS-триггера являются соответственно первым и вторым сигнальными входами им- пульсно-фазового детектора, а вход первого

повторителя напряжения является управляющим входом импульсно-фазового детектора, о т л и ч а ю щ и и с я тем, что, с целью уменьшения уровня нежелательных составляющих, выход цифроаиалогового преобразователя соединен с управляющим входом импульсно-фазового детектора, э в им- пульсно-фазовый детектор введены третий повторитель напряжения и третий конденсатор, который включен параллельно выходу четвертого ключа, управляющие входы первого, второго м четвертого ключей соединены с R-входом RS-триггера, выход четвертого ключа соединен с входом третьего повторителя напряжения, выход которо5 го является выходом импульсно-фазового детектора.

| Синтезатор частот | 1988 |

|

SU1628203A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-12-15—Публикация

1988-04-08—Подача