Изобретение относится к радиотехнике и может быть использовано в при емно-передающих устройствах и в измерительной технике с

Целью изобретения является повышение спектральной чистоты выходных сигналов о

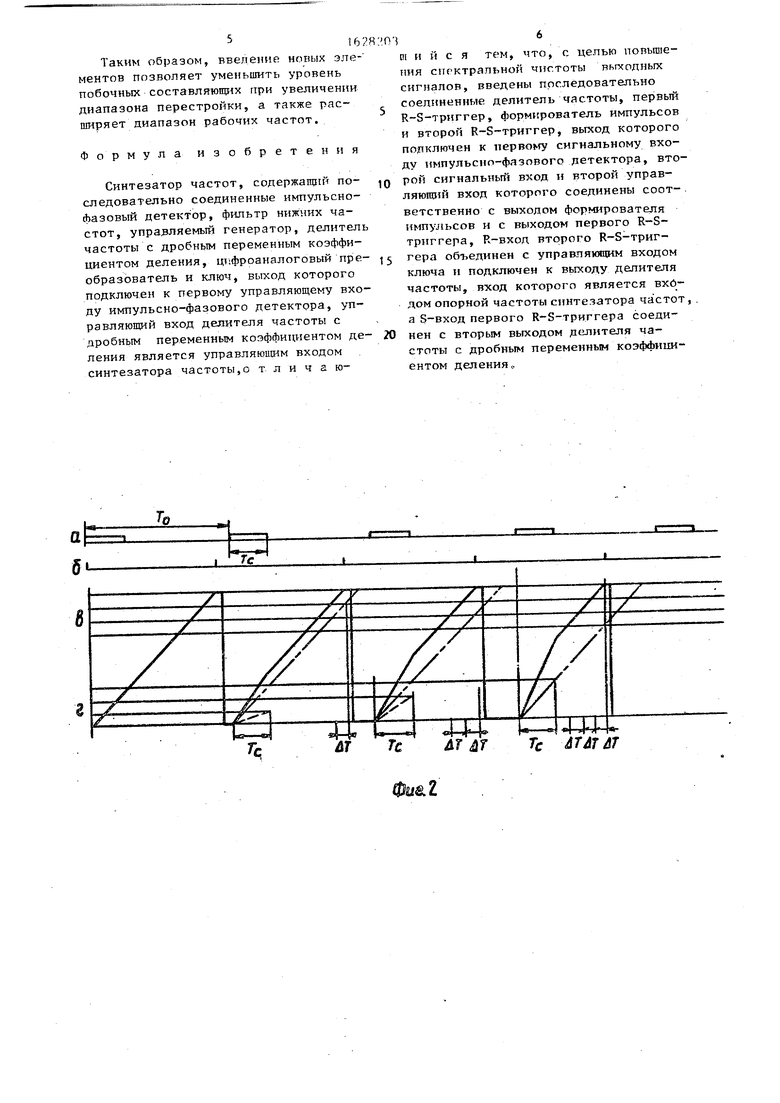

На фиго 1 изображена эпектричес- кая структурная схема синтезатора частот; на фиг„ 2 - диаграммы работы

Синтезатор частот содержит импулъ но-фазовый детектор (ИФД) 1, фильтр

2нижних частот, управляемый генератор 3, делитель частоты с дробным переменным коэффициентом деления (ДДПКД) 4, делитель 5 частоты, первый R-S-триггер 6, второй R-S-тригге

7, формирователь 8 импульсов, цифро- аналоговый преобразователь (ЦАП) 9, ключ 10о При этом ИФД 1 состоит из первого 11, второго 12 и третьего 13 ключей, первого повторителя 14, второго повторителя 15, генератора тока 16, первого конденсатора 17, второго конденсатора 18, ДДПКД А содержит блоки суммирования 19 и деления 20с

Синтезатор частот работает следую щим образом

Управляемый генератор 3, ДДПКД 4, ИФД 1 и фильтр 2 образуют кольцо фазовой автоподстройки частоты Опорна частота кольца автоподстройки поступает на вход делителя 5„

На выходе делителя 5 период импульса равен Т0, длительность равна Т0/К (либо кратно ей), где К - коэффициент деления делителя 5„ Коэффициент деления блока деления 20 ДДПКД 4 равен N или N+1 и определен на его дополнительной шине управления, причем этот код определяет, какую часть периода блок деления 20 делит входную частоту управляемого генератора 3 на N+1: в оставшуюся часть пе риода производится деление на N0 Период частоты управляемого генератора

3равен Т/М, где М - информационная емкость входа управления синтезатора частот, X - числовое значение кода на этом входе, X - значени дробной части сдвига частоты управляемого генератора 30

На выходе блока суммирования 19

ДДПКД 4 содержится текущее общее опережение сигналом управляемого генератора целой части частоты выходного сигнала управляемого генератора 3, целой части частоты выходного сигнала

5

0 5

Q

д

Q

5

управляемого генератора 3 Когда опережение достигает целого периода ,на выходе переноса блока суммирования 19 появляется импульс, уменьшая количество делений на N на единицу и увеличивая количество делений на N+1 в блоке деления 20, т е0 из входного сигнала управляемого генератора 3 вырезается один импульс

За счет опережения сигналом управляемого генератора 3 целой части выходного сигнала и вырезания импульса на выходе ИФД 1 (без учета компенсации ЦАП 9) выходной сигнал содержит постоянную и пилообразную составляющие о Стробирование выходного тока 1Щ1 9 на время ключом 10 и суммирование тока ЦАП 9 и тока генератора тока 16 ИФД позволяет устранить пилообразную составляющую в выходном сигнале ИФД 1 следующим образом

При поступлении сигнала на второй вход ИФД 1 (эпюра а) первый и второй R-S-триггеры 6 и 7 устанавливаются в нулевое состояние, при этом закрывается первый ключ 11 ИФД 1, второй ключ 12 соединяет выход генератора тока 16 с первым конденсатором 17« Начинается заряд конденсатора 17 суммой токов генератора тока 16 (эпюра в, штрихпун тирнал линия) и ЦАП 9 (эпюра в, штриховая линия). Через время Tt ключ 10 отключает первый конденсатор 17 от ЦАП 9 и подключает выход ЦАП 9 к общей шине0 По приходу импульса с выхода ДДПКД 4 (эпюра б) переключается в состояние логической единицы первый R-S-триггер 6, отключая генератор тока 16 от первого конденсатора (эпюра - в, сплошная линия)„ На выходе формирователя 8 появляется короткий импульс, открывающий третий ключ 13, при этом напряжение с первого конденсатора 17 передается через первый повторитель 14 на второй конденсатор 18 (эпюра г) Первый конденсатор 17 разряжается через первый ключ 11, открытый единичным уровнем с выхода второго R-S-триггера 7.

Для компенсации необходимо выполнение условия

л т 1ЙТ

61 -- , Lc

где А I - шаг квантования ЦАП 9;

I - шаг генератора тока 165 UT - разность лежду периодами сигналов на входах ИФД 1.

J16

Таким образом, введение ноных элементов позволяет уменьшить уровень побочных составляющих при увеличении диапазона перестройки, а также расширяет диапазон рабочих частот.

Формула изобретения

Синтезатор частот, содержащий по- следовательно соединенные импулъсно- сЬазовый детектор, фильтр нижних частот, управляемый генератор, делитель частоты с дробным переменным коэффициентом деления, цъфроаналоговый пре- образователь и ключ, выход которого подключен к первому управляющему входу импульсно-фазового детектора, управляющий вход делителя частоты с дробным переменным коэффициентом де- ления является управляющим входом синтезатора частоты,о т л и ч а ю6

m и и с я тем, что, с целью повышения спгктральной чистоты выходных сигналов, введены последовательно соединенные делитель частоты, первый R-S-триггер, формирователь импульсов и второй R-S-триггер, выход которого подключен к первому сигнальному входу импульсно-фазового детектора, второй сигнальный вход и второй управляющий вход которого соединены соответственно с выходом формирователя импульсов и с выходом первого R-S- триггера, R-вход второго R-S-триг- гера объединен с управляющим входом ключа и подключен к выходу делителя частоты, вход которого является входом опорной частоты синтезатора частот, а S-вход первого R-S-триггера соединен с вторым выходом делителя частоты с дробным переменным коэффициентом деления о

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1698989A1 |

| Синтезатор частот | 1988 |

|

SU1698988A1 |

| Синтезатор частот | 1987 |

|

SU1555862A1 |

| Синтезатор частот | 1987 |

|

SU1631720A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Синтезатор с коммутируемой полосой пропускания кольца фазовой автоподстройки частоты | 2023 |

|

RU2812098C1 |

| Синтезатор частот | 1987 |

|

SU1474838A1 |

| Синтезатор частот | 1989 |

|

SU1646053A1 |

Изобретение относится к радиотехнике. Цель изобретения - повыше- |ние спектральной чистоты выходных сигналово Синтезатор частот содержит импульсно-фазовый детектор () 13 фильтр 2 нижних частот, управляемый генератор 3, делитель с дробным переменным коэффициентом деления (ДДПКД) 4, делитель 5 частоты, первый R-S-триггер 6, второй R-S-триг- гер 7, формирователь 8 импупьсов, цифроаналоговый преобразователь (ЦАП) 9, ключ 10о ИФД 1 содержит первый 11, второй 12, третий 13 ключи, первый 14, второй 15 повторители, генератор 16 тока и первый 17 и второй 18 конденсаторы ДДПКД 4 включает блок 19 суммирования и блок 20 деления. Управляемый генератор 3, ДДПКД 4, ИФД 1 и фильтр 2 образуют кольцо фазовой автоподстройки, при этом ДПГДЦ 4 осуществляет деление частоты на коэффициент К клг N--1 в зависимости, от кода управления на шине управления блока 20 .ля, В связи с этим на выхода ИФД 1 сигнал содержит постоянней и пиле 3раз- ную составляющие. За счет суммирования токов ЦАП 9 и генераита т6 устраняется пилообразная оставлгтюцдя в сигнале ИФД 1„ Управление работой этих элементов осуществляемся прт; помоши первого и второго 11- -трпггй- ров 6, 7 и ключа 10, Л пл, уз

а б

/о

Те

V.

23

v

7/

j/

S :.

ш

ta

z

jL

s

/

/

У /

/7

A

Я

7c

44

AT Jf

Te AT&T &1

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| Синтезатор частот | 1987 |

|

SU1555862A1 |

Авторы

Даты

1991-02-15—Публикация

1988-01-04—Подача