Изобрегение относится к радиотехнике и может быть использовано в приемопередающих устройствах и в измерительной технике.

Целью изобретения является повышение спектральной чистоты выходных сигналов.

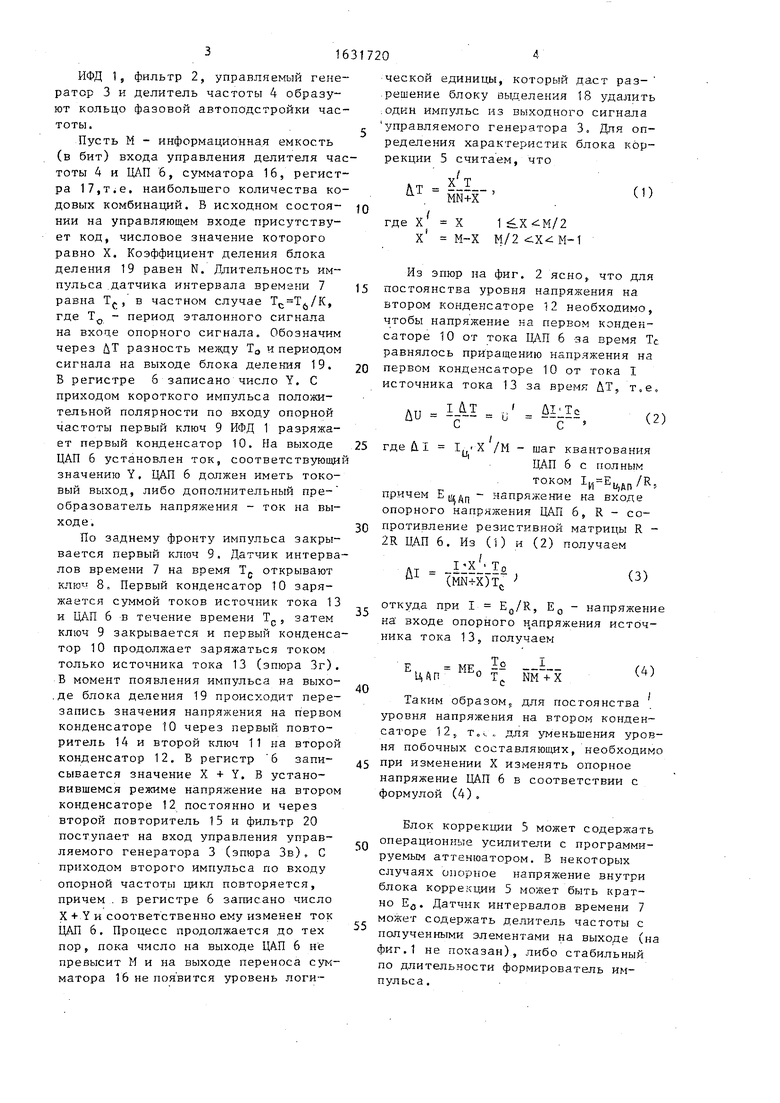

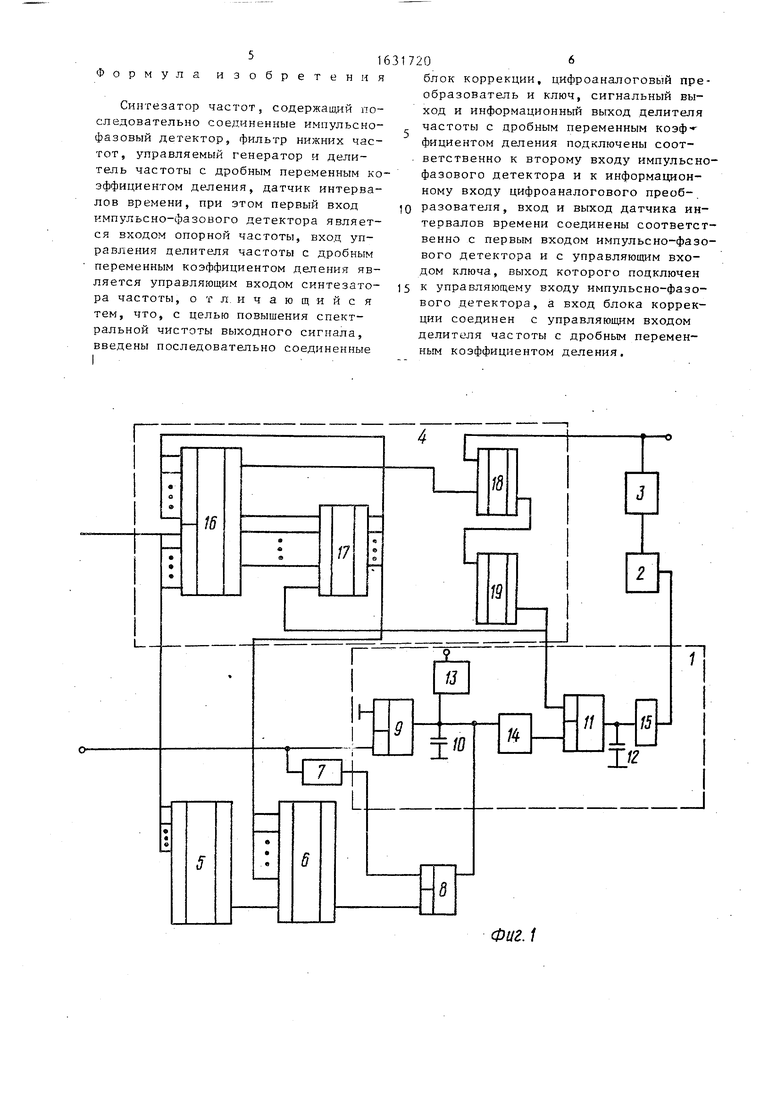

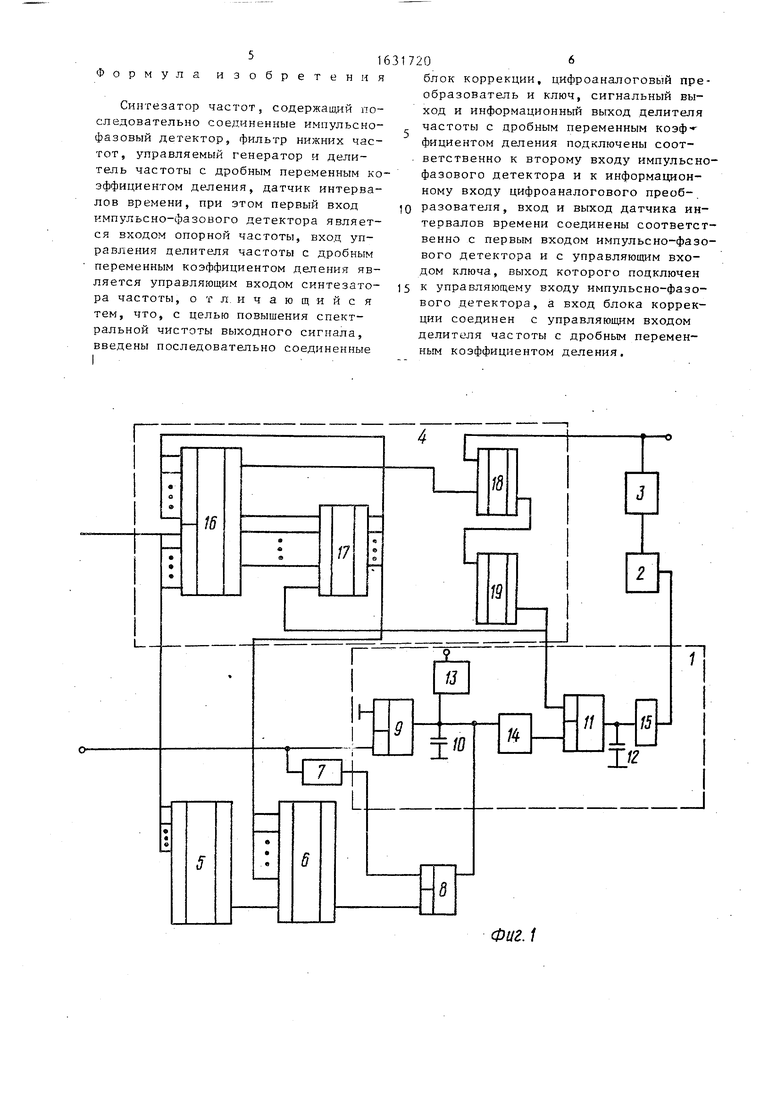

На фиг.1 представлена структурная электрическая схема синтезатора частот; на фиг.2 (а, б, в, г) - временные диаграммы.

Синтезатор частот содержит им- пульсно-фазовый детектор (ИФД) 1, фильтр 2 нижних частот, управляемый генератор 3, делитель частоты 4 с

дробным переменным коэффициентом деления, блок коррекции 5, цифроанало- говый преобразователь (ЦАП) 6, датчик интервалов времени 7, ключ 8. При этом ИФД 1 состоит из первого ключа 9, первого конденсатора 10, второго ключа 11, второго конденсатора 12, источника тока 3, первого повторителя 14, второго повторителя 15. Делитель частоты 4 содержит сумматор 16 кодов, регистр 17 фазы, блок выделения 18 импульса, блок деления 19.

Синтезатор частот работает следующим образом.

05

го vj

N5

ИФД 15 фильтр 2, управляемый генератор 3 и делитель частоты 4 образуют кольцо фазовой автоподстройки частоты.

Пусть М - информационная емкость (в бит) входа управления делителя частоты 4 и ЦАП 6, сумматора 16, регистра 17,т.е. наибольшего количества кодовых комбинаций. В исходном состоянии на управляющем входе присутствует код, числовое значение которого равно X. Коэффициент деления блока деления 19 равен N. Длительность импульса датчика интервала времени 7 равна Tf, в частном случае , где Т0 - период эталонного сигнала на входе опорного сигнала. Обозначим через ДТ разность между Т0 ч периодом сигнала на выходе блока деления 19. В регистре 6 записано число Y. С приходом короткого импульса положительной полярности по входу опорной частоты первый ключ 9 ИФД 1 разряжает первый конденсатор 10. На выходе ЦАП б установлен ток, соответствующий значению Y, ЦАП 6 должен иметь токовый выход, либо дополнительный пре- образователь напряжения - ток на выходе.

По заднему фронту импульса закрывается первый ключ 9. Датчик интервалов времени 7 на время Тс открывают клютг 8, Первый конденсатор 10 заряжается суммой токов источник тока 13 и ЦАП 6 в течение времени Тс, затем ключ 9 закрывается и первый конденсатор 10 продолжает заряжаться током только источника тока 13 (эпюра Зг). В момент появления импульса на выходе блока деления 19 происходит перезапись значения напряжения на первом конденсаторе 0 через первый повторитель 14 и второй ключ 11 на второй конденсатор 12. В регистр 6 записывается значение X + Y. В установившемся режиме напряжение на втором конденсаторе 12 постоянно и через второй повторитель 15 и фильтр 20 поступает на вход управления управляемого генератора 3 (эпюра Зв), С приходом второго импульса по входу опорной частоты цикл повторяется, причем в регистре 6 записано число X + Y и соответственно ему изменен ток ЦАП 6, Процесс продолжается цо тех пор, пока число на выходе ЦАП 6 не превысит М и на выходе переноса сумматора 16 не появится уровень логической единицы, который даст разрешение блоку выделения 18 удалить один импульс из выходного сигнала управляемого генератора 3. Для определения характеристик блока коррекции 5 считаем, что

AT

х т

где X X

/

MN+X

X М-Х

(1)

1 :. М/2 M-1

Из эпюр на фиг. 2 ясно,, что для постоянства уровня напряжения на втором конденсаторе 2 необходимо, чтобы напряжение на первом конденсаторе 10 от тока ЦАП 6 за время Тс равнялось приращению напряжения на первом конденсаторе 10 от гока I источника тока 13 за время ДТ,

т о е«

До - Ш .

I

и

С

(2)

где uI Тц-Х /М - шаг квантования

ЦАП 6 с полным

0

Wn/R.

током

причем - напряжение на входе опорного напряжения ЦАП 6, R - сопротивление резистивиой матрицы R - 2R ЦАП 6. Из (1) и (2) получаем

(MN-fX)i;

Д1

;

(3)

35

откуда при I EQ/R, Е0 - напряжение на входе опорного напряжения источника тока 13, получаем

0

5

0

5

То

I

щТх

(4) /

Таким образом5 для постоянства уровня напряжения на втором конденсаторе 12, т„1., для уменьшения уровня побочных составляющих, необходимо при изменении X изменять опорное напряжение ЦАП 6 в соответствии с формулой (4).

Блок коррекции 5 может содержать операционные усилители с программируемым аттенюатором. В некоторых случаях опорное напряжение внутри блока корре сции 5 может быть кратно Е0. Датчик интервалов времени 7 может содержать делитель частоты с полученными элементами на выходе (на фиг.1 не показан), либо стабильный по длительности формирователь импульса .

51

Формула изобретения

Синтезатор частот, содержащий последовательно соединенные импульсно- фазовый детектор, фильтр нижних частот, управляемый генератор и делитель частоты с дробным переменным коэффициентом деления, датчик интервалов времени, при этом первый вход импульсно-фазового детектора является входом опорной частоты, вхоц управления делителя частоты с дробным переменным коэффициентом деления является управляющим входом синтезатора частоты, отличающийся тем, что, с целью повышения спектральной чистоты выходного сигнала, введены последовательно соединенные I

7206

блок коррекции, цифроаналоговый преобразователь и ключ, сигнальный выход и информационный выход целителя частоты с дробным переменным коэф- фициентом деления подключены соответственно к второму входу импульсно- фазового детектора и к информационному входу цифроаналогового преобразователя, вход и выход датчика интервалов времени соединены соответственно с первым входом импульсно-фазового детектора и с управляющим входом ключа, выход которого подключен

к управляющему входу импульсно-фазового детектора, а вход блока коррекции соединен с управляющим входом делителя частоты с дробным переменным коэффициентом деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1988 |

|

SU1698988A1 |

| Синтезатор частот | 1987 |

|

SU1555862A1 |

| Синтезатор частот | 1988 |

|

SU1698989A1 |

| Синтезатор частот | 1988 |

|

SU1628203A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1984 |

|

SU1283964A1 |

| Синтезатор частот | 1987 |

|

SU1543545A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| СИНТЕЗАТОР ЧАСТОТЫ С ДЕЛЕНИЕМ НА ДРОБНОЕ ЧИСЛО И КОРРЕКЦИЕЙ ОСТАТОЧНОЙ ПОГРЕШНОСТИ И СПОСОБ СИНТЕЗА ЧАСТОТЫ | 1994 |

|

RU2134930C1 |

Изобретение относится к радиотехнике. Цель изобретения - повыше- ние спектральной чистоты выходных сигналов. Синтезатор частот содержит им- пульсно-фазовый детектор (ИФД) 1, фильтр 2 нижних частот, управляемый генератор 3, делитель частоты 4 с дробным переменным коэффициентом деления, блок коррекции 5, цифроаналотовый преобразователь (ЦАП) 6, датчик интервалов времени 7, ключ 8. При этом ИФД 1 состоит из первого ключа 9, первого конденсатора 10, второго ключа 1 1 , второго конденсатора 12, источника тока 13, первого повторителя 14, второго повторителя 15. Делитель частоты 4 содержит сумматор 16 кодов, регистр 17 фазы, блок выделения 18 импульса, блок целения 19. Для уменьшения уровня помех необходимо, чтобы напряжение на выходе второго конденсатора 12 было постоянным, для этого напряжение на первом конденсаторе 10 от тока ЦАП 6 за время TC равнялось приращению напряжения от тока источника тока 13 за время ДТ. Задание величины напряжения ЦАП 6 и временных интервалов осуществляется при помощи блока коррекции 5 и датчика интервалов времени 7. 2 ил. g (Л

Фиг.1

| Гибсс Г | |||

| Темил | |||

| Анализатор спектра на базе синтезатора частоты с контуром ФАПЧ | |||

| - Электроника, 1978, f 9, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-28—Публикация

1987-10-05—Подача