Изобретение относится к радиотехнике и может быть использовано в приемопередающих устройствах и в измерительной технике.

Целью изобретения является расширение диапазона выходных частот При сохранении уровня подавления помех добротности.

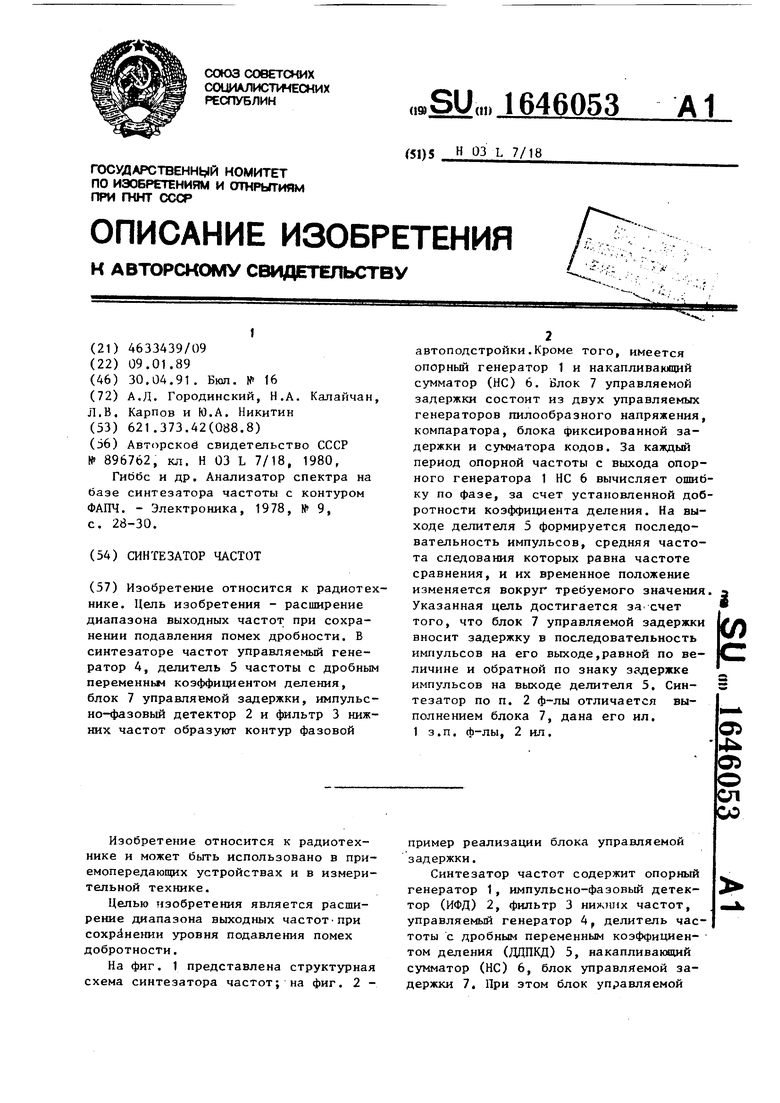

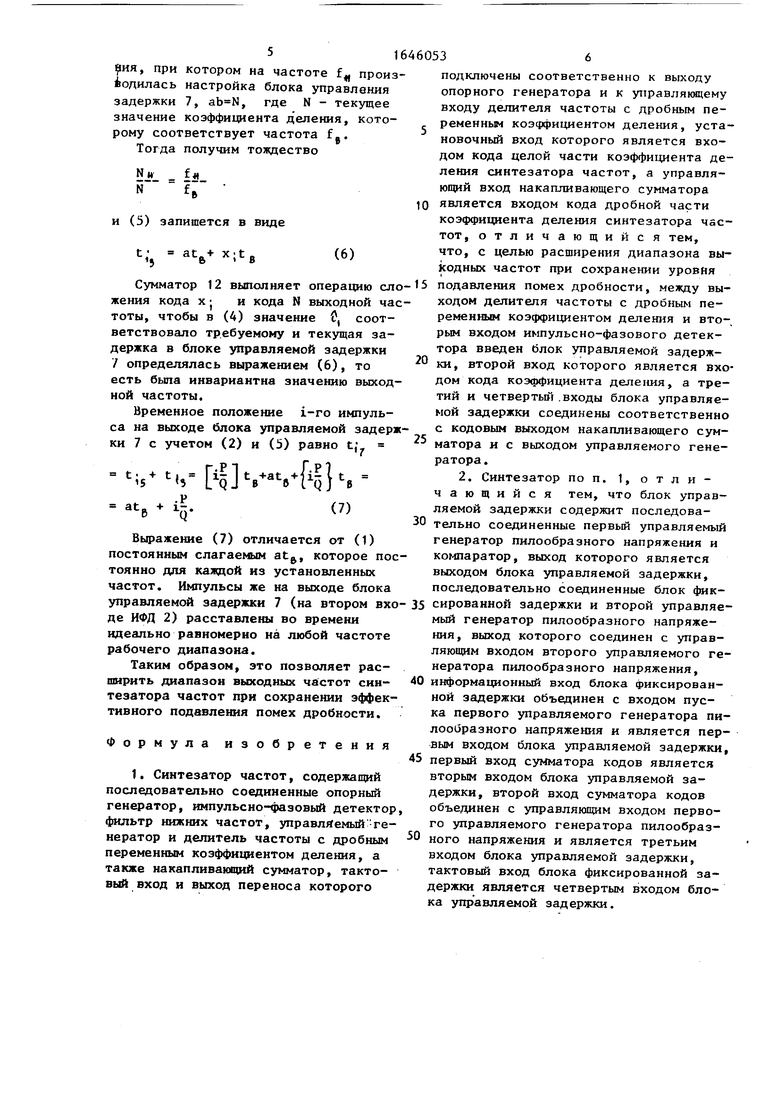

На фиг. 1 представлена структурная схема синтезатора частот; на фиг. 2 пример реализации блока управляемой задержки.

Синтезатор частот содержит опорный генератор 1, импульсно-фаэовый детектор (ИФД) 2, фильтр 3 нижних частот, управляемый генератор 4, делитель частоты с дробным переменным коэффициентом деления (ДЦПКД) 5, накапливающий сумматор (НС) 6, блок управляемой задержки 7. При этом блок управляемой

задержки 7 состоит из первого управляемого генератора пилообразного напряжения (УПШ) 8, компаратора 9, блока фиксированной задержки 10, второго УГПН 11, сумматора 12 кодов.

Синтезатор частот работает следующим образом.

На второй вход блока управляемой задержки подан код выходной частоты N, состоящий из целой и дробной Јм частей: + Јм|. На установочный вход ДДПКД 5 подан код Nj целой части N, на управляющий вход НС 6 подан код Гм1 дробной части N. Так- тируется НС 6 импульсами с выхода опорного генератора 1. За каждый такт Ть опорной частоты fon НС 6 вычисляет ошибку по фазе U.Cf , вызванную установленной дробностью V. Эта ошибка линейно накапливается и, когда содержимое НС 6 превысит его емкость (то есть когда ошибка по фазе превысит 21Г или один период частоты fft управляемого генератора 4) на выходе НС 6 появляется сигнал переноса, который дает команду ДДПКД 5 увеличить коэффициент деления Nj на единицу (например, путем исключения из процесса счета одного входного импульса). В этот момент ошибка по фазе (в уменьшается на 2/и и далее процесс циклически повторяется. В результате, на выходе ДДНКД 5 формируется последовательность импульсов, средняя час- тота следования которых равна частоте сравнения f0 , а их временное положение (фаза) изменяется вокруг требуемого (среднего) значения по пило- образноступенчатому закону с наиболь- дам отклонением от среднего, равным периоду частоты управляемого генератора 4. НС 6 вырабатывает код ошибки по фазе х, зависящий от Јм|, но не зависящий от мЗ (инвариантный XJ). Этот код поступает на третий вход блока управляемой задержки 7 и вносимая им задержка равна по величине и об- ратна по знаку задержке импульсов на выходе ДДЛКД 5. Величина наибольшей задержки на выходе блока управляемой, задержки 7 равна периоду колебаний управляемого генератора 4 в любой точке выходного диапазона и, следо- ,вательно, в любой точке выходного Ди- апазона происходит полная компенсация временной модуляции импульсов на выходе ДДНКД 5. Рассмотрим этот вопрос подробнее.

Если выразить частоты f

Q-FC и

fe Р-Fc в долях шага сетки Ff, тогда для момента появления 1-го импульса строго периодической последовательности на выходе опорного генератора 1 (на первом входу ИФД 2) можно записать

Ч Т е тК+НК (°

где t; 1/ffl.

Аналогично для момента появления , 1-го импульса на выходе ДДПКД 5

-СС оЧ-Ш в- (2);

Код х на выходе НС 6 определяется

формулой

(3)

причем НС Ъ тактируется импульсами с выхода опорного генератора 1. Импульсы с выхода ДДКПД 5 запускают первый УГПН 8. Напряжение на его выходе U8 Еt;5/Ј8. Второй УГПН запускается теми же импульсами с выхода ДДКПД 5, но задержанными на время ate, кратное целому числа а периодов выходного колебания Јр в блоке фиксированной задержки 10. Напряжение на выходе второго УГПН 11:

и« EUjj-at,)/,

причем 1/мсЈ0. Компаратор 9 срабатывает в момент равенства напряжений U e и U,,

tjft. . «jj,;2Јй

или

t. - .t XГ e o,-V

(4)

Если выбрать Јг « x,- Т„; 0, -х, Т„ + + btft, то (4) перепишется в виде

S ач+х; г v

(5)

где ТH k/f« выходная частота, на которой производится настройка блока управляемой задержки 7, а и k целые положительные числа.i

Необходимо, чтобы

N,

const - -где Мм коэффициент делейия, при котором на частоте f производилась настройка блока управления задержки 7, , где N - текущее значение коэффициента деления, которому соответствует частота f. Тогда получим тождество

о If

и (5) запишется в виде

15

av

;tB

(6)

Сумматор 12 выполняет операцию ело- 5 жения кода х и кода N выходной частоты, чтобы в (А) значение 0, соответствовало требуемому и текущая задержка в блоке управляемой задержки У определялась выражением (6), то есть была инвариантна значению выходной частоты.

Временное положение 1-го импульса на выходе блока управляемой задержки 7 с учетом (2) и (5)

20

равно t;

25

+

KJv vH

S

at

В

.Р

XQ

(7)

Выражение (7) отличается от (1) постоянным слагаемым atfr, которое постоянно для каждой из установленных частот. Импульсы же на выходе блока

0

5

0

5

0

подключены соответственно к выходу опорного генератора и к управляющему входу делителя частоты с дробным переменным коэффициентом деления, установочный вход которого является входом кода целой части коэффициента деления синтезатора частот, а управляющий вход накапливающего сумматора является входом кода дробной части коэффициента деления синтезатора частот, отличающийся тем, что, с целью расширения диапазона вы- Кодных частот при сохранении уровня подавления помех дробности, между выходом делителя частоты с дробным переменным коэффициентом деления и вторым входом импульсно-фазового детектора введен блок управляемой задержки, второй вход которого является входом кода коэффициента деления, а третий и четвертый.входы блока управляемой задержки соединены соответственно с кодовым выходом накапливающего сумматора и с выходом управляемого генератора .

2. Синтезатор по п. 1, отличающийся тем, что блок управляемой задержки содержит последовательно соединенные первый управляемый генератор пилообразного напряжения и компаратор, выход которого является выходом блока управляемой задержки, последовательно соединенные блок фик

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| Синтезатор частот | 1988 |

|

SU1628203A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Синтезатор частот | 1987 |

|

SU1555862A1 |

| СИНТЕЗАТОР СЕТКИ ЧАСТОТ НА БАЗЕ КОНТУРА ФАПЧ С КОМПЕНСАЦИЕЙ ПОМЕХ ДРОБНОСТИ | 2012 |

|

RU2491713C1 |

| Синтезатор частот | 1988 |

|

SU1698988A1 |

| Синтезатор частот | 1988 |

|

SU1698989A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2602991C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| Синтезатор частот | 1985 |

|

SU1314454A1 |

Изобретение относится к радиотехнике. Цель изобретения - расширение диапазона выходных частот при сохранении подавления помех дробности. В синтезаторе частот управляемый генератор 4, делитель 5 частоты с дробным переменным коэффициентом деления, блок 7 управляемой задержки, импульс- но-фазовый детектор 2 и фильтр 3 нижних частот образуют контур фазовой автоподстройки.Кроме того, имеется опорный генератор 1 и накапливающий сумматор (НС) 6. блок 7 управляемой задержки состоит из двух управляемых генераторов пилообразного напряжения, компаратора, блока фиксированной задержки и сумматора кодов. За каждый период опорной частоты с выхода опорного генератора 1 НС 6 вычисляет ошибку по фазе, за счет установленной добротности коэффициента деления. На выходе делителя 5 формируется последовательность импульсов, средняя частота следования которых равна частоте сравнения, и их временное положение изменяется вокруг требуемого значения. Указанная цель достигается за счет того, что блок 7 управляемой задержки вносит задержку в последовательность импульсов на его выходе,равной по величине и обратной по знаку задержке импульсов на выходе делителя 5. Синтезатор по п. 2 ф-лы отличается выполнением блока 7, дана его ил. 1 з.п. ф-лы, 2 ил. 1В О 4ь ОЭ О сл оо

управляемой задержки 7 (на втором вхо- 35 сированной задержки и второй управляеде ИФД 2) расставлены во времени идеально равномерно на любой частоте рабочего диапазона.

Таким образом, это позволяет расширить диапазон выходных частот синтезатора частот при сохранении эффективного подавления помех дробности.

Формула изобретения

мый генератор пилообразного напряжения, выход которого соединен с управляющим входом второго управляемого генератора пилообразного напряжения,

0 информационный вход блока фиксированной задержки объединен с входом пуска первого управляемого генератора пилообразного напряжения и является первым входом блока управляемой задержки,

5 первый вход сумматора кодов является вторым входом блока управляемой задержки, второй вход сумматора кодов объединен с управляющим входом первого управляемого генератора пилообразного напряжения и является третьим входом блока управляемой задержки, тактовый вход блока фиксированной задержки является четвертым входом блока управляемой задержки.

0

Фиг. 1

Фи1.2

Редактор Н. Коляда

Составитель Ю. Ковалев

Техред Л.Олийнык Корректор Л. Натай

Заказ 1555

Тираж 463

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

11

10 К

Подписное

Авторы

Даты

1991-04-30—Публикация

1989-01-09—Подача