.енис .г к автоматике м вычислительной - хч1-/ е и fs --ет быть использовано в рээ w ых областях науки и техники, rrje зоз «икязг необходимость оп- оеделзния nsoar етпоз очспреаепения случайной Е,епчч« нн по мг, ым .

Целью мзойретенчя чвляетсг повышение точности оаботы строиства за счет про- вер си с г-Г -,тн еской гипотезы о сходимости теорети °счогс и экспериментального распре;: лэни на основе отношения правяопо ю5,.,

/.s jCTUjapHOLTb псггроенмя по выбороч- иыад данным -о;1,чг г / цествеино повысить, Hcno ib s сг «;д ющии подход. Исходны17 и геовзл рабтодечия А(а,-Ь) случайно 1 с лич уны (СВ) X разбмваетсяна rri диапазонов шир-iHO i и; zi - ги 0 Гй). По оезупьтата наблюдения случайной взл- ин -1 XL . ХР, .., XN (N - объем в. ) пссло/ атегьгЮ, начиная с п 1, строится аго ао орная глотнос ь fn i(x) EL боронного s ipp, эн „огпас -о спо peКХ. -)иг ОН J38Mt i vOr-1 V

У

Nf

гчч. н

SX.

-: г i(x/e,) 1(в).

(1)

onssS)

, .г1 1 O3f1 гпэоделче- мь г« ..о

,. - 13i

+ пу0U

i - -(а ал -ьое Зтччрниь весояпго ко- зг ine na (уо 0

р i(O-плотность выборочного pacnpt- доленмя Ј. (п - 1)-ог шаге

fh (х/ф)- условная плотность распределения выборочного значения хп в диагнозе наблюдения А гы, zi, определяется по формуле:

рп (x/Q)

-Ц

(3)

где I (х) - характеристическая функция отрезка Д , определяемая по формуле:

HI - гипотеза отвергается; еп - порог принятия решения, определяющий с учетом объема выборки, ошибки первого рода и теоретической вероятности Р| попадания СВ в интервал Д вычисляемой по формуле:

Pi

l fi.i(z)-fM-i(z)| .

Д,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ ФУНКЦИИ РАСПРЕДЕЛЕНИЯ СЛУЧАЙНЫХ ВЕЛИЧИН И ЕЕ ТОЛЕРАНТНЫХ ГРАНИЦ ПО МАЛЫМ ВЫБОРКАМ | 2014 |

|

RU2553120C1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для выполнения операций обращения матриц | 1985 |

|

SU1265796A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

Игпбиг енп 1 относится к аь Смэтике и вычислительной e/Hi/i e , быть v-c- пояьзоззио в обпаст°х науки и техники, где необходимость определения napavp- иоз распределения случайной вешнииы по га--нм выборкам Е1зобоетения является повышение точч, с-1 ча счет гфоверкн статист,i-еской p i о cxout iocTii теоретического и I crecvrc-.ia/.bHOfo распроделечий на ос- ноз с г«ою8ния правдоподобия. Устройство содсрЖ11 блоки входных регистров, KOMV, «-op, блок регистрации, синхронизо- юг,, оегистры. узлы когадутации, группу ре- пт рсе сдвига, узлы сравнения, блок ум14охенья, блок суммирования с константой Г О , уЗТЫ V НОУР Р Qj OK РЫЧ-1ТгНМ in -fOHCI n-U °nC v ЬНТОВ залоо «и i оуппн элемэк ов MTt I уз и дс- r.ensiq, блок согй- ч.1 группу С о- оь Bti- числе Ч -я ппст лсгч расп ецепРниг, вь Ч1ПЬЛИЯ -) К СЩУЛ /ЗЛЫ С/ММИp-t I блг с Еычит2М1Л ч ч стан ты /зел с л аи |/,Г

«Й|(Ю

1, ,Z|J

О, xn - 1 ,zi,

(4)

ln($) - индикатор случайного события, характеризующего результат n-ro испытания, определяемый по формуле:

In (fl)

1, xn e zi - 1 ,zi 0, xn - 1 ,zi,

(5)

В качестве начальной плотности распределения (nP)fo.i(x) при п 0 используется

равномерное распределение:

fo.i (х) Го

,хЈ(а,Ь) О, xf(a,b).

(6)

Вероятность попадания Fn,i (х) СВХ в интервал Д на n-м шаге определится по формуле:

Fn.i(x) fn.i(x) -4,1 1,m. (7)

На каждом шаге находятся значения теоретической ПР fn.iT(zi) в предположении, что она подчинена нормальному закону, как функции величин Fn.i (х) и середин интервалов разбиения zi, определяемых по формуле:

zl,ЈL±p.„

Для проверки статистической гипотезы о соответствии теоретического и выборочного распределения используется последовательный критерий, который реализуется с помощью следующего правила принятия гипотез при фиксированном объеме выборки п:

(Н0, если i - 1 I Јп (9) Hi, если I U -1 I еп , где MO - гипотеза о виде распределения принимается, и плотность fn,i(x) можно считать в качестве теоретической;

где fn,iT(z) и fn.i-iT(z) - теоретические значения ПР на n-м шаге в l-том и (1-1)-м сечениях соответственно (наличие разных аргументову выборочной и теоретической ПР объясняется тем, что аргументам теоретической ПР являются узловые точки на оси х zi, а у выборочной - случайный аргумент х);

Ln - отношение правдоподобия в узлах

сетки интервала наблюдения, которое находится по формуле:

,,fci

(11)

где fn,iT(z) - нормированная плотность теоретического распределения, определяемая по формуле:

30

fTn,,(z)(12)

Pi

I 1

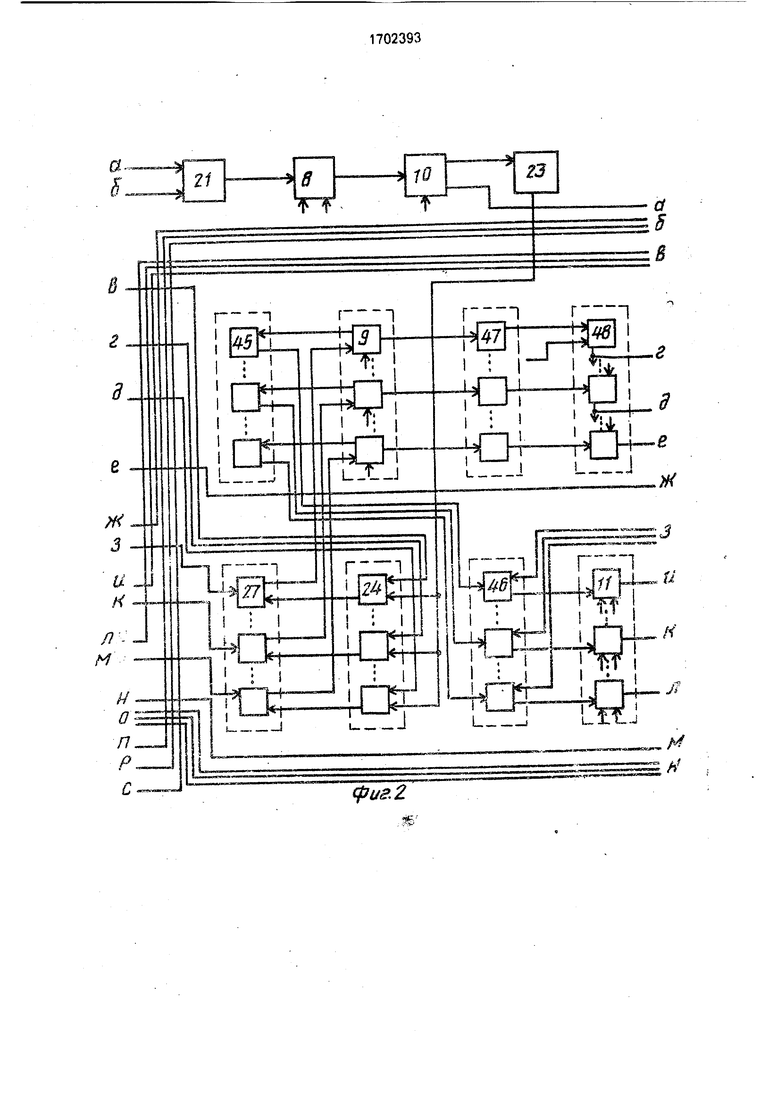

На фиг. 1 - 4 представлена структурная схема устройства для определения параметров распределения по малым выборкам.

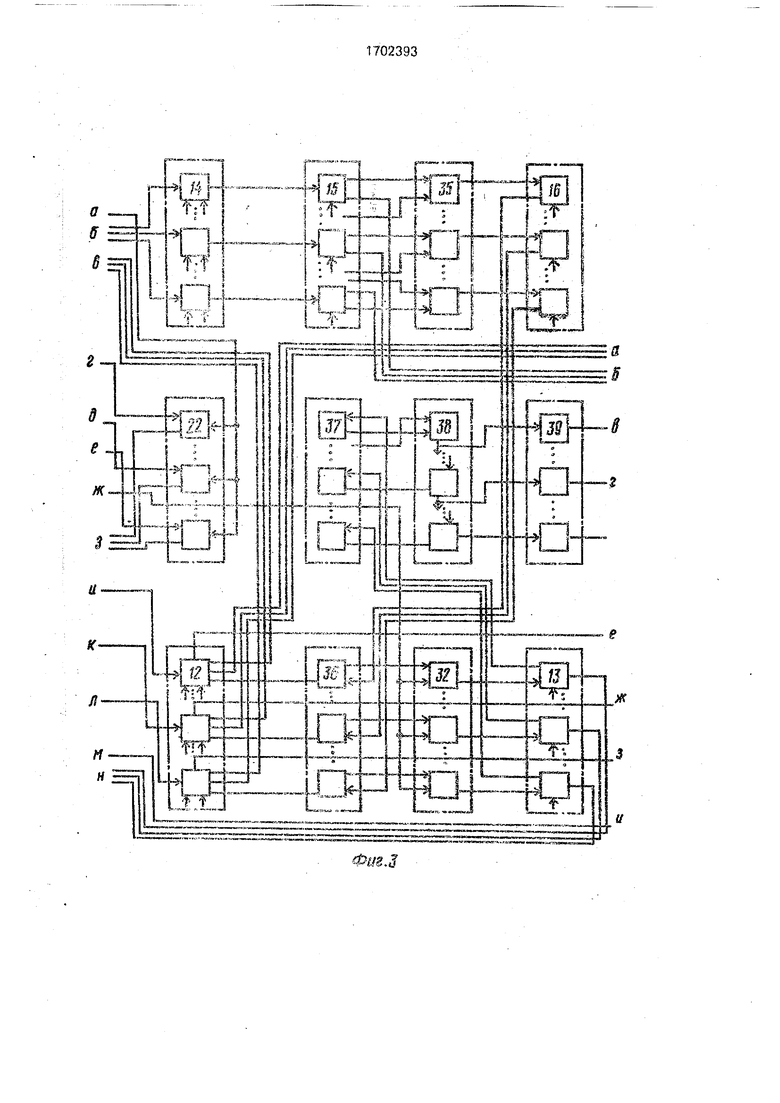

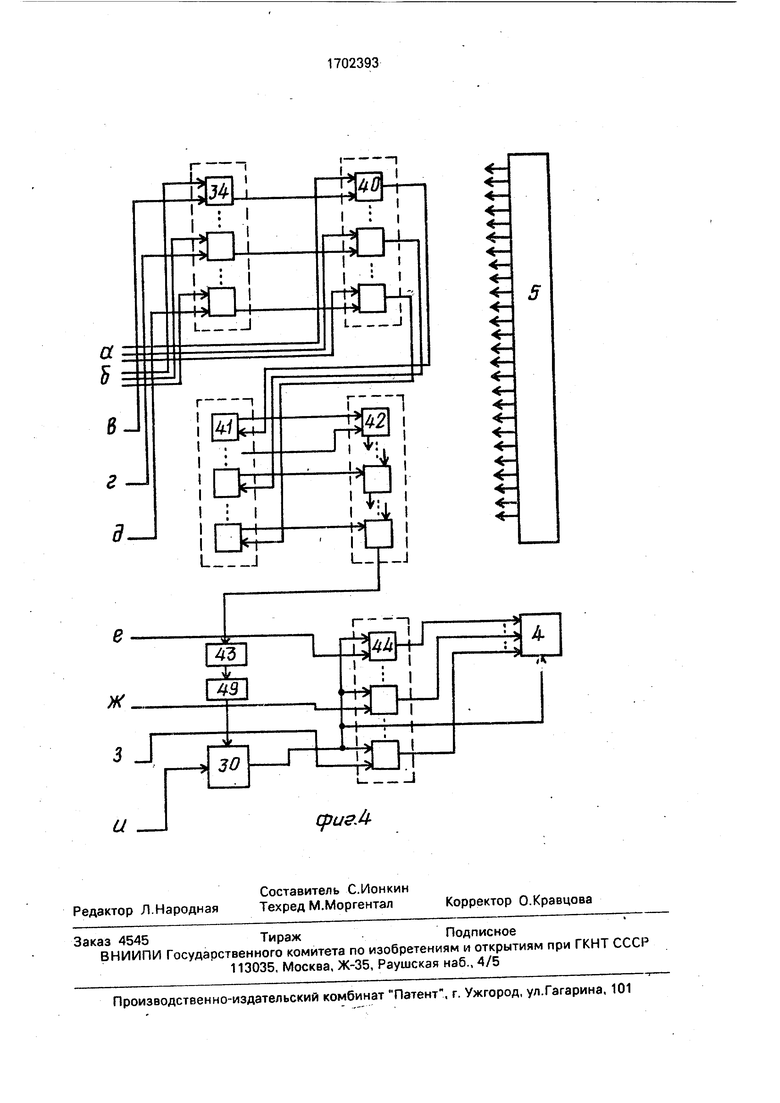

Устройство содержит блоки 1, 2 входных регистров, коммутатор 3, блок 4 регистрации, синхронизатор 5, блоки б, 7 входных регистров, регистр 8, узел 9 коммутации, коммутатор 10, группу 11 регистров, узлы 12, 13 коммутации, группу 14 регистров, узел 15 коммутации, группу 16 регистров

сдвига, узлы 17,18 сравнения, блок 19 умножения, блок 20 суммирования с константой, блок 21 деления, узел 22 умножения, блок 23 вычитания из константы, группу элементов ИЛИ 24, группу элементов 25 задержки,

узел 26 коммутации, узел 27 умножения, группу элементов ИЛИ 28, узел 29 деления, блок 30 сравнения, элемент 31 задержки, узел 32 умножения, группу блоков 33 вычисления плотности распределения, узел 34 деления, группу блоков 35 вычитания по модулю, группу элементов ИЛИ 36, группу элементов 37 задержки, узел 38 суммирования, группу элементов 39 задержки, узел 40 деления, группу элементов 41 задержки,

узел 42 умножения, блок 43 вычитания константы, узел 44 коммутации, группу элементов 45 задержки, узел 46 суммирования, группу элементов 47 задержки, узел 48 суммирования, блок 49 вычисления модуля.

Устройство работает следующим образом.

Через первый информационный вход в блок 1 памяти записываются текущее значение объекта выборки (в начале п 1), первое значение случайной величины XL Поскольку эта информация поступает одновременно блок 1 имеет один управляющий вход. Через информационные входы второго блока 2 одновременно записываются значения узловых точек zi, через информационные входы блока 6 памяти - значения середин интервалов zi. Через информационные входы блока 7 входных регистров записываются: величина Д ширины диапазона; величина уь начального значения весового коэффициента; значение f0 начальной ПР; величина Еп порога принятия решений. Сигналы на запись подключаются на управляющие входы с выходов синхронизатора 5.

С выхода синхронизатора 5 подается управляющий сигнал на установочный вход блоков 33 вычисления плотности распределения группы.

По сигналу с выхода синхронизатора 5 сигнал, соответствующий первому значению случайной величины х,, поступает с первого аыхода блока 1 на первые входы узлов 17 и 18 сравнения. Со второго выхода блока сигнал, соответствующий величине п, подается на первый вход узла 19 умножения.

По сигналу с выхода синхронизатора 5 сигналы, соответствующие величинам zi, с выходов блока 2 поступают на вторые входы (левые границы диапазонов и правые границы диапазонов) узлов 17 и 18 сравнения. По сигналу с выхода синхронизатора 5 с выхода блока 7 входных регистров сигнал, соответствующий величине у0, подается на второй вход блока 19 умножения и на вход элемента 31 задержки. С выхода произведения блока 19 сигнал, соответствующий величине пуо , поступает на вход блока 20, с выхода суммы которого сигнал, соответствующий величине 1 + пу0 , подается на вход делимого блока 21 деления. На вход делителя блока 21 с выхода элемента 31 задержки поступает сигнал, соответствующий величине уо. Таким образом, с выхода частного блока 21 сигнал, соответствующий величине ) п, определяемый по формуле (2), подается на информационный вход регистра 8. Управляющий сигнал на запись подается при этом с выхода синхронизатора 5.

Узел сравнения 17 построен следующим образом: если хп ZM, то на их выходах появляется 1; в случае когда xn ZI-L на его выходах будет 0. Узел сравнения 18 нзстроен следующим образом: если xn zi, то на его выходах появится 1; в случае, когда xn zi, на его выходах будет 0. Такая настройка обеспечивает оценку величин 1д( (х) и in( $) по формулам соотретственно (4)

и (5).

В дальнейшем осуществляется вычисление величины fn,i(x) по формуле (1). В данной ситуации используются следующие блоки: регистр 8, синхронизатор 5, блок 23

вычитания из константы, коммутаторы 3 и 10, блоки элементов ИЛИ 24 и 28 групп, узлы 22 и 27 умножения, узлы коммутации 9, элементы задержки 25, 45 и 47 групп, узлы 46 суммирования, узел коммутации 26, узел деления 29, Сигналы, соответствующие величинам fn,i(x), поступают на информационные входы регистров 11 группы. Управляющие сигналы на запись подаются при этом с выхода синхронизатора 5.

По сигналу с выхода синхронизатора 5 на вход считывания регистров 11 группы с выходов этих регистров сигналы, соответствующие величинам fn,i(x), через узел 12 коммутации и группу элементов ИЛИ 36 поступают на входы узла умножения 32. На другие выходы этого узла по сигналу с да синхронизатора на вход считывания блока 7 входных регистров через коммутатор 3 подается сигнал, соответствующий величине Д .

С выхода произведения узпг 32 умножения сигналч, соответствующие величинам Fn.i(x)- определяемые по формуле (7), через узел 13 (управляющие сигналы на их входы

подаются с выхода шнхр .низатора 5) поступают на входы блоков 33 вычисления плотности распределения. На другие входы блоков 33 с выходов блока 6 по сигналу с выхода синхронизатора 5 подаются сигнзлы, .соответствующие величинам zi. Начало работы блоков 33 осуществляется по сигналу с выхода синхрониззюра 5. С выходов блоков 33 сигналы, соответствующие величинам теоретической ПР fn,r(x), поступают

на информационные входы регистроо 14 группы, управляющие сигналы при этом подаются на вход Записи этих регистров с выхода синхронизатора 5.

Далее по формуле (1) с использованием формул (10) и (12) осуществляется .вычисление отношения правдоподобия Ln. Здесь используются Следующие блоки: регистры 11 и 14 групп, узлы деления 34 и 40, узлы коммутации 12, 13 и 15, группа 35 блоков

вычитания по модулю, группа 16 регистров сдвига, блок 7 входных регистров, синхронизатор 5, блоки элементов ПЛИ 36, узлы умножения 32 и 42, коммутатор 3, элементы задержки 37, 39 и 41 групп, узел 38 суммирования.

С последнего выхода произведения узла 42 умножения сигнал, соответствующий величине Ln, поступает на ахол блока 43 вычитания из константы и затем - на вход блока 49, с выхода которого сигнал, соответствующий величине U - 1 I , подается на второй вход блока 30 сравнения, на первый вход которого по сигналу с выхода синхронизатора 5 с выхода блока 7 входных регистров поступает сигнал, соответствующий величине е,п - порогу принятия решения.

С помощью блока 30 сравнения осуществляется проверка статистической гипотезы в соответствии с формулой (9), и поэтому он построен следующим образом: если I Ln -1 I Јn, to на выходе блока 30 проявится сигнал; в случае, когда I Ln - 1 I Јn, на выходе блока 30 сигнала не будет. При наличии сигнала, т. е, при подтверждения гипотезы Н, открывается для пропуска информации узел 44 коммутации и готовится к записи выходной информации блок 4 регистрации, В данной ситуации с выхода регистров 11 группы через узлы коммутации 12 и 44 сигналы, соответствующие величинам fn,i{x), поступают на информационные входы блока 4 регистрации, и они принимаются в качестве теоретической плотности распределения,

При отсутствии сигнала на выходе блока 30 сравнения, что соответствует о подтверждении гипотезы Hi, узлы коммутации будут закрыты, информация на блок 4 регистрации не пройдет и начнется цикл работы устройства, Все последующие циклы работы устройства происходят аналогично первому циклу. Единственное отличие заключается в том, что при определении величины fn,i(x) по формуле (1) на вторые информационные входы группы узлов умножения 27 подаются через элементы ИЛИ 28 второй группы на значения for а величины fn-i,i(x), т. е. значения fn,i(x) предыдущего .цикла с выходов регистров 11 группы через узел 12 коммутации.

Формула изобретения

Устройство для определения параметров распределения по малым выборкам, содержащее три блока входных регистров, блок умножения, блок суммирования с константой, элементы задержки, блок деления, регистр, два коммутатора, блок вычитания из константы, блок чычитания константы,

блок сравнения, блок регистрации, первый узел сравнения, первую группу элементов задержки, шесть узлов коммутации, три узла суммирования, дае группы регистров,

группу регистров сдвига, два узла деления, четыре узла умножения, три группы блоков элементов ИЛИ и синхронизатор, первый выход которого соединен с входом синхронизации первого блока входных регистров,

первая и вторая группы информационны входов которого являются соответственно входом задания объема выборки и информационным входом устройства, первый выход первого блока входных регистров подключен к первому входу блока умножения, выход которого через блок суммирования с константой соединен с входом делимого блока деления, вход делителя которого подключен к выходу элемента задержки, второй

и третий выходы синхронизатора соединены соответственно с входами записи и счи- тывания регистра, выход которого подключен к информационному входу первого коммутатора, управляющий вход кото,рого соединен с четвертым выходом синхронизатора, а первая группа выходов первого коммутатора подключена к первой группе входов первого узла умножения, выходы которого соединены с первой группой

входоа первого узла суммирования, выходы которого подключены к информационным входам регистров первой группы, входы записи и считывания которых подключены соответственно к пятому и шестому выходам

синхронизатора, выходы регистров первой группы подключены к информационным входам первого узла коммутации, первый и второй управляющие входы которого соединены соответственно с седьмым и восьмым

выходами синхронизатора, а первая группа выходов подключена к информационным входам второго узла коммутации, выходы которого соединены с информационными входами блока регистрации, вторая группа

выходов первого узла коммутации подключена соответственно к первым входам блоков элементов ИЛИ первой группы, выходы которых соединены с первой группой входов второго узла умножения, вторая группа

входов которого подключена соответственно к выходам блоков элементов ИЛИ второй группы, девятый выход синхронизатора соединен с входом синхронизации второго блока входных регистров, информационные

входы которого являются входами задания координат интервалов, второй выход первого блока входных регистров соединен с первым входом первого узла сравнения, девятый выход синхронизатора подключен к управляющему входу второго коммутатора, первый выход которого соединен с первым входом третьего узла умножения, второй вход которого,подключен соответственно к выходу блоков элементов ИЛИ третьей группы, первые входы которых соединены с третьей группой выходов первого узла коммутации, одиннадцатый выход синхронизатора подключен к входу синхронизации третьего блока входных регистров, информационные входы которого являются входами задания середин интервалов разбиения, двенадцатый и тринадцатый выходы синхронизатора соединены соответственно с входами записи и считывания регистров второй группы, выходы которых подключены к информационным входам третьего узла коммутации, первая группа выходов которого соединена с входами делимого первого узла деления, выходы четвертого узла коммутации подключены к входам делимого второго узла деления, выход Меньше или равно блока сравнения подключен к управляющим входам второго узла коммутации и входу синхронизации блока регистрации, отличающееся тем, что, с целью повышения точности, в него введены второй узел сравнения, пять групп элементов задержки, третий узел деления, группа блоков аычитания по модулю, группа блоков вычисления плотности распределения, блок вычисления модуля и четвертый бло входных регистров, групп и входов записи и считывания которого подключены соответственно к первой и второй группам выходов синхронизатора, первый выход четвертого блока входных регистров соединен с информационным входом второго коммутатора, второй выход которого соединен с входами делителя второго узла деления, выходы которого подключены соответственно к первым входам блоков элементов ИЛИ первой группы, вторые входы которых соединены с вторым выходом четвертого блока входных регистров, третий выход которого подключен к второму входу блока умножения и входу элемента задержки, четвертый выход четвертого блока входных регистров подключен к первому входу блока сравнения, второй вход которого соединен с выходом блоха вычисления модуля, вход которого подключен к выходу блока вычитания константы, вход которого соединен с выходом четвертого узла умножения, группа выходов которого подключена соответственно к выходам элементов задержки первой группы, входы которых соединены с выходами третьего узла деления, входы делимого которого подключены к четвертой группе выходов первого узла коммутации, первый выход второго блока входных регистров соединен с вторым входом первого узла сравнения, выходы Больше которого подключены к информационным

входам «етвертого узла коммутации, управляющие входы которого соединены с выходами Меньше или равно второго узла сравнения, первый вход которого подключен к второму выходу первого блока вход0 ных регистров, а второй вход соединен с вторым выходом второго блока входных регистров, выходы четвертого узла коммутации через одноименные элементы задержки второй группы подключены к первым вхо5 дам блоков элементов ИЛИ второй группы, вторые входы которых соединены с выходом блока вычитания из константы, входы которого подключены к второй группе выходов первого коммутатора, выход блока деления

0 соединен с информационным входом регистра, четырнадцатый выход синхронизатора подключен к управляющему входу пятого узла коммутации, информационные входы которого соединены с выходами второго уз5 ла умножения, первая группа выходов пятого узла коммутации через соответствующие элементы задержки третьей группы соединена ее второй группой входов первого узла суммирования, вторая группа выходов пято0 го узла коммутации через соответствующие элементы задержки чсгрертой группы подключено к группе входов второго узла суммирования, выходы КОТОРОГО соединены с второй группой входов первого узла умно5 женмя, вторая группа выходов третьего узла коммутации соединена с входами уменьшаемого блоков вычитания по модулю группы, входы вычитаемого которых подключены к третьей группе выходов третьего узла ком0 мутации, а выходы соединены с информационными входами регистров сдвига группы, входы упоавления сдвигом которых подключены к пятнадцатому выходу синхронизатора, а выходы соединены соответст5 венчо с вторыми аходами блоков элементов ПАИ третьей группу, шестнадцатый и семнадцатый выходы синхронизатора подключены соответственно к управляющим входам третьего и шестого узлов коммута0 цни, информационные входы которого сое- динены с выходами третьего узла умножения, а первая группа выходов подключена к информационным входам блока вычисления плотности распределения

5 группы, входы синхронизации которых соединены с восемнадцатым выходом синхронизатора, а выходы подключены к информационным входам одноименных регистров группы, вторая группа выходов шестого узла коммутации через

соответствующие элементы задержки пятой группы подключена к группе входов третьего узла суммирования, выходы которого через соответствующие элементы задержки

шестой группы соединены с ёходами де/ш- 5 лов разбиения блоков вычисления плотнотеля первого узла деления, выходы которого

подключены соответственно к входам делителя третьего узла деления, выходы третьего блока входных регистров подключены к входам задания значений середин интервасти распределения группы.

а

5

Фиг.1

т

ОТ CN О

r«3

«sa

«S3

QJ

i

t

t; Ct.

И

.3

Авторы

Даты

1991-12-30—Публикация

1989-12-25—Подача