13

Изобретение относится к вычисши- тельной технике и предназначено для использования в арифметических устройствах с плавающей запятой, функционирующих в модулярной системе счис- ления.

Цель изобретения - повьшение быстродействия.

На фиг. 1 приведена структурная схема устройства для нормализации чисел в модулярной системе счисления; на фиг. 2 - структура блока хранения констант; на фиг. 3 - структура блока анализа интервального ин- декса.

Устройство для нормализации в модулярной системе счисления (фиг. содержит тактовый вход 1 устройства, информационный вход 2 устройства, блоки 3.1-З.п хранения констант, элемент 4 задержки, блоки 5о1-5.п с ум- мирования вычетов, блок 6 модульного умножения, блоки 7,1-7.п анализа интервального индекса, вспомогатель- иый регистр 8, элементы И 9.1-9.П-1, шифратор 10, выход 11 мантиссы устройства, выход 12 порядка устройства

k-1- + log,,, М., П т.,

где n,-m - основания модулярной системы счисления, являющиеся попарно-взаимно простыми числами, причем , 2p+k-2;

р - фиксированное натуральное

число; S - множитель нормализации,

равный т,.

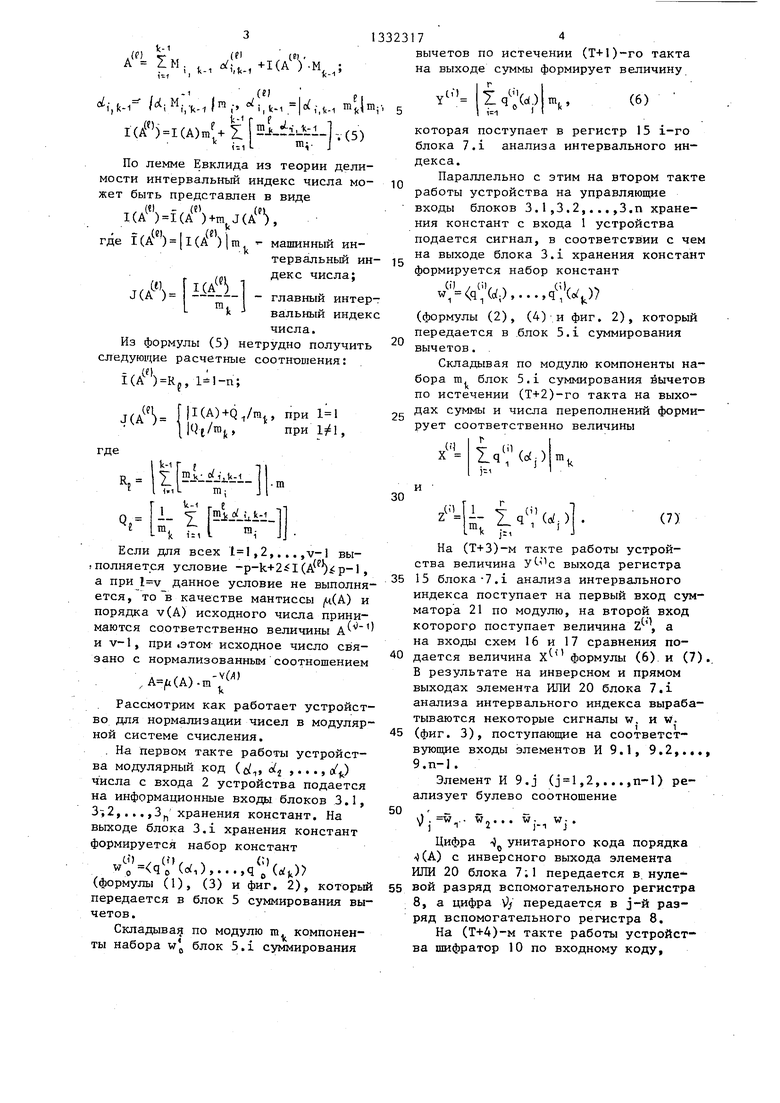

Первьй блок хранения констант (фиг. 2) содержит узлы .k памяти и группы мультиплексоров 14.1- 14.k.

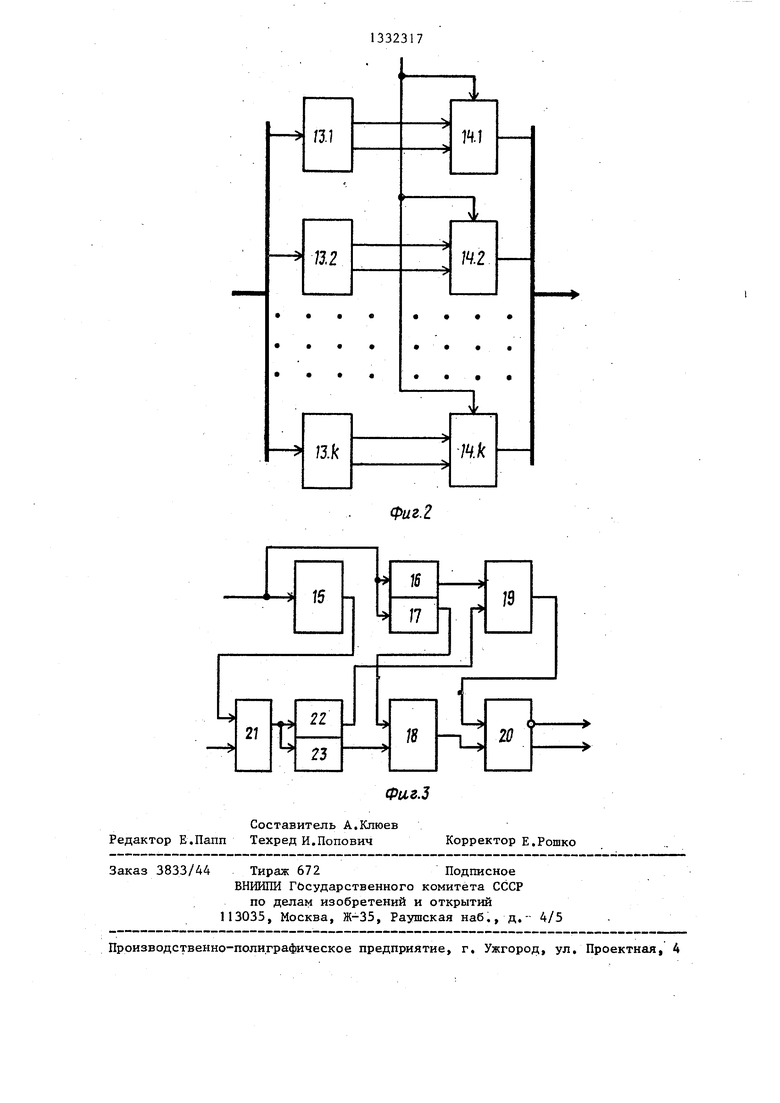

Блок анализа интервального индек- са (фиг. 3) содержит регистр 15, первую и вторую схемы 16 и 17 сравнения с константой, первый и второй элементы И 18 и 19, элемент ИЛИ 20, сумматор 21 по модулю, схему 22 сравне- ния с нулем и третью схему 23 срав- нения с константой. Схемы 16 и 17 сравнения с константой могут быть реализованы с помощью постоянного запоминающего устройства. Сумматор 21 по модулю т, и схемы 22 и 23 сравнения также могут быть реализованы с помощью постоянного запоминающего устройства.

17

Б узел 13.j памяти () первого блока 3.1 хранения констант по адресу Х- О,1,...,т записывается пара констант, компоненты которой определяются соотношениями

q : (Xj).

iibL.MiAllPi | .(п

L.т,. Л-к

01

П}1 2 J J LiBi 1 q; . ли

О, если

f

где Mj-f Mf/mj , M П m (j l ,2,... , k-1,.. , k) -Блоки 3.2, 3.3,...,3.n хранения констант структурно аналогичны первому блоку 3.1 хранения констант, , при этом i-й блок 3.1 хранения констант (,3,...,п) выполнен на основе k-1 узлов памяти и k-1 групп мультиплексоров, причем в узел 13.J памяти записывается пара констант, компоненты которой определяются соотношениями

(3)

(4)

Элемент 4 задержки представляет собой цепочку из Т+4 регистров (Т Jlogjk).

Блоки 5.1, 5.2,...,5.п суммирования вычетов имеют Т-каскадную конвейерную структуру.

Схемы 16 и 17 сравнения с константой формируют по входной величине X единичные значения соответственно, ели , р-1 и Xe m -p+k-2, .

Схема 23 сравнения с константой выполняет сравнение с величиной .

На инверсном и прямом выходах элемента ИЛИ 20 формируются соответственно признаки W. и W., являющиеся .выходными значениями блока 7.1 анализа интервального индекса.

Работа устройства для нормализации чиседт: в модулярной системе счи- сления базируется: на следующем.

Пусть число AeD, заданное своим модулярным кодом ( oi,,. . ., о() является числом, подлежащим нормализации. Используя интервально-модулярное представление числа можно записать:

Jf)

k-1

(fl

. 4 .-. 41, .М,;

,(г)

i,k-i MiMi,vil ,,k-i. (/ )I(A),(5)

По лемме Евклида из теории делимости интервальный индекс числа мо- жет быть представлен в виде

I(/ )i(r).(), где I (А ) I (А ) 1 m машинный ин k

тервальный ин- деке числа;

Г (

J(A ) - главный интерL k вальный индекс

числа.

Из формулы (5) нетрудно получить следующие расчетные соотновшния: .(1.

I(A )Rp,

J() (il(A)QiS. при iQt/m, при ,

где

vllH-t - |..

Q fl У fn}i «Lui-j l Н, t,i -, JJ.

Если для всех ,2,...,v-l вы- полняется условие -p-k+2 I(A , а при данное условие не выполняется, то в качестве мантиссы |М.(А) и порядка v(A) исходного числа принимаются соответственно величины и V-1, при .этом исходное число связано с нормализованным соотношением

А , АЧ -( (A)-m

Рассмотрим как работает устройство для нормализации чисел в модулярной системе счисления,

. На первом такте работы устройства модулярный код (й, ,.. ., (/) числа с входа 2 устройства подается на информационные входы блоков 3.1, ,... ,3j хранения констант. На выходе блока 3.1 хранения констант формируется набор констант

,...,(fc)

(формулы (1), (3) и фиг. 2), который передается в блок 5 суммирования вычетов.

Складывая по модулю га. компоненты набора w p блок 5.1 суммирования

3323174

вычетов по истечении (Т+1)-го такта на выходе суммы формирует величину

г

5

ю

- 15

с

25

Т .)

m,

(6)

- 1

которая поступает в регистр 15 i-ro блока 7.1 анализа интервального индекса.

Параллельно с этим на втором такте работы устройства на управляющие входы блоков 3.1,3.2,...,3.п хранения констант с входа 1 устройства подается сигнал, в соответствии с чем на выходе блока 3.i хранения констант формируется набор констант

СП / (il/ , (i)x , чч

w q(o(;),...,q,U))

(формулы (2), (4) и фиг. 2), который передается в блок 5.1 суммирования вычетов.

Складывая по модулю компоненты набора т, блок 5.1 суммирования вычетов по истечении (Т+2)-го такта на выходах суммы и числа переполнений формирует соответственно величины г

(il . . ,1

.т,

х

iq ; (.,)

30

и

ч-:: ,

(7):

5

На (Т+3)-м такте работы устройства величина У - c выхода регистра 15 блока-7.1 анализа интервального индекса поступает на первый вход сумматора 21 по модулю, на второй вход которого поступает величина Z , а на входы схем 16 и 17 сравнения по- 0 дается величина формулы (6). и (7).. В результате на инверсном и прямом выходах элемента ИЛИ 20 блока 7.1 анализа интервального индекса вырабатываются некоторые сигналы w, и w. (фиг. 3), поступающие на соответствующие входы элементов И 9.1, 9.2,.,., 9.П-1.

Элемент И 9.J (,2,...,п-1) реализует булево соотношение

W- J

) 2Цифра - унитарного кода порядка -(А) с инверсного выхода элемента ИЛИ 20 блока 7;1 передается в, нулевой разряд вспомогательного регистра 8, а цифра У передается в j-й разряд вспомогательного регистра 8.

На (Т+4)-м такте работы устройства шифратор 10 по входному коду.

поступающему с выхода вспомогательного регистра 8, получает двоичный код порядка л) (А) , который передается па выход 12 порядка устройства, ,На заключительном (Т+5)-м такте работы устройства порядок и модулярный код исходного числа -подаются соответственно на второй и первый входы блока 6 модульного умножения, на выходе которого формируется модулярный код мантиссы |U(A). Мантисса снимается с выхода 1 мантиссы устройства и на этом операция нормализации числа заканчивается.

Формула изобретения

Устройство для нормализации чисел в модулярной системе счисления, содержсицее первый блок хранения констант,, первый блок суммирования вычетов, первый блок анализа интервального индекса, элемент задержки, блок модульного умножения и вспомогательный регистр, причем выход первого блока хранения констант подключен к входу первого блока суммирования вычетов, отличающееся тем, что, с целью повьшения быстродействия , оно содержит (п-1) блоков хранения констант, (п-1) блоков суммирования вычетов, (п-) блоков анализа интервального индекса, (п-1) элемент И и шифратор, причем блок анализа интервального индекса содержит регистр, три схемы сравнения с константой, схему сравнения с нулем, суматор по модулю, два элемента И и- элемент ИЛИ, при этом информационный вход устройства соединен с адресными входами блоков хранения констант с первого по -й и с входом элемента задержки, выход которого соединен с входом первого сомножителя блока модульного умножения, вход второго сомножителя которого подключен к вы

10

15

20

332317

ходу шифратора и является выходом порядка устройства, тактовьм вход которого соединен с входами разрешения выбора блоков храпения констант с первого по п-й, выходы которых,кроме первого, соединены с входами соответствующих блоков суммирования вычетов , выхода суммы и числа переполнений блоков суммирования вычетов с первого по п-й соединены соответственно с входом регистра и с входом первого слагаемого сумматора по модулю составляющего блока анализа интервального индекса i-й и (з+1)-й входы j-ro элемента И, где (n-l), i l-j, соединены соответственно с- прямым выходом элемента ИЛИ i-ro блока анализа интервального индекса и с инверсным выходом элемента ИЛИ (j+ +1)-го блока анализа интервального индекса инверсный выход элемента ИЛИ первого блока анализа интервального индекса и выходы элементов И с первого по (п-1)-й соединены соответственно с входами разрядов вспомогательного регистра, выход которого соединен с входом шифратора, выход блока модульного умножения является выходом мантиссы устройства, причем в блоке анализа интервального индекса вход регистра соединен с входами первой и второй схем сравнения с константой, выходы второй и первой схем сравнения с константой соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход регистра соединен с входом второго слагаемЬго сумматора по модулю, выход которого соединен с входом

25

30

35

40

45

третьей cxeMia сравнения с нулем, выходы которых соединены соответственно с вторыми входами первого и второго элементов И.

Редактор Е.Папп

Составитель А.Клюев Техред И.Попович

Заказ 3833/44 Тираж 672Подписное

ВНИРШИ ГЬсударственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.- 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

сриг.2

Фи,г.З

Корректор Е.Рошко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нормализации чисел в модулярном коде | 1984 |

|

SU1242942A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для нормализации числа в интервально-модулярном коде | 1984 |

|

SU1275439A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

Изобретение относится к вычислительной технике и может быть.использовано в арифметических устройствах с плавающей запятой, функционирующих в модулярной системе счисления. Цель изобретения - повьппение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит блоки 3.1-З.п хранения констант, блоки 5.1-З.п суммирования вычетов, элемент 4 задержки, блок 6 модульного умножения, блоки 7.1-7.П анализа интервального индекса и вспомогательный регистр 8, элементы И 9.1-9.П-1 и шифратор 10 с соответствующими связями, причем блок анализа интервального индекса содержит регистр, схемы сравнения с константой, элементы И, элемент ИЛИ, сумматор по модулю и схему сравнения с нулем с соответствующими связями. 3 ил. . (Л С

Авторы

Даты

1987-08-23—Публикация

1986-03-17—Подача