1

Изобретение относится к вычисли- ;тельной технике и предназначено для использования в арифметических уст ройствах с плавающей запятой, функционирующих в модулярной системе счисления.

Целью изобретения является расширение области применения путем обеспечения возможности умножения чисел в модулярной системе счисления в режиме с плавающей запятой.

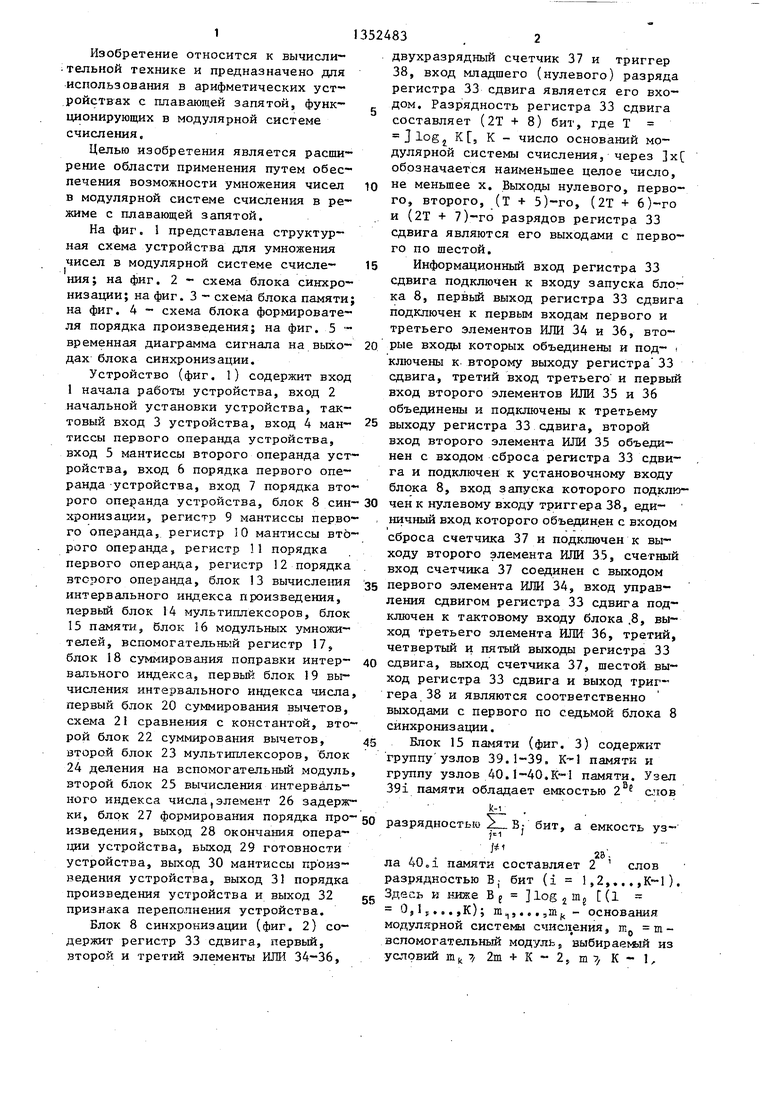

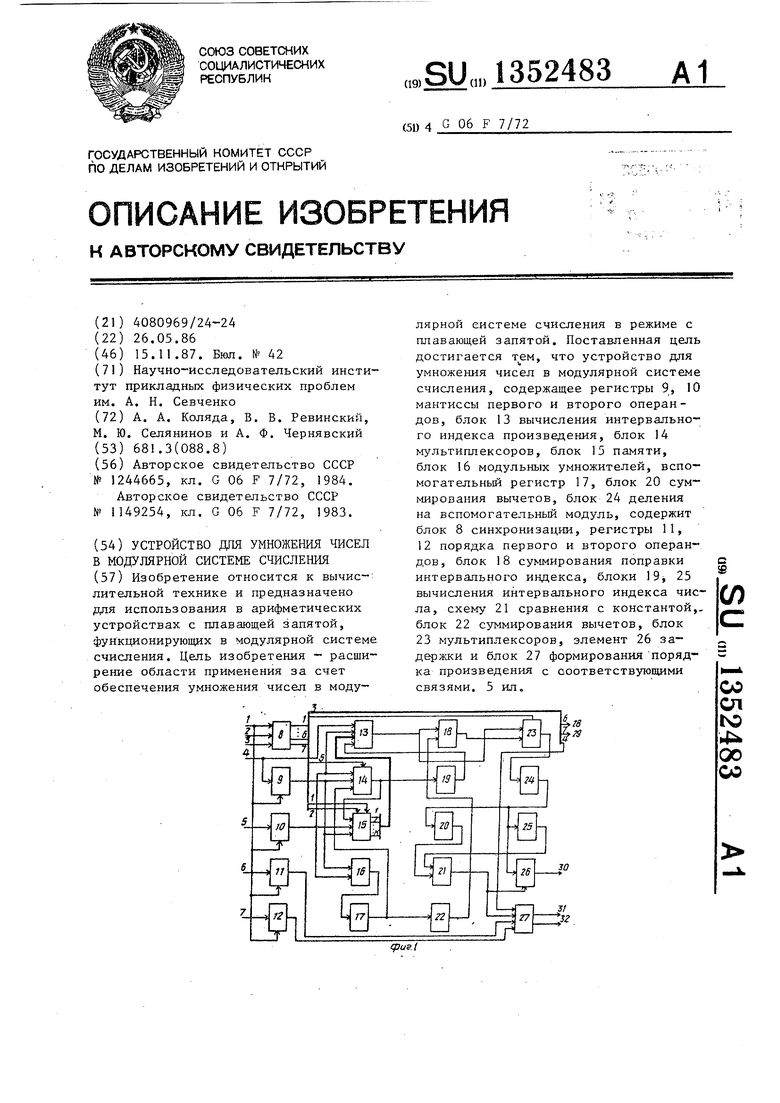

На фиг, 1 представлена структурная схема устройства для умножения

чисел в модулярной системе счисления ; на фиг, 2 - схема блока синхронизации; на фиг, 3 - схема блока памяти; на фиг, 4 - схема блока формирователя порядка произведения; на фиг, 5 - временная диаграмма сигнала на выходах блока синхронизации.

Устройство (фиг, 1) содержит вход 1 начала работы устройства, вход 2 начальной установки устройства, тактовый вход 3 устройства, вход 4 мантиссы первого операнда устройства, вход 5 мантиссы второго операнда устройства, вход 6 порядка первого операнда устройства, вход 7 порядка вто15 Информационный вход регистра 33 сдвига подключен к входу запуска бл ка 8, первый выход регистра 33 сдви подключен к первым входам первого и третьего элементов ИЛИ 34 и 36, вто

20 рые входы которых объединены и подключены к второму выходу регистра 3 сдвига, третий вход третьего и перв вход второго элементов ИЛИ 35 и 36 объединены и подключены к третьему

25 выходу регистра 33 сдвига, второй вход второго элемента ИЛИ 35 объеди нен с входом сброса регистра 33 сдв га и подключен к установочному вход блока 8, вход запуска которого подк

рого операнда устройства, блок 8 син-30 чен к нулевому входу тр1иггера 38, едихронизации, регистр 9 мантиссы первого операнда, регистр 10 мантиссы второго операнда, регистр 11 порядка первого операдца, регистр 12 порядка второго операнда, блок 13 вычисле1шя интервального индекса произведения, первый блок 14 мультиплексоров, блок 15 памяти, блок 16 модульных умножителей, вспомогательньзй регистр 17, блок 18 суммирования поправки интервального индекса, первый блок 19 вычисления интервального индекса числа, первый блок 20 суммирования вычетов, схема 21 сравнения с константой, второй блок 22 суммирования вычетов, второй блок 23 мультиплексоров, блок 24 деления на вспомогательный модуль, второй блок 25 вычисления интервального индекса

числа элемент

26 задержки, блок 27 формирования порядка про- изведения, выход 28 окончания опера- и;ии устройства, выход 29 готовности устройства, выход 30 мантиссы произведения устройства, выход 31 порядка произведения устройства и выход 32 признака переполнения устройства.

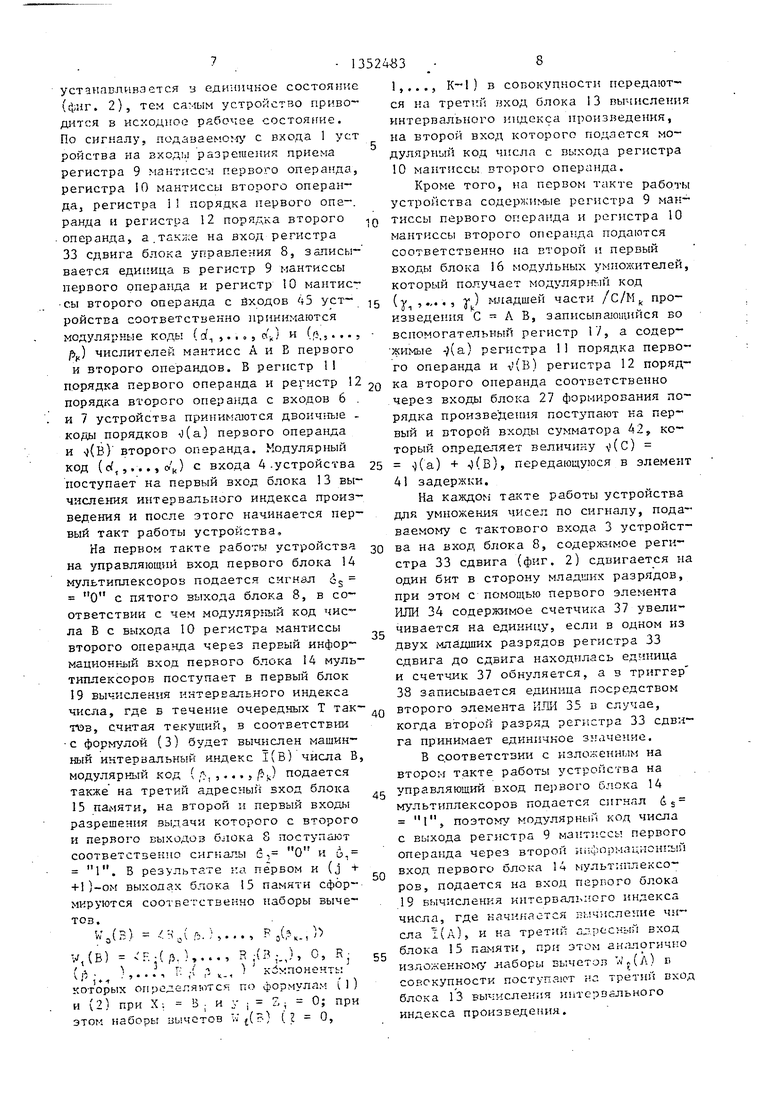

Блок 8 синхронизации (фиг, 2) содержит регистр 33 сдвига, первый, второй и третий элементы ШП 34-36,

двухразрядньй счетчик 37 и триггер 38, вход младшего (нулевого) разряда регистра 33 сдвига является его вхо- дом. Разрядность регистра 33 сдвига составляет (2Т + 8) бит, где Т Jlogj К, К - число оснований модулярной системы счисления, через х обозначается наименьшее целое число,

не меньшее х. Выходы нулевого, первого, второго, (т + 5)-го, (2Т + 6)-го и (2Т + 7)-го разрядов регистра 33 сдвига являются его выходами с первого по шестой,

Информационный вход регистра 33 сдвига подключен к входу запуска блока 8, первый выход регистра 33 сдвига подключен к первым входам первого и третьего элементов ИЛИ 34 и 36, вторые входы которых объединены и под . ключены к второму выходу регистра 33 сдвига, третий вход третьего и первый вход второго элементов ИЛИ 35 и 36 объединены и подключены к третьему

выходу регистра 33 сдвига, второй вход второго элемента ИЛИ 35 объединен с входом сброса регистра 33 сдвига и подключен к установочному входу блока 8, вход запуска которого подклю-

ничный вход которого объединен с входом сброса счетчика 37 и подключен к выходу второго элемента ИЛИ 35, счетный вход счетчика 37 соединен с выходом

первого элемента ИДИ 34, вход управления сдвигом регистра 33 сдвига подключен к тактовому входу блока .8, выход третьего элемента ИЛИ 36, третий, четвертый и пятый выходы регистра 33

сдвига, выход счетчика 37, шестой выход регистра 33 сдвига и выход триггера 38 и являются соответственно выходами с первого по седьмой блока 8 синхронизации,

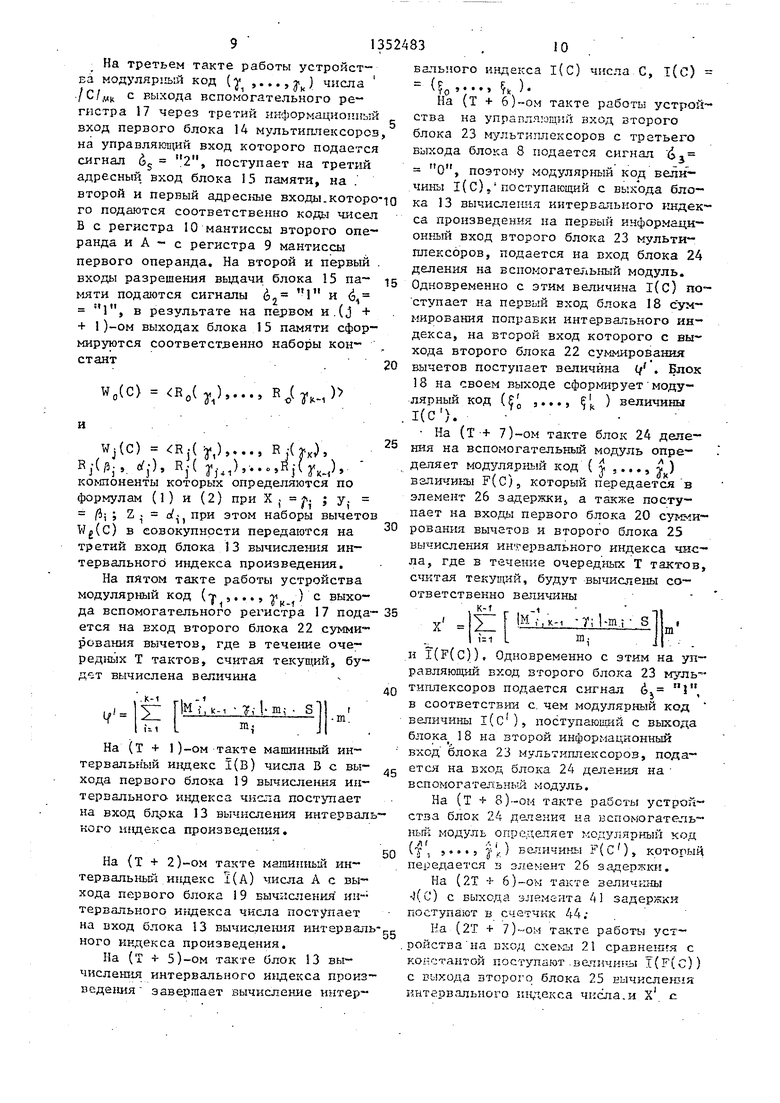

Клок 15 памяти (фиг, 3) содержит группу узлов 39,1-39. К-1 памяти и группу узлов 40,1-40.К-1 памяти. Узел 39i памяти обладает емкостью 2 спов

k-1

разрядностью

1Ф

Sf

бит, а емкость уз-

28.

ла 40«1 памяти составляет 2 слов разрядностью В; бит (i 1,2,,,.,), Здесь и ниже В j Jlog nig (1 0,lj.,,,K); m,.,,5mj, - основания модулярной системы счисиения, т т- вспомогательный модуль, выбираемый из условий m|j7/ 2т - К 2f m7/ К- 1,

В ячейку 39.1 памяти с адресом х. записывается набор констант Е„(Х.),..,,R..(Xj,

R;,(X.),...,R,.,(X,)

VIM ; к... X;lm

где Е(Х()

Ш;

m

,-iJ R,-(y,, Z.)

М ;,к-. }м/., . У; |пц-|м ; хм Z-,m;

т.

X, У, , Z ,. е 0,1,.,.,т ;., J

через х обозначается целая часть

действительного числа х.

Адресные входы узлов 39.1, 39.2,...,39.К-1 памяти в совокупности составляют третий адресный вход блока 15 памяти, первые адресные входы узлов 40.1, 40.2,...,40К-1 памяти в совокупности составляют второй адрес- Ньш вход блока 15 памяти, а их вторые адресные входы в совокупности составляют первый адресньй вход блока 15 памяти,выходы узлов 39,1, 39.2,..., 39.К-1 и 40.1, 40.2,.,.,40.К-1 памяти, соответствующие выходным вычетам наборов по модулю га. объединяются и в совокупности составляют выход блока 15 памяти. Управляющие входы выдачи кода узлов 40.1, 40.2,...,40.К-1 памяти объединены и подключены к второму входу разрешения выдачи блока 15 памяти, а управляющие входы выдачи кода узлов 39.1, 39.2,...,39.К-1 памяти объединены и подключены к первому входу разрешения выдачи блока 15 памяти.

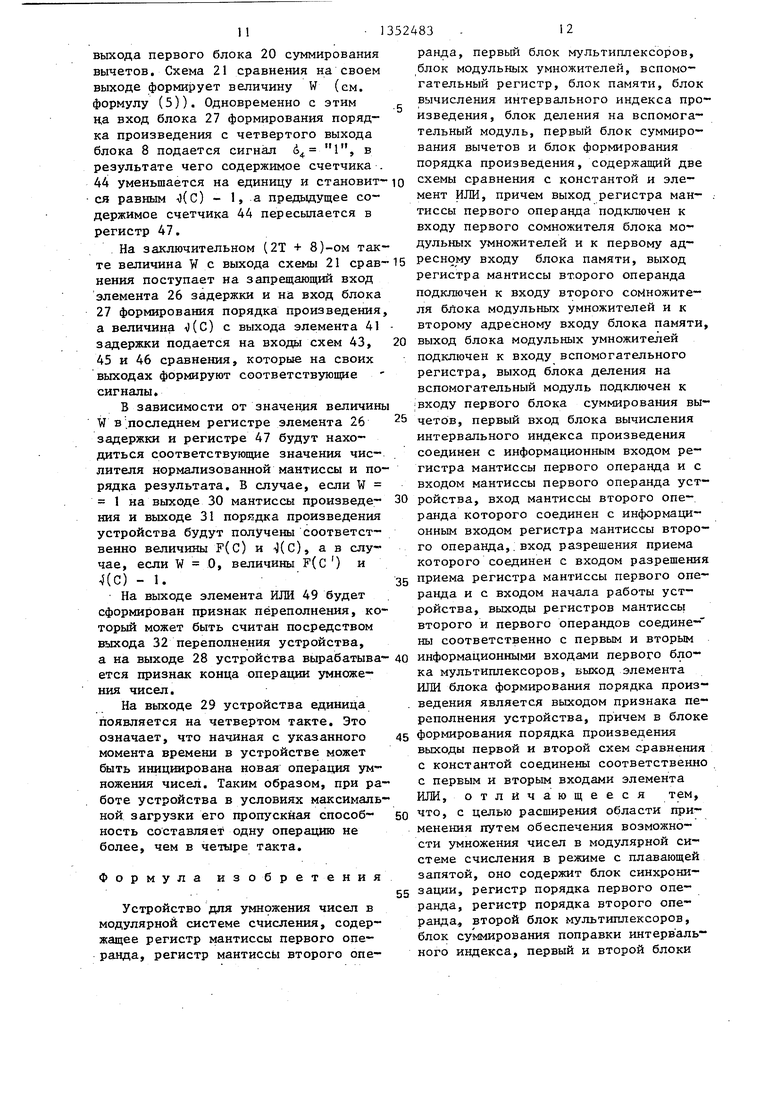

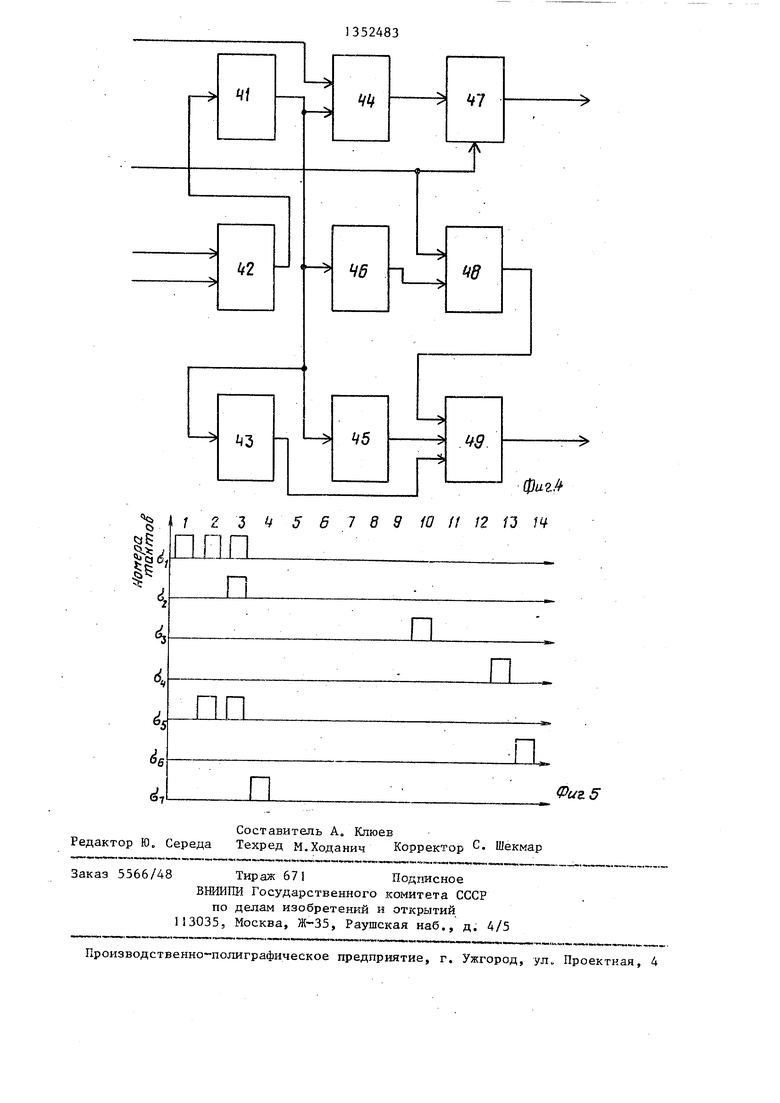

Блок 27 формирования порядка произведения (фиг. 4) содержит элемент 41 задержки, сумматор 42, схему 43 сравнения с константой, счетчик 44, схемы 45 и 46 сравнения с константой, регистр 47, элемент И 48, элемент ИЛИ 49. Элемент 41 задержки представляет собой цепочку из (2Т + 4) последовательно соединенных регистров.

Первая схема 43 сравнения на своем выходе вырабатывает сигнал логической единицы в случае, если величина X, подаваемая на ее вход, удов- летворяет условию X q.

Вторая схема 45 сравнения на своем выходе вырабатывает сигнал логической единицы в случае, если X -q.

О,1,..,,i-l, i+1,...,К-1

M,

i,,/m,-,M k., П m

P через 1X Ip

обозначается наименьший неотрицатель- 5 ный вычет, сравниваемый с величиной X по модулю р.

В ячейку узла 40.1 памяти с адре10

сом у. + Z - 2 станта

записывается кон-

У; |пц-|м ; хм Z-,m;

т.

- Ш;

(2)

5

0 5 0 0

g

Третья схема 46 сравнения на своем выходе вырабатывает сигнал логической единицы, если X q+1, , диапазон изменения порядков рассматриваемых чисел с плавающей запятой.

Блок 13 вычисления интервального индекса произведения, используемый в устройстве, совпадает с блоком вычисления интервального номера произведения прототипа за исключением того, что вход интегральной характеристики (ранга) не задействован. Блок 13 вычисления интервального индекса произведения имеет конвейерную структуру, его быстродействие составляет (Т + 5) тактов при пропускной способности одна операция в один такт.

Первый и второй блоки суммирования вычетов осуществляют сложение за Т тактов наборов из (К-1) вычетов по модулю т 7/ (K-I)S, где S - основание характеристики. Первый и второй блоки 20 и 22 суммирования вычетов име- ют Т - каскадную конвейерную структуру и реализуются аналогично.прототипу .

Первый и второй блоки 19 и 25 вычисления интервального индекса числа служат дпя определения по входному модулярному коду (о/ ,...} ) числа А из диапазона модулярной системы счисления

D { -mlvi |,,...,тМ 1.,- l),

где с/- I А|т,, машинного интервального индекса числа А по формуле

М,-,к-1 i |1Д,1(А)

R-1

ГО;

т, +

(3)

м

т../т, .

Структурно первый и второй блоки 19 и 25 вычисления интервального индекса числа аналогичны блоку суммиро вания вычетов по модулю.

Блок 18 суммирования поправки йн тервального индекса реализуется с по- мощью (К+1) постоянных запоминающих узлов, i- и из которых обладает емко стью слов разрядностью В; бит..В память i-ro постоянного запоминающего узла по адресу X; . записывается константа

.2-- IXj- S + уЧш,.;

Х; Б 0,1,...,т,-1}, у е 0,1,..., т - Ц, i 0,1,...,К.

Блок 24 деления на вспомогательный модуль реализован на основе К постоянных запоминающих узлов, 1-й из которых обладает емкостью 2 слов разрядностью В,- бит. В память i- TO постоянного запоминающего узла по адресу + . 2 записывается константа

л

Тг

т- )

где q.

о m

о к

т.

при 1 ,...К-1|30

при i к,

fj ф,1,.,.,т--1 U1 0,1,,,.Д) . Схема 21 сравнения с константой реали- д зуется на основе постоянного запоми- н.ающего узла емкостью 2 одноразрядных слов, из памяти которое го по адресу I + 2 х считывается константа w 1, если . 40

I-S + Х ||Г-т,-К+2, m -1, (5)

Г I если I 2-т..-+К-2 где I I

1 i-m , в противном случае

I е .0,I,...,m, x e(0,L

,m

-1}

Элемент 26 задержки представляет собой цепочку из (Т+) последовательно соединенных регистров. Вход перво- го из регистров является входом элемента 26 задержки, выход последнего .регистра элемента 26 задержки является его выходом. Управляющий вход запрещения записи последнего регистра элемента 26 за,цержки является его соответствующим управляющим входом.

Устройство осуществляет умножение чисел а );, i)(a)||, Ъ {нСъ),

(b)j , представленных в форме с mia вающей. запятой, где (а) А/М и |u(b) В/М - мантиссы, а V (а) и л)(В)- порядки операндов а и Ъ соответственно; А, BeD; М тоМц,., ; q(a);- V(B) . q.

Условие нормализации в рассматриваемой модулярной системе счисления для чисел а и Ъ имеет вид

- (A), 1(в) . ш - 1,

I(A), I(B) - интервальные индексы соответственно чисел А и В.

Возможно возникновение необходимости нормализации произведения путем умножения на S.

Используя формулу интервально-мо- дулярного представления чисел можно записать

x-i

С А«В Z М.,К-1-|.., К-1

.+ i (c)M., ,

(6)

0

д 0

5

0 5

где у;Д-1 IM ;-., C/m.,-l(C) - интервальный индекс числа С.

Умножая (6) на З.и применяя лемму Евклида из теории делимости, число С С S можно привести к ви,цу k--t

. с 1111.,,., ).,., 4i(cVM,.,,

где I(C ) I(C)-S +il -

iv-i L m, J

Принимая в качестве оценки дроби С 7м величину F(c ) l(C )/MJ, нетрудно показать, что если интервальный индекс числа F{c ) вfcvxoдит за пределы интервала тр-К+2, , то то число F(C )stD.. В этом случае дробь F.( С)/М является нормализованной и, следовательно, представляет собой мантиссу результата в противном случае в качестве мантиссы результата принимается дробь F(C )/M. В первом случае порядок результата определяется соотношегшем А)(С) (а) + о(В), а so втором - лг{С) -л)(а) .+ (Е} - 1.

Рассмотрим, как работает устройство рдгя уг«1ножения чисел в модулярной системе счисления. По сигналу, подаваемому с входа 2 устройства в блок 8, регистр 33 сдвига обнуляется, счетчик 37 посредством второго элемента ИШ .35 также обнуляется,, а триггер 38 посредством второго элемента ИЛИ 36

устанавливается з единичное состояние (фиг. 2), тем самым устройство приводится в исходное рабочее состояние. По сигналу, пoдaвaeмoм, с входа 1 уст ройства на входы разрешения приема регистра 9 мантиссы первого операнда, регистра 10 мантиссы второго операнда, регистра i порядка первого one-, ранда и регистра 12 порядка второго

-Операнда, а.такл;е на вход регистра 33 сдвига блока угфавления 8, записывается едипица в регистр 9 мантиссы первого операнда и регистр 10 мантисС.Ы второго операнда с Входов 45 устройства соответственно принимаются модулярные коды { d ,. , . , и ;,) и (р,... , ) числителей мантисс А и В первого и второго операндов. В регистр 11 порядка первого операнда и регистр 12 порядка второго операнда с входов 6 . и 7 устройства принимшотся двоичмьге - коды порядков -О(а) первого операнда и (В) второго операнда. Модулярный код (с/,,..., с. к) с входа 4 .устройства поступает на первый вход блока 13 вы- числеьшя интервального индекса произведения и после этого начинается первый такт работы устройства.

На первом такте работы устройства на управляющий вход первого блока 14 мультиплексоров подается сигнал О с пятого выхода блока 8, в соответствии с чем модулярный код чис ла В с выхода 10 регистра мантиссы второго операнда через первый инфор- мащюнный вход первого блока 14 мультиплексоров поступает в первый блок 19 вычисления интервального индекса числа, где Б течение очередных Т тактов, считая текущий, в соответствии

с формулой (3) будет вычислен машинный интервальный индекс 1(В) числа В, модулярный код ( л., ,... J ) подается также на третий адресный вход блока 15 памяти, на второй и первый входы разрешения выдачи которого с второго и первого Еыходоз блока 8 поступают соответственно сиг1;алы и , О и 6, 1. В результате ка первом и (j -t- + 1 )-ом выходах блока 5 памяти сформируются соответственно наборы вычетоз.

W

.(..,

У,(В) vR;(;3.),..., R;(B:.,), О, R,

кбхпоненть:

которых опроделяютск

и (2) при X; в ; и этом наборы БЫЧСТОВ

1,..., К-1) в совокупности передаются на третий вход блока 13 вычисления интервального индекса произведения, на второй вход которого подается модулярный код числа с выхода регистра 10 мантиссы второго операнда.

Кроме того, на первом такте работы устройства содержимые регистра 9 манQ тиссы первого операнда и регистра 10 мантиссы второго операнда подаются соответственно на второй и первый входы блока 16 модульных умнохштелей, который получает модулярн.1Й код

5 (у, «-« ) младшей части /С/М про- изведе шя С А В, записывающийся во вспомогательный регистр Г/, а содер- жимые -j(a) регистра 1 порядка первого операнда и v(B) регистра 12 поряд0 ка второго онеранда соответственно через входы блока 27 формирования порядка произведения постз пают на первый и второй входы сумматора 42, который определяет величину v(c)

5 )(а) + )(в}, передающуюся в элемент 41 задержки.

На каждом такте работы устройства для умножеш1Я чисел по сигналу, подаваемому с тактового входа 3 устройст-

0 ва на вход блока 8, содержимое регистра 33 сдвига (фиг. 2) сдвигается на один бит в сторону младших разрядов, при этом с помои ью первого элемента ИЛИ 34 содержимое счетчика 37 увелиj- чивается на единицу, если в одном из двух младших разрядов регистра 33 сдвига до сдвига находилась единица и счетчик 37 обнуляется, а в триггер 38 записывается единнда посредством

Q второго элемента ИЛИ 35 в случае,

когда второй разряд perjiCTpa 33 сдвига принимает единичное значение.

В соответствии с изложенным на втором такте работы устройства на

5 управляющий вход первого блока 14 мультиплексоров подается сигнал us

поэтому модулярный код числа

с выхода регистра 9 мантиссы первого операнда через второй ииформац;1ОН Л; Й вход первого блока 14 мультиплексоров, подается на вход первого блока 19 вычисления интервального индекса числа, где начинается пычясление числа К А), и на третий адресный вход блока 15 памяти, при этом ан;шргично излокенн:оь(у .наборы вычетов Wj(A) в совокупности поступают на третий вход блока 13 вычисления иптервйльного индекса произведения.

На третьем такте работы устройст

ва модулярный код ( ,..., числа

fJ с выхода вспомогательного ре/С/

гистра 17 через третий информационный вход первого блока 14 мультиплексоров на управляющий вход которого подается сигнал dj 2, поступает на третий адресный, вход блока 15 памяти, на . второй и первый адрес1а е входы.которого подаются соответственно коды чисел В с регистра 10 мантиссы второго опе ранда и А - с регистра 9 мантиссы первого операнда. На второй и первый . входы разрешения выдачи блока 15 па мяти подаются сигналы ё 1 и э, 1, в результате на первом H.(j + + 1)-ом выходах блока I5 памяти сфор мируются соответственно наборы констант

Wo(c) :RO(T),...,

и

R

J

(Ь1,,

Wj(C) Rj( 3«,),..

Rj(j,. ), Rj( yj.,).-..«.(yj компоненты которых определяются по формулам (1 ) и (2) при X . ; . | У; ft ; Z cl при этом наборы вычето У(С) в совокупности передаются на третий вход блока 13 вычисления интервального индекса произведения.

На пятом такте работы устройства модулярный код (j ,..., 2 ,) с выхо да вспомогательного регистра 17 пода ется на вход второго блока 22 сумми- рования вычетов, где в течение оче- реднь х Т тактов, считая текущий, бу вычислена величина

..к-1 .VI

I 1x1 L

tel

IC-1

2ili

Bli

ТР..

11

-т.

На (т + 1)-ом такте машинный ин- тервальн ый шздекс 1(В) числа В с выхода первого блока 19 вычисления интервального индекса числа поступает на вход блока 13 вычисления интерваль кого ивдекса произведения,

..

На (Т + 2)-ом такте малипньа интервальный индекс 1(А) числа А с выхода первого блока 19 вычггсления ий-- терзального индекса числа поступает на вход блока 13 вычисления интерваль ного индекса произведения.

На (т -J- 5)-ом такте блок 13 вы числения интервального ивдекса произ- ведешш завершает вычисление интер5

0

25

30

35

Бального индекса l(C) числа.С, l(C)

Чо к.

На (Т + б)ом такте работы устрой

ства на упраплягащий вход второго блока 23 мультитшексоров с третьего выхода блока 8 подается сигнал (Si О, поэтому модулярный код ,чины l(с)5 поступающий с выхода бло ка 13 вычислехшя интервального 1-шдек са произведения на первый информаци вход второго блока 23 мультиплексоров, подается на вход блока 24 деления на вспомогательный модуль. Одновременно с этим величина 1{С) по ступает на первый вход блока 18 с:ум- мирования поправки интервального индекса, на второй вход которого с вы хода второго блока 22 суммирования вычетов поступает величина (/ . Блок 18 на своем выходе сформирует модулярный код (К j..j ц ) величины I(C ). На (т + 7)-ом такте блок 24 деления на вспомогательный модуль определяет модулярный код ( |, ,.,., 2) величины F(C)5 который передается в элемент 26 задержки5 а также поступает на входы первого блока 20 с умми- ровашш вычетов и второго блока 25 вычисления интервального индекса числа, где в течение очередных Т тактов, считая текущий, будут вычислены соответственно величины

K-f

х

IM ,

к-1 -Г; l-m.i S

HI;

m

0

5

0

р.с

и I(F(C)). Одновременно с этим на уп равляющий вход второго блока 23 мультиплексоров подается сигнал &, 1, в соответствии с. чем модулярный код величины l(C ), поступающий с выхода блока 18 на второй информационный вход блока 23 мультиплексоров, подается на вход блока 24 деления на вспомогательный модуль.

На (т + 8)-ом такте работы устройства блок 24 датения на вспомогатель- ньй модуль определяет модулярный код (j , ,... 5 у ) вапичины F( С ), КОТОРЫЙ передается в злемент 26 задержки.

На (2Т -ь 6)-о-м такте величины К С) с выхода элемента 41 задержки поступают в счетчик 44 ;

Ка (2Т + 7)-ом такте работы уст- . ройства на нкод 21 сравнешгя с константой поступают-Веотичины l(F(c)) с выхода второго блока 25 Еычислею я интервального ивдекса числа.и х . п

выхода первого блока 20 суммирования вычетов. Схема 21 сравнения на своем выходе формирует величину W (см. формулу (5)). Одновременно с этим на вход блока 27 формирования порядка произведения с четвертого выхода блока 8 подается сигнал (34 1, в результате чего содержимое счетчика .

44уменьшается на единицу и становит ся равным л)(С) - 1, а предыдущее содержимое счетчика 44 пересылается в регистр 47.

На заключительном (2Т + 8)-ом такте величина W с выхода схемы 21 сравнения поступает на запрещающий вход элемента 26 задержки и на вход блока 27 формирования порядка произведения а величина i)(C) с выхода элемента 41 задержки подается на входы схем 43,

45и 46 сравнения, которые на своих выходах формируют соответствующие сигналы.

В зависимости от значения величины W в .последнем регистре элемента 26 задержки и регистре 47 будут находиться соответствующие значения числителя нормализованной мантиссы и порядка результата. В случае, если W 1 на выходе 30 мантиссы произведе- НИН и выходе 31 порядка произведения устройства будут получены соответственно величины F(C) и (с), а в случае, если W О, величины F(C ) и (С) - 1.

На выходе элемента ИЛИ 49 будет сформирован признак переполнения, который может быть считан посредством выхода 32 переполнения устройства, а на выходе 28 устройства вырабатыва- ется признак конца операции умножения чисел.

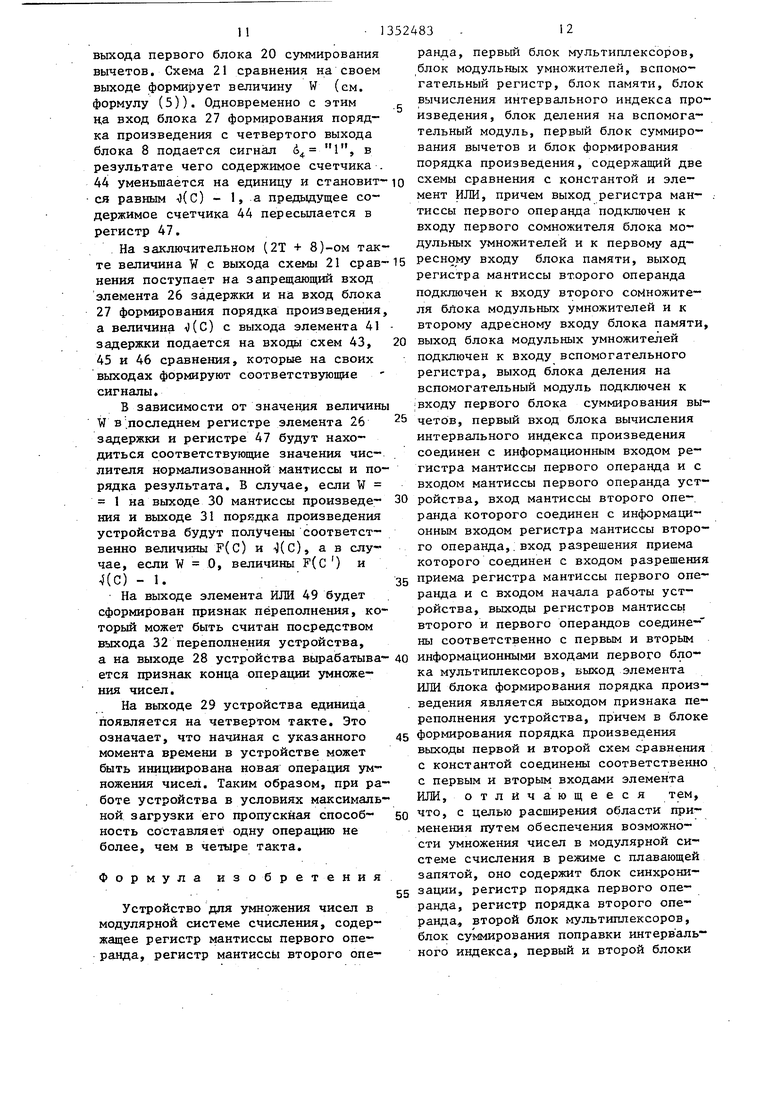

На выходе 29 устройства единица появляется на четвертом такте. Это означает, что начиная с указанного момента времени в устройстве может быть инициирована новая операция умножения чисел. Таким образом, при работе устройства в условиях максимальной загрузки его пропускная способ- ность составляет одну операцию не более, чем в четыре такта.

Формула изобретения

Устройство для умножения чисел в модулярной системе счисления, содержащее регистр мантиссы первого операнда, регистр мантиссы второго опеg

о

5 0

0 35

0

5 0

5

ранда, первый блок мультиплексоров, блок модульных умножителей, вспомогательный регистр, блок памяти, блок вычисления интервального индекса про изведения, блок деления на вспомогательный модуль, первый блок суммирования вычетов и блок формирования порядка произведения, содержащий две схемы сравнения с константой и элемент ИЛИ, причем выход регистра ман- . тнссы первого операнда подключен к входу первого сомножителя блока модульных умножителей и к первому адресному входу блока памяти, выход регистра мантиссы второго операнда подключен к входу второго сомножителя блока модульных умножителей и к второму адресному входу блока памяти, выход блока модульных умножителей подключен к входу вспомогательного регистра, выход блока деления на вспомогательный модуль подключен к входу первого блока суммирования вычетов, первый вход блока вычисления интервального индекса произведения соединен с информационным входом регистра мантиссы первого операнда и с входом мантиссы первого операнда устройства, вход мантиссы второго операнда которого соединен с информационным входом регистра мантиссы второго операнда,. вход разрешения приема которого соединен с входом разрешения приема регистра мантиссы первого операнда и с входом начала работы устройства, выходы регистров мантиссы второго и первого операндов соедине- ны соответственно с первым и вторым информационными входами первого блока мультиплексоров, выход элемента ШЖ блока формирования порядка произведения является выходом признака переполнения устройства, причем в блоке формирования порядка произведения выходы первой и второй схем сравнения с константой соединены соответственно с первым и вторым входами элемента ИЛИ, отличающееся тем, что, с целью расширения области применения путем обеспечения возможности умножения чисел в модулярной системе счисления в режиме с плавающей запятой, оно содержит блок синхронизации, регистр порядка первого операнда, регистр порядка второго операнда, второй блок мультиплексоров, блок суммирования поправки интерв аль- ного индекса, первый и второй блоки

вычисления интервального индекса числа, схему сравнения с константой, второй блок суммирования вычетов, элемент задержки и блок формирования порядка произведения, дополнительно содержит элемент задержки, сумматор, третью схему сравнения с константой, регистр-И элемент И, причем вход за пуска, установочный и тактовый входы блока синхронизации соединены соответственно с входами начала работы, начальной установки и тактовым входом устройства, входы порядка первого и второго операндов устройства соединены соответственно с информационными входами регистров порядка первого и второго операндов, второй вход блока вычисления интервального индекса произведения подключен к выходу регистра мантиссы второго операнда, третий информационный вход первого блока мультиплексоров объединен с входом второго блока суммирования вычетов и подключен к выходу вспомогательного регистра, третий адресный вход блока памяти объединен с входом первого блока вычисления интервального индекса числа и подключен к выходу первого блока мультиплексоров, выходы с первого по седьмой блоков синхрони™ зации соединены с первым и вторым входами разрешения выдачи блока памяти с управляющим входом второго блока мультиплексоров, со счетным входом счетчика блока формирования порядка произведения, с управляющим входом первого блока мультиплексоров, с выходами окончания операции и готовности устройства, третий и четвертый входы блока вычисления интервального ивдекса произведения подключены соот- ветственно к выходам блока памяти и первого блока вычисления интервального индекса числа, выход блока вычисления интервального индекса произ- ведения соединен с входом первого слагаемого блока суммирования поправки, интервального индекса и с первым информационньм входом второго блока

5

0

5

0

5

0

5

мультиплексоров, вход второго слагаемого и выход блока суммирования поправки интервального 1 индекса подключены соответственно к выходу второго блока суммирования вычетов и к второму информационному входу второго блока мультиплексоров, выход которого подключен к входу блока деления на вспомогательньш модуль, выход которого соединен с входом второго блока вычисления интервального индекса числа и с информационным входом элемента задержки, входы разрядов схемы сравнения с константой подключены,соответственно к выходам второго блока gычиcлeшiя интервального индекса числа и первого блока суммирования вычетов, выход схемы сравнения с константой соединен с входом запрещения приема элемента задержки и с первым входом элемента И блока формирования порядка произведения, выходы регистров порядка первого и второго операндов соединены соответственно с входами первого и второго слагаемых сумматора блока формирования порядка про - изведения, выход регистра которого является выходом порядка произведения устройства, вьгкод мантиссы произведения которого соединен с выходом элемента задержки, входы разрешения приема регистров порядка первого и второго операндов соединены с входом начала работы устройства, причем в блоке формирования порядка произведения выход сумматора подключен к входу элемента задержки9 выход которого соединен с информационным входом счетчика, с входами первой, второй и третьей схем сравнения с константой, выход счетчика соединен с информационным входом регистра, первьй вход элемента И и вход запрещения записи регистра объединены, выход третьей схемы сравнения с кон- стантой соединен с вторым входом элемента И , выход которого сое - динен с третьим входом элемента ИЛИ.

Фаг.г

5 6 789 fO f/ 12 П i4

5|

в

Составитель А„ Клюев Редактор Ю, Середа Техред М.Ходанич Корректор С, Шекмар

Заказ 5566/48 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

Изобретение относится к вычис- лительной технике и предназначено для использования в арифметических устройствах с гшавающей запятой, функционирующих в модулярной системе счисления. Цель изобретения - расширение области применения за счет обеспечения умножения чисел в модулярной системе счисления в режиме с плавающей запятой. Поставленная цель достигается тем, что устройство для умножения чисел в модулярной системе счисления, содержащее регистры 9, 10 мантиссы первого и второго операндов, блок 13 вычисления интервального индекса произведения, блок 14 мультиплексоров, блок 15 памяти, блок 16 модульных умножителей, вспомогательный регистр 17, блок 20 суммирования вычетов, блок 24 деления на вспомогательньй модуль, содержит блок 8 синхронизации, регистры 11, 12 порядка первого и второго операндов, блок 18 суммирования поправки интервального индекса, блоки 19j 25 вычисления интервального индекса числа, схему 21 сравнения с константой,- блок 22 суммирования вычетов, блок 23 мультиплексоров, элемент 26 за- и блок 27 формирования порядка произведения с соответствующими связями. 5 ил. С 9 (Л со 01 o 4 00 оо

| Вычислительное устройство в модулярной системе счисления | 1984 |

|

SU1244665A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1986-05-26—Подача