Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих специализированных системах конвейерного типа, функционирую- ш,их в модулярной системе счисления.

Цель изобретения - расширение функциональных возможностей за счет выполнения операции умножения чисел с анализом на переполнение в мoдyv яpнoй системе счисления.

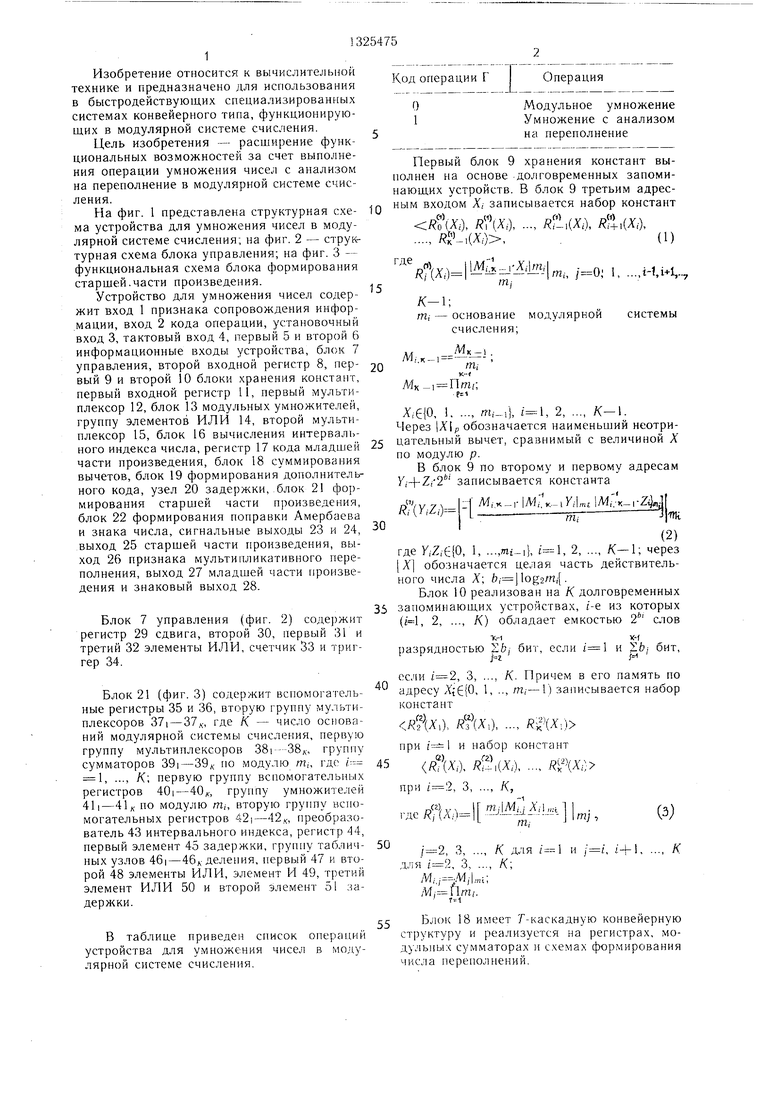

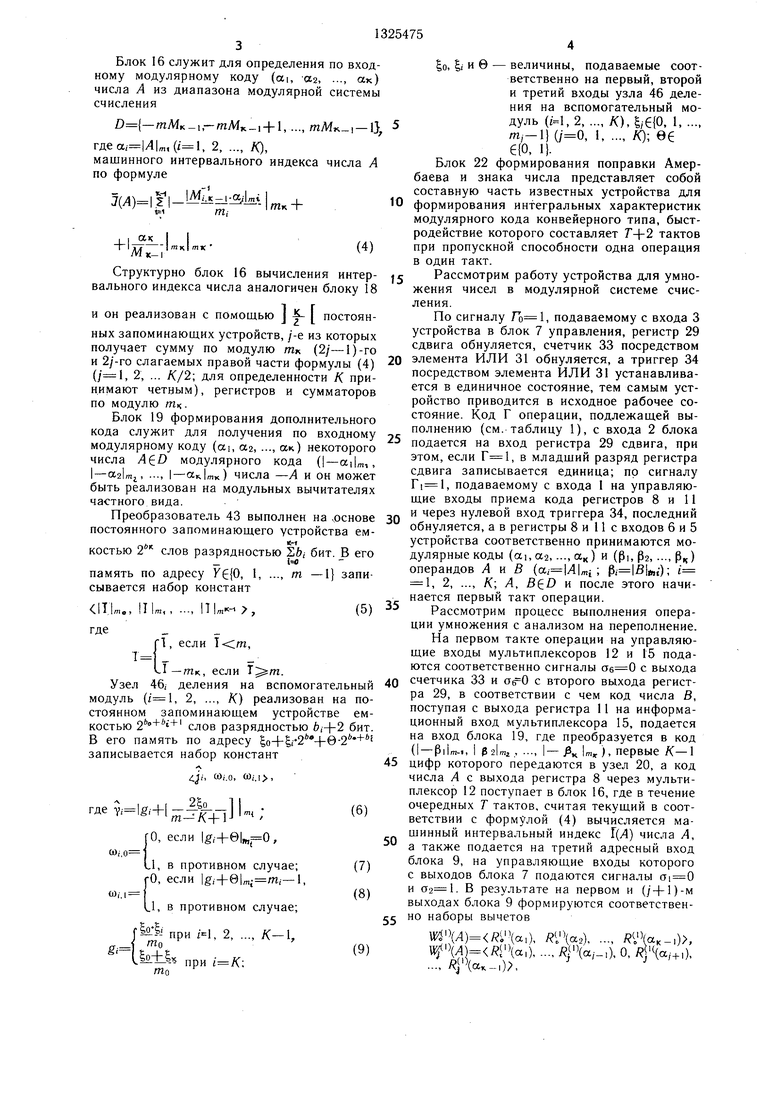

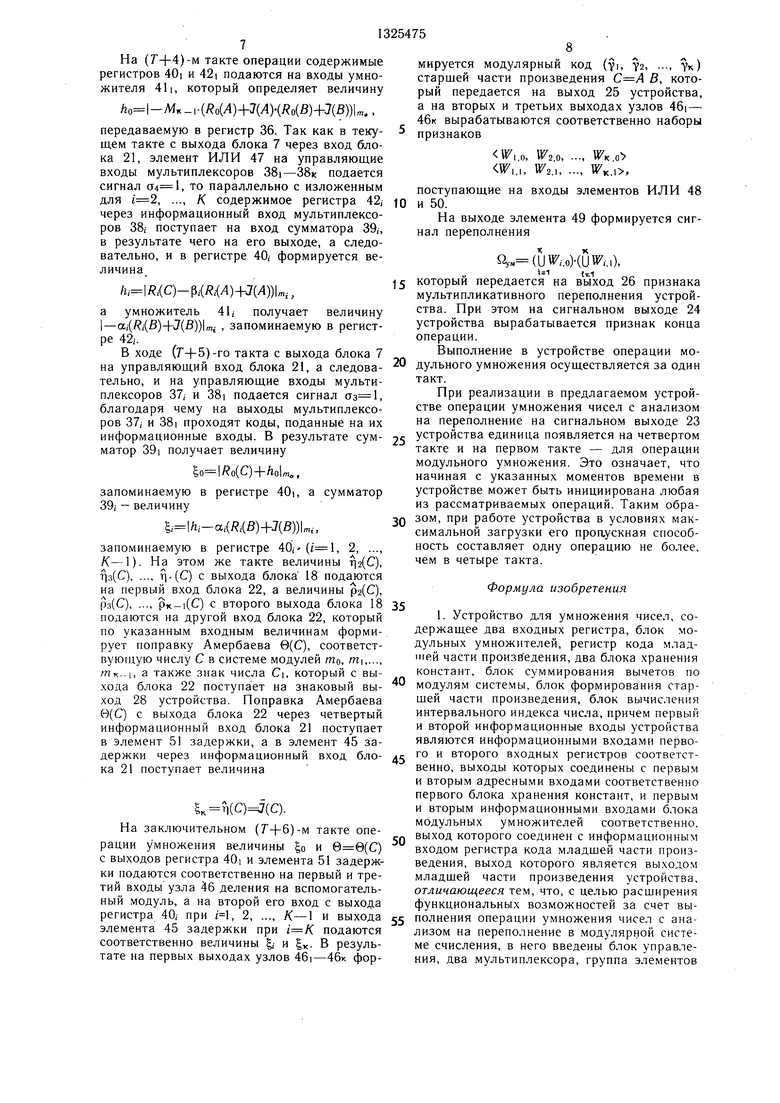

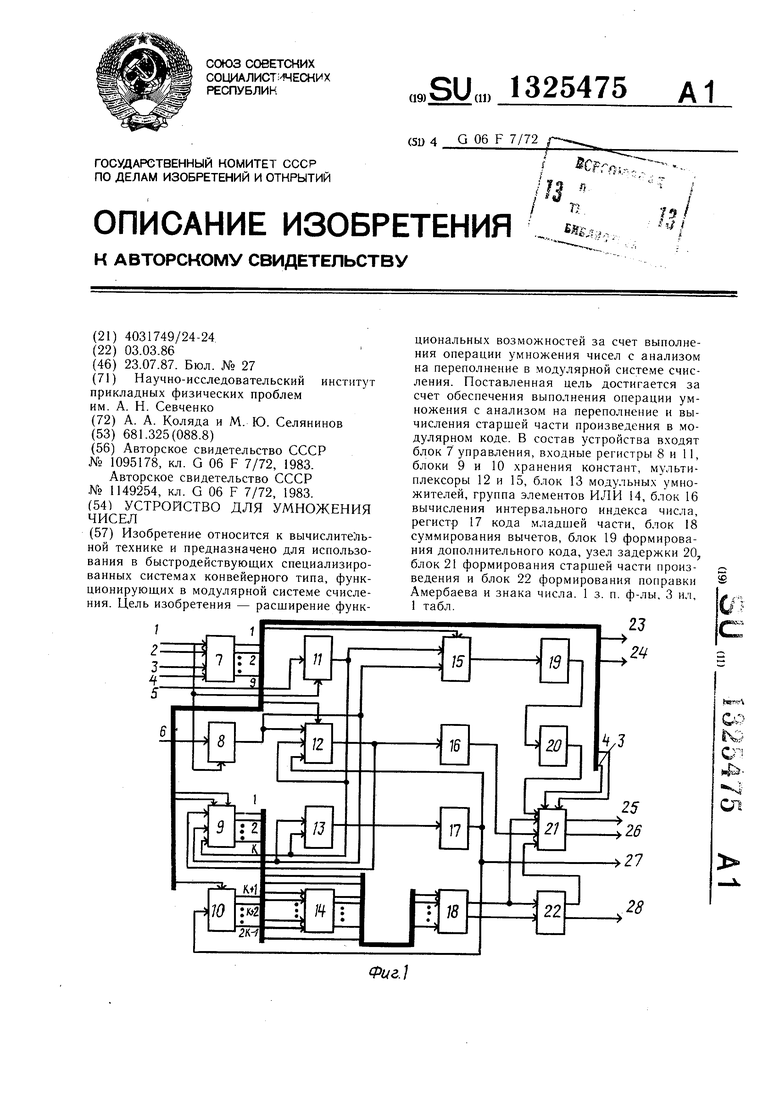

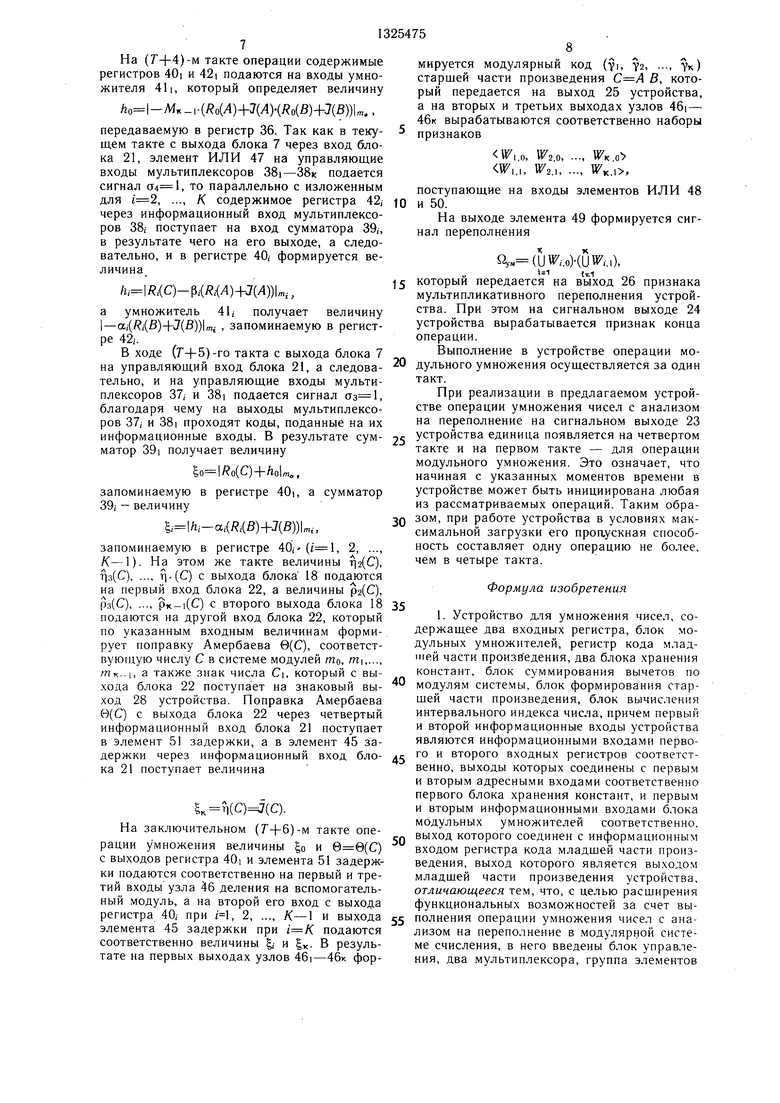

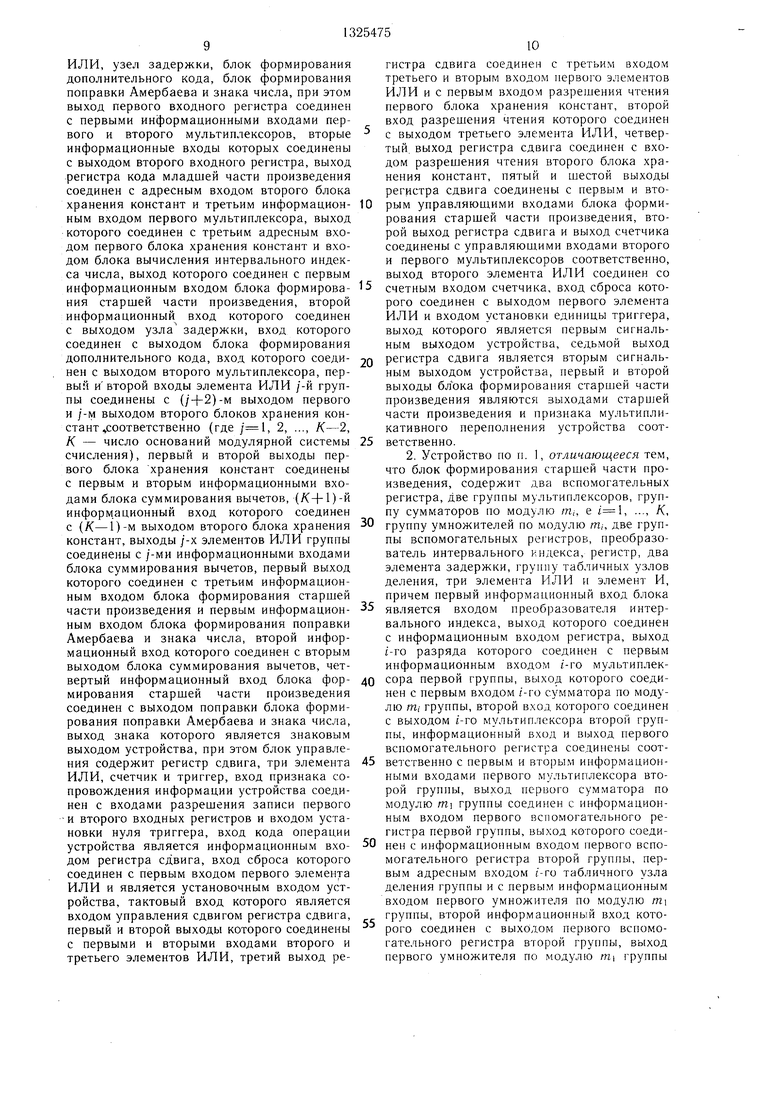

На фиг. 1 представлена структурная схе- ма устройства для умножения чисел в модулярной системе счисления; на фиг. 2 - стру; турная схема блока управления; на фиг. 3 - функциональная схема блока формирования старшей,части произведения.

Устройство для умножения чисел содержит вход 1 признака сопровождения информации, вход 2 кода операции, установочный вход 3, тактовый вход 4, первый 5 и второй 6 информационные входы устройства, блок 7 управления, второй входной регистр 8, пер- вый 9 и второй 10 блоки хранения констант, первый входной регистр 11, первый мультиплексор 12, блок 13 модульных умножителей, группу элементов ИЛИ 14, второй мультиплексор 15, блок 16 вычисления интервального индекса числа, регистр 17 кода младшей части произведения, блок 18 суммирования вычетов, блок 19 формирования дополнительного кода, узел 20 задержки, .блок 2 фо)- мирования старшей части произведения, блок 22 формирования поправки Амербаева и знака числа, сигнальные выходы 23 и 24, выход 25 старшей части произведения, выход 26 признака мультипликативного переполнения, выход 27 младшей части произведения и знаковый выход 28.

Блок 7 управления (фиг. 2) содержит регистр 29 сдвига, второй 30, первый 31 и третий 32 элементы ИЛИ, счетчик 33 и триггер 34.

Блок 21 (фиг. 3) содержит вспомогательные регистры 35 и 36, вторую группу мультиплексоров 37i - 37д., где К - число оснований модулярной системы счисления, первую группу мультиплексоров 38i- -38, группу сумматоров 39|-39 гю модулю т,, где J- 1, ..., К , первую группу вспомогательпь х регистров 40|-40, группу умножителей 41|-41 по модулю т,, Е торую группу вспомогательных регистров 42|-12, преобразователь 43 интервального индекса, регистр 44, первый элемент 45 задержки, группу таблич- ных узлов 46|-46 деления, первый 47 и второй 48 элементы ИЛИ, элемент И 49, третий элемент ИЛИ 50 и второй элемент 51 задержки.

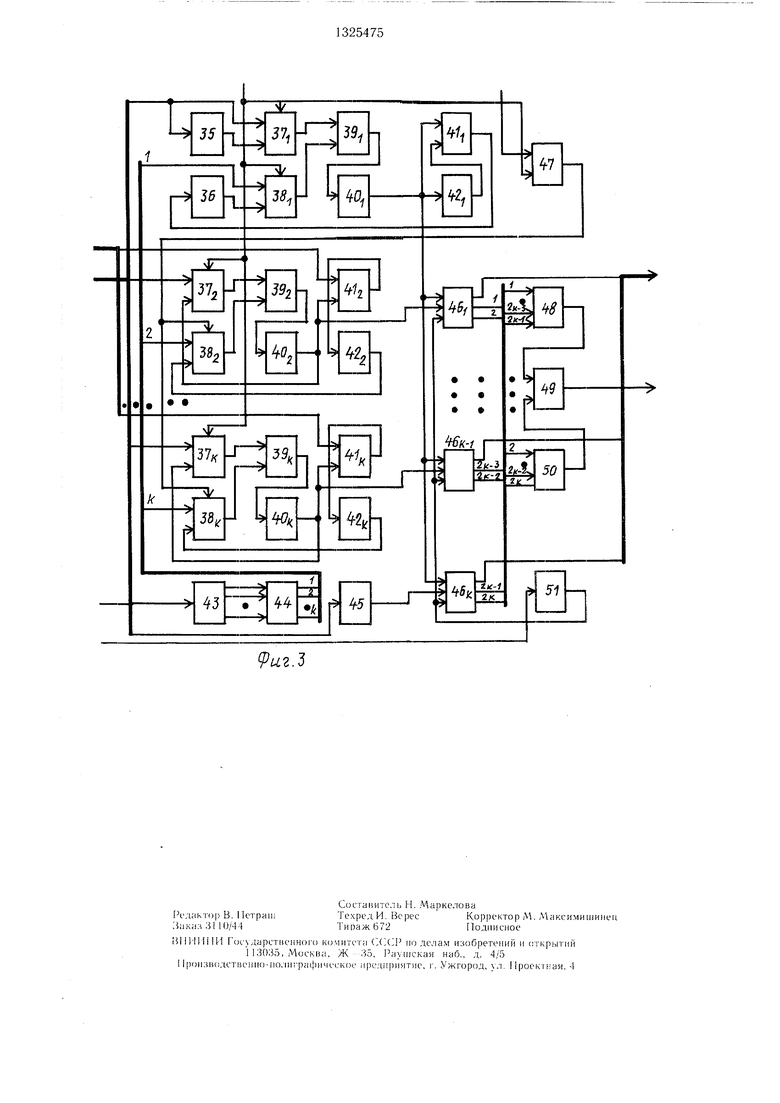

В таблице приведен список операций устройства для умножения чисел в модулярной системе счисления.

i:

Операция

Модульное умножение Умножение с анализом на переполнение

Первый блок 9 хранения констант выполнен на основе долговременных запоминающих устройств. В блок 9 третьим адресным входом X, записывается набор констант

,-), R (X,). ..., ,(X;), ,(Х,-), ,а .л-

...., ,№},

(1)

где

Л

lM.,.,-A i|m,

п-уу ,.- - 1 И-г,, ,

К; (,л,)-I(т,-, j-и; 1, ...,11,1+1,

т/

К-1;

т/ - основание модулярной системы счисления;

М,..,Ь т,К

MK -i Ilm/;

X.ejO, , ..., m;..,}, , 2, ..., K. Через обозначается наименьший неотрицательный вычет, сравнимый с величиной Л по модулю р.

В блок 9 по второму и первому адресам y;-f-Z, 2 записывается константа

(У/2,

4M,.,-|Ai;,K-iK,-l,,

Щ

К

im

(2)

где ViZ.tjO, 1, ...,Mi-il, , 2, ..., /(-1; через A l обозначается целая часть действительного числа А ; fo,,{.

Блок 10 реализован на К долговременных запоминающих устройствах, i-e из которых (Ы, 2, ..., К.) обладает емкостью 2 слов

Т-1Х-(

разрядностью Ifc, бит, если и УЬ, бит,

если , 3, ..., К. Причем в его память по адресу А {({0, 1, .., т,--Г) записывается набор констант

д/,Ч

rff,

ЩА:,). M Uo, .... (X,)

при г 1 и набор констант

(,), И,(.,) R(Xi}

при , 3, ..., /(,

Xil.r.i

m,

Imj,

(3)

, 3, ..., л: для и , i+, ..., к для , 3, ..., К; М,р,М, „к; ;VI,, flm,.

Блок 18 имеет Г-каскадную конвейерную структуру и реализуется на регистрах, модульных сумматорах и схемах формирования числа переполнений.

Блок 16 служит для определения по входному модулярному коду (ai, -аа, ..., ак) числа А из диапазона модулярной системы счисления

О {-тМк-1,- тМк-1 + 1, ..., -1}

, , 2, ..., К),

машинного интервального индекса числа А

по формуле

5(Л)|Г|-1М1:: - и

Ит.

МтгI I Шк +

Структурно блок 16 вычисления интервального индекса числа аналогичен блоку 18

и он реализован с помощью

f

постоянных запоминающих устройств, /-е из которых получает сумму по модулю гпк (2/-1)-го и 2/-ГО слагаемых правой части формулы (4) (, 2, ... К./2; для определенности К принимают четным), регистров и сумматоров по модулю ткБлок 19 формирования дополнительного кода служит для получения по входному модулярному коду (ai, 0.2, ..., ак) некоторого числа модулярного кода (|-ailmi, I-a2lmj, ..., I-ак|тк) числа -А и он может быть реализован на модульных вычитателях частного вида.

По сигналу Л)1, подаваемому с входа 3 устройства в блок 7 управления, регистр 29 сдвига обнуляется, счетчик 33 посредством

20 элемента ИЛИ 31 обнуляется, а триггер 34 посредством элемента ИЛИ 31 устанавливается в единичное состояние, тем самым устройство приводится в исходное рабочее состояние. Код Г операции, подлежащей выполнению (см. таблицу 1), с входа 2 блока подается на вход регистра 29 сдвига, при этом, если , в младший разряд регистра сдвига записывается единица; по сигналу , подаваемому с входа 1 на управляющие входы приема кода регистров 8 и 11

25

Преобразователь 43 выполнен на .основе 30 нулевой вход триггера 34, последний

постоянного запоминающего устройства емit-t

костью 2 слов разрядностью Sfe, бит. В его

память по адресу VgfO, 1, ..., т -1} записывается набор констант

обнуляется, а в регистры 8 и 11 с входов 6 и 5 устройства соответственно принимаются модулярные коды (ai,a2, ...,ах) и (Pi,p2, .... Рк) операндов А к В (а,И1т ; ,); i 1, 2, ..., К; А, и после этого начинается первый такт операции.

1Т1 где

.., II

|TL-,

(5)

(1, если 1.т, I -гпк., если .

Узел 46, деления на вспомогательный модуль (, 2, ..., К) реализован на постоянном запоминающем устройстве емкостью слов разрядностью Ь,+2 бит. В его память по адресу Ы-,-2 Ч-в-2 -+ записывается набор констант

4JI. ft,-.o, ft);.

где9.1яЖ-4|- - и,; го, если

1, в противном случае; О, если |g,+e|m; n,-1,

U)i,0

«1,1

1, в противном случае;

при , 2, ..., К-1, а-

-UJL+I. при то

0, Ei и в - величины, подаваемые соответственно на первый, второй и третий входы узла 46 деления на вспомогательный мо5дуль (ы,2,..., А:),/€{О. I

т-1)(, 1, ..., Ю- в6 6(0, 1).

Блок 22 формирования поправки Амер- баева и знака числа представляет собой составную часть известных устройства для

Ю формирования интегральных характеристик модулярного кода конвейерного типа, быстродействие которого составляет 7+2 тактов при пропускной способности одна операция в один такт.

Рассмотрим работу устройства для умножения чисел в модулярной системе счисления.

По сигналу Л)1, подаваемому с входа 3 устройства в блок 7 управления, регистр 29 сдвига обнуляется, счетчик 33 посредством

20 элемента ИЛИ 31 обнуляется, а триггер 34 посредством элемента ИЛИ 31 устанавливается в единичное состояние, тем самым устройство приводится в исходное рабочее состояние. Код Г операции, подлежащей выполнению (см. таблицу 1), с входа 2 блока подается на вход регистра 29 сдвига, при этом, если , в младший разряд регистра сдвига записывается единица; по сигналу , подаваемому с входа 1 на управляющие входы приема кода регистров 8 и 11

J5

25

ове 30 нулевой вход триггера 34, последний

емго

пи(5)

35

ый поемит. +

40

обнуляется, а в регистры 8 и 11 с входов 6 и 5 устройства соответственно принимаются модулярные коды (ai,a2, ...,ах) и (Pi,p2, .... Рк) операндов А к В (а,И1т ; ,); i 1, 2, ..., К; А, и после этого начинается первый такт операции.

Рассмотрим процесс выполнения операции умножения с анализом на переполнение.

На первом такте операции на управляющие входы мультиплексоров 12 и 15 подаются соответственно сигналы с выхода счетчика 33 и OffO с второго выхода регистра 29, в соответствии с чем код числа В, поступая с выхода регистра 11 на информационный вход мультиплексора 15, подается на вход блока 19, где преобразуется в код

I-PI

Р2

6)

(7) (8)

(9)

50

к Imx), первые /С-1

45 цифр которого передаются в узел 20, а код числа А с выхода регистра 8 через мультиплексор 12 поступает в блок 16, где в течение очередных Т тактов, считая текуший в соответствии с формулой (4) вычисляется машинный интервальный индекс 1(А) числа А, а также подается на третий адресный вход блока 9, на управляющие входы которого с выходов блока 7 подаются сигналы и . В результате на первом и (/4-1)-м выходах блока 9 формируются соответственно наборы вычетов

), ), ..., ,,),

,)(ay-,). О, (а,-+,),

.-, / VK-I);,

55

компоненты которых определяются по формулам (1) и (2) при ,i и Yi-Zi 0. При этом наборы вычетов ) и ) непосредственно, а наборы вычетов , .... W -(А) через элементы ИЛИ 14 группы передаются в блок 18 и по истечении (r+l)- го такта на первом выходе формируется набор величин Ro(A R(A}, ..., (Л), где Ri(A) - сумма по модулю т набора констант , 1, ..., К-).

Кроме того, на первом такте операции содержимые А к В регистров 8 и 11 подаются на входы блока 13, который получает модулярный код младшей части произведения , записывающийся в регистр 17, откуда он может быть считан с помощью выхода 27.

На каждом такте работы устройства для умножения чисел по сигналу, подаваемому с входа 4 на вход блока 7, содержимое регистра 29 сдвигается на один бит в сторону старщих разрядов, при этом с помощью элемента ИЛИ 30 содержимое счетчика 33 увеличивается на единицу, если в одном из двух младших разрядов регистра 29 сдвига до сдвига находилась единица, и счетчик 33 обнуляется, а в триггер 34 записывается единица посредством элемента ИЛИ 31 в случае, когда второй разряд регистра 29 сдвига принимает единичное значение.

В соответствии с указанным на втором такте рассматриваемой операции на управляющие входы мультиплексоров 12 и 15 подаются соответственно сигналы (т, 1 и 05 1, поэтому код числа А, поступая с выхода регистра 8 на информационный вход мультиплексора, подается на вход блока 19, где преобразуется в код (|-aiU, , 1-a2lm.,, ..., I-оск1т), первые К. - 1 цифр которого подаются в узел 20, а код числа В с выхода второго регистра 11 через информационный вход мультиплексора 12 поступает в блок 16, где начинается вычисление мащинного интервального индекса J(B) числа В, и на третий адресный вход блока 9. При этом аналогично изложенному по истечении (7 -f2)-ro такта блок 18 получает набор величин Ro(B), R(B}, ..., RK-I(B}, определяемый так же, как и для числа А.

На третьем такте операции модулярный код (YI, 72, --, YK) числа с выхода регистра 17 через информационный вход мультиплексора 12, на управляющий вход которого подается сигнал (, поступает на третий адресны-й вход блока 9, на второй и первый адресные входы которого подаются соответственно коды чисел Л и В с регистров 8 и 11, а на управляющие входы - сигналы 01 1 и (. В результате на первом и (/+1)-м выходах первого блока 9 хранения констант (, 2, ..., /(-1) формируются соответственно наборы констант

1( ), R

ш( Лс)л} Ы, .... «УЪ/ |Ч7/+.).... / Pk-OJ.

компоненты которых определяются по формулам (1) и (2) при

X-Yb , , (, 2, ..., .

Суммируя наборы указанных вычетов по соответствующим модулям, блок 18 по истечении (7 +3)-го такта получает набор величин Ro(C), R(C), ..., ;.K-i(C).

На четвертом такте модулярный код (Vb Y2. YK) с выхода регистра 17 подается 0 на адресный вход блока 10, на управляющий вход которого с выхода блока 7 поступает сигнал , поэтому на /-м выходе блока 10 формируется набора констант

),(70, 1(72), ..., «K.(T, + l),

(, 2, ..., К-1), определяемых по формуле (3) при , 2, ..., К). При этом набор констант ) через /-ю группу элементов ИЛИ (, 2, ..., л:-2), а набор констант (C) непосредственно поступа- 0 ют в блок 18, который но истечении (7+4)-го такта на своих выходах сформирует величины

5

riKCHIS f (7,)U.i ; /-2, 3, ..., Л-.

и

/(с) ,-)

, 3,

(К-1).

0

5

На (Г+lj-M такте машинный интервальный индекс 1(А) числа А с выхода блока 16 Q через вход блока 21 поступает на вход преобразователя 43, который формирует набор вычетов

р(Л)|„,, и(Л)и,, ..., р(л)|,„,., ,

запоминаемый в регистре 44.

5 На (7+2)-м такте операции на управляющие входы блока 21 с выходов блока 7 подаются сигналы и , в соответствии с чем на управляющие входы мультиплексоров 38i и 37i-37к подается сигнал , а на управляющие входы мультиплек0 соров 382-38к подается сигнал а 0зУо4 0 с выхода элемента ИЛИ 47, поэтому вычет |J()L( с г-го выхода регистра 44 через информационный вход мультиплексоров 38j поступает на вход модульного сумг матора 39;, на другой вход которого с выхода блока 18 подается величина /,(Л). Сумма-- тор 39; находит вычет (Ri(A)( ), и он записывается во вспомогательный регистр 40,- (, 1, ..., К-).

На (Г4-3)-м такте содержимое регистра 40i пересылается во вспомогательный регистр 42i. Содержимое регистра 40; (, 2, ..., К-1) подается на вход модульного умножителя 41;, а на другой вход с выхода элемента 20 через блок 21 подается вычет Шт. Величина | - р,((Л)+7(Л)„,,., полученная умножителем 41;, передается в регистр 42;. Одновременно с этим в регистре 40; формируется вычет ((В)+7(В)|,„.) для всех , ..., К.

На (7+4)-м такте операции содержимые регистров 40i и 42 подаются на входы умножителя 411, который определяет величину

/1о I-М. - |-((Л)+7((В)+ади.,

передаваемую в регистр 36. Так как в текущем такте с выхода блока 7 через вход блока 21, элемент ИЛИ 47 на управляющие входы мультиплексоров 38i-38к подается сигнал , то параллельно с изложенным для , ..., /С содержимое регистра 42, через информационный вход мультиплексоров 38; поступает на вход сумматора 39/, в результате чего на его выходе, а следовательно, и в регистре 40; формируется ве- личина

/г,.1/,(С)-р;(/,Л)+7(Л))и,,

а умножитель 41; получает величину 1-ai(Ri{B)(B))mi , запоминаемую в регистре 42;.

в ходе (Г+5)-го такта с выхода блока 7 на управляющий вход блока 21, а следовательно, и на управляющие входы мультиплексоров 37; и 38 подается сигнал , благодаря чему на выходы мультиплексоров 37; и 38: проходят коды, поданные на их информационные входы. В результате сумматор 39i получает величину

(C} + ,,,

запоминаемую в регистре 40i, а сумматор 39; - величину

|; |/t;-a;((B)+J(B))L,,

запоминаемую в регистре 40;-(, 2, ..., К-). На этом же такте величины т12(С),

г|з(С) Ц-(С} с выхода блока 18 подаются

на первый вход блока 22, а величины р2(С), рз(С), ..., pK-i(C) с второго выхода блока 18 подаются на другой вход блока 22, который по указанным входным величинам формирует поправку Амербаева в(С), соответствующую числу С в системе модулей то, т,..., , а также знак числа Ci, который с выхода блока 22 поступа ет на знаковый выход 28 устройства. Поправка Амербаева в(С) с выхода блока 22 через четвертый информационный вход блока 21 поступает в элемент 51 задержки, а в элемент 45 задержки через информационный вход бло- ка 21 поступает величина

,Л(С)(С).

На заключительном (7-|-6)-м такте операции умножения величины о и (С) с выходов регистра 40i и элемента 51 задержки подаются соответственно на первый и третий входы узла 46 деления на вспомогательный модуль, а на второй его вход с выхода регистра 40; при , 2, ..., К-1 и выхода элемента 45 задержки при подаются соответственно величины - и |х- В результате на первых выходах узлов 46:-46к фор8

мируется модулярный код (YI, V2. . YK ) старшей части произведения В, который передается на выход 25 устройства, а на вторых и третьих выходах узлов 46i- 4бг вырабатываются соответственно наборы признаков

|,0, Г2.0, ..., 1Гк.О W ,,,, Г2,,, ..., W,l,

поступающие на входы элементов ИЛИ 48 0 и 50.

На выходе элемента 49 формируется сигнал переполнения

Цм(.о(),

Ul(«I

5 который передается на выход 26 признака мультипликативного переполнения устройства. При этом на сигнальном выходе 24 устройства вырабатывается признак конца операции.

Выполнение в устройстве операции модульного умножения осуществляется за один такт.

При реализации в предлагаемом устройстве операции умножения чисел с анализом на переполнение на сигнальном выходе 23 устройства единица появляется на четвертом такте и на первом такте - для операции модульного умножения. Это означает, что начиная с указанных моментов времени в устройстве может быть инициирована любая из рассматриваемых операций. Таким обра0 зом, при работе устройства в условиях максимальной загрузки его проаускная способность составляет одну операцию не более, чем в четыре такта.

0

5

5

5

0

0

5

Формула изобретения

1. Устройство для умножения чисел, содержащее два входных регистра, блок модульных умножителей, регистр кода младшей части произв едения, два блока хранения констант, блок суммирования вычетов по модулям системы, блок формирования стар- щей части произведения, блок вычисления интервального индекса числа, причем первый и второй информационные входы устройства являются информационными входами первого и второго входных регистров соответственно, выходы которых соединены с первым и вторым адресными входами соответственно первого блока хранения констант, и первым и вторым информационными входами блока модульных умножителей соответственно, выход которого соединен с инфopмaциoнны входом регистра кода младщей части произведения, выход которого является выходом младщей части произведения устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения операции умножения чисел с анализом на переполнение в модулярной системе счисления, в него введены блок управления, два мультиплексора, группа элементов

ИЛИ, узел задержки, блок формирования дополнительного кода, блок формирования поправки Амербаева и знака числа, при этом выход первого входного регистра соединен с первыми информационными входами первого и второго мультиплексоров, вторые информационные входы которых соединены с выходом второго входного регистра, выход регистра кода младшей части произведения соединен с адресным входом второго блока хранения констант и третьим информацион- ным входом первого мультиплексора, выход которого соединен с третьим адресным входом первого блока хранения констант и входом блока вычисления интервального индекса числа, выход которого соединен с первым информационным входом блока формирова- ния старшей части произведения, второй информационный вход которого соединен с выходом узла задержки, вход которого соединен с выходом блока формирования дополнительного кода, вход которого соеди- нен с выходом второго мультиплексора, первый и второй входы элемента ИЛИ /-и группы соединены с ()-м выходом первого и /-М выходом второго блоков хранения констант соответственно (где , 2, ..., /С-2, К - число оснований модулярной системы счисления), первый и второй выходы первого блока хранения констант соединены с первым и вторым информационными входами блока суммирования вычетов, ()- информационный вход которого соединен с (К-1)-м выходом второго блока хранения констант, выходы /-х элементов ИЛИ группы соединены с /-ми информационными входами блока суммирования вычетов, первый выход которого соединен с третьим информационным входом блока формирования старшей части произведения и первым информацион- ным входом блока формирования поправки Амербаева и знака числа, второй информационный вход которого соединен с вторым выходом блока суммирования вычетов, четвертый информационный вход блока фор- мирования старшей части произведения соединен с выходом поправки блока формирования поправки Амербаева и знака числа, выход знака которого является знаковым выходом устройства, при этом блок управления содержит регистр сдвига, три элемента ИЛИ, счетчик и триггер, вход признака сопровождения информации устройства соединен с входами разрешения записи первого и второго входных регистров и входом установки нуля триггера, вход кода операции устройства является информационным вхо- дом регистра сдвига, вход сброса которого соединен с первым входом первого элемента ИЛИ и является установочным входом устройства, тактовый вход которого является

входом управления сдвигом регистра сдвига

первый и второй выходы которого соединены с первыми и вторыми входами второго и третьего элементов ИЛИ, третий выход ре10 1520 25 0540455055

гистра сдвига соединен с третьим входом третьего и вторым входом первого элементов ИЛИ и с первым входом разрешения чтения первого блока хранения констант, второй вход разрешения чтения которого соединен с выходом третьего элемента ИЛИ, четвертый, выход регистра сдвига соединен с входом разрешения чтения второго блока хранения констант, пятый и шестой выходы регистра сдвига соединены с первым и вторым управляющими входами блока формирования старшей части произведения, второй выход регистра сдвига и выход счетчика соединены с управляюш.ими входами второго и первого мультиплексоров соответственно, выход второго элемента ИЛИ соединен со счетным входом счетчика, вход сброса которого соединен с выходом первого элемента ИЛИ и входом установки единицы триггера, выход которого является первым сигнальным выходом устройства, седьмой выход регистра сдвига является вторым сигнальным выходом устройства, первый и второй выходы бл ока формирования старшей части произведения являются выходами старшей части произведения и признака мультипликативного переполнения устройства соответственно.

2. Устройство по п. 1, отличающееся тем, что блок формирования старшей части произведения, содержит два вспомогательных регистра, две группы мультиплексоров, группу сумматоров по модулю т,, е , ..., К, группу умножителей по модулю /П;, две группы вспомогательных рег истров, преобразователь интервального индекса, регистр, два элемента задержки, группу табличных узлов деления, три элемента ИЛИ и элемент И, причем первый информационный вход блока является входом преобразователя интервального индекса, выход которого соединен с информационным входом регистра, выход г -го разряда которого соединен с первым информационным входом г -го мультиплексора первой группы, выход которого соединен с первым входом /-го сумматора по модулю т,- группы, второй вход которого соединен с выходом i-ro мультиплексора второй группы, информационный вход и выход первого вспомогательного регистра соединены соответственно с первым и вторым информационными входами первого мультиплексора второй группы, выход первого сумматора по модулю rni группы соединен с информационным входом первого вспомогательного регистра первой группы, выход которого соединен с информационным входом первого вспомогательного регистра второй группы, первым адресным входом г-го табличного узла деления группы и с первым информационным входом первого умножителя по модулю т группы, второй информационный вход которого соединен с выходом первого вспомогательного регистра второй группы, ВЬЕХОД первого умножителя по модулю гп группы

11

соединен с информационным входом второго вспомогательного регистра, выход которого соединен с вторым информационным входом первого мультиплексора первой группы, первый управляющий вход блока является первым входом первого элемента ИЛИ, второй вход которого является вторым управляющим входом блока и соединен с управляющими входами первого мультиплексора первой группы и всех мультиплексоров второй группы, выход первого элемента ИЛИ соединен с управляющим входом (г+1)-го мультиплексора первой группы, второй информационный вход которого соединен с выходом (г-f 1)-го вспомогательного регистра второй группы, информационный вход кото- рого соединен с выходом (i-fl)-го умножителя группы по модулю m,-+i, первый информационный вход которого соединен с вторым информационным входом блока, третий информационный вход которого является ин- формационным входом первого вспомогательного регистра и соединен с входом первого элемента задержки и первым инфор1325475

12

мационным входом (/-4-1)-го мyльтиплeкcoJ ра второй группы, второй информационный вход которого соединен с выходом ((+1)-го вспомогательного регистра первой группы, с вторым информационным входом (/-|-1)-го умножителя по модулю mi+ группы и вторым адресным входом г-го табличного узла деления группы, выход первого эл.емента задержки соединен с вторым адресным входом /С-го табличного узла деления группы, третий адресный вход которого соединен с выходом второго элемента задержки и третьим адресным входом (i-1)-го табличного узла деления группы, перв ый выход которого является первым рыходом блока, вторым выходом которого является выход элемента И, первый и второй входы которого соединены с выходами второго и третьего элементов ИЛИ соответственно, второй и третий выходы /-го табличного узла деления группы соединены с i-ми входами второго и третьего элементов ИЛИ соответственно, выход (г + 1)-го сумматора по модулю т,ч-| соединен с информационным входом (J+1)- го вспомогательного регистра первой группы.

.2

9U2.

Состаинтель Н. .Маркелова

Техред И. 5сресКорректор ДА. Макснмишинец

Тираж 672Подписное

lil 11-11111И Г()е дарст 1енного комитета С/ХЛ ио делам изобретений и открытии

1 13035, А осква, Ж 35, Рауи1ская иаб., д. 4/5 11|)01131К дет1)е11110Ч10.-|Игра4 ическое 1рсдприятие, i-. Ужгород, ул. Проектная. 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Вычислительное устройство в модулярной системе счисления | 1984 |

|

SU1244665A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих специализированных системах конвейерного типа, функционирующих в модулярной системе счисления. Цель изобретения - расширение функциональных возможностей за счет выполнения операции умножения чисел с анализом на переполнение в модулярной системе счисления. Поставленная цель достигается за счет обеспечения выполнения операции умножения с анализом на переполнение и вычисления старшей части произведения в модулярном коде. В состав устройства входят блок 7 управления, входные регистры 8 и 11, блоки 9 и 10 хранения констант, мультиплексоры 12 и 15, блок 13 модульных умножителей, группа элементов ИЛИ 14, блок 16 вычисления интервального индекса числа, регистр 17 кода младшей части, блок 18 суммирования вычетов, блок 19 формирования дополнительного кода, узел задержки 20, блок 21 формирования старшей части произведения и блок 22 формирования поправки Амербаева и знака числа. 1 з. п. ф-лы, 3 ил, 1 табл. ( О К: . ы СЛ

| Устройство для умножения чисел по модулю @ | 1983 |

|

SU1095178A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1986-03-03—Подача