Изобретение гл носится к электротехнике, а именно к измерению характеристик гибридных шаговых электродвигателей (ШД), и может э;ль использовано при исследовании и контрольны испытаний двигателей в процессе производства

Цель иэобр; - ровыи ен л (SH-J- сти контроли

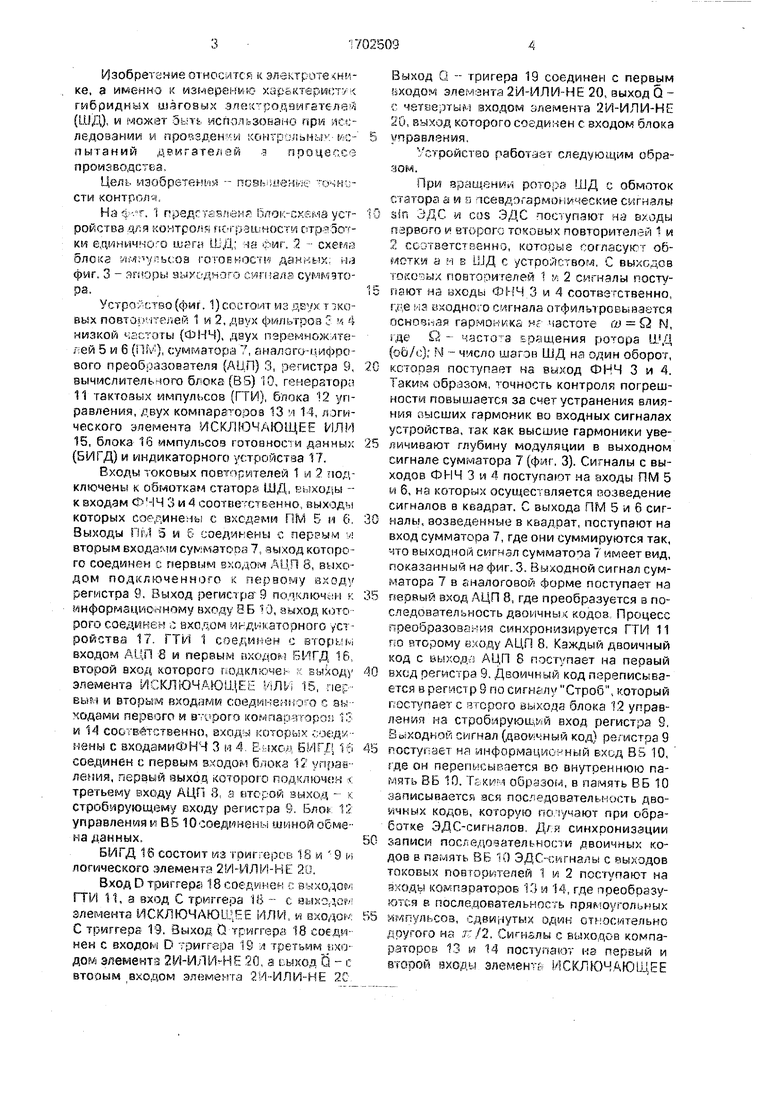

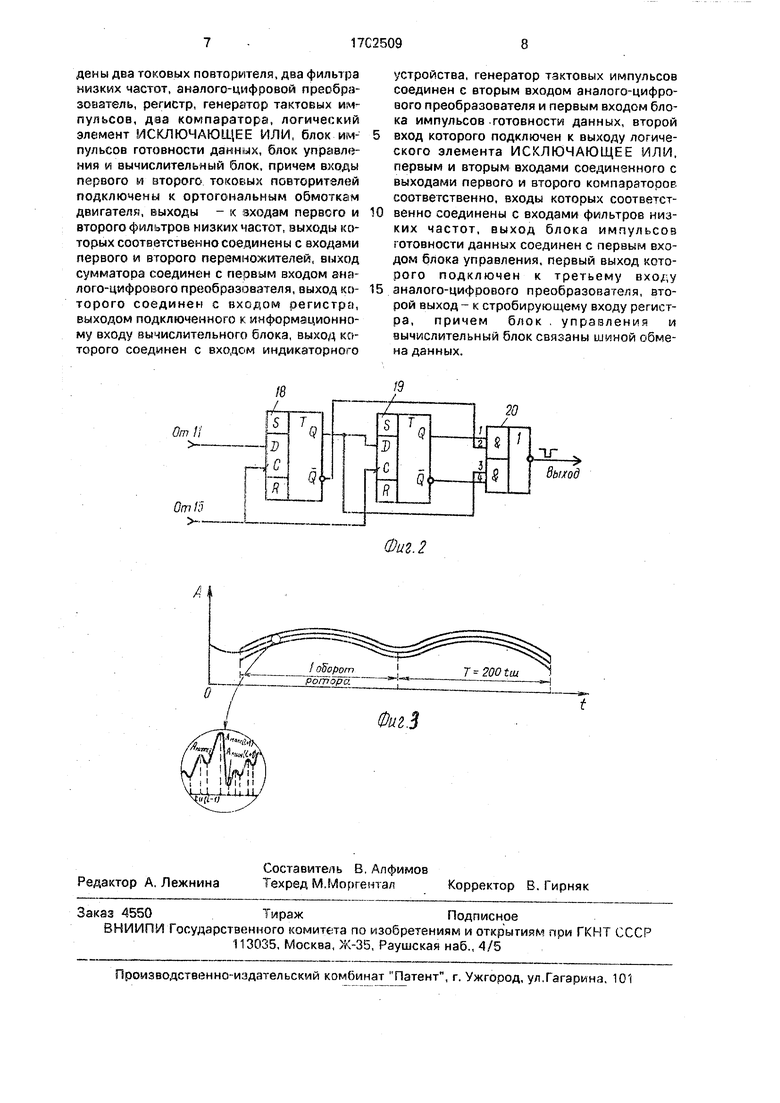

На , г. 1 ьччен блок-сус-ма устройства цля коитропя погрешности ки ег мниччо а И|Д: на Фиг 5 схема блока лм -ьсоа готовности данных, на фиг. 3 - -- ii jpb- -дього сигнала сумматора.

Устрой /П-.О (фИГ. 1) СОСТОИТ ИЗ ДР//Х Т КОвых повто т« чей 1 и 2, фильтров 3 и 4 низкой ч с сны (сынЧ), двух перемножите- ; ей 5 и 6 (), сумматора 7, аналого-цифрового преоб 1азоеэтеля (АЦП) 3. регистра 9, вычислительного блока (ВБ) 10, генератора 11 такгоэых импульсов (ГТИ), блока 12 управления, /пвух компараторов 13 и 14, логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, блока 16 импульсов готовности данных (5ИГД) и индикаторного устройства 17,

Входы токовых повторителей 1 и 2 подключены к обмоткам статора ШД, выходы - к входам ФЧЧ 3 и 4 соответственно, выходы которых сомине мы с входами ПМ 5 и 6. Выходы Иг,1 5 и t соединены с первым и вторым входами сумматопа 7, выход которого соединен с первым входом АЦП 8, выходом подключенного к первому входу регистра 9. Выход регистра 9 подключен к информационному входу ВБ 10, выход которого соединен ,: входом индикаторного устройства 17. ГТи 1 соединен с вторим входом АЦП 8 и первым входом БИГД 16, второй вход которого подключен выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, лер- вым и вторым входами соединенного с вы ходами первого и второго компаратороп 13 и 14 соответственно, входы которых соединены с входамиФНЧ 3 и 4. Выход БИГД 16 соединен с первым вводом блока 12 vnpae- ления, первый выход которого подключен к третьему входу АЦП 8, а второй выход - к стробирующему входу регистра 9. Блок 12 управления и ВБ Юсоединены шиной обмена данных.

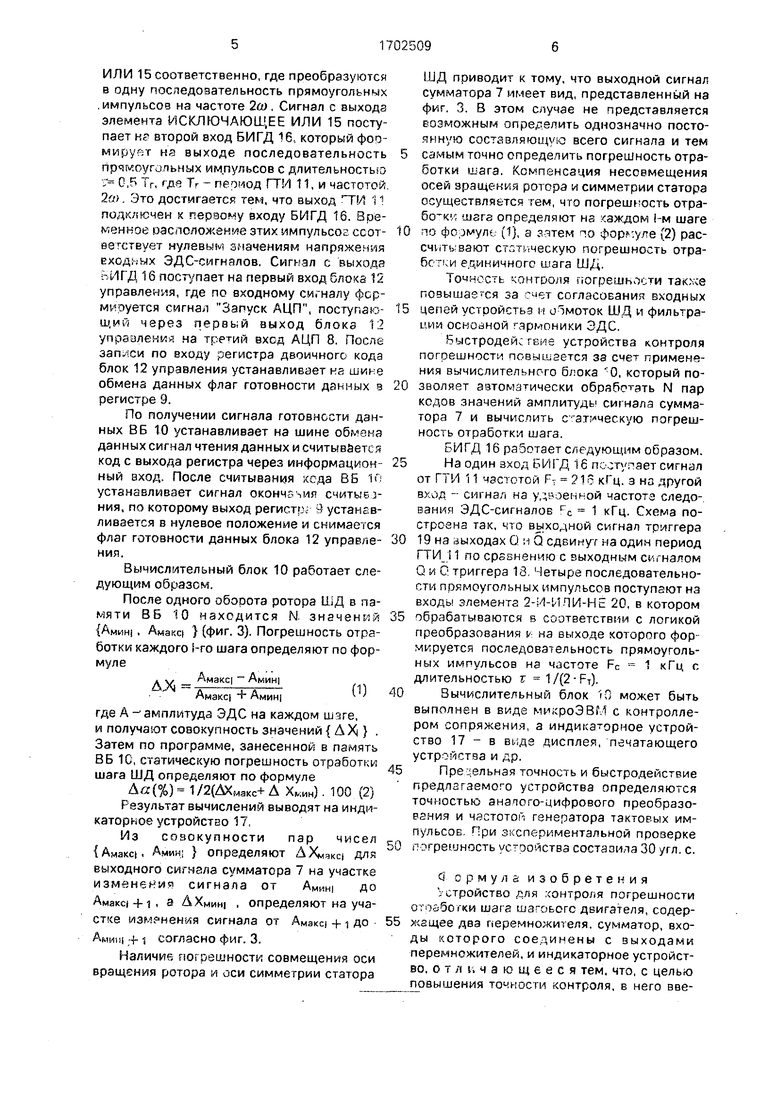

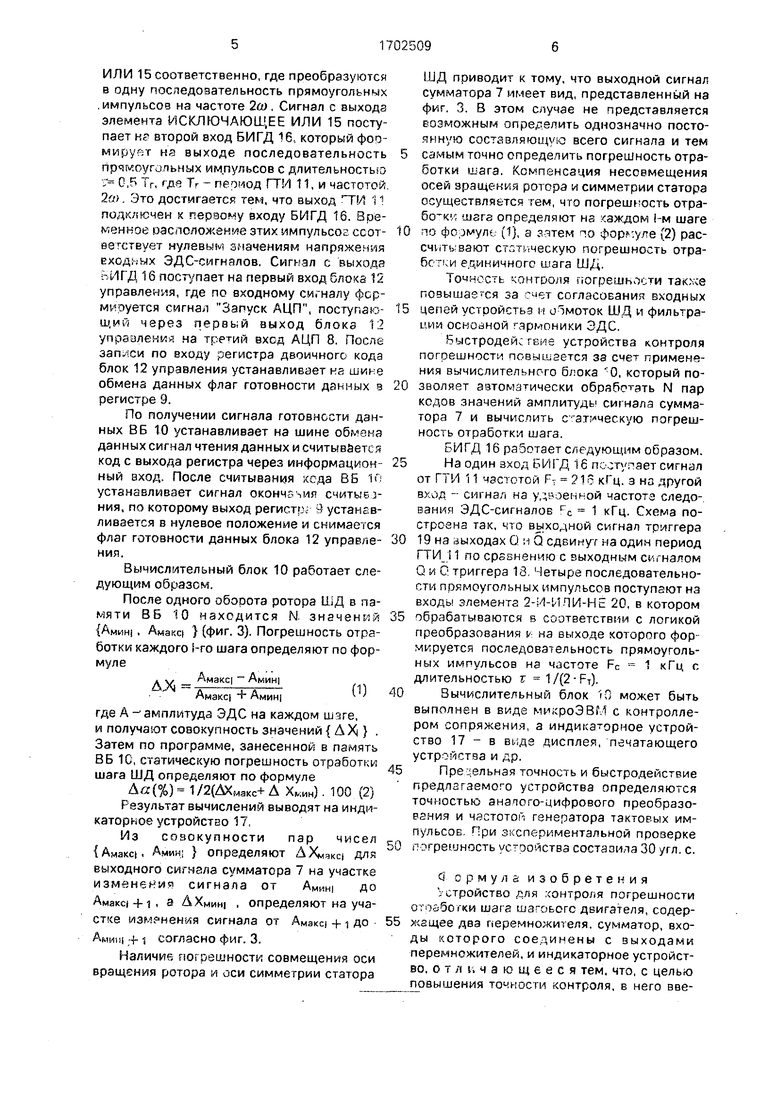

БИГД 16 состоит из триггеров 18 и 19 и логического элемента 2И-ИЛИ-НЕ 20.

Вход D триггера 18 соединен с выходом ГТИ 11, а вход С триггера 18 с выходим элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, и входом С триггера 19. Выход Q триггера 18 соединен с входом D триггера 19 и третьим входом элемента 2И-И.ПИ-НЕ 20, а ьыход U - с вторым входом элемента 2И-ИЛИ-НЕ 20.

Выход О тригера 19 соединен с первым входом эпемэнтя 2И-ИЛИ-НЕ 20, выход Q - с чь-тсе,) входом элемента 2И-ИПИ-НГ. 20, вы од которого соединен с входом блока

управления.

строиство pa6oidfei образом.

При вращг.нип ротора ШД с обмоток статора а и в псевдогармоьические сигналы

ОДС и cos ЭДС поступают на входы первого и егорой., токовых повторителей и 2 сс.чветстюнно. котооые согласую1 ob- мстки а ч в ШД с устройством. С выходов гоко ых повториге ей 1 и 2 сигналы поступэют на ьходы cDh 3 и 4 соответственно /,е сходно- о сигнала огфипыровыйаотся ОСНОВ.-ЯР rapMOiiHK иг частоте О) - Q N, .де L2 - частота сращения ротора Ц Д (ob/r), N - число шэ;ов ШД ня один оборот,

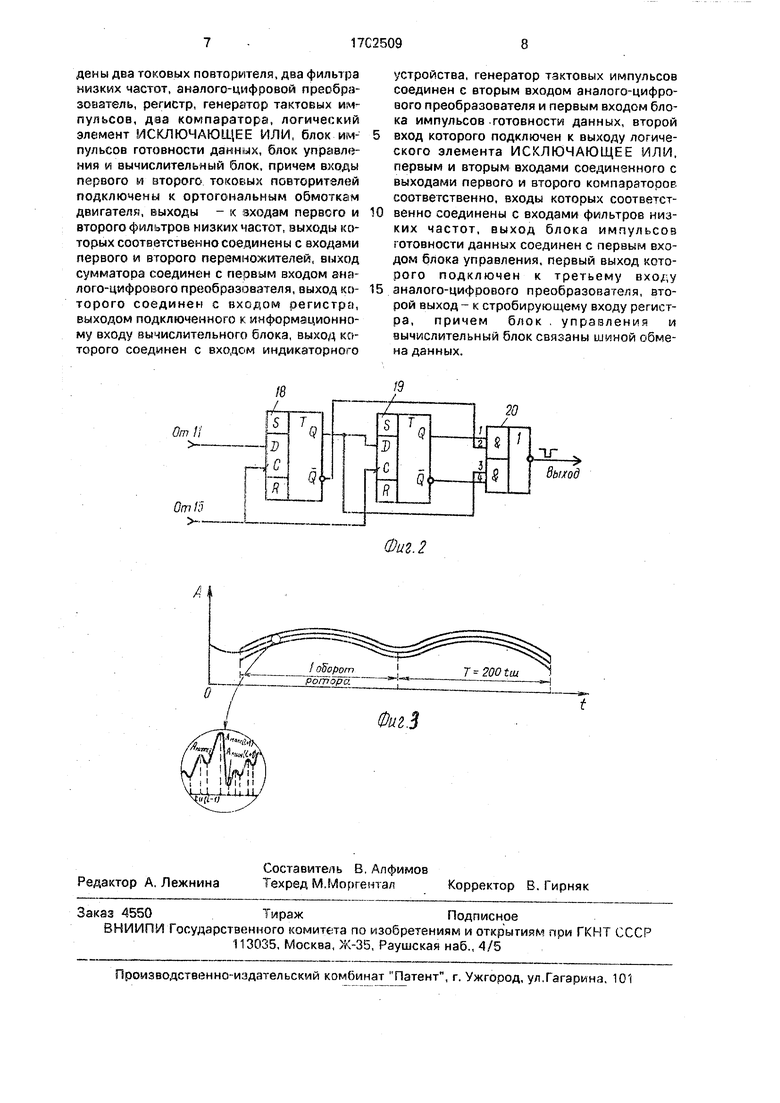

кс топая поступает на выход ФИЧ 3 и 4. Таким обрззом, точность контроля погрешности повышается за счет устранения влияния оысших гармоник во входных сигналах устройства, так как высшие гармоники увеличивают глубину модуляции в выходном сигнале сумматора 7 (фиг. 3). Сигналы с выходов ФНЧ 3 и 4 поступают на входы ПМ 5 и 6, на которых осуществляется возведение сигналов в квадрат. С выхода ПМ 5 и 6 сигналы, возведенные в квадрат, поступают на вход сумматора 7. где они суммируются так, что выходной сигнал сумматора 7 имеет вид, показанный на фиг. 3. Выходной сигнал сумматора 7 в аналоговой форме поступает на

первый вход АЦП 8, где преобразуется в по- следонател.ность двоичных кодов Процесс преобразования синхронизируется ГТИ 11 по второму ь (оду АЦП 8. Каждый двоичный код с вьг од -. АЦП 8 поступает на первый

вхсд регист рэ 9. Двоичный код переписывается в регистр 9 по сигналу Строб, который поступает с второго выхода блока 12 управления на стробирующий вход регистра Q. Выходной сигнал (двоичный код) регистра 9

поступает ня информационный вход ВБ 10, де он переп1 г.Ырпется во внутреннюю память ВЬ 10. Т кпч образом, в память ВБ 10 записывается вся последовательность двоичных кодов, которую по |учают при обработке ЭДС-сигналов Дгя синхронизации

записи поспйловательности двоичных кодов в память ВЬ 10 ЭДС-сигналы с выходов токовых повторителей 1 и 2 поступают на чходы компараторов 13 и 14, где преобоазу- юи.ч е последовательность прямоугольных

ям улм;пв, сдвинутых один относительно другого на ;г /2. Си1 налы с выходов компараторов 13 w 14 поступают на первый и второй входы элемента ИСКЛЮЧАЮ НЕЕ

ИЛИ 15 соответственно где преобразуются в одну последовательность прямоугольных импульсов на частоте . Сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 поступает нг второй вход БИГД 1pi который фоо- Mnr,i ,T HP выходе последовательность прчмгуг тьных импульсов с .плительностыз С г Гг, д° Гг - РГ ) юд ГТ 1 11, и частотой У .)то достигается ген выход 11 подключен к пердо у ахсди БИГД 16. Вое- N eHHoe оэг.толожен /ч; этих импульсо. ее от- ре-с:гв/«-т нулевые, обучениям напряжения рхсд/ ЫУ ЭДС-гигнялов. эл с. выхода ИГ Д 16 пост пает на первый вход 12 управления, где по входному фьр- М11оуется сигнал Запуск АЦП, поступаю ший через п рвь-й оыход блоке 12 у мр5але HI- на гг ртий вхсд АЦП 8 После по входу регистра двоимногс кода блок 12 управления устанавливает на шин е обмена данных флаг готовности данных в регистре 9.

По получении сигнала готовности данных ВБ 10 устанавливает на шине обгона данныхсигчал чтения данных исчитывает(.ч код с выхода регистра через информацион ныи вход После считывания , да В Б 1 устанавливает сигнал оконч СБИТЫЕ i- ния, по которому выход реги л устанга- ливается в нулевое положение и снимаемся флаг готовности данных блока 12 упраеле- ния.

Вычислительный блок 10 работает следующим образом

После одного обооота ротора 1ЬД в памяти ВБ 10 находится N значень- (Амищ , Амакс) } (фиг. 3). Погрешность отработки каждого 1-го шага определяют по формуле

ftA

. у. rtMdKCI r NiHH|

АМЗКС| AMMHI

0)

где А - амплитуда ЭДС на каждом и,, и получают совокупность значений { АХ } . Затем по программе, занесение в память ВБ 1C, статическую погрешность отработки шага ШД определяют по формуле

Да(%)(ДХм«с-1-Д Х„Ин) 100 (2;

Гезультат вычислений выводят на индикаторное устройстао 17

Из слаокупности пар чисел (Амзкс). АмИл, } определяют лХико для выходного сигнала сумматора 7 на участке иэм- неии сигчапа or АМчИ| до

Амакс| + 1 , а Д ХМин| , определяют на уча стче из .°нен/я сигнала о г AMSKCI + 1 до Ами,, f 1 согласно фиг. 3.

Наличие по. ишностк совмещения оси вращения ротора л иси симметрии статора

5 10 15 20

25 30

3540

45

55

ШД приводит к тому, что выходной сигнал сумматора 7 имеет вид, представленный на фиг. 3 В этом случае не представляется возможным определить однозначно постоянную СОСТЯВЛЯЮЩУО всего сигнала и тем самым точно опредепить погрешность отработки шага. Компенсация нессвмещения огей вращения ротора и симметрии статора осуществляется гем, ч го погрешгость отра- шага определяют нз аждом l-м шаге IQ фг .)мул (1), а зчтем о ор уе 2) рассчитывают сглп.ческую 1огрешность отра- бг - и единичного шага ШД

сгн контроля погрезь-) ти так-чв пoRышa Cя за согласования входных цепе й угтоойстьа п о IMOTOK ШД и фильтра- иии основной гярмоники ОДС.

Кыстродей,гвие устройства контроля потешности повивается за счет применения вычислительного б/ ока 0, который по- ЗВОЛЯРТ автоматически обработать N пар кодов чначений амплитуда cm нал з сумматора 7 и вычислить с этическую погрешность отработки шага.

Г- ИГД 16 работает следующим образом.

На один вход БИ1 Д т6 п .гукает сигнс)л от ПИ 11 -lac CTon Г- 1 . э но другой вуид cm на/i на у,;г «астотз следо- вани« ЭДС-сигналов гс 1 кГц. Схема по- строгнз так, то выходной сигнал триггера 19 на выходах О я Q сдсинуг ia один период ГТИ 11 по сргснению с пыходным ct i наяом Q и О триггера 13 1етыре последовательности прямоугольных импульсов поступают нз входь элемента 2-ИЧПИ-ИЕ 20, в котором обрабатываются R cojTeeTerBnn с логикой преобразования v на выходе которого фор мируется последовательность прямоуоль- ных импульсов на частоте Fc 1 кГц с длительностью т - 1/(2-FT).

Вычислительный блок может быть выполнен в виде ми,сроЭВМ с контроллером сопряжения а индикаторное устройство 17 - в дисплея, печатающего устр-MVrga и др.

Пре ельная точность и быстродействие предллгаемого устройства определяются точностью аналсго-иифрового преобразо- РЙНИЧ и 4ft тотоп генератора ТЭКГОРЫХ им- ПУЛЬСОЕ :, спс-риментэльной прозерке ) TppHjHOCTb «/с оойства сост-эзичя 30 /гл с.

о с р мул с изобретения

гройство для сонтро;.я погрешности w .5сжи uudia шзт ьогс двигателя, содержащее два иеремножителя. сумматор, входы /оторого соединены с выходами перемножителей, и индикаторное устройство, о т л i, ч а ю щ е е с я тем, что, с целью повышения тоииосги контроля, в него внедены два токовых повторителя, два фильтра низких частот, аналого-цифровой преобразователь, регистр, генератор тактовых импульсов, два компаратора, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок импульсов готовности данных, блок управления и вычислительный блок, причем входы первого и второго токовых повторителей подключены к ортогональным обмоткам двигателя, выходы - к входам первого и второго фильтров низких частот, выходы которых соответственно соединены с входами первого и второго перемножителей, выход сумматора соединен с первым входом аналого-цифрового преобразователя, выход которого соединен с входом регистра, выходом подключенного к информационному входу вычислительного блока, выход которого соединен с входом индикаторного

устройства, генератор тактовых импульсов соединен с вторым входом аналого-цифрового преобразователя и первым входом блока импульсов готовности данных, второй

вход которого подключен к выходу логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первым и вторым входами соединенного с выходами первого и второго компараторов соответственно, входы которых соответственно соединены с входами фильтров низких частот, выход блока импульсов готовности данных соединен с первым входом блока управления, первый выход которого подключен к третьему вхо/,у

аналого-цифрового преобразователя, второй выход - к стробирующему входу регистра, причем блок управления и вычислительный блок связаны шиной обмена данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи телеизмерений | 1982 |

|

SU1018140A2 |

| Устройство для измерения температуры | 1985 |

|

SU1390515A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| СПОСОБ КОНТРОЛЯ РАБОТЫ ЭЛЕКТРОПРИВОДА НА ОСНОВЕ ДВУХОБМОТОЧНОГО ШАГОВОГО ДВИГАТЕЛЯ, РАБОТАЮЩЕГО В ПОЛНОШАГОВОМ РЕЖИМЕ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2021 |

|

RU2774923C1 |

| Устройство для измерения температуры | 1987 |

|

SU1578511A1 |

| Устройство для ввода информации | 1987 |

|

SU1522189A1 |

| Устройство для автоматизированного управления процессом налива емкостей | 1987 |

|

SU1588710A1 |

| Устройство для измерения температуры | 1984 |

|

SU1281921A1 |

Изобретение относится к электротехнике, а именно к измерению характеристики гибридных шаговых электродвигателей (ШД). Цель изобретения - повышение точности контроля. При принудительном вращении ротора шагового двигателя (ШД) с обмоток статора ЭДС-сигналы поступают через фильтры 3 и 4 низких частот на входы перемножителей 5 и 6, с выходов которых сигналы подаются на входы сумматора 7. выходной сигнал которого в аналоговой форме подается на вход аналого-цифрового преобразователя (АЦП) 8. Последовательность дрг ичных код IB с выхода АЦП 8 через регистр 9 записываемся в память вычислительного блока 10. где осуществляется обработка информации и результат выводится на индикаторное устройство 17. Точность устройства повышается за счет компенсации погрешности совмещения оси вращения оотооа и оси симметрии статора ШД путем вычисления погрешности отработки шага ШД на каждом шаге. 3 ил. Ј XI О ГО ел о ю

/8

А

/9

Фиг 2

| Устройство для измерения модуля сдвига фаз | 1987 |

|

SU1476401A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| кл, G 01 R 25/00 10.0189 | |||

Авторы

Даты

1991-12-30—Публикация

1989-10-16—Подача