Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| ИНФОРМАЦИОННО-ПОИСКОВАЯ СИСТЕМА | 2001 |

|

RU2199778C1 |

| Устройство для управления вентильным преобразователем | 1984 |

|

SU1205243A2 |

| ПАРАЛЛЕЛЬНАЯ СИСТЕМА ИНФОРМАЦИОННОГО ПОИСКА | 2001 |

|

RU2195015C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для определения взаимной корреляционной функции | 1989 |

|

SU1689968A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

Использование: в измерительной технике при анализе формы сигналов. Сущность изобретения: измеритель содержит компаратор 1, формирователи 2,4, 6, 10 коротких импульсов, генератор 3 тактовых импульсов, элемент И-НЕ 5, элемент 7 задержки, блок 8 массива отсчетов, элемент 9 сравнения, блок 11 управления, блок 12 сравнения, блок 13 хранения минимального значения функции несимметричности, блок 14 вычисления. 12 ил.

VI

ю ел

VI ю

Изобретение относится к измерительной технике и может быть использовано при анализе формы сигналов.

Цель изобретения - расширение функциональных возможностей.

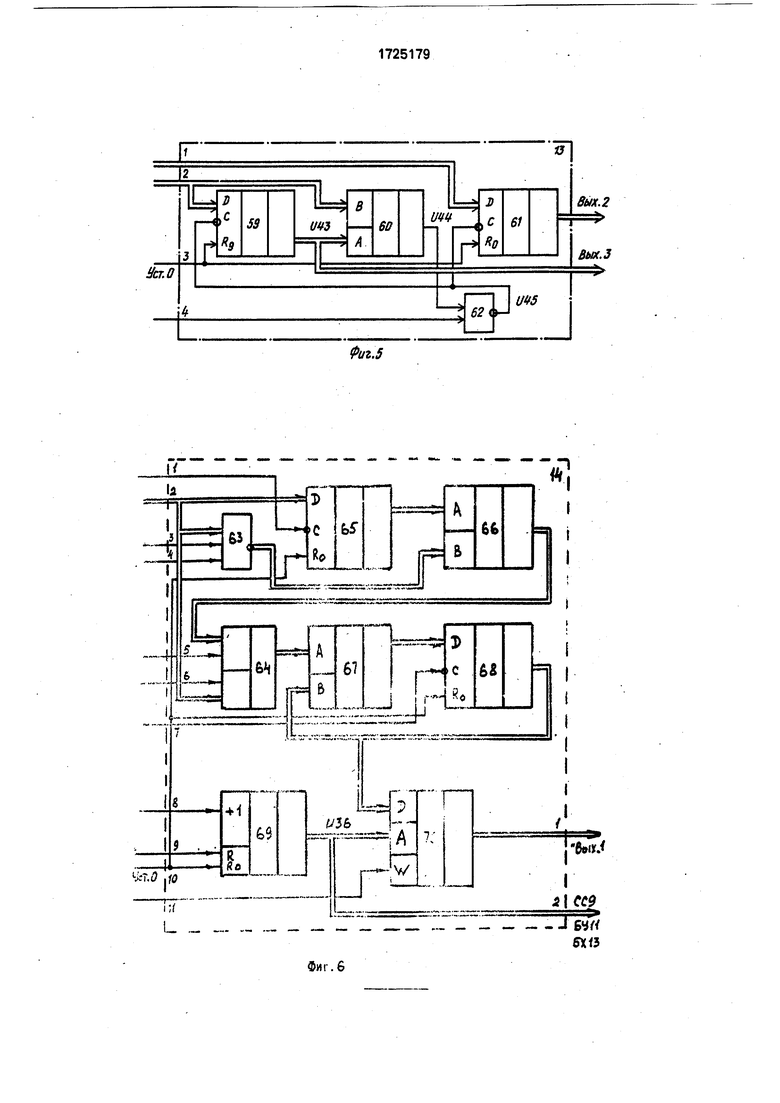

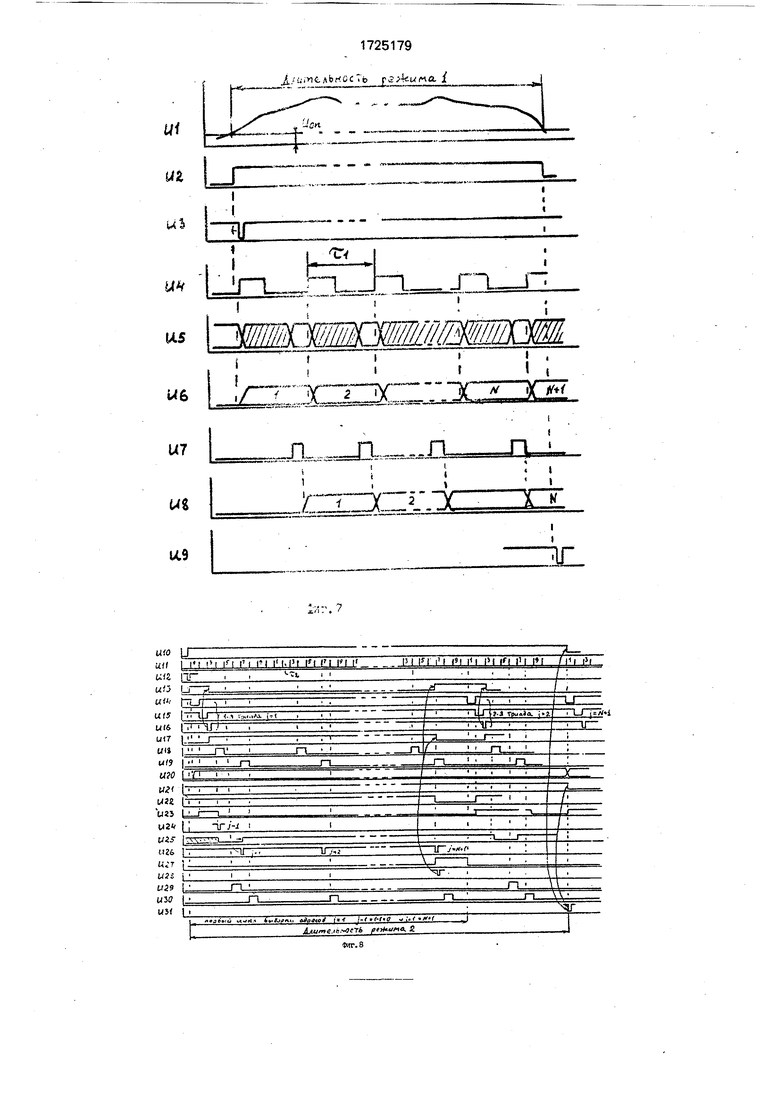

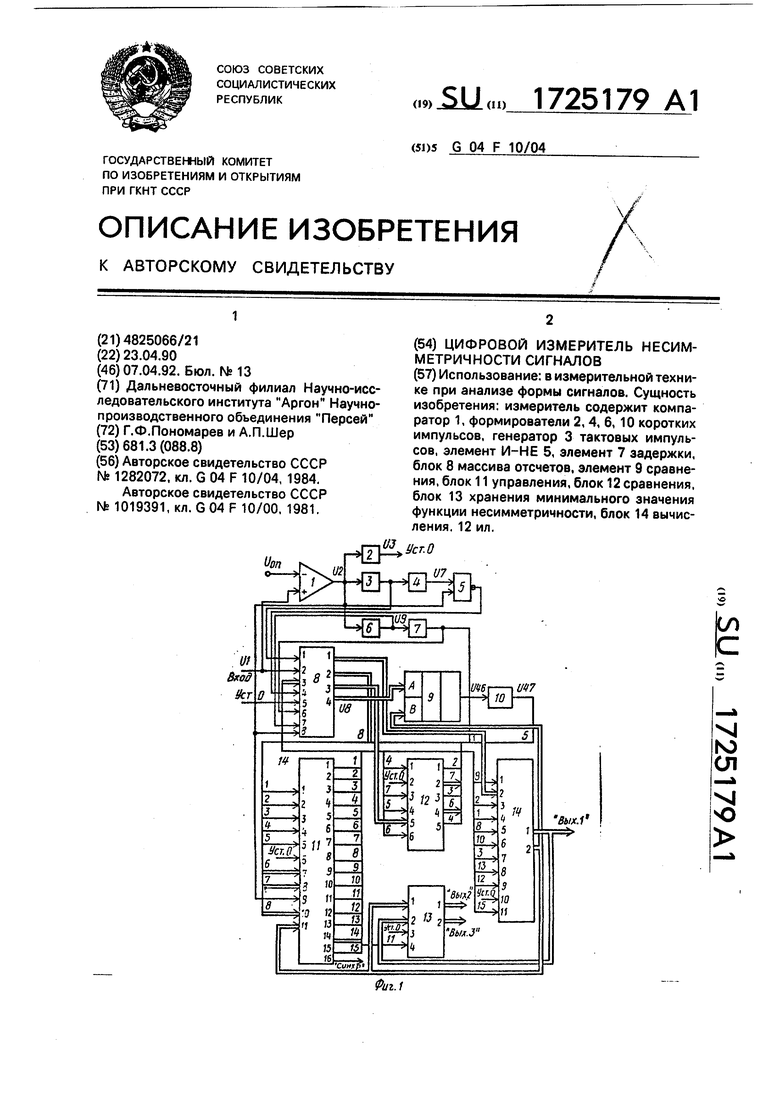

На фиг.1 показана структурная схема цифрового измерителя несимметричности сигналов; на фиг.2-6 - схемы функциональных блоков; на фиг.7-11 - временные диаграммы работы измерителя; на фиг. 12 - примеры функций несимметричности сигналов различной формы.

Цифровой измеритель несимметричности сигналов (фиг.1) содержит компаратор 1, формирователь 2 коротких импульсов (ФКИ), генератор 3 тактовых импульсов (ГТИ), ФКИ 4, элемент И-НЕ 5. ФКИ 6, элемент 7 задержки, блок 8 массива отсчетов, элемент 9 сравнения, ФКИ 10, блок 11 управления, блок 12 сравнения, блок 13 хранения минимального значения функции несимметричности сигнала и блок 14 вычисления значения функции несимметричности. При этом первый вход компаратора 1 соединен с шиной опорного напряжения Don, второй вход - с шиной Вход и вторым входом блока 8, а выход компаратора 1 соединен с входами ФКИ 2 и 6, ГТИ 3, вторым входом элемента И-НЕ 5, восьмым входом блока 8 и девятым входом блока 11. Выход ФКИ 2 соединен с шиной Уст.О, по которой осуществляется установка измерителя в исходное состояние, выход ГТИ 3 соединен с входом ФКИ 4 и первым входом блока 8, выход второго ФКИ 4 соединен с первым входом элемента И-НЕ 5, выход которого соединен с четвертым входом блока 8, выход ФКИ 6 соединен с входом элемента 7 задержки и седьмым входом блока 8, выход элемента 7 задержки соединен с первым входом блока 11 и шестым входом блока 8, пятый вход блока 8 соединен с шиной Уст.О, первый выход блока 8 - с вторым входом блока 14, второй выход блока 8 - с десятым входом блока 11, третий выход блока 8 - с пятым входом блока 12, четвертый выход блока 8 - с А-входом элемента 9 сравнения. Выход элемента 9 сравнения соединен с входом четвертого ФКИ 10, выход которого соединен с пятым входом блока 11. Первый выход блока 11 соединен с четвертым входом блока 14, второй выход блока 11 - с третьим входом блока 14, третий выход блока 11 - с седьмым входом блока 14, четвертый выход блока 11 - с первым входом блока 12, пятый выход блока 11 - с четвертым входом блока 12, шестой выход блока 11 - с шестым входом блока 12, седьмой выход блока 11 - с третьим входом блока 12, восьмой выход блока 11 - с пятым

входом блока 14, девятый выход блока 11 - с первым входом блока 14, десятый выход блока 11 - с шестым входом блока 14, одиннадцатый выход блока 11 - с четвертым вхо- дом блока 13, двенадцатый выход блока 11

-с девятым входом блока 14, тринадцатый выход блока 11 - с восьмым входом блока 14, четырнадцатый выход блока 11 - с третьим входом блока 8, пятнадцатый выход бло0 ка 11 - с одиннадцатым входом блока 14, шестой вход блока 11 - с шиной Уст.О. Первый выход блока 12 соединен с вторым входом блока 11, второй выход блока 12 - с восьмым входом блока 11, третий выход

5 блока 12 - с третьим входом блока 11, четвертый выход блока 12 - с седьмым входом блока 11, пятый выход блока 12 - с четвертым входом блока 11, второй вход блока 12

-с шиной Уст.О. Первый выход блока 13 0 соединен с информационной шиной

Вых.2, второй выход блока 13 - с информационной шиной Вых.З, а третий вход блока 13 - с шиной Уст.О. Первый выход блока 14 соединен с вторым входом блока

5 13 и информационной шиной Вых,1, второй выход блока 14 - с В-входом элемента 9 сравнения, с первым входом блока 13 и одиннадцатым входом блока 11, а десятый вход блока 14 - с шиной Уст.О, шестнадца0 тый выход блока 11 - с шиной Синхронизация.

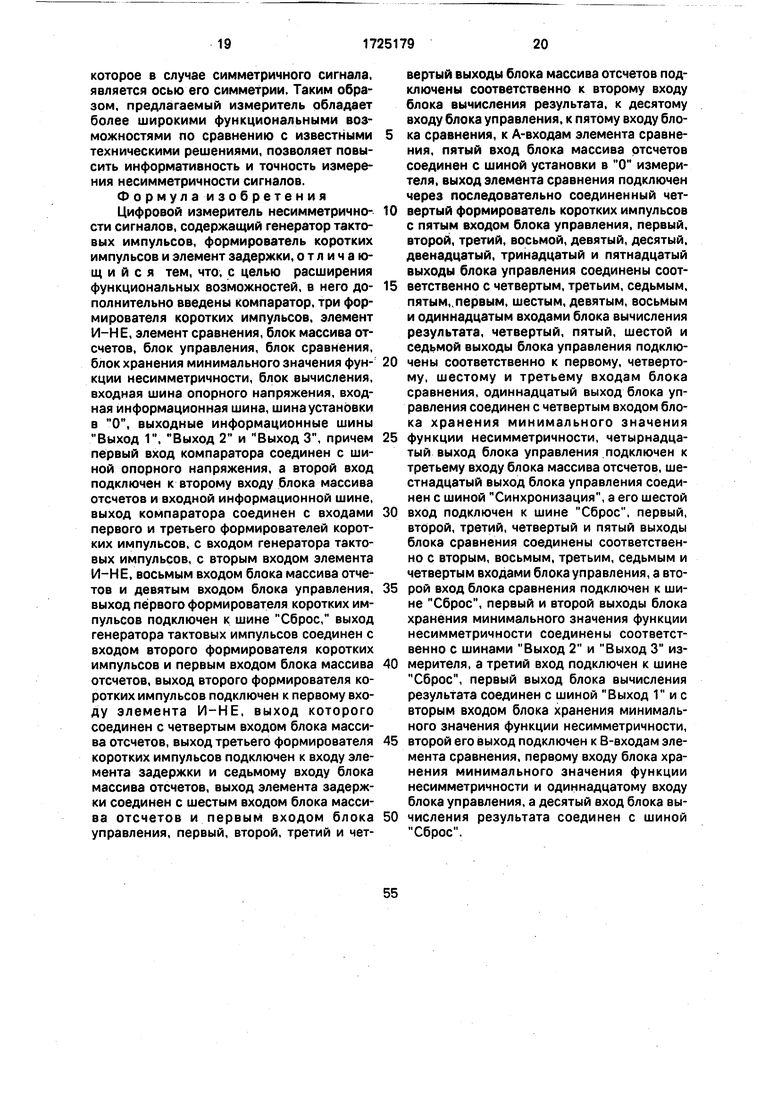

Блок управления (фиг.2) содержит RS- триггеры 15-20, элемент ИЛИ 21, ФКИ 22, ГТИ 23, элемент И 24, распределитель 25

5 импульсов, элементы И-НЕ 26-28, элементы И 29 и 30, ФКИ 31 и 32, элемент И 33, ФКИ 34, элемент И-НЕ 35, элемент ИЛИ 36, элемент И 37, распределитель 38 импульсов, элемент НЕ 39, ГТИ 40, распределитель

0 41 импульсов, группу 42 элементов 4-ЗИ- 4ИЛИ, элемент И 43, элемент 3-2И-ЗИЛИ 44 и ФКИ 45.

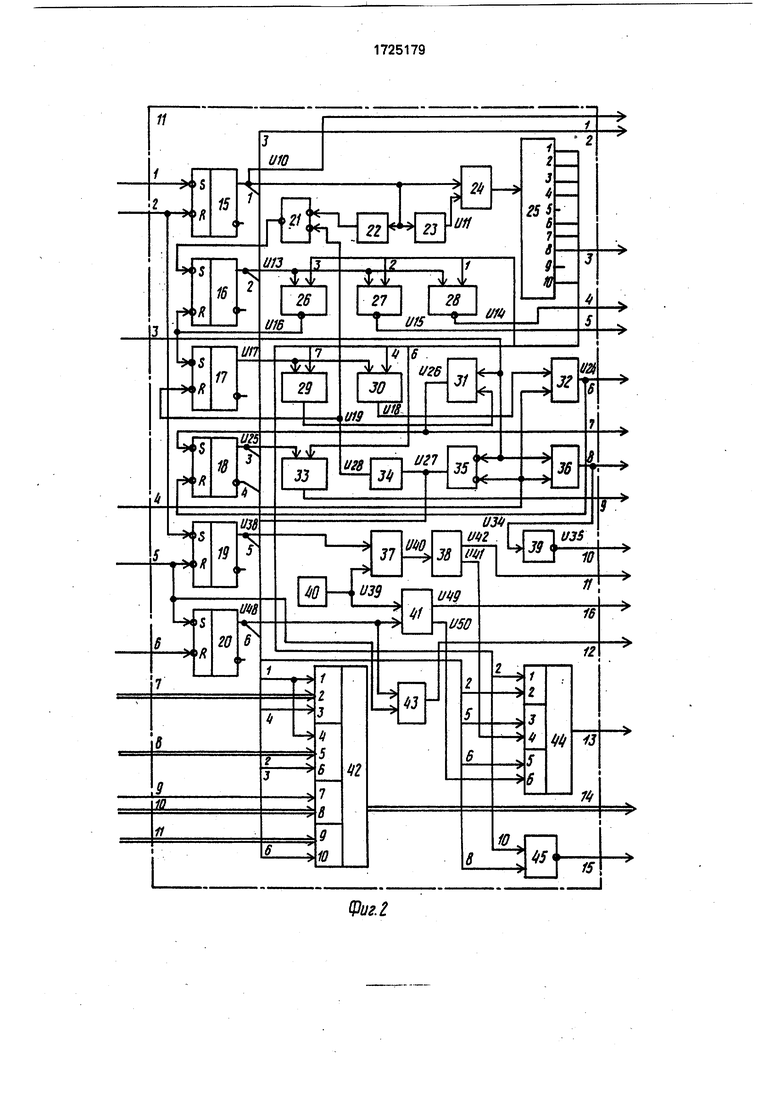

Блок 12 сравнения (фиг.З) содержит двоичные счетчики 46-48, элементы 49-51 срав5 нения и ФКИ 52.

Блок 8 массива отсчетов (фиг.4) содержит аналоговый коммутатор 53, аналого- цифровой преобразователь (АЦП) 54, оперативное запоминающее устройство (ОЗУ) 55, двоичные счетчики 56 и 57 и ре0 гистр 58 памяти.

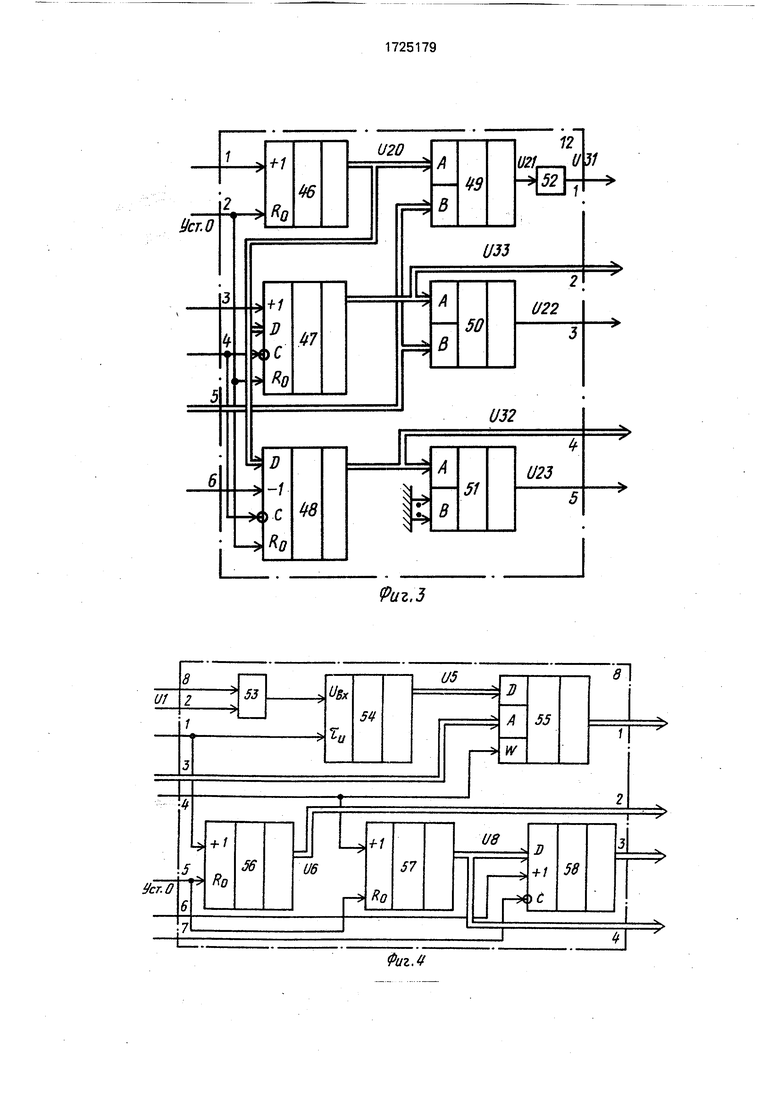

Блок 13 хранения минимального значения функции несимметричности (фиг.5) содержит регистр 59 памяти, элемент 60 сравнения, регистр 61 памяти и элемент И

5 62.

Блок 14 вычисления значения функции несимметричности сигналов (фиг.6) содержит группу 63 элементов ЗИ-НЕ, группу 64 элементов 2-2И-2ИЛИ, регистр 65 памяти,

вычитатель 66, сумматор 67, регистр 68 памяти, счетчик 69 и ОЗУ 70.

Блок 8 массива отсчетов преобразует аналоговый сигнал в цифровую форму, хранит массив отсчетов в ОЗУ и хранит количество отсчетов в регистре памяти.

Блок 11 управления вырабатывает управляющие сигналы, обеспечивающие функционирование цифрового измерителя в различных режимах работы.

Блок 12 сравнения вырабатывает импульсы прерывания функционирования измерителя по различным критериям. Блок 13. хранения минимального значения функции несимметричности предназначен для определения минимального значения функции несимметричности при последовательном поступлении потока информации, а также определения адреса ячейки, в которую записано минимальное значение функции. Блок 14 вычисления осуществляет операции суммирования и вычитания над операндами отсчетов в соответствии с принятым алгоритмом, а также хранит значения вычисленных функций несимметричности.

В исходном состоянии после подачи напряжения питания триггеры, счетчики, регистры памяти, ОЗУ и ГТИ могут находиться в произвольном состоянии. Сигнал исходного состояния Уст.О формируется на выходе формирователя 2 только в случае поступления сигнала на шину Вход (фиг.1). Сигнал Уст.О поступает на входы блоков 8, 11-14. Триггеры 15-20 блока 11 (фиг.2) устанавливаются в нулевое состояние. Элементы 22- 24, 26-30,33, 37, 41, 43 и 45 находятся в закрытом состоянии. Элемент 42 находится в закрытом состоянии по входам 1,4, 6 и 10. Элемент 44 находится в закрытом состоянии по входам 2,3 и 5. Счетчики 46-48 блока 12 (фиг.З) установлены в нулевое состояние. На А-входах элемента 49 сравнения и D-вхо- дах счетчиков 47 и 48 присутствуют нулевые потенциалы со счетчика 46. На А-входах элемента 50 сравнения присутствуют нулевые потенциалы с входов счетчика 47. На А-входах элемента 51 сравнения присутствуют нулевые потенциалы с выхода счетчика 48. На В-входах элементов 49 и 50 сравнения присутствуют нулевые потенциалы с выходов регистра 58 памяти. На В-входах элемента 51 сравнения установлен нулевой потенциал монтажным путем. На входах элементов 49-51 сравнения устанавливается потенциал логического нуля,

Счетчики 56 и 57 блока 8 (фиг.4) установлены в исходное состояние, регистр 58 памяти - в произвольном состоянии, на А-входах ОЗУ 55 выбран адрес нулевой ячейки. На выходах АЦП 54 установлен произвольный двоичный код. В исходном состоянии на выходах регистра 59 памяти блока 13 (фиг.5) установлены потенциалы логической единицы (двоичный код 1...1), а на выходах регистра 61 памяти - потенциалы логического нуля. На А-входах элемента 60 сравнения установлены потенциалы логической единицы, на В-входах элемента 60 сравнения и D-входах регистра 59 памяти 0 произвольные потенциалы. На D-входах регистра 61 памяти установлены произвольные потенциалы с выходов нулевой ячейки ОЗУ 70 блока 14. Регистры 65 и 68 памяти блока 14 (фиг.6) и счетчик 69 установлены в

5 исходное состояние, на их входах присутствуют потенциалы логического нуля. На А- входах вычитателя 66 и накапливающего сумматора 67 присутствуют потенциалы логического нуля.

0 На В-входах накапливающего сумматора 67 и D-входах ОЗУ 70 присутствуют по- тенциалы логического нуля. В ОЗУ 70 выбрана нулевая ячейка памяти.

Измеритель имеет четыре режима рабо5 ты: режим I - формирование в запись массива отсчетов анализируемого сигнала; режим II - формирование функции несимметричности сигнала; режим III - определение минимального значения функции

0 несимметричности и его временного положения относительно начала анализируемого сигнала; режим IV - формирование информации на индикаторном устройстве. Последовательность режимов работы

5 измерителя жестко закреплена его логикой и не может быть изменена.

Измеритель работает следующим образом.

Режим I. Формирование и запись мас0 сива отсчетов анализируемого сигнала осуществляется следующим образом.

Анализируемый сигнал по шине Вход поступает на компаратора 1 (фиг.7). На вход - компаратора поступает опорное

5 напряжение Uon (фиг.7). Если величина входного сигнала превышает величину порога срабатывания, то на выходе компаратора устанавливается уровень логической единцы U2, в противном случае - потенциал

0 логического нуля. На выходе компаратора 1 формируется прямоугольный положительный импульс U2, длительность которого соответствует длительности анализируемого сигнала. Прямоугольный импульс U2 с выхо5 да компаратора 1 поступает на входы элементов 2,3,5 и 6 на 8-й вход блока 8 и на 9-й вход блока 11. ФКИ 2 вырабатывает короткий отрицательный импульс U3, временное положение которого соответствует переднему фронту положительного импульса U2

с выхода компаратора 1 (фиг,7). Данный импульс используется в качестве сигнала Уст.О, устанавливающего элементы устройства в исходное состояние. Поступивший положительный импульс U2 на вход ГТИ 3 обеспечивает условия генерации прямоугольных импульсов U4. Начальная фаза первого импульса U4 с выхода ГТИ 3 жестко привязана к переднему фронту положительного импульса U2 и переходит из состояния логического нуля в состояние логической единицы. С выхода ГТИ 3 сигналы U4 поступают на вход ФКИ 4 и через 1-й вход блока 8 на Гп-вход АЦП 54 и вход +1 счетчика 56. АЦП 54 преобразует аналоговый сигнал в двоичный цифровой код. Работой АЦП 54 управляет тактовый сигнал, поступающий на Гп-вход. Выборка осуществляется по переднему фронту тактового импульса. Кодирование производится с подачей заднего фронта тактового импульса. Результат, полученный во время кодирования, на выходной регистр выдается после окончания переходных процессов.

Для записи цифрового значения отсчета в ячейку памяти ОЗУ 55 блока 8 вырабатываются адрес и импульс записи. Адрес для ОЗУ 55 вырабатывается счетчиком 56. В исходном состоянии в счетчике записан код 0...0. Состояние U6 счетчика 56 (фиг.7) последовательно изменяется от 1 до N при переходе импульса U4 из состояния 0-1 (фиг.7). С выхода счетчика 56 код адреса поступает на 8-е входы группы 42 элементов 4-ЗИ-4ИЛИ блока 11. На 7-е входы этой же группы поступает разрешающий потенциал с выхода компаратора 1. Двоичный код с выходов группы 42 элементов поступает на адресные входы ОЗУ 55, выбирая соответствующую ячейку. Импульс записи U7 вырабатывается формирователем 4, который осуществляет задержку импульса записи относительно заднего фронта импульса U4 с ГТИ 3 на время преобразования и установления переходных процессов (фиг.7). С выхода ФКИ 4 импульсы U7 поступают на вход элемента И-НЕ 5. На другой вход элемента И-НЕ 5 поступает разрешающий потенциал U2 с выхода компаратора 1. С выхода элемента И-НЕ 5 инвертированный импульс поступает на вход записи W ОЗУ 55 блока 8.

Отсчеты входного сигнала записываются последовательно в память ОЗУ 55 по адресам 1, №. Количество отсчетов соответствует целому числу (t/ti), где t - длительность анализируемого сигнала; П- период тактовых импульсов ГТИ 3. Количество отсчетов не должно превышать объем памяти ОЗУ 55. Кроме того, импульс

отрицательной полярности с выхода элемента И-НЕ 5 поступает на вход +1 счетчика 57 и последовательно устанавливает его в состояние от 1 до N U8 (фиг.7).

Процесс формирования и записи массива отсчетов оканчивается, когда уровень анализируемого сигнала будет меньше порога срабатывания. При этом на выходе компаратора 1 устанавливается потенциал

логического нуля U2 (фиг.7). Формирователь 6 вырабатывает импульс U9 отрицательной полярности, который поступает на С-вход регистра 58 памяти блока 8 и перепадом 1-0 осуществляется перезапись информации по D-входам регистра 58 с выходов счетчика 57. На вход +1 регистра 58 памяти поступает задержанный элементом 7 импульс отрицательной полярности U9 и увеличивает содержимое регистра 58 памяти

на единицу.

Таким образом, по окончании режима записи в ячейках 1,,..,N памяти ОЗУ 55 хранятся отсчеты анализируемого сигнала, в счетчике 57 хранится двоичный код десятичного числа N, а в регистре 58 памяти - двоичный код десятичного числа N+1. Процесс формирования массива отсчетов окончен.

Работу остальных режимов обеспечивают блоки управления 11 и сравнения 12.

Алгоритм формирования функции несимметричности сигнала имеет следующий вид.

Для каждого номера отсчета je

{1,2N} имеем слева J-1 и справа N-J отсчетов сигнала. При этом возможны три ситуации (N - число отсчетов), когда j-1 N-j, тогда 2j N + 1; J - номер отсчета; когда , тогда i - текущее значение

отсчета; когда , тогда .

В первом случае j-тое значение функции несимметричности можно вычислить как

sj Ё11 fi

i 1

f2J-1 I +2 fi

во втором случае - посредством выражения

Sj-5)1 If|-f2j-i I, i 1

в третьем случае - с использованием 55 формулы

J-1

2j-N

fi-f2J-l I +

2j-JU-1

fl.

s 1

Эквивалентная формула для первого случая имеет вид

Hj-i-fj+1 I + 2 fi, (1)

i 1 для второго случая

Sj 21|fj-i-fj + il (2) 1°

i 1

и для третьего случая

N-j2J-N-1

lfj-1-fj+,l+ 2 f,.

Из зависимостей (1)-(3) функции несимметричности следует, что для симметрично- го сигнала существует такой номер J, для которого и для всех других номеров . Другими словами, для сигнала, симметричного относительно некоторого j-ro отсчета (или, что то же самое, относительно j-ro момента времени), выполняется

гтшт Sj 0 ,

И.и

тогда как для несимметричности сигнала

mjn Sj О,

H.N следовательно, значение mjn Sj может слуJ-1.N

жить оценкой степени несимметричности сигнала, чем ближе mjn Sj к нулю, тем более

JM.N

сигнал симметричен или тем менее он несимметричен.

Возможен только один случай, при кото- ром

rmn Sj 0, j,N

когда в выражении (2) при нечетном числе N отсчетов все модули разностей |fj-i- fj+il отсчетов сигнала, равноотстоящих от j-ro отсчета по разные стороны от негр, обращаются в нуль. При этом достигается в случае, когда для j(N+1)/2.

Приведенные формулы (1) и (3) допускают еще две возможности сигналу иметь ось симметрии в некоторый j-й момент времени: ерли часть отсчетов сигнала до некоторого номера 2j-N-1 в (3) или начиная с некоторо- го номера 2 j в (1) имеет нулевое значение. Тогда при выполнении условий равенства нулю левых сумм в (1) и (3) возможно . Однако эти два случая при выбранном в

5

1°

15

2025

30

35

40

45 50

55

устройстве способе формирования массива отсчетов сигнала по условию, превышающему некоторый наперед заданный не равный нулю порог, исключаются.

Алгоритм работы реализуется следующим образом.

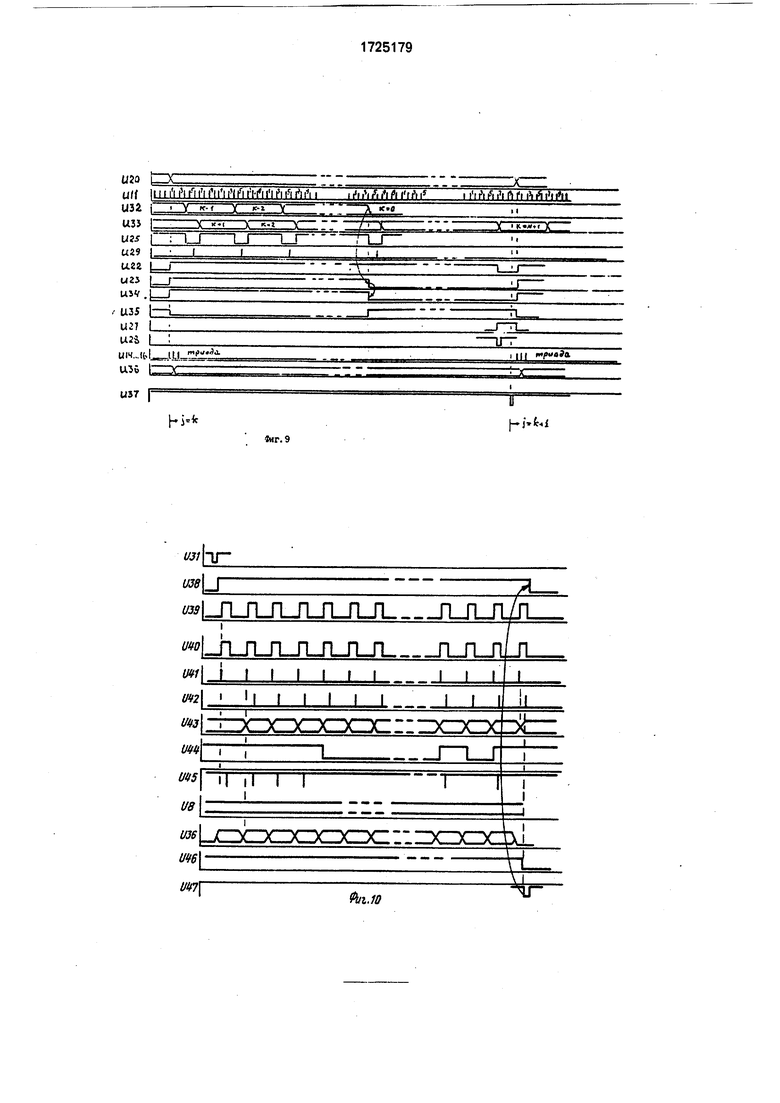

Импульс отрицательной полярности U9, задержанный элементом 7, поступает на S- вход триггера 15 блока 11 и устанавливает его в единичное состояние. Триггер 15 находится в единичном состоянии U10 (фиг.8) на время формирования функции несимметричности анализируемого сигнала. На Q-вы- ходе триггера 15 устанавливается потенциал U10 логической единицы (фиг.8), который поступает на входы блоков 22-24, разрешая формирование импульсов. На выходе ПГИ 23 формируются прямоугольные импульсы U11, причем фаза первого импульса ГТИ 23 привязана к переднему фронту положительного импульса U10 (фиг.8). ГТИ 23 вырабатывает последовательность положительных импульсов с периодом повторения та, которые поступают на вход элемента И 24 и далее на вход распределителя 25 импульсов. Последний вырабатывает на выходах 1-10 импульсы положительной полярности длительностью Т2, сдвинутые друг относительно друга. Эти импульсы поступают на входы соответствующих элементов и формируют управляющие сигналы измерителя.

Кроме того, формирователь 22 по переднему фронту положительного импульса с Q-выхода триггера 15 формирует короткий отрицательный импульс, который поступает на вход элемента ИЛИ 21. С выхода элемента 21 импульс U12 поступает на S-вход триггера 16 и устанавливает его в единичное состояние. Он находится в единичной состоянии на время формирования триады. На Q-выходе триггера 16 устанавливается потенциал U13 логической единицы. Разрешающий потенциал U13 поступает на входы элементов 26-28. На другие входы элементов 26-28 поступают соответственно 1-й, 2- й и 3-й положительные импульсы с выхода распределителя. На выходах элементов 26- 28 формируются импульсы 1Л4-и16отрица- тельной полярности первой триады (), Импульс U14 с выхода элемента 28 блока 11 (фиг.8) поступает на вход +1 счетчика 46, осуществляющего выборку текущего значения j-ro отсчета анализируемого сигнала. К началу режима II на выходах счетчика 46 установлен двоичный код. 0...0 U20. С приходом импульса U14 его состояние изменяется в пределах f,N. Двоичный код U20 с выходов счетчика 46 поступает на А-входы

элемента 49 сравнения. На В-входы элемента 49 сравнения поступает двоичный код числа N+1 с выходов регистра 58 памяти. Коды на А- и В-входах сравнения не равны. На А В-выходе элемента 49 сравнения установится потенциал логической единицы U21. Двоичный код j-ro отсчета с выходов счетчика 46 поступает на D-входы счетчиков

47и 48. Импульс U15 с выхода элемента 27 поступает на С-входы счетчиков 47 и 48 блока 12 и осуществляет перезапись текущего значения j-ro отсчета в счетчики 47 и 48. К началу режима II в счетчиках записан двоичный код 0...0. В исходном состоянии на А- входе элемента 50 сравнения установлен двоичный код нуля, а на В-входе - двоичный код числа N+1. Коды не равны, тогда на А В-выходе элемента 50 сравнения установится потенциал логической единицы U22. К началу режима II на А-входе элемента 51 сравнения установлен двоичный код нуля, а на В-входе - монтажный нуль. Коды равны, тогда на А В-выходе элемента 51 сравнения установится потенциал логического нуля U23 (фиг.8).

Второй импульс U15 с выхода элемента 27 первой триады переписывает двоичный код 0...1 со счетчика 46 в счетчики 47 и 48. На А В-выходе элемента 51 сравнения установится потенциал логической единицы U23 (фиг.8).

Третий импульс U16 первой триады с выхода элемента 26 поступает на R-вход триггера 16 и на S-вход триггера 17. На Q-выходе триггера 16 устанавливается потенциал логического нуля U13, который запрещает прохождение 1-му, 2-му и 3-му импульсам с выходов распределителя 25.

Триггер 17 устанавливается в единичное состояние, а на Q-выходе - потенциал логической единицы U17. Разрешающий потенциал U17 поступает на входы элементов 29 и 30. На вторые входы поступают 4-й и 7-й импульсы с распределителя 25. С выхода элемента 30 импульс U18 положительной полярности поступает на вход ФКИ 32, формирующего импульс отрицательной полярности U24, который поступает на R-вход триггера 18 и устанавливает его в нулевое состояние U25. К началу режима II состояние триггера 18 произвольное. Кроме того, импульс U24 поступает на вход 1 счетчика

48блока 12 и осуществляет операцию де- крементирования содержимого счетчика. На нем последовательно устанавливаются

коды чисел J-1, j-20. Так как на счетчике

48 установлен код числа J-1, то с приходом первого импульса U24 на нем установится код числа . При равенстве кодов на А- и В-входах элемента 51 сравнения и на его

А В-выходе установится потенциал логического нуля U23 и запретит формирование импульсов U24 ФКИ 32 последующими импульсами U18.

С выхода элемента 29 импульсы U19

положительной полярности поступают на вход ФКИ 31, формирующего импульс отрицательной полярности U26, который поступает на S-вход триггера 18 и устанавливает

его в единичное состояние U25. Кроме того, импульс U26 поступает на вход +1 счетчика 47 блока 12 и осуществляет операцию инкрементирования содержимого. На нем последовательно устанавливаются коды чисел J+1J+2N+1. Формирование импульса

U26 на выходе ФКИ 31 продолжается до тех пор, пока на счетчике 47 не установится двоичный код числа N+1. В этом случае на А- и В-входах элемента 50 сравнения двоичные коды равны. На А--В-выходе устанавливается потенциал логического нуля U22. Потенциалы логического нуля U21 и U22 с выходов элементов 50 и 51 сравнения поступают на вход элемента И-НЕ 35 и формируют положительный перепад U27 (фиг.8). На выходе ФКИ 34 формируется отрицательный импульс U28, который поступает на R- вход триггера 17 и через элемент ИЛИ 21 на S-вход триггера 16. На Q-выходе триггера 17

устанавливается потенциал логического нуля U13 и запрещает прохождение 4-му и 7-му импульсам с распределителя 25. Кроме того, импульс U28 устанавливает триггер 16 в единичное состояние. На его Q-выходе

формируется разрешающий потенциал U13, поступающий на входы элементов 26-28 и разрешающий прохождение 1-го, 2-го и 3-го импульсов с выходов распределителя 25. Формируется вторая триада, j-2 из импульсов U14, U15 и U16. Цикл выборки адресов

-1,Ои J+1, j+2N+1 для повторяется.

Таким образом, для каждого j-ro отсчета счетчик 48 блока 12 последовательно формирует двоичные коды чисел j-1, j-20, а

счетчик 47 - двоичные коды чисел j+1, j+2

N+1.

В зависимости от числа N отсчетов анализируемого сигнала и номера j текущего отсчета количество отсчетов слева и справа

от j может быть различным. Это условие фиксируется с помощью элемента ИЛИ 36 блока 11 .При поступлении на любой из входов элемента 36 потенциалов логического нуля U22 и U23 с элементов 50 и 51 сравнения на выходе элемента 36 установится потенциал логического нуля U34, а на выходе элемента 39 - потенциал логической единицы U35 (фиг.9).

Перебор текущих отсчетов j оканчивается тогда, когда на счетчике 46 блока 12 установится двоичный код числа N+1. С выходов счетчика 46 двоичный код поступает на А- входы элемента 49 сравнения, а на В-входы поступает двоичный код числа N+1 с регистра 58 памяти блока 8. При равенстве кодов на ArB-выходе элемента 49 сравнения устанавливается потенциал логического нуля U21 (фиг.8), который поступает на вход ФКИ 52. Последний вырабатывает импульс U31 отрицательной полярности, поступающий на R-вход триггера 15 и устанавливающий его в нулевое состояние U10 (фиг.8). Запрещающий потенциал U10 поступает на входы ГТИ 23 и элемента И 24, прекращается выдача импульсов с выхода распределителя 25.

Режим II. Формирование функции несимметричности сигнала производится следующим образом.

Покажем это на примере вычисления j-ro отсчета функции. Пусть в счетчике 46 блока 12 записан двоичный код U20 номера j-ro отсчета анализируемого сигнала (фиг.9). В счетчике 48 последовательно устанавливаются коды чисел U32 j-1, j-20 (фиг.9).

Формирование этих импульсов рассмотрено. В счетчике 47 устанавливаются коды чисел U33 j+1, j+2 N+1 (фиг.9). Вначале

выбирается двоичное число, находящееся в памяти ОЗУ 55 по адресу j-1, а затем - по адресу j+1. Двоичные коды U32 и U33 (фиг.9) с выходов счетчиков 47 и 48 блока 12 поступают на 2-й и 5-й входы группы 42 элементов 4-ЗИ-4ИЛИ. На 1-й и 4-й входы этой же группы поступает разрешающий потенциал U10 (фиг. 10) с Q-выхода триггера 15, который находится в единичном состоянии на время вычисления функции несимметричности. На 3-й вход поступает сигнал с Q-выхода триггера 18, а на 6-й вход - сигнал U25 с Q-выхода триггера 18. Триггер 18 осуществляет временную селекцию кодов, поступающих со счетчиков 47 и 48. Когда на Q-выходе триггера 18 присутствует потенциал логической единицы, то на выход группы 42 элементов проходят адресные коды со

счетчика 48 (j-1, j-20), а когда на Q-выходе

триггера 18 присутствует потенциал логической единицы U25, то на выход этой же группы проходят адресные коды со счетчика

47 0+1. j+2N+1). С выходов группы 42

элементов адресные коды поступают на А- входы ОЗУ 55 блока 8 и осуществляют выбор информации из ячейки памяти ОЗУ 55.

Таким образом, последовательно осуществляется формирование пар ячеек ОЗУ 55 с адресами j-1 nj+1, j-2 и j+2, и т.д.

Операцию вычитания |fj-j - fj-n (производят блоки 65 и 66 блока 14. Двоичный код (j-ij-й ячейки памяти с выходов ОЗУ 55 поступает на информационные D-входы регистра 65 памяти блока 14. Перепадом 0-1 импульса U29 (фиг.8) с выхода элемента 33, временное положение которого соответствует шестому импульсу распределителя 25, осуществляется перезапись двоичного кода по адресу j-i с выхода ОЗУ 55 в регистр 65 памяти. С выхода регистра 65 двоичный код fj-i поступает на А-входы вычитателя 66. За0 тем выбирается двоичный код (j+Q-й ячейки памяти ОЗУ 55. Двоичный код fj-н с выходов ОЗУ 55 поступает на первые входы группы 63 элементов ЗИ-НЕ. На вторые входы группы 63 поступает разрешающий потенциал

5 И25 с Q-выхода триггера 18, а на третьи входы группы 63 - разрешающий потенциал U10 с Q-выхода триггера 15. Двоичный код инвертируется и подается на В-вход вычитателя 66. На выходе вычитателя 66 получаем

0 результат вычитания в модифицированном обратном коде модуля разности значения отсчетов сигнала.

С выхода вычитателя 66 двоичный код поступает на первые входы группы 64 эле5 ментов 2-2И-2ИЛИ. Блоки 64. 67 и 68 в совокупности представляют накапливающий сумматор. На вторые входы группы 64 элементов поступает разрешающий потенциал LJ34 с выхода элемента 36. Двоичный

0 код с выходов вычитателя 66 через группу 64 поступает на А-входы сумматора 67. На В- входы сумматора 67 подается двоичный код с выходов регистра 68 памяти (к началу режима II в регистре 68 был установлен двоич5 ный код 0...0). На выходе сумматора 67 устанавливается двоичный код суммы чисел, поступающих на А- и В-входы. Восьмой импульс распределителя 25 поступает на С- вход регистра 68 и осуществляет переза0 пись по D-входам содержимого сумматора 67 в регистр 68 памяти. Перезапись производится при переходе U30 (фиг.8) с 0-1 восьмого импульса распределителя 25. Операция вычитания и суммирования

5 2) Ifj-rfj-H I производится до тех пор, пока на счетчике 47 не установится двоичный код числа N+1 или на счетчике 48 код нуля. Следует заметить, что отсчеты записаны по адресам T7N, а операции вычитаниями

0 суммирования выполняются по адресам О, N+1. Изменение пределов выборки адресов до О, N+1 вызваны тем, что операции вычитания и суммирования выполняются шестым и восьмым импульсами распределителя

5 25, а условия окончания формирования функции несимметричности - первым и вторым импульсами распределителя 25. Поэтому пределы изменения выборки адресов справа и слева от j-ro адреса увеличиваются на единицу.

Условие, когда на счетчике 47 установится код числа N+1 или на счетчике 48 код числа 0, фиксируется элементом ИЛИ 36. Потенциал U22 поступает на один из входов элемента ИЛИ 36, а потенциал U23 - на другой вход этого элемента. Когда потенциалы U22 и U23 соответствуют логической единице, т.е. текущие коды на счетчиках 47 и 48 не равны соответственно N+1 и 0, то на выходе элемента ИЛИ 36 устанавливается потенциал логической единицы U34. Когда потенциал U22 или U23 равен логическому нулю, то на выходе элемента ИЛИ 36 также устанавливается потенциал логического нуля.

Разрешающий потенциал U34 (фиг.9) с выхода элемента 36 поступает на второй вход группы 64 элементов, а запрещающий потенциал U35 (инверсный сигнал U34) с выхода элемента 39 поступает на третий вход группы 64 элементов. Потенциал U34 разрешает прохождение двоичных кодов с выходов вычитателя 66. Сумматор осуществляет операцию суммирования модулей разности 2, lfj-i fj+i I- При поступлении запрещающего потенциала U34 и разрешаю-; щего потенциала U35 двоичный код отсчетов анализируемого сигнала с выходов ОЗУ 55 блока 8 поступает на четвертые входы группы 64 элементов. Запрещается прохождение информации с выхода вычитателя 66 и разрешается прохождение информации с выходов ОЗУ 55 на А-входы накапливающего сумматора. Дальше производится только суммирование отсчетов сигнала 2 ft до тех пор,пока не окончится формирование значения Sj функции несимметричности, т.е. пока на счетчике 46 блока 12 не установится двоичный код следующего номера отсчета . Этот момент фиксируется элементом И-НЕ 35. На его входы поступают потенциалы U22 и U23. Когда на их входах установятся одновременно потенциалы логического нуля (фиг.9), то на выходе установится потенциал логической единицы U27. Этот сигнал поступает на вход ФКИ 34 и вырабатывает импульс U28 (фиг.8).

Запись значения Sj функции несимметричности осуществляется в ОЗУ 70. Выбор адресов ячеек памяти ОЗУ 70 производится с помощью счетчика 69. В исходном состоянии на выходах счетчика 69 записан двоичный код 0...0. Изменение состояния реализуется импульсами, поступающими на вход +Г счетчика 69 с элемента 3-2И- ЗИЛИ 44. В режиме формирования функции несимметричности на второй вход элемента 44 поступает разрешающий потенциал с 0- выхода триггера 16. На первый вход элемента 44 поступает второй импульс с выхода

распределителя 25 и проходит на вход +1 , счетчика 69. На выходах счетчика 69 уста- навливаются двоичные коды чисел . Импульс записи формируется после

вычисления значения Sj функции несимметричности с помощью элемента И-НЕ35. На один вход поступает разрешающий потенциал U27 с выхода элемента 35 (фиг.9), на другой вход - десятый импульс с выхода

0 распределителя 25. Импульс записи U37 поступает на W-вход ОЗУ 70 и по выбранному адресу записывает двоичный код с выхода накапливающего сумматора.Счетчик 69 производит последовательно запись значе5 ний Sj по адресам ,N ОЗУ 70.

Формирование функции несимметричности оканчивается, когда в счетчике 46 будет записан текущий двоичный код числа N+1.

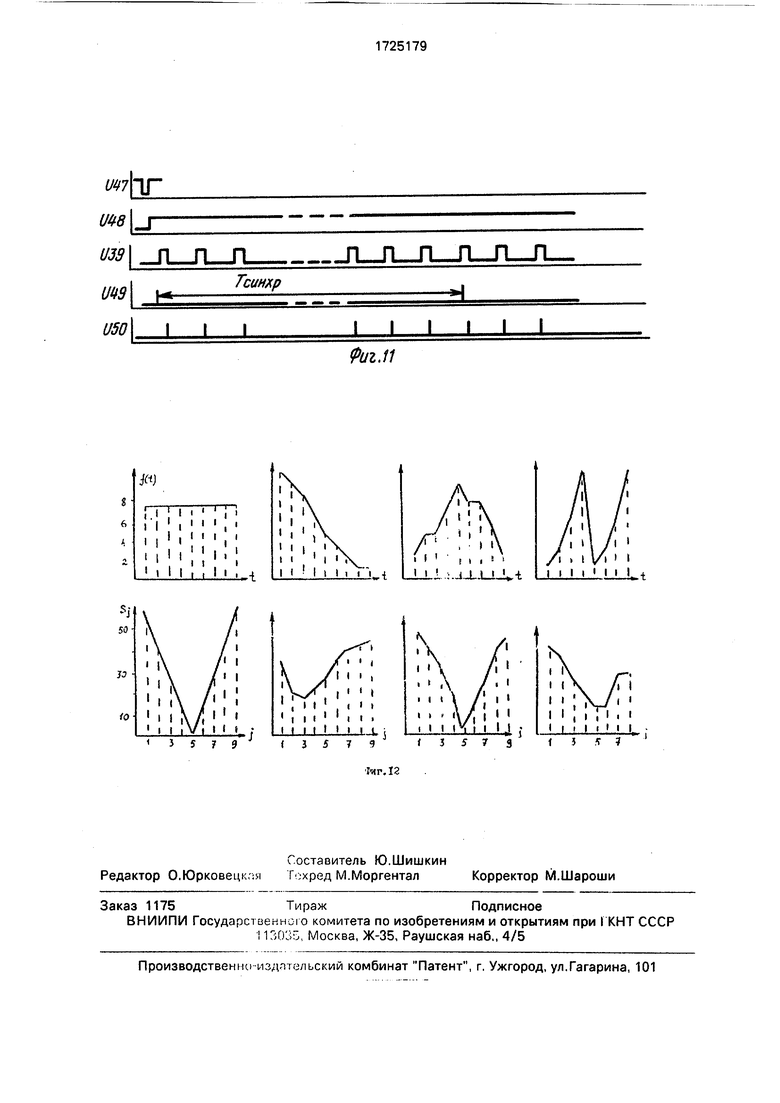

0 Режим III. Определение минимального значения функции несимметричности сигнала и его временного положения относительно начала анализируемого сигнала осуществляется следующим образом.

5 Импульс U31 (фиг. 10) отрицательной полярности с выхода формирователя 52 блока 12 поступает на триггера 19 и устанавливает его в единичное состояние. На Q-выходе триггера 19 устанавливается по0 тенциал логической единицы. С 0-выхода триггера 19 разрешающий потенциал поступает на первый вход элемента И 37, а на второй вход поступают импульсы U39 ГТИ 40 (фиг. 10). С выхода элемента 37 сигналы

5 U40 поступают на распределитель 38 импульсов. На его выходе формируются сигналы U41 и U42. Сигнал U41 поступает на четвертый вход элемента 44, а на третий вход поступает разрешающий потенциал

0 U38 с Q-выхода триггера 19(фиг.Ю). Сигнал U41 проходит на выход элемента 44 и далее на вход +1 счетчика 69. Производится последовательный перебор 1.N+1 адресов U36 ОЗУ 70. На выходах ОЗУ 70 устанавливают5 ся последовательно значения Sj функции несимметричности. С выходов ОЗУ 70 двоичные коды поступают на В-вход элемента 60 сравнения и D-входы регистра 59 памяти. На D-входы регистра 61 памяти поступают

0 двоичные крды со счетчика 69. В исходном состоянии на регистре 59 записан двоичный код 1...1, поэтому число А больше числа В, поступившего с первой ячейки памяти ОЗУ 70. На А В-выходе элемента 60 сравнения

5 установится потенциал логической единицы U44. Потенциал U44 поступает на вход элемента И 62, на его второй вход поступает сигнал U42 с распределителя 38. Инвертированный сигнал производит запись в регистры 59 и 61 памяти по С-входам. При этом

в регистре 59 сигналом U43 записывается значение функции несимметричности, находящееся в первой ячейке ОЗУ 70, а в регистре 61 - адрес первой ячейки (код 0...1). Затем выбирается содержимое второй ячейки ОЗУ 70. Если содержимое второй ячейки ОЗУ 70 меньше содержимого регистра 59, то на выходе элемента 60 сравнения сигнал U44 не изменяется, сигнал U42 проходит на выход элемента 62 и производит запись сигналом U45 значения функции несимметричности второй ячейки в регистр 59, а ее адрес - в регистр 61. В противном случае запись не производится, так как , и на выходе схемы сравнения устанавливается потенциал логического нуля U44. Указанное сравнение содержимого регистра 59 и ОЗУ 70 производится по всем N ячейкам памяти. В результате в регистре 59 записывается минимальное значение функции несимметричности анализируемого сигнала, а в регистре 61 - номер ячейки, содержащей это значение. Этот номер однозначно определяет временное положение минимума функции несимметричности. При-фиксированном начале отсчетов сигнала и периоде At тактовых импульсов положение минимального значения функции несимметричности относительно начала отсчета времени определяется как ) At.

Окончание процесса отыскания минимума функции несимметричности определяется элементом 9 сравнения, на А-вхбд которого поступает код U8 числа N с выхода счетчика 57, а на В-вход - текущий код U36 со счетчика 69. При равенстве кодов на А-В- выходе элемента 9 сравнения формируется отрицательный потенциал 1)46, поступающий на ФКИ 10, который вырабатывает отрицательный импульс U47, задержанный относительно импульса U42, и поступает на R-вход триггера 19. Импульс U47 устанавливает триггер 19 в нулевое состояние U38 (фиг. 10). Триггер 19 запрещает прохождение импульсов с выхода ГТИ 40.

Режим IV. Выдача информации на индикаторные устройства осуществляется следующим образом.

В регистрах 59 и 61 записаны минимальное значение функции несимметричности и адрес ячейки ОЗУ 70, содержащей это значение. Указанная информация поступает на вход цифровых индикаторов с блока 13 по шинам Вых.2 и Вых.З. Индикация анализируемого сигнала, хранящегося в ОЗУ 55 блока 8, и функции несимметричности, записанной в ОЗУ 70 блока 14, производится следующим образом. Сигнал U47 с выхода ФКИ 10 (фиг. 11) поступает на S-вход триггера 20 и устанавливает его в единичное

состояние. Разрешающий потенциал с Q- выхода триггера 20 поступает на десятый вход группы 42 элементов, на второй вход распределителя 41 и на пятый вход элемента 44. На первый вход распределителя поступают сигналы U39 с ГТИ 40. Распределитель 41 вырабатывает синхроимпульсы U49 и тактовые импульсы U50 длительностью гт (фиг. 11). Причем период

повторения импульсов синхронизации должен удовлетворять условию Тсинхр Мгт. Импульсы синхронизации U49 поступают на вход графического индикатора с 16-го выхода блока 11 Синхронизация и осуществляют запуск развертки. Тактовые импульсы U50 поступают на шестой вход элемента 44, на пятый вход поступает разрешающий потенциал с выхода триггера 20. Тактовые импульсы с выхода элемента 44 последовательно поступают на вход счетчика 69 и выбирают значения Sj функции несимметричности из ячеек ОЗУ 70 и значения аналогового сигнала из ячеек памяти ОЗУ 55. Выбор информации из ОЗУ 55 и 70 производится циклически и прекращается при поступлении сигнала Уст.О на R-вход триггера 20. Информация на графический индикатор поступает в двоичном коде. Любой сигнал может быть либо симметричным, либо несимметричным. Симметричность не может изменяться по степеням выраженности, например нельзя симметричный сигнал сделать еще более симметричным. В этом смысле несимметричность это иное качество сигнала. Несимметричность может изменяться по степени выраженности. Сигнал может быть несимметричным в большей или меньшей степени. Крайним, предельным случаем несимметричности является симметрия. Для симметричного сигнала степень его несимметричности может считаться равной нулю. Отклонения от симметрии, т.е. увеличение несимметричности, обнаруживается визуально и может

оцениваться качественно. Предлагаемое устройство позволяет выполнять эту операцию количественно, т.е. измерять степень несимметричности. Известные устройства указанную техническую задачу не решают.

Они позволяют только определять одну из характеристик (ось симметрии) предельного случая несимметричности. Предлагаемое устройство, решая и эту задачу, позволяет также сформировать функцию несимметричности сигнала произвольной формы, оценить степень несимметричности сигнала по значению минимума функции несимметричности и определить временное положение минимума функции несимметричности,

которое в случае симметричного сигнала, является осью его симметрии. Таким образом, предлагаемый измеритель обладает более широкими функциональными возможностями по сравнению с известными техническими решениями, позволяет повысить информативность и точность измерения несимметричности сигналов. Формула изобретения Цифровой измеритель несимметричности сигналов, содержащий генератор тактовых импульсов, формирователь коротких импульсов и элемент задержки, отличающийся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены компаратор, три формирователя коротких импульсов, элемент И-НЕ, элемент сравнения, блок массива отсчетов, блок управления, блок сравнения, блок хранения минимального значения функции несимметричности, блок вычисления, входная шина опорного напряжения, входная информационная шина, шина установки в О, выходные информационные шины Выход 1, Выход 2 и Выход 3, причем первый вход компаратора соединен с шиной опорного напряжения, а второй вход подключен к второму входу блока массива отсчетов и входной информационной шине, выход компаратора соединен с входами первого и третьего формирователей коротких импульсов, с входом генератора тактовых импульсов, с вторым входом элемента И-НЕ, восьмым входом блока массива отчетов и девятым входом блока управления, выход первого формирователя коротких импульсов подключен к шине Сброс, выход генератора тактовых импульсов соединен с входом второго формирователя коротких импульсов и первым входом блока массива отсчетов, выход второго формирователя коротких импульсов подключен к первому входу элемента И-НЕ, выход которого соединен с четвертым входом блока массива отсчетов, выход третьего формирователя коротких импульсов подключен к входу элемента задержки и седьмому входу блока массива отсчетов, выход элемента задержки соединен с шестым входом блока массива отсчетов и первым входом блока управления, первый, второй, третий и четвертый выходы блока массива отсчетов подключены соответственно к второму входу блока вычисления результата, к десятому входу блока управления, к пятому входу блока сравнения, к А-входам элемента сравнения, пятый вход блока массива отсчетов соединен с шиной установки в О измерителя, выход элемента сравнения подключен через последовательно соединенный четвертый формирователь коротких импульсов с пятым входом блока управления, первый, второй, третий, восьмой, девятый, десятый, двенадцатый, тринадцатый и пятнадцатый выходы блока управления соединены соответственно с четвертым, третьим, седьмым, пятым,,первым, шестым, девятым, восьмым и одиннадцатым входами блока вычисления результата, четвертый, пятый, шестой и седьмой выходы блока управления подключены соответственно к первому, четвертому, шестому и третьему входам блока сравнения, одиннадцатый выход блока управления соединен с четвертым входом блока хранения минимального значения

функции несимметричности, четырнадцатый выход блока управления подключен к третьему входу блока массива отсчетов, шестнадцатый выход блока управления соединен с шиной Синхронизация, а его шестой

вход подключен к шине Сброс, первый, второй, третий, четвертый и пятый выходы блока сравнения соединены соответственно с вторым, восьмым, третьим, седьмым и четвертым входами блока управления, а второй вход блока сравнения подключен к шине Сброс, первый и второй выходы блока хранения минимального значения функции несимметричности соединены соответственно с шинами Выход 2 и Выход 3 измерителя, а третий вход подключен к шине Сброс, первый выход блока вычисления результата соединен с шиной Выход 1 и с вторым входом блока хранения минимального значения функции несимметричности,

второй его выход подключен к В-входам элемента сравнения, первому входу блока хранения минимального значения функции несимметричности и одиннадцатому входу блока управления, а десятый вход блока вычисления результата соединен с шиной Сброс.

Риг.З

US

JCZIDCIi:.DC

U.9

к

ЧГ

nnnnnnnr д

-Л./Г/7

-У Ч

6ALS2Z.I.

| Устройство для определения середины импульсов периодической монотонной импульсной последовательности | 1984 |

|

SU1282072A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для определения середины прямоугольных импульсов | 1981 |

|

SU1019391A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-04-07—Публикация

1990-04-23—Подача