Предлагаемое изобретение относится к электротехнике и может быть использовано для контроля работы шагового привода, содержащего двухобмоточный шаговый двигатель (ШД), работающий в полношаговом режиме.

Наиболее часто при работе двухобмоточного ШД используется полношаговый режим, как позволяющий развивать максимальный момент. При этом регулирование тока в обмотках обеспечивается импульсным регулятором, который на интервале отключения обмотки от источника тока обеспечивает медленный спад тока для минимизации частоты переключений и уровня пульсаций.

Известны способы контроля работы шагового привода, использующие датчик положения, механически соединенный с ротором шагового двигателя, например [1] или [2]. Такие технические решения требуют введения в конструкцию привода дополнительных конструкционных элементов - самого датчика положения и элементов, обеспечивающих соединение его с ротором ШД, что ведет к увеличению массогабаритных характеристик. Известны также способы бесконтактного контроля, использующие кроме напряжений на обмотках ШД, управляющие сигналы его драйвера, например, как предложено в [3]. Необходимость использования для контроля внутренних управляющих сигналов делает невозможным использование данного технического решение для контроля уже эксплуатирующихся приводов. Известен также способ контроля работы шагового привода [4], содержащего двухфазный шаговый электродвигатель. Этот способ обеспечивает контроль наличия и смены полярности напряжений на выходе драйвера, но не позволяет проверять наличие и целостность подключенных к нему обмоток ШД. Кроме того, при использовании импульсной стабилизации тока в обмотках ШД (как, например, в современных драйверах: А4989 Allegro Microsystems [5] или ТМС262 TRINAMIC Motion Control GmbH & Co. KG [6]), выходной сигнал предложенного в [4] устройства будет иметь импульсный характер со случайной частотой, так как регулирование тока в каждой обмотке происходит независимо и, в большинстве драйверов, асинхронно.

Наиболее близким к предлагаемому техническому решению является способ контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме, и устройство для его осуществления, описанные в [7]. Применение этого способа позволяет повысить достоверность контроля работы электропривода за счет использования сигналов с датчиков тока в обмотках ШД, что позволяет определять такие отказы как обрыв в какой-либо обмотке ШД. Это техническое решение обеспечивает контроль тока в обмотках, контроль правильности его направления и достаточности величины для совершения шагов в нужном направлении, но оно не позволяет контролировать потерю синхронизации.

Задачей предлагаемого изобретения является обеспечение оперативного автоматизированного контроля потери шаговым электроприводом синхронизации.

Для решения этой задачи по окончании переходного состояния электропривода на каждом текущем шаге запоминают значения четырех первичных логических сигналов, а их значения на каждом следующем шаге по окончании следующего переходного состояния электропривода сравнивают с их предшествующими значениями и, если эти значения совпадают, формируют логический сигнал, свидетельствующий о потере шаговым приводом синхронизации, и формируют стационарное значение сигнала ступенчатого напряжения, соответствующее потере шаговым приводом синхронизации.

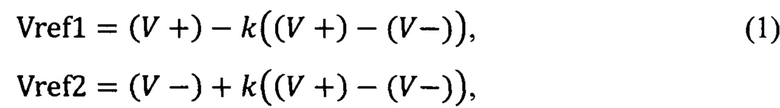

Заданные верхнее и нижнее пороговые значения напряжения, характеризующие начало и окончание переходного процесса изменения тока в каждой из обмоток ШД, выбирают в соответствии с соотношениями

где Vref1 - заданное верхнее пороговое значение,

Vref2 - заданное нижнее пороговое значение,

(V+) - напряжение, соответствующее стабилизируемому стационарному положительному значению уровня тока в обмотках ШД,

(V-) - напряжение, соответствующее стабилизируемому стационарному отрицательному значению уровня тока в обмотках ШД,

k - положительный коэффициент, значение которого выбирается при проведении заводских или лабораторных испытаний электропривода из диапазона 0,01…0,05.

Логический сигнал, свидетельствующий о потере шаговым приводом синхронизации, может быть передан в другую систему, контролирующую работу электропривода.

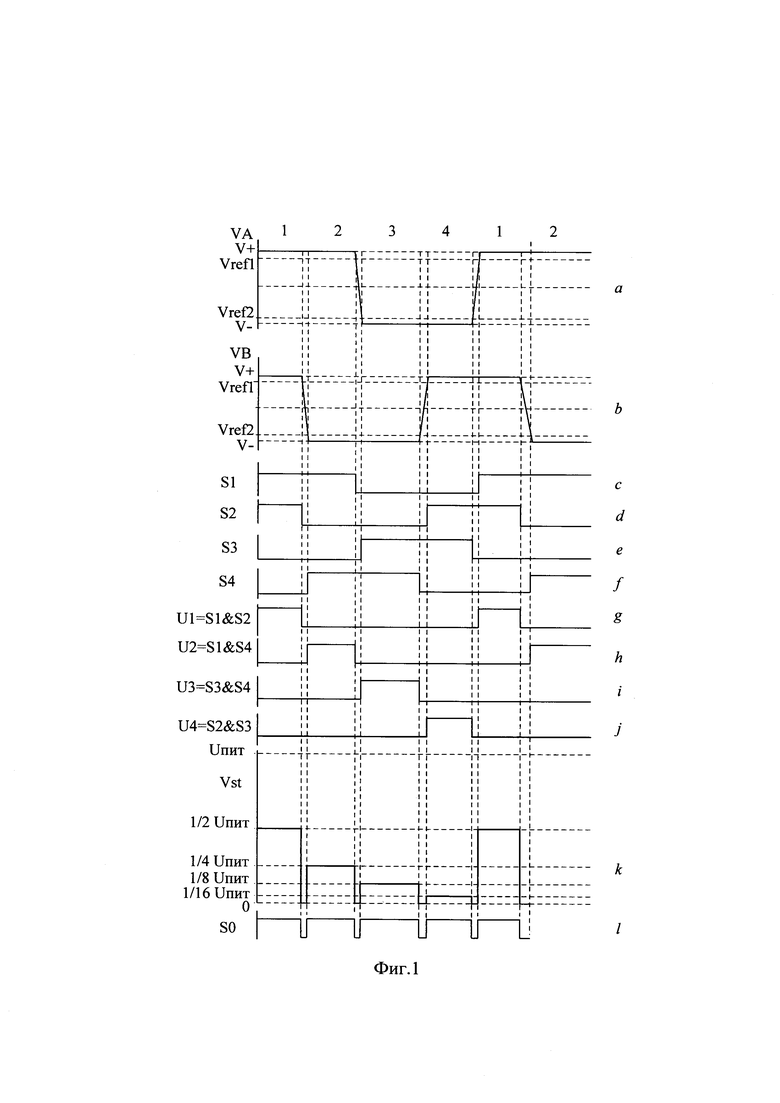

Для решения задачи изобретения в устройство введен блок обнаружения потери синхронизации с пятью входами и двумя выходами, причем первый, второй, третий и четвертый входы блока обнаружения потери синхронизации соединены соответственно с выходами первого, второго, третьего и четвертого компараторов, а его пятый вход - с выходом блока формирования ступенчатого напряжения. Первый выход блока обнаружения потери синхронизации является дискретным выходом устройства для контроля работы электропривода, а второй выход - его телеметрическим выходом.

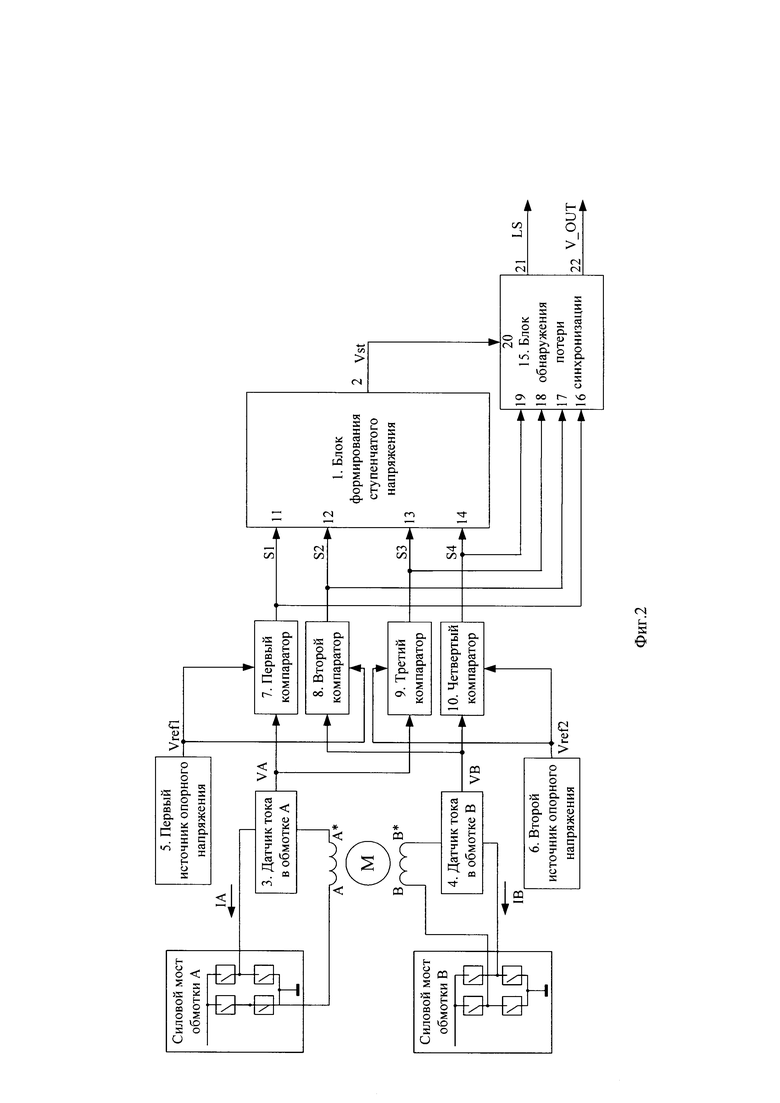

Одно из возможных исполнений блока обнаружения потери синхронизации содержит аналоговый компаратор, третий источник опорного напряжения, формирователь импульсов, регистр хранения, цифровой компаратор, D-триггер и сумматор. Причем первый вход аналогового компаратора соединен с пятым входом блока обнаружения потери синхронизации, а его второй вход с выходом третьего источника опорного напряжения, выход аналогового компаратора соединен с входом формирователя импульсов, первый и второй выходы которого соединены соответственно с тактовыми входами D-триггера и регистра хранения. Входы данных регистра хранения и входы секции В цифрового компаратора соединены соответственно с первым, вторым, третьим и четвертым входами блока обнаружения потери синхронизации. Выходы регистра хранения соединены с соответствующими входами секции А цифрового компаратора, выход которого соединен с входом данных D-триггера, прямой выход которого является дискретным выходом устройства для контроля работы электропривода и соединен с первым входом сумматора, второй вход которого соединен с пятым входом блока обнаружения потери синхронизации, а его выход является телеметрическим выходом устройства для контроля работы электропривода.

Другое возможное исполнение блока обнаружения потери синхронизации содержит два логических элемента 2ИЛИ, логический элемент 2И, формирователь импульсов, регистр хранения, цифровой компаратор, D-триггер и сумматор. Причем входы первого логического элемента 2ИЛИ соединены с первым и вторым входами блока обнаружения потери синхронизации, а входы второго логического элемента 2ИЛИ соединены с третьим и четвертым входами блока обнаружения потери синхронизации. Выходы обоих логических элементов 2ИЛИ соединены с входами логического элемента 2И, выход которого соединен с входом формирователя импульсов, первый и второй выходы которого соединены соответственно с тактовыми входами D-триггера и регистра хранения. Входы данных регистра хранения и входы секции В цифрового компаратора соединены соответственно с первым, вторым, третьим и четвертым входами блока обнаружения потери синхронизации, выходы регистра хранения соединены с соответствующими входами секции А цифрового компаратора, выход которого соединен с входом данных D-триггера, прямой выход которого является дискретным выходом устройства для контроля работы электропривода и соединен с первым входом сумматора, второй вход которого соединен с пятым входом блока обнаружения потери синхронизации, а его выход является телеметрическим выходом устройства для контроля работы электропривода.

Формирователь импульсов блока обнаружения потери синхронизации может быть выполнен по схеме трех последовательно соединенных одновибраторов. Причем вход первого одновибратора является входом формирователя импульсов, а его инверсный выход является первым выходом формирователя импульсов и соединен с входом второго одновибратора, инверсный выход которого соединен с входом третьего одновибратора, прямой выход которого является вторым выходом формирователя импульсов.

Сущность предлагаемого технического решения поясняется чертежами.

Фиг. 1. Схематичная временная диаграмма формирования первичных и вторичных логических сигналов и сигнала ступенчатого напряжения, отражающего состояние ШД после совершения очередного шага.

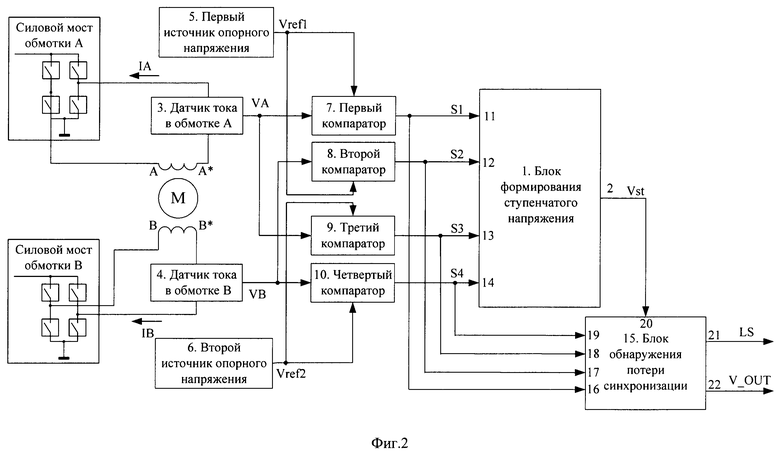

Фиг. 2. Функциональная схема устройства для контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме.

Фиг. 3. Функциональная схема первого варианта исполнения блока обнаружения потери синхронизации.

Фиг. 4. Функциональная схема второго варианта исполнения блока обнаружения потери синхронизации.

Фиг. 5. Функциональная схема возможного исполнения формирователя импульсов.

Фиг. 6. Электрическая принципиальная схема возможного варианта исполнения блока формирования ступенчатого напряжения.

Фиг. 7. Результаты компьютерного моделирования работы устройства для контроля работы электропривода при вторичной обработке первого набора экспериментальных данных.

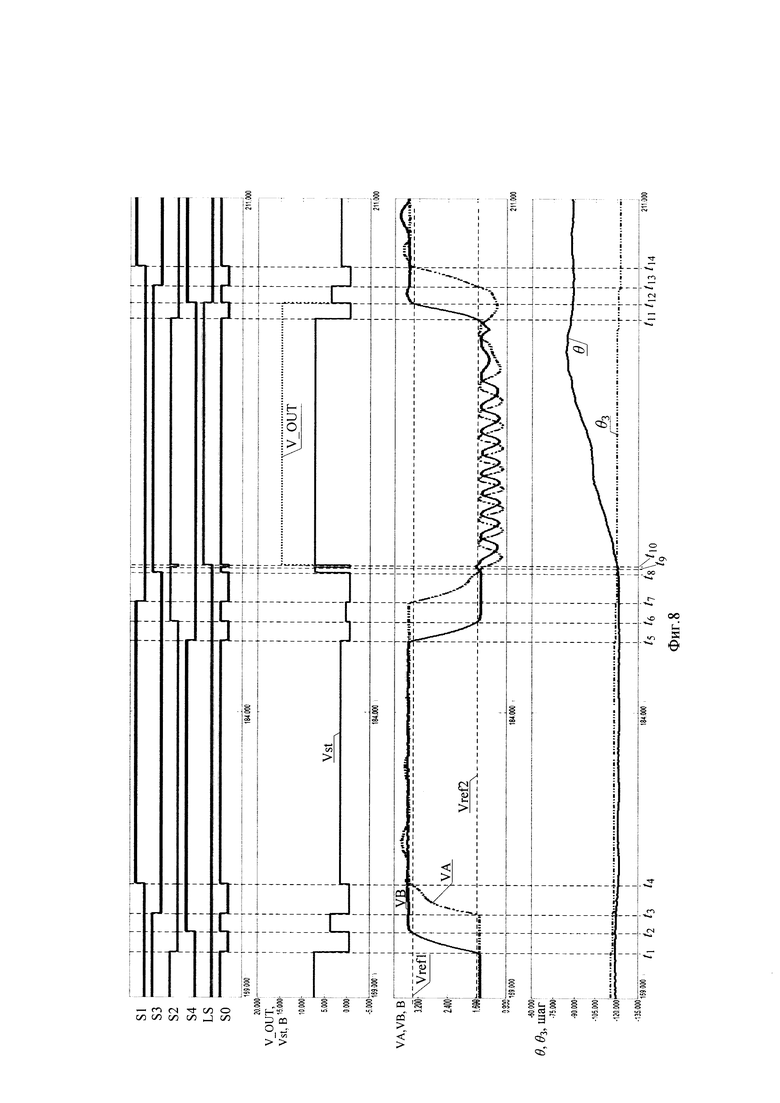

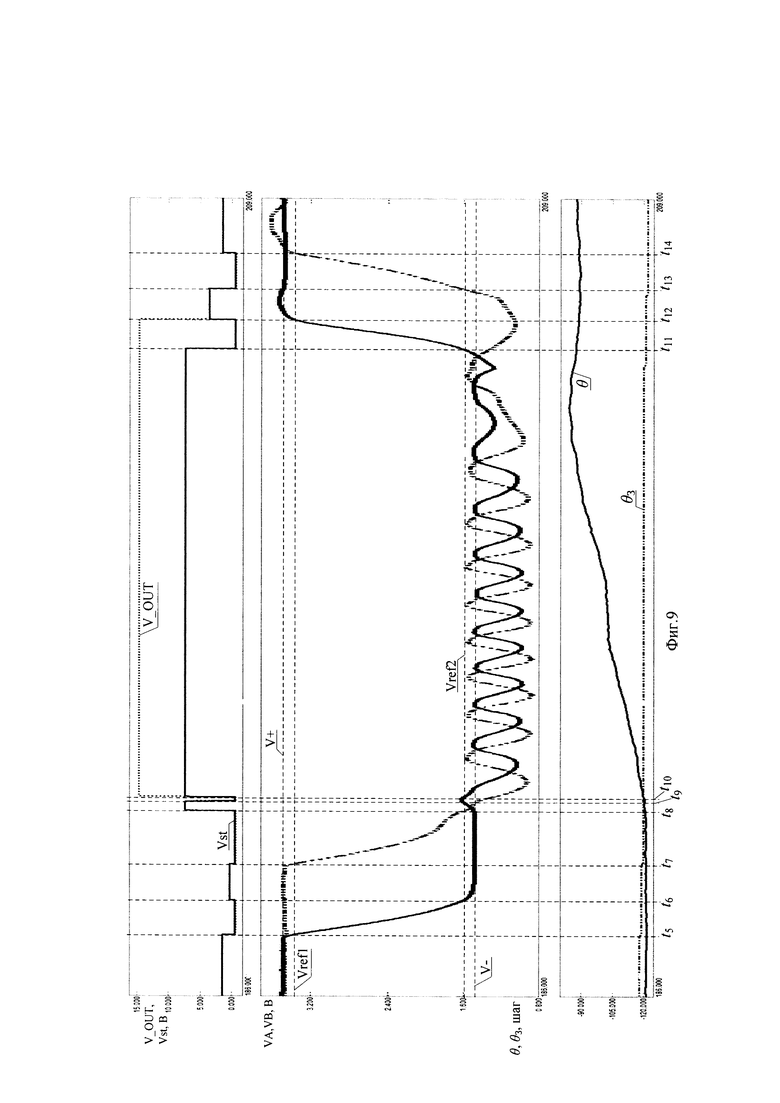

Фиг. 8. Результаты компьютерного моделирования работы устройства для контроля работы электропривода при вторичной обработке второго набора экспериментальных данных.

Фиг. 9. Переходные процессы изменения основных параметров электропривода в увеличенном масштабе на характерном участке компьютерного моделирования, результаты которого приведены на фиг. 8.

Работа электропривода на основе двухобмоточного ШД в полношаговом режиме подробно описана в разных литературных источниках (см., например, [8]). Из тех же источников известно, что при работе такого шагового электропривода в условиях большой статической или динамической нагрузки, а также при подаче управляющих импульсов с частотой, близкой к резонансной, может возникать пропуск шагов или потеря синхронизации. В этом случае действительное значение положения вала электропривода перестает совпадать с его заданным значением, которое формируется управляющими импульсами. Предлагаемое техническое решение позволяет как раз обеспечить оперативный автоматизированный контроль потери шаговым электроприводом синхронизации.

Схематичная временная диаграмма, поясняющая процессы формирования первичных и вторичных логических сигналов, позволяющих получить сигнал ступенчатого напряжения, отражающий состояние ШД после совершения очередного шага, приведена на фиг. 1. Из приведенных на этом рисунке графиков видно, что напряжения VA и VB, соответствующие величинам токов в обмотках ШД, имеют характерные стационарные и переходные участки.

Стационарный участок V+ соответствует стабилизируемому положительному значению уровня тока в обмотках ШД, а стационарный участок V- соответствует стабилизируемому отрицательному значению уровня тока. При использовании полношагового режима для вращения ротора ШД в одну сторону производится поочередная смена направления тока в фазах А и В, как это показано на фиг. 1 а и b. После последовательного перебора четырех возможных сочетаний направлений токов в двух фазах, эта картина циклически повторяется. Для изменения направления вращения ротора при совершении очередного шага реверс тока осуществляется в той же фазе, в которой он был произведен на предыдущем шаге. Таким образом, четыре возможных сочетания направлений токов в обмотках ШД, полностью характеризуют состояние ШД, что позволяет достоверно контролировать работу электропривода в стационарном режиме.

За переходный участок, когда происходит смена стационарных режимов, принимается участок изменения тока в любой фазе ШД, на котором значение тока в этой фазе меньше заданного верхнего порогового значения Vref1 и больше заданного нижнего порогового значения Vref2. Если на каком-то участке работы электропривода значение тока в любой из фаз ШД или больше заданного верхнего порогового значения Vref1, или меньше заданного нижнего порогового значения Vref2, то этот участок работы считается стационарным. Заданные верхнее и нижнее пороговые значения выбираются в соответствии с соотношениями (1). Значение положительного коэффициента k обычно выбирают при лабораторных или заводских испытаниях в диапазоне от 0,01 до 0,05 из условия обеспечения помехозащищенности. При таком значении коэффициента k достигается отклонение заданного верхнего порогового значения Vref1 и заданного нижнего порогового значения Vref2 от величины стабилизируемого значения модуля тока в обмотках 2…10%.

Во время работы ШД непрерывно измеряют токи в каждой обмотке и формируют два сигнала напряжения VA и VB, соответствующие току в каждой обмотке, сравнивают их с заданными верхним и нижним пороговыми значениями Vref1 и Vref2 и формируют четыре первичных логических сигнала S1, S2, S3 и S4 (см. фиг. 1 c, d, e и f) так, что первый из них S1 принимает значение логической «1», если сигнал напряжения VA, соответствующий току в обмотке А, превосходит заданное верхнее пороговое значение Vref1, и значение логического «0» в противном случае. Второй из них S2 принимает значение логической «1», если сигнал напряжения VB, соответствующий току в обмотке В, превосходит заданное верхнее пороговое значение Vref1, и значение логического «0» в противном случае. Третий из них S3 принимает значение логической «1», если сигнал напряжения VA, соответствующий току в обмотке А, имеет значение ниже заданного нижнего порогового значения Vref2, и значение логического «0» в противном случае. Четвертый из них S4 принимает значение логической «1», если сигнал напряжения VB, соответствующий току в обмотке В, имеет значение ниже заданного нижнего порогового значения Vref2, и значение логического «0» в противном случае. В зависимости от полученных значений первичных логических сигналов формируют четыре вторичных логических сигнала U1, U2, U3 и U4 таким образом, что (см. фиг. 1 g, h, i и j) первый из них U1 принимает значение логической «1», если первый и второй первичные логические сигналы S1 и S2 имеют значение логической «1», и значение логического «0» в противном случае. Второй из них U2 принимает значение логической «1», если первый и четвертый первичные логические сигналы S1 и S4 имеют значение логической «1», и значение логического «0» в противном случае. Третий из них U3 принимает значение логической «1», если третий и четвертый первичные логические сигналы S3 и S4 имеют значение логической «1», и значение логического «0» в противном случае. Четвертый из них U4 принимает значение логической «1», если второй и третий первичные логические сигналы S2 и S3 имеют значение логической «1» и значение логического «0» в противном случае. В зависимости от полученных значений вторичных логических сигналов формируют сигнал ступенчатого напряжения Vst (см. фиг. 1k), каждое стационарное значение которого соответствует одному из четырех возможных состояний установившихся значений токов в обмотках шагового двигателя. А, если значения всех четырех вторичных логических сигналов U1, U2, U3 и U4 одновременно имеют значение логического «0», формируют стационарное значение сигнала ступенчатого напряжения, соответствующее этому переходному состоянию электропривода (на фиг. 1k это стационарное значение сигнала ступенчатого напряжения равно нулю). На фиг. 1l показан логический сигнал S0, который принимает значение логического «0», когда значение сигнала ступенчатого напряжения Vst соответствует переходному состоянию электропривода, и значение логической «1» в противном случае.

Одним из возможных решений по формированию сигнала ступенчатого напряжения является такое [7]. Значение сигнала ступенчатого напряжения (см. фиг. 1k) формируют равным 1/2 максимально возможного уровня ступенчатого напряжения, если значение первого вторичного логического сигнала равно логической «1». Максимально возможным уровнем ступенчатого напряжения можно считать напряжение питания схемы формирования сигнала ступенчатого напряжения Uпит. Значение сигнала ступенчатого напряжения на данном шаге формируют равным 1/4 максимально возможного уровня ступенчатого напряжения, если значение второго вторичного логического сигнала равно логической «1». Значение сигнала ступенчатого напряжения на данном шаге формируют равным 1/8 максимально возможного уровня ступенчатого напряжения, если значение третьего вторичного логического сигнала равно логической «1». Значение сигнала ступенчатого напряжения на данном шаге формируют равным 1/16 максимально возможного уровня ступенчатого напряжения, если значение четвертого вторичного логического сигнала равно логической «1».

Если значения всех четырех вторичных логических сигналов одновременно имеют значение логического «0», формируют значение сигнала ступенчатого напряжения, равное минимально возможному уровню ступенчатого напряжения, которое фактически соответствует нулю.

Таким образом, формирование уровней сигнала ступенчатого напряжения Vst можно производить в зависимости от удобства последующего анализа этого сигнала и простоты реализации операции его формирования. На фиг. 1k показан пример формирования сигнала ступенчатого напряжения, в котором формируемые четыре уровня сигнала Vst будут принимать значения 1/2Uпит, 1/4Uпит, 1/8Uпит, 1/16Uпит и 0.

Анализ сформированного сигнала ступенчатого напряжения позволяет определить количество выполненных шагов ШД, направление вращения выходного вала электропривода, частоту шагов (а значит, среднюю скорость вращения) и изменение угла поворота выходного вала во время работы электропривода, т.е. обеспечить контроль его работы.

Когда же (под действием возрастающей статической или динамической нагрузки или при приближении частоты следования управляющих импульсов к резонансной) возникает ситуация, которая называется потерей синхронизации электропривода (см., например [8]), начинается вращение ротора ШД со скоростью, значительно превосходящей заданную допустимую скорость вращения, и, обычно, в направлении, противоположном заданному направлению вращения. Задачей предполагаемого изобретения является как раз обеспечение оперативного автоматизированного контроля потери шаговым электроприводом синхронизации.

Для решения этой задачи каждый раз по окончании переходного состояния электропривода, которому соответствует значение Vst=0 и значение логического нуля сигнала S0, на каждом текущем шаге i запоминают значения четырех первичных логических сигналов S1i, S2i, S3i и S4i. Их значения на каждом следующем шаге (i+1) по окончании следующего переходного состояния электропривода S1i+1, S2i+1, S3i+1 и S4i+1 сравнивают с их предшествующими значениями S1i, S2i, S3i и S4i. Если эти значения совпадают, формируют логический сигнал LS (lost sync), свидетельствующий о потере шаговым приводом синхронизации, и одновременно формируют стационарное значение сигнала ступенчатого напряжения Vst=Uпит, соответствующее потере шаговым приводом синхронизации.

Состояние, когда одновременно S1i+1=S1i, S2i+1=S2i, S3i+1=S3i и S4i+1=S4i, возникает только в том случае, если значение тока в любой из обмоток либо после уменьшения ниже заданного верхнего порогового значения Vref1 не достигает заданного нижнего порогового значения Vref2, а опять становится выше заданного верхнего порогового значения Vref1, либо после превышения заданного нижнего порогового значения Vref2 не достигает заданного верхнего порогового значения Vref1, а опять становится ниже заданного нижнего порогового значения Vref2. Именно такое состояние однозначно свидетельствует о потере шаговым приводом синхронизации, поскольку нарушается логика его работы.

Для реализации предлагаемого способа было разработано устройство для контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме. Функциональная схема устройства приведена на фиг. 2. Устройство содержит (см. фиг. 2) блок формирования ступенчатого напряжения 1, имеющий выход 2, два датчика тока 3 и 4, два источника опорного напряжения 5 и 6 и четыре компаратора 7, 8, 9 и 10, выходы которых соединены соответственно с первым, вторым, третьим и четвертым входами 11, 12, 13 и 14 блока формирования ступенчатого напряжения, и блок обнаружения потери синхронизации 15 с пятью входами и двумя выходами. Первые входы первого и третьего компараторов 7 и 9 соединены с выходом датчика тока 3 в обмотке А. Первые входы второго и четвертого компараторов 8 и 10 соединены с выходом датчика тока 4 в обмотке В. Вторые входы первого и второго компараторов 7 и 8 соединены с выходом первого источника опорного напряжения 5, а вторые входы третьего и четвертого компараторов 9 и 10 соединены с выходом второго источника опорного напряжения 6. Первый 16, второй 17, третий 18 и четвертый 19 входы блока обнаружения потери синхронизации 15 соединены соответственно с выходами первого 7, второго 8, третьего 9 и четвертого компараторов 10, а его пятый вход 20 - с выходом 2 блока формирования ступенчатого напряжения 1. Первый выход 21 блока обнаружения потери синхронизации 15 является дискретным выходом устройства для контроля работы электропривода, а второй выход 22 - его телеметрическим выходом.

Функциональная схема первого варианта исполнения блока обнаружения потери синхронизации приведена на фиг. 3. Блок обнаружения потери синхронизации в этом исполнении (см. фиг. 3) содержит аналоговый компаратор 23, третий источник опорного напряжения 24, формирователь импульсов 25, регистр хранения 26, цифровой компаратор 27, D-триггер 28 и сумматор 29. Первый вход аналогового компаратора 23 соединен с пятым входом блока обнаружения потери синхронизации 20, а его второй вход с выходом третьего источника опорного напряжения 24. Выход аналогового компаратора 23 соединен с входом формирователя импульсов 25, первый и второй выходы которого соединены соответственно с тактовыми входами D-триггера 28 и регистра хранения 26. Входы данных регистра хранения 26 и входы секции В цифрового компаратора 27 соединены соответственно с первым 16, вторым 17, третьим 18 и четвертым 19 входами блока обнаружения потери синхронизации. Выходы регистра хранения 26 соединены с соответствующими входами секции А цифрового компаратора 27, выход которого соединен с входом данных D-триггера 28, прямой выход которого является дискретным выходом устройства для контроля работы электропривода 21 и соединен с первым входом сумматора 29, второй вход которого соединен с пятым входом блока обнаружения потери синхронизации 20. Выход сумматора 29 является телеметрическим выходом 22 устройства для контроля работы электропривода.

Функциональная схема второго варианта исполнения блока обнаружения потери синхронизации приведена на фиг. 4. Блок обнаружения потери синхронизации в этом исполнении (см. фиг. 4) содержит два логических элемента 2ИЛИ 30 и 31, логический элемент 2И 32, формирователь импульсов 25, регистр хранения 26, цифровой компаратор 27, D-триггер 28 и сумматор 29. Входы первого логического элемента 2ИЛИ 30 соединены с первым 16 и вторым 17 входами блока обнаружения потери синхронизации. Входы второго логического элемента 2ИЛИ 31 соединены с третьим 18 и четвертым 19 входами блока обнаружения потери синхронизации. Выходы обоих логических элементов 2ИЛИ 30 и 31 соединены с входами логического элемента 2И 32, выход которого соединен с входом формирователя импульсов 25. Первый и второй выходы формирователя импульсов 25 соединены соответственно с тактовыми входами D-триггера 28 и регистра хранения 26. Входы данных регистра хранения 26 и входы секции В цифрового компаратора 27 соединены соответственно с первым 16, вторым 17, третьим 18 и четвертым 19 входами блока обнаружения потери синхронизации. Выходы регистра хранения 26 соединены с соответствующими входами секции А цифрового компаратора 27, выход которого соединен с входом данных D-триггера 28, прямой выход которого является дискретным выходом 21 устройства для контроля работы электропривода и соединен с первым входом сумматора 29. Второй вход сумматора 29 соединен с пятым входом 20 блока обнаружения потери синхронизации, а его выход является телеметрическим выходом 22 устройства для контроля работы электропривода.

Функциональная схема возможного исполнения формирователя импульсов для обоих предложенных вариантов исполнения блока обнаружения потери синхронизации приведена на фиг. 5. Формирователь импульсов (см. фиг. 5) выполнен по схеме трех последовательно соединенных одновибраторов. Вход S0 первого одновибратора 33 является входом формирователя импульсов, а его инверсный выход Т1 является первым выходом формирователя импульсов и соединен с входом второго одновибратора 34, инверсный выход которого соединен с входом третьего одновибратора 35. Прямой выход Т2 третьего одновибратора 35 является вторым выходом формирователя импульсов. В нижней части фиг. 5 приведена временная диаграмма работы формирователя импульсов. Формирование импульсов начинается каждый раз после поступления на вход формирователя импульсов переднего фронта логического сигнала S0. Каждый одновибратор может быть построен, например, по схеме, приведенной на странице 58 рис. 1 в [9].

На фиг. 6 показана электрическая принципиальная схема возможного варианта исполнения блока формирования ступенчатого напряжения [7]. Блок формирования ступенчатого напряжения содержит (см. фиг. 6) четыре логических элемента 2И DD1.1-DD1.4, операционный усилитель DA7.1, четвертый источник опорного напряжения Vref4 (на схеме не показан), четыре полевых транзистора VT1-VT4 и четыре резистивных делителя напряжения на элементах R1-R5, каждый из которых образован резистором R1…R4, соединенным со стоком соответствующего полевого транзистора VT1…VT4, и резистором обратной связи R5. Первые входы первого и второго логических элементов 2И DD1.1 и DD1.2 соединены с первым входом блока формирования ступенчатого напряжения 11. Первые входы третьего и четвертого логических элементов 2И DD1.3 и DD1.4 соединены с третьим входом блока формирования ступенчатого напряжения 13. Вторые входы первого и четвертого логических элементов 2И DD1.1 и DD1.4 соединены со вторым входом блока формирования ступенчатого напряжения 12. Вторые входы второго и третьего логических элементов 2И DD1.2 и DD1.3 соединены с четвертым входом блока формирования ступенчатого напряжения 14. Выходы всех логических элементов 2И DD1.1-DD1.4 соединены соответственно с затворами первого, второго, третьего и четвертого полевых транзисторов VT1-VT4, истоки которых соединены между собой, а стоки соединены соответственно с первыми выводами первого, второго, третьего и четвертого резисторов R1, R2, R3 и R4. Вторые выводы первого, второго, третьего и четвертого резисторов R1, R2, R3 и R4 соединены между собой, а также с инвертирующим входом операционного усилителя DA7.1 и с первым выводом резистора обратной связи R5, второй вывод которого соединен с выходом операционного усилителя, являющегося выходом блока формирования ступенчатого напряжения 2. Неинвертирующий вход операционного усилителя DA7.1 соединен с выходом четвертого источника опорного напряжения, величина которого Vref4 выбирается равной 1/32 максимально возможного уровня ступенчатого напряжения. Такая величина опорного напряжения определяется исходя из того, что максимальный коэффициент усиления усилителя с параметрами, показанными на Figure 2-35 (страница 2.33 в [10]) при замыкании одного ключа (что соответствует нормальной работе драйвера), не превышает 16. Для обеспечения диагностики аварийных состояний при замыкании четырех ключей коэффициент усиления усилителя будет равен 30, что при выбранном значении опорного напряжения не позволит переходить усилителю в режим насыщения.

В схеме, приведенной на фиг. 6, формирование сигнала ступенчатого напряжения выполняется с использованием усилителя с программируемым коэффициентом усиления, выполненного, например, как показано на Figure 2-35 (страница 2.33 в [10]). Для обеспечения необходимой точности в качестве ключей необходимо использовать NMOSFET транзисторы VT1-VT4 IRLML0060TRPbF [11] с малым сопротивлением RDS(on), не превышающим 116 мОм, при напряжении затвора 4,5 В. При указанных параметрах ключа (RDS(on) max) вносимая им относительная погрешность даже для минимального значения сопротивления 625 Ом, приведенного в [10], составит ΔR/R=0.116/625=0.000186. Источник опорного напряжения, формирующий напряжение Vref4, может быть выполнен на резистивном делителе.

Функционирует предлагаемое устройство для контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме, следующим образом.

Измерение тока в обмотках ШД осуществляется датчиками тока 3 и 4. Учитывая тенденцию современной техники к миниатюризации, снижению стоимости и расширению универсальности применения, наиболее эффективным решением является применение датчиков тока на основе микросхем с интегрированными элементами Холла. Для двигателя с номинальным током обмоток 5А, в качестве такого датчика может быть применена микросхема ACS724LLCTR-10AB [12]. Напряжение на выходе микросхемы будет определяться выражением

где I - ток через датчик;

К=0,2 В/А - коэффициент преобразования;

Uп=5 В - напряжение питания датчика.

При использовании данного датчика сопротивление, вносимое в цепь измерения тока в обмотке, составляет не более 1.2 мОм. Полностью исключить влияние датчика на цепь измерения тока в обмотке можно, применив бесконтактный датчик тока MLX91206 [13], позволяющий получить выходное напряжение в соответствии с выражением (2), при К=35 мВ/А.

Выходные сигналы датчиков тока 3 и 4 в обмотках VA и VB поступают на входы компараторов 7-10, где сравниваются с опорными напряжениями Vref1 и Vref2, формируемыми первым 5 и вторым 6 источниками опорного напряжения.

Таким образом, первый 7 и второй 8 компараторы формируют на выходе логическую «1» в случае превышения выходным сигналом датчика тока 3 и 4 соответственно в обмотке А и В ШД верхнего порогового значения Vref1, третий и четвертый компараторы - при величине выходного сигнала соответствующего датчика тока меньше нижнего порогового значения Vref2. В качестве компаратора может быть использована микросхема MIC7211BM5 [14].

Выходные сигналы компараторов S1-S4 поступают на соответствующие входы блока формирования ступенчатого напряжения 1 и блока обнаружения потери синхронизации 15.

В блоке формирования ступенчатого напряжения первичные логические сигналы S1-S4, поступающие на его входы (см. фиг. 6), преобразуются с помощью четырех логических элементов 2И DD1.1-DD1.4 во вторичные логические сигналы U1-U4 в соответствии с временной диаграммой, показанной на фиг. 1 g-j. Вторичные логические сигналы U1-U4 поступают на затворы полевых транзисторов VT1-VT4, стоки которых через соответствующие резисторы соединены с инвертирующим входом операционного усилителя DA7.1, на выходе которого в результате формируется сигнал ступенчатого напряжения Vst, поступающий на пятый вход блока обнаружения потери синхронизации.

Блок обнаружения потери синхронизации в обоих исполнениях работает аналогично. В первом исполнении (см. фиг. 3) для формирования логического сигнала S0 используется аналоговый компаратор 23, на вход которого подается сигнал ступенчатого напряжения Vst, поступающий на пятый вход 20 блока обнаружения потери синхронизации. На второй вход аналогового компаратора 23 подается опорное напряжение Vref3 с выхода третьего источника опорного напряжения 24. Сигнал S0 на выходе аналогового компаратора 23 имеет значение логический «0» в момент времени, когда сигнал ступенчатого напряжения Vst соответствует нулевому уровню. Это обеспечивается сравнением ступенчатого напряжения с опорным напряжением Vref3, величина которого выбирается для обеспечения максимальной помехозащищенности из условия:

где Vst_min - минимальное значение ступенчатого напряжения Vst, соответствующее 1/16Uпит на фиг. 1k,

Vst0 - значение ступенчатого напряжения, когда сигнал ступенчатого напряжения Vst соответствует нулевому уровню.

Сигнал S0 на выходе аналогового компаратора принимает значение логическая «1», когда Vst>Vref3.

Во втором исполнении блока обнаружения потери синхронизации (см. фиг. 4) для формирования логического сигнала S0 используются входные первичные логические сигналы S1-S4, которые преобразуются с помощью двух логических элементов 2ИЛИ 30 и 31 и логического элемента 2И 32. В результате на выходе логического элемента 2И 32 формируется логический сигнал S0, который принимает значение логический «0», когда два из любой пары первичных логических сигналов S1 и S2 или S3 и S4 имеют значение логический «0», и значение логическая «1» в противном случае. То есть логический сигнал S0 принимает значение логический «0», когда сигнал ступенчатого напряжения Vst соответствует нулевому уровню (см. временную диаграмму фиг. 1k и l). Или иначе, сигнал S0 получается в результате выполнения логического выражения:

Логический сигнал S0 для любого из двух предложенных вариантов исполнения поступает на вход формирователя импульсов 25. По переднему фронту этого сигнала формирователь импульсов 25 формирует два последовательных импульса, разделенных защитным интервалом, на выходах Т1 и Т2 в соответствии с временной диаграммой, приведенной в нижней части фиг. 5.

Первичные логические сигналы S1…S4 одновременно поступают на информационные входы четырехразрядного регистра хранения 26 и входы секции В цифрового компаратора 27. На входы секции А цифрового компаратора 27 поступают аналогичные сигналы S1i…S4i с выходов регистра хранения 26, которые соответствуют предшествовавшим значениям первичных логических сигналов S1…S4 на предыдущем интервале между двумя состояниями логический «0» сигнала S0. Фиксация сигналов S1i…S4i на выходе регистра хранения 26 происходит при поступлении на его тактовый вход отрицательного фронта сигнала Т2 от формирователя импульсов 25. Логическая «1» на выходе цифрового компаратора 27 устанавливается при одновременном выполнении четырех условий: S1i=S1i+1; S2i=S2i+1; S3i=S3i+1 и; S4i=S4i+1.

Сигнал с выхода цифрового компаратора 27 поступает на информационный вход D D-триггера 28 и передается на его прямой выход, когда на тактовом входе С D-триггера 28 появляется передний фронт импульса сигнала Т1, поступающего от формирователя импульсов 25. По окончании защитного интервала по отрицательному фронту сигнала Т2 состояние сигналов S1…S4 на текущем шаге ШД фиксируется на выходе регистра хранения 26 до появления следующего переднего фронта сигнала Т2. Работа формирователя импульсов 25 соответствует временной диаграмме, приведенной в нижней части фиг. 5.

Сигнал с прямого выхода D-триггера 28 поступает на первый вход сумматора 29, на второй вход которого подается сигнал ступенчатого напряжения Vst. Параметры сумматора 29 выбираются так, чтобы при логической «1» на его первом входе обеспечить напряжение V_OUT на его выходе, близкое к напряжению питания, что значительно превышает величину ступенчатого напряжения при нормальной работе ШД (без потери синхронизации).

Прямой выход D-триггера 28 является прямым выходом предлагаемого устройства. Когда сигнал на выходе D-триггера 28 имеет значение логическая «1», это свидетельствует о потере электроприводом синхронизации. Выход сумматора 29 является аналоговым выходом устройства и представляет собой ступенчатое напряжение, каждый стационарный уровень которого соответствует определенному стационарному состоянию электропривода.

В качестве цифрового компаратора может быть использована, например, микросхема 555СП1 [15] или ее аналог SN7485 (page 7-57 в [16]). Регистр хранения может быть выполнен, например, на микросхеме КМ155ТМ5, объединяющей в себе четыре D-триггера, или на ее аналоге SN54L77 (page 7-35 в [16]). В качестве элемента 2ИЛИ может быть применена микросхема 1594ЛЛ1Т [17], а в качестве элемента 2И - микросхема 1594ЛИ1Т [18]. Возможная схема сумматора и расчет его параметров описаны в [19] на с. 77. Подобный сумматор также можно построить с использованием операционного усилителя MCP6V02-E/SN/ [20].

Наиболее перспективным решением может быть реализация всего предлагаемого устройства, кроме датчиков тока, на одной полузаказной микросхеме серии 5503 [21].

Для подтверждения работоспособности и эффективности заявляемого технического решения было проведено компьютерное моделирование работы электрической принципиальной схемы устройства, реализующего предлагаемый способ, построенной на основании его функциональной схемы, приведенной на фиг. 2. При этом использовался программный пакет Micro-Cap (Microcomputer Circuit Analysis Program) для компьютерного моделирования аналоговых и цифровых электронных устройств [22, 23]. Компьютерное моделирование работы электрической принципиальной схемы устройства проводилось путем подачи на ее входы экспериментальных значений выходных сигналов датчиков тока в обмотках А и В ШД, которые обозначены на схеме фиг. 2 VA и VB соответственно.

На фиг. 7 приведены результаты компьютерного моделирования функционирования устройства для контроля работы электропривода при вторичной обработке первого набора экспериментальных данных. На фиг. 8 приведены результаты компьютерного моделирования функционирования устройства для контроля работы электропривода при вторичной обработке второго набора экспериментальных данных. А на фиг. 9 показаны переходные процессы изменения основных параметров электропривода в увеличенном масштабе на характерном участке компьютерного моделирования, результаты которого приведены на фиг. 8.

На графиках показаны процессы изменения выходных сигналов датчиков токов в обмотках ШД VA и VB, сигнала ступенчатого напряжения Vst, аналогового выходного сигнала устройства V_OUT, сигналов заданного положения θ3 и измеренного с помощью энкодера действительного положения θ выходного вала электропривода, а также дискретных сигналов: первичных логических сигналов S1, S2, S3 и S4, логического сигнала S0 и дискретного выходного сигнала устройства LS. На график также нанесены верхнее Vref1 и нижнее Vref2 пороговые значения токов в обмотках. По оси абсцисс нанесено время в миллисекундах. Все напряжения показаны в вольтах, а положения выходного вала электропривода в шагах ШД.

Усеченная, но укрупненная фиг. 9 позволяет подробнее и точнее проиллюстрировать процессы формирования ступенчатого напряжения Vst и аналогового выходного сигнала устройства V_OUT. Здесь хорошо видно, что на переходных участках изменения токов фаз (отрезки [t5, t6], [t7, t8], [t9, t10], [t11, t12] и [t13, t14]), когда значение напряжения, характеризующего изменение тока в одной из фаз, находится в интервале между нижним Vref2 и верхним Vref1 заданными пороговыми значениями, формируется значение ступенчатого напряжения Vst, соответствующее нулевому уровню. Хорошо видно также, что, после того как напряжение, соответствующее току в одной из обмоток ШД (в данном случае в обмотке В - VB), пересекает дважды подряд одно заданное пороговое значение (в данном случае заданное нижнее пороговое значение Vref2), происходит формирование сигнала V_OUT (и LS), информирующего о потере электроприводом синхронизации.

Приведенные на фиг. 7-9 результаты компьютерного моделирования работы предлагаемого устройства, реализующего заявляемый способ, подтверждают работоспособность и эффективность предложенного технического решения, а также то, что поставленная задача по обеспечению оперативного автоматизированного контроля потери шаговым электроприводом синхронизации решена. При работе в реальном времени формируемый предлагаемым устройством дискретный выходной сигнал LS, свидетельствующий о потере электроприводом синхронизации, может быть передан в систему управления приводом или систему верхнего уровня, которая формирует командные сигналы для электропривода, для оперативной реакции на возникшую ситуацию.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. RU 2273944 С2. Система контроля работы бесщеточных двигателей 10.04.2006, бюл. №10.

2. ЕР 1356583 A1. SYSTEME DE CONTROLE DE MOTEURS SANS BALAIS, 13.10.2010. Bulletin 2010/41.

3. RU 2475933 С2. 20.03.2012. Бюл. №8. Четырехтактный реверсивный распределитель импульсов для управления шаговым двигателем с автоматической коррекцией одиночных ошибок.

4. RU 2638522 С2. 14.12.2017. Бюл. №35. ШАГОВЫЙ ЭЛЕКТРОПРИВОД.

5. A4989-Datasheet.pdf, Inc. www.allegromicro.com, 2020.

6. ТМС262 DATASHEET (Rev. 2.14/2016-JUL-14). www.trinamic.com, 2020.

7. RU 2738348, бюл. №35, 11.12.2020. Способ контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме, и устройство для его осуществления.

8. Емельянов А.В., Шилин А.Н. Шаговые двигатели: учебное пособие. ВолгГТУ. Волгоград, 2005. - 48 с.

9. Одновибратор на D-триггерах, РАДИО 1984, №7.

10. https://www.analog.com/media/en/training-seminars/design-handbooks/Op-Amp-Applications/Section2.pdf, 2020.

11. https://www.infineom.com/cms/en/product/power/mosfet/20v-100v-n-chanel-smal-power-mosfet/irlml0060/, 2020.

12. https://www.allegromicro.com/~/media/Files/Datasheets/ACS724-Datasheet.ashx, 2020.

13. https://www.melexis.com/-/media/files/documents/datasheets/mlx91206-datasheet-melexis.pdf, 2020.

14. http://ww1.microchip.com/downloads/en/DeviceDoc/mic7211.pdf, 2020.

15. Технические условия бК0.347.443-03ТУ.

16. The Engineering Staff of TEXAS INSTRUMENTS INCORPORATED Semiconductor Group The TTL Data Book for Design Engineers. Second Edition TEXAS INSTRUMENTS INCORPORATED 1981 Printed in U.S.A Third Printing LCC4112 74062-116-AI.

17. Технические условия АЕЯР.431200.208-07ТУ.

18. Технические условия АЕЯР.431200.208-08ТУ.

19. Алексенко А.Г., Коломбет Е.А., Стародуб Г.И. Применение прецизионных аналоговых ИС. - М.: Радио и связь, 1981. - 224 с.

20. MCP6V01/2/3 300 μA, Auto-Zeroed Op Amps 22058c.pdf www.microchip.com/product/en/MCP5V02, 2020.

21. А.Н. Денисов, Ю.П. Фомин, В.В. Коняхин, Р.А. Федоров / Под общ. ред. А.Н. Саурова / Библиотека функциональных ячеек для проектирования полузаказных микросхем серий 5503 и 5507 Москва: Техносфера, 2012. - 304 с., ISBN 978'5'94836'332'5.

22. www.spectrum-soft.com, 2020.

23. Амелина М.А., Амелин С.А. Программа схемотехнического моделирования Micro-Cap. Версии 9, 10. - Смоленск, Смоленский филиал НИУ МЭИ, 2013. - 618 с., ил.

* При использовании ссылок на интернет-ресурсы указывается год обращения.

Изобретение относится к области электротехники и может быть использовано для контроля работы шагового привода, содержащего двухобмоточный шаговый двигатель (ШД), работающий в полношаговом режиме. Техническим результатом применения предлагаемого решения будет возможность осуществлять непрерывный, независимый мониторинг работы электропривода и оперативный автоматизированный контроль потери шаговым электроприводом синхронизации при помощи средств телеметрического контроля. Для решения этой задачи во время работы ШД непрерывно измеряют токи в каждой обмотке, формируют два сигнала напряжения, соответствующие току в каждой обмотке, сравнивают их с заданными верхним и нижним пороговыми значениями и формируют четыре первичных логических сигнала. В зависимости от полученных значений первичных логических сигналов формируют четыре вторичных логических сигнала, по полученным значениям которых формируют сигнал ступенчатого напряжения, каждое стационарное значение которого соответствует одному из четырех возможных состояний установившихся значений токов в обмотках шагового двигателя. А если значения всех четырех вторичных логических сигналов одновременно имеют значение логического «0», формируют стационарное значение сигнала ступенчатого напряжения, соответствующее этому переходному состоянию электропривода. По окончании переходного состояния электропривода на каждом текущем шаге запоминают значения четырех первичных логических сигналов, а их значения на каждом следующем шаге по окончании следующего переходного состояния электропривода сравнивают с их предшествующими значениями и, если эти значения совпадают, формируют логический сигнал, свидетельствующий о потере шаговым приводом синхронизации, и формируют стационарное значение сигнала ступенчатого напряжения, соответствующее потере шаговым приводом синхронизации. Функциональная схема реализующего предлагаемый способ устройства для контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме, приведена на фиг. 2. 2 н. и 5 з.п. ф-лы, 9 ил.

1. Способ контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме, включающий измерение параметров электропитания шагового двигателя и формирование сигнала ступенчатого напряжения, позволяющего контролировать работу электропривода, для чего во время работы шагового двигателя непрерывно измеряют токи в каждой обмотке, формируют два сигнала напряжения, соответствующие току в каждой обмотке, сравнивают их с заданными верхним и нижним пороговыми значениями и формируют четыре первичных логических сигнала так, что первый из них принимает значение логической «1», если сигнал напряжения, соответствующий току в обмотке А, превосходит заданное верхнее пороговое значение, и значение логического «0» в противном случае, второй из них принимает значение логической «1», если сигнал напряжения, соответствующий току в обмотке В, превосходит заданное верхнее пороговое значение, и значение логического «0» в противном случае, третий из них принимает значение логической «1», если сигнал напряжения, соответствующий току в обмотке А, имеет значение ниже заданного нижнего порогового значения, и значение логического «0» в противном случае, четвертый из них принимает значение логической «1», если сигнал напряжения, соответствующий току в обмотке В, имеет значение ниже заданного нижнего порогового значения, и значение логического «0» в противном случае, в зависимости от полученных значений первичных логических сигналов формируют четыре вторичных логических сигнала таким образом, что первый из них принимает значение логической «1», если первый и второй первичные логические сигналы имеют значение логической «1», и значение логического «0» в противном случае, второй из них принимает значение логической «1», если первый и четвертый первичные логические сигналы имеют значение логической «1», и значение логического «0» в противном случае, третий из них принимает значение логической «1», если третий и четвертый первичные логические сигналы имеют значение логической «1», и значение логического «0» в противном случае, четвертый из них принимает значение логической «1», если второй и третий первичные логические сигналы имеют значение логической «1» и значение логического «0» в противном случае, в зависимости от полученных значений вторичных логических сигналов формируют сигнал ступенчатого напряжения, каждое стационарное значение которого соответствует одному из четырех возможных состояний установившихся значений токов в обмотках шагового двигателя, а если значения всех четырех вторичных логических сигналов одновременно имеют значение логического «0», формируют стационарное значение сигнала ступенчатого напряжения, соответствующее этому переходному состоянию электропривода, отличающийся тем, что по окончании переходного состояния электропривода на каждом текущем шаге запоминают значения четырех первичных логических сигналов, а их значения на каждом следующем шаге по окончании следующего переходного состояния электропривода сравнивают с их предшествующими значениями и, если эти значения совпадают, формируют логический сигнал, свидетельствующий о потере шаговым приводом синхронизации, и формируют стационарное значение сигнала ступенчатого напряжения, соответствующее потере шаговым приводом синхронизации.

2. Способ контроля работы электропривода по п. 1, отличающийся тем, что заданные верхнее и нижнее пороговые значения выбирают в соответствии с соотношениями

Vref1=(V+)-k((V+)-(V-)),

Vref2=(V-)+k((V+)-(V-)),

где Vref1 - заданное верхнее пороговое значение,

Vref2 - заданное нижнее пороговое значение,

(V+) - напряжение, соответствующее стабилизируемому стационарному положительному значению уровня тока в обмотках шагового двигателя (ШД),

(V-) - напряжение, соответствующее стабилизируемому стационарному отрицательному значению уровня тока в обмотках ШД,

k - положительный коэффициент, значение которого выбирается при проведении заводских или лабораторных испытаний электропривода из диапазона 0,01…0,05.

3. Способ контроля работы электропривода по п. 1, отличающийся тем, что логический сигнал, свидетельствующий о потере шаговым приводом синхронизации, передают в другую систему, контролирующую работу электропривода.

4. Устройство для контроля работы электропривода на основе двухобмоточного шагового двигателя, работающего в полношаговом режиме, содержащее блок формирования ступенчатого напряжения, два датчика тока, два источника опорного напряжения и четыре компаратора, причем первые входы первого и третьего компараторов соединены с выходом датчика тока в обмотке А, первые входы второго и четвертого компараторов соединены с выходом датчика тока в обмотке В, вторые входы первого и второго компараторов соединены с выходом первого источника опорного напряжения, а вторые входы третьего и четвертого компараторов соединены в выходом второго источника опорного напряжения, выходы первого, второго, третьего и четвертого компараторов соединены соответственно с первым, вторым, третьим и четвертым входами блока формирования ступенчатого напряжения, отличающееся тем, что в него введен блок обнаружения потери синхронизации с пятью входами и двумя выходами, причем первый, второй, третий и четвертый входы блока обнаружения потери синхронизации соединены соответственно с выходами первого, второго, третьего и четвертого компараторов, а его пятый вход - с выходом блока формирования ступенчатого напряжения, первый выход блока обнаружения потери синхронизации является дискретным выходом устройства для контроля работы электропривода, а второй выход - его телеметрическим выходом.

5. Устройство … по п. 4, отличающееся тем, что блок обнаружения потери синхронизации содержит аналоговый компаратор, третий источник опорного напряжения, формирователь импульсов, регистр хранения, цифровой компаратор, D-триггер и сумматор, причем первый вход аналогового компаратора соединен с пятым входом блока обнаружения потери синхронизации, а его второй вход с выходом третьего источника опорного напряжения, выход аналогового компаратора соединен с входом формирователя импульсов, первый и второй выходы которого соединены соответственно с тактовыми входами D-триггера и регистра хранения, входы данных регистра хранения и входы секции В цифрового компаратора соединены соответственно с первым, вторым, третьим и четвертым входами блока обнаружения потери синхронизации, выходы регистра хранения соединены с соответствующими входами секции А цифрового компаратора, выход которого соединен с входом данных D-триггера, прямой выход которого является дискретным выходом устройства для контроля работы электропривода и соединен с первым входом сумматора, второй вход которого соединен с пятым входом блока обнаружения потери синхронизации, а его выход является телеметрическим выходом устройства для контроля работы электропривода.

6. Устройство … по п. 4, отличающееся тем, что блок обнаружения потери синхронизации содержит два логических элемента 2ИЛИ, логический элемент 2И, формирователь импульсов, регистр хранения, цифровой компаратор, D-триггер и сумматор, причем входы первого логического элемента 2ИЛИ соединены с первым и вторым входами блока обнаружения потери синхронизации, входы второго логического элемента 2ИЛИ соединены с третьим и четвертым входами блока обнаружения потери синхронизации, выходы обоих логических элементов 2ИЛИ соединены с входами логического элемента 2И, выход которого соединен с входом формирователя импульсов, первый и второй выходы которого соединены соответственно с тактовыми входами D-триггера и регистра хранения, входы данных регистра хранения и входы секции В цифрового компаратора соединены соответственно с первым, вторым, третьим и четвертым входами блока обнаружения потери синхронизации, выходы регистра хранения соединены с соответствующими входами секции А цифрового компаратора, выход которого соединен с входом данных D-триггера, прямой выход которого является дискретным выходом устройства для контроля работы электропривода и соединен с первым входом сумматора, второй вход которого соединен с пятым входом блока обнаружения потери синхронизации, а его выход является телеметрическим выходом устройства для контроля работы электропривода.

7. Устройство для контроля работы электропривода по п. 4 или 5, отличающееся тем, что формирователь импульсов выполнен по схеме трех последовательно соединенных одновибраторов, причем вход первого одновибратора является входом формирователя импульсов, а его инверсный выход является первым выходом формирователя импульсов и соединен с входом второго одновибратора, инверсный выход которого соединен с входом третьего одновибратора, прямой выход которого является вторым выходом формирователя импульсов.

| СПОСОБ КОНТРОЛЯ РАБОТЫ ЭЛЕКТРОПРИВОДА НА ОСНОВЕ ДВУХОБМОТОЧНОГО ШАГОВОГО ДВИГАТЕЛЯ, РАБОТАЮЩЕГО В ПОЛНОШАГОВОМ РЕЖИМЕ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2020 |

|

RU2738348C1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1987 |

|

SU1415401A1 |

| Устройство для обнаружения отказов в шаговом электроприводе | 1988 |

|

SU1511843A1 |

| WO 2021112125 A1, 10.06.2021 | |||

| EP 0458159 B1, 18.02.1998 | |||

| Устройство для обнаружения отказов в шаговом электроприводе | 1985 |

|

SU1319227A1 |

Авторы

Даты

2022-06-24—Публикация

2021-08-23—Подача