Изслтротение. относится к технике связи может .тьисполь; ов-змо для «р-томатичс- кой коррекции нераькомернисти группоого кремеми зэмедлония (ГВЗ) каналоп

tv.i.v.1.

Цель ;--зс5р(;темг..ч РООЫШОНИО точноти кор: ,е. цин нср-з иомерност1., ГВЗ кзна- г; ..

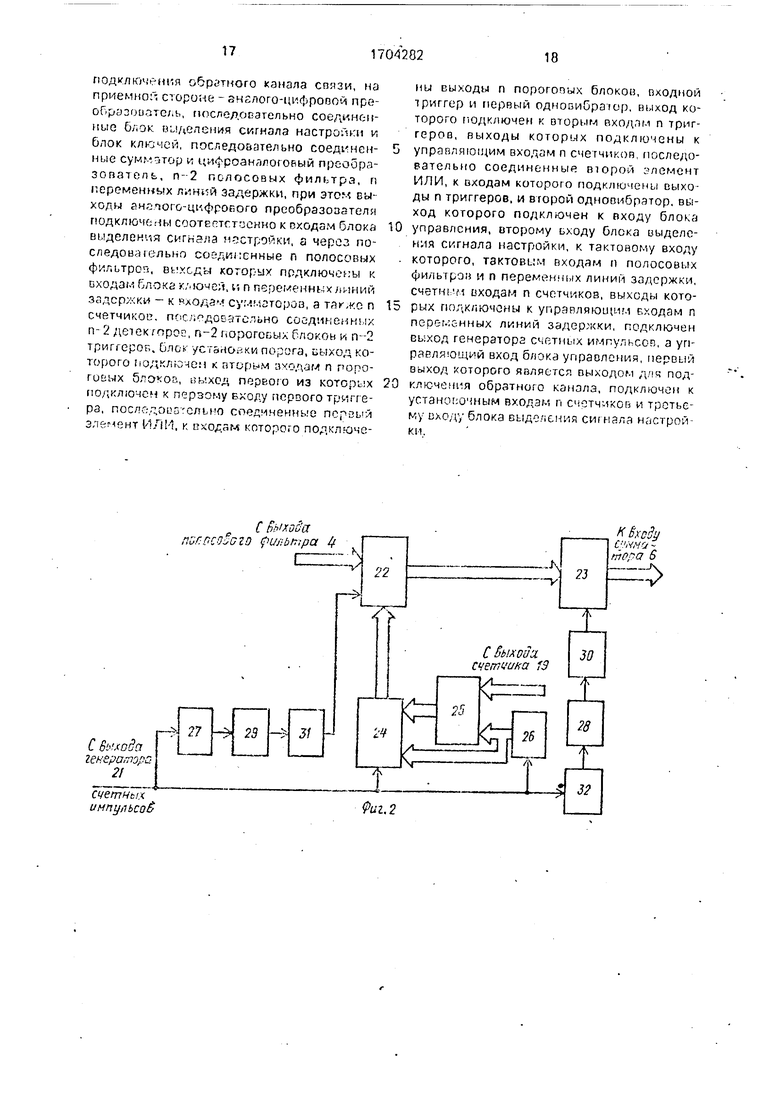

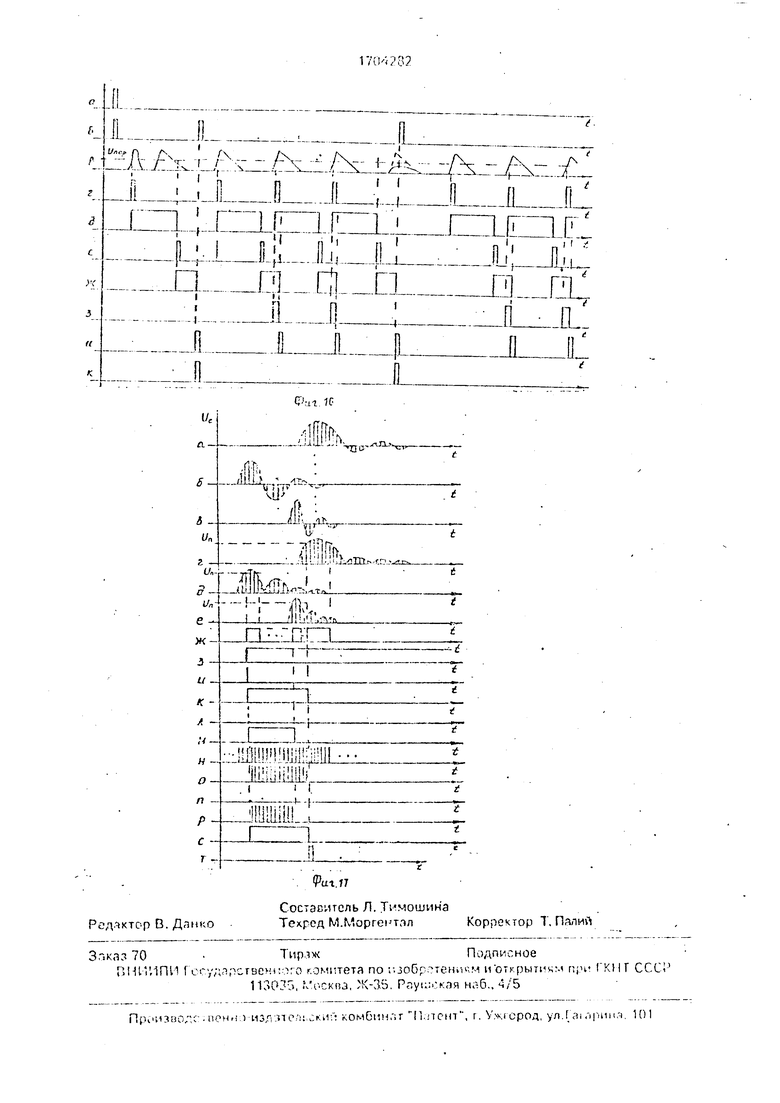

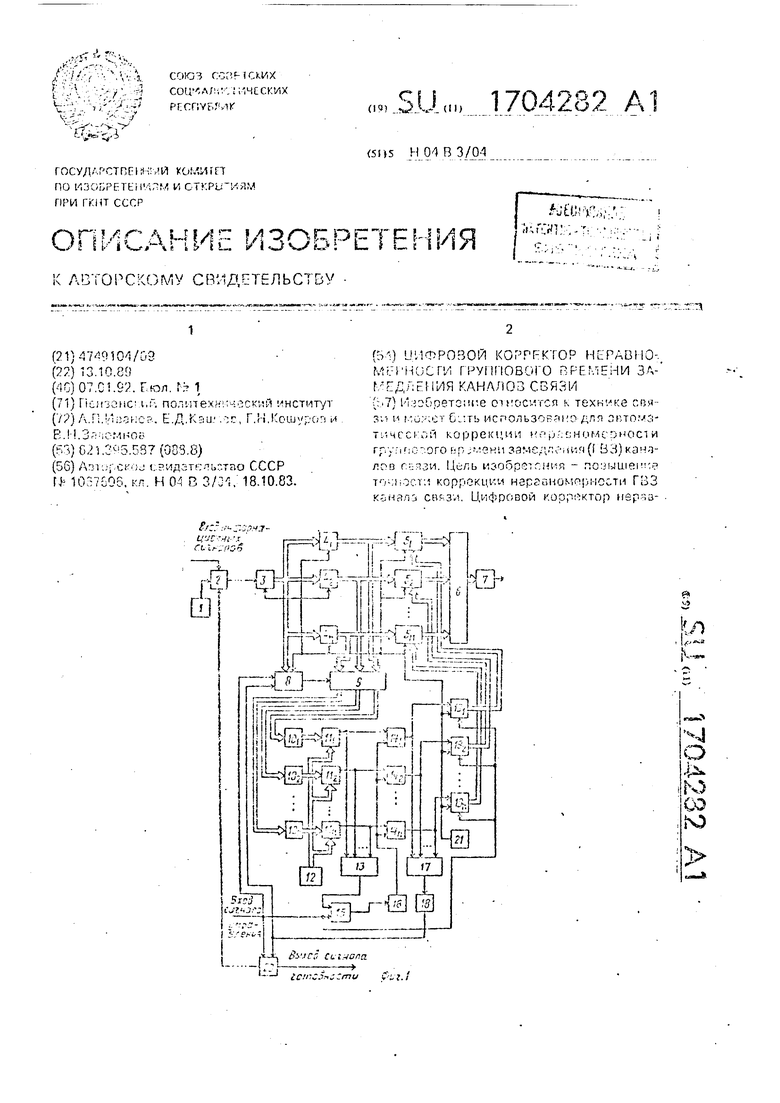

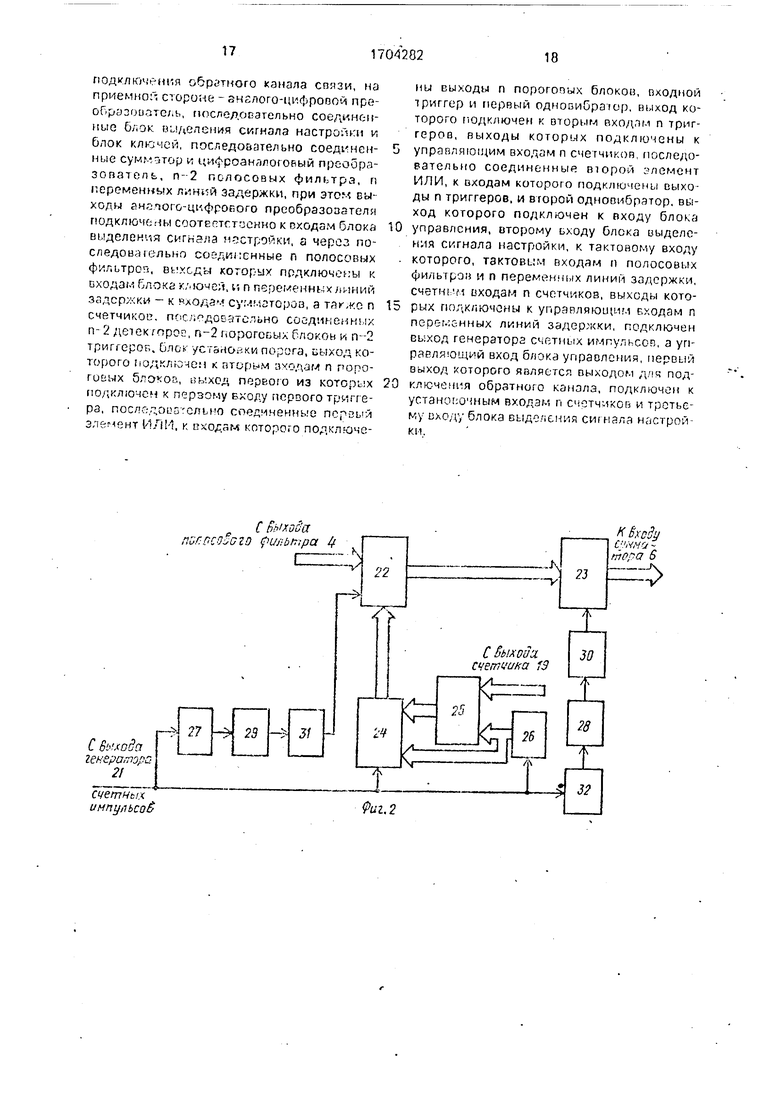

На фиг. 1 приведена структурная электрическая схема цифрового корректора неравномерности группового времени замедления каналов связи; на ф .:г. 2 - пример возможной реализации, переменкой л ..иии задержки;; на фгг. 3 ди- arpsMML рабогм п.ре.-.онне; - лимии задерки; на фиг. 4 - пример возможной реализации блокз переключений, на фиг. 5 - прем нныедиаг раму.ьд ргсоты блока переключения; на фиг. б, 7 - БОЗМОЖНОЙ реализации бг.пк.я упо.чялечит и срегиенные диаграммы ею работы соответственно; на фиг. 8- пр . мер Г озмочно реализации блока ьыд лсмия сигнала насфопкд БВС1/); на фиг. 8-11 - примеры ре-плизАЦми узлоз Зло- ка выделения сигнала мэстройки: nopoiono- го блока (ЛБ), Tfifif- -jp-a ьссмени запрета (ТВЗ), анплиозторп импульсных откпнкоа (АИС): нл фиг. 12 - гременигнс дсзграммы .iK Г; ;лли5атора; на ф-иг. 13. 14 - примеры резли: л,- ч счетшка количества

ИМПу/:ЬСп.-1Х ОТКЛИКОВ (CKl IQ) И бПОКЭ СЫдочи си; млла рпзрошония (53СР); на фиг, 15, 16 - времгннне лнзгозммн работы GBCM; на фиг. 17 - времени i re диаграммы работи .) корр-екюря псрйг.номер- ности ррсмеми ззмедлемия к налоп свчзи.. Цифровой корректор нерикно. -ерности группопого cpoi- .OHt , замед они- канала связи ссдорм;;-т (. 1} ген--глтгр t прямоуГО- S.. IIMUVT- Cfl. 2 Г -pv-ir;K 40Hl13,

ан/1-ого- цифровом (АЦП) 3. n iuv;: conw фи. -. п пор /меннмх

Г -1. Cyf- r i STC t ;: . .- ЛОгоиый проооразоватоль (ЦАП) /, блок 8 выделения сигнала настройки, блок 9 ключей, - n детекторов 10, n пороговых блоков 11, блок 12 установки порога, первый элемент

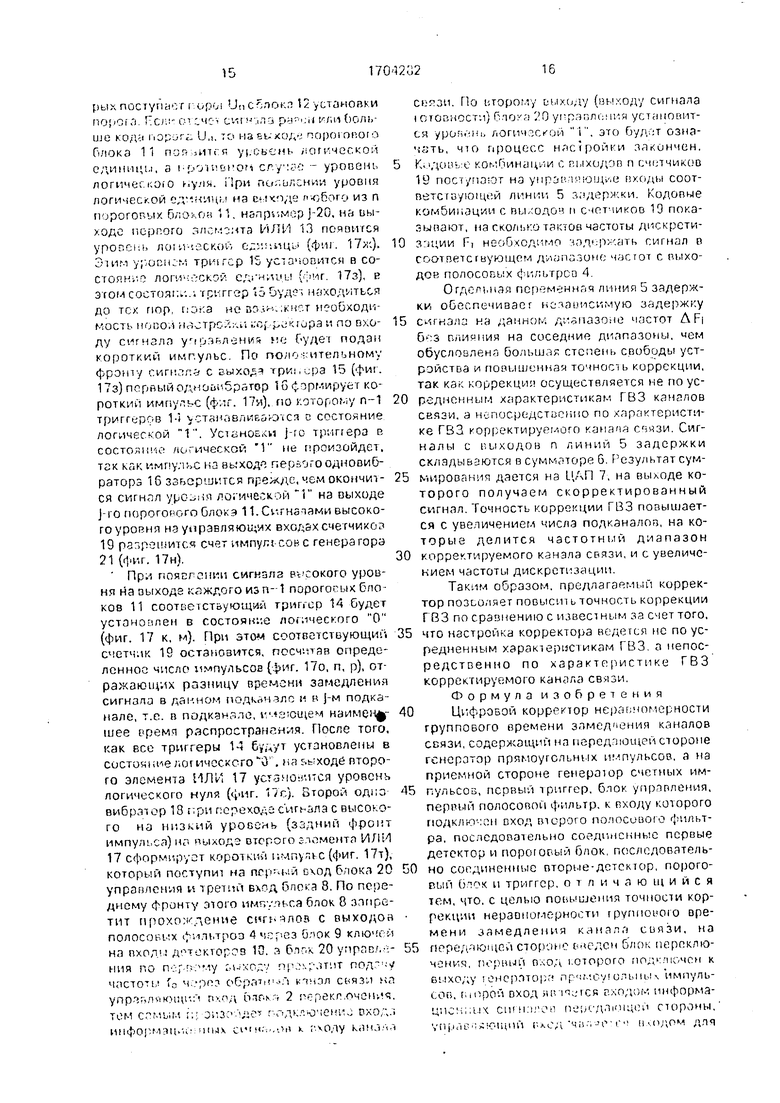

ИЛИ 13, Р. триггеров 14, входной триггер 15, перзый сдпог.ибрэтор 16, второй элемент ИЛИ 17, сторож одновибротор 18, n сметчиков 19, блок 20 управления, генератор 21 счетных импульсов соответственно на передающей и приемной сторонах, Переменная линия 5 задерхки включает в себя блок 22 памяти, буферный регистр 23, мультиплексор 24, сумматор 25, счетчик 26, два одно- вибрзтора 27 и 28, два элемента 29 и 30

задержки, дпа элемента НЕ 31 и 32, Блок 2 переключения включает в себя узкополосный фильтр (УФ) 33, выпрямитель (В) 34. сглаживающий фильтр (СФ)35, компаратор (К) 36 и коммутатор (КМ) 37. Блок 20 управленмя включает в себя триггер 38, генератор- 39 частоты fc и ключ 40. Второй вход блока 20 управления является входом установки S триггера, г первый вход блока 20 управления - входом сброса R, инперсный иыход

триггера 33 япляется вторым выходом блока 20 упрзпления (выходом сигнала готовности), а инверсный выход триггера 38 подключен к управляющему входу ключл 40Ч выход генератора 39 частоты fo - к входу

ключа 40, выход которого является порпым выходом блока 20 управления.

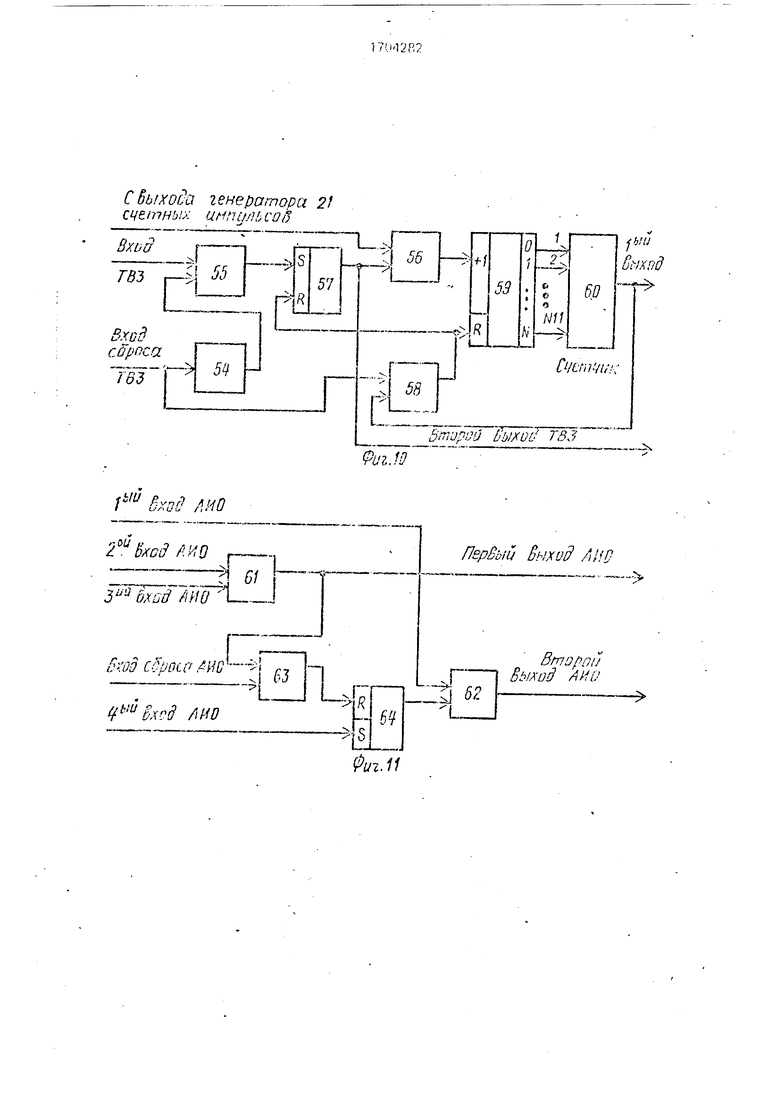

Елок 8 выделения сигнала настройки включает з себя пороговый блок (ГIB) 41, таймор 42 времени запрета (ТВЗ) таймер 43

премени охида.тия (ТВО). анализатор 44 импульсных откликов (ЛИО), смотчик 45 количества импульсных откликов (GKI40), блок 46 выдачи сигнллл pa p -1 - 1 14 (ГпВСР) и блок 47 н чзли .ой устансики Ы IV).

ПБ 41 (фиг. 9) нкл 0ч;-нм п себя к:;мплра- тор -18. блок i9 угт.-;чпикц порога, ллимент ИЛМ-НГ; Г 0, лсропй 51 и иторой 52 элементы 1Л1 . и трипгр 53. 1 РЗ -17 (-inr. 0) иключает в себя элемент НЕ 54, перпый 55 и второй 5G элементы И, триггер 57, элемент ИЛИ 58, счетчик 59 и элемент 60 сонпаде- ния,

(фиг. J1) включает в сеоя первый 61 и второй G2 елемежы И. эпомент ИЛИ G3 и триггер Б1. СКИС b включаю;1; себя счетчик 65, племенV GG совпадения и триггер 67. Счетный ь-.,. гчг-т --:::з R5 язляется входом СКИО, РХОД сС-рос.э СКИО одновременно подключен к иходам R счетчика 65 и триггера 67, выходы счетчика 65 связаны с следами элемента GG ССЕЛЗДПНИЯ, пь-ход которого по.г,./ьочен к входу R триггера 67. выход которого л шлется выходом СКИО (фиг. 13).

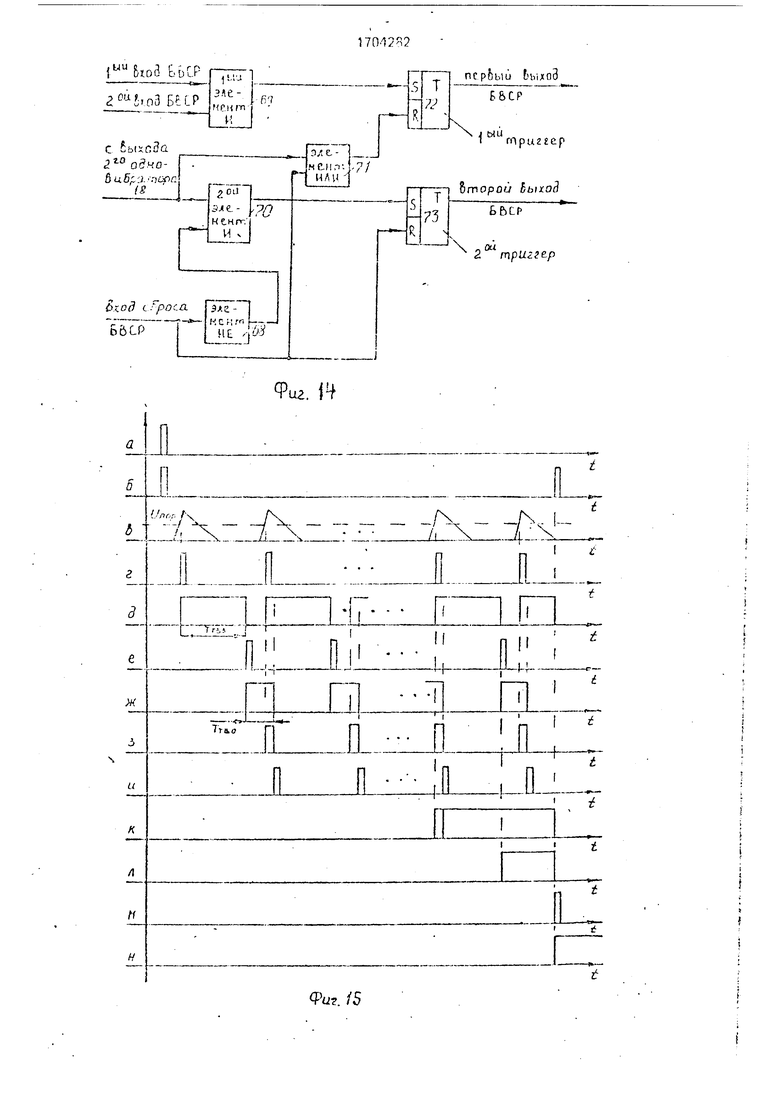

ВВСР (фиг. 1-) р.кл. очсет ь себя элемент НЕ 08, псриый 03 и втог.ой 70 элементы И, элемент ИЛИ 71 и первый 72 и Ј:урой 73 триггер -1. П- :р15ый ьход первого зг.емг.нта И 69 являет ел первым ох с дом оВСР 45, БТО- рой вход г.орсою элемента К - вторым сходом БВСР 5, в .о:од первого элемента И 63 соодинеч с входам S nsptoro триггера 72, выход которого :-.Р.ЛЛСТСЯ первом выходом оВСР 46, первое Ггыхзды второго элемента И 70 и элемента ИЛИ 71 объединены и спя- ЗЙНУ с пм/одом ьторого o/ 5 O j::6p iTopD 18 и являются управляющим в.-.одом БВСР -1G. Вход емуMT;J Hi- f/J, ьтсрс. ; зход з. ;е;. епта ИЛИ 71 и вход Р. ьторого тс::; ге;,з 73 о5ъп-

ДИНСНЬ 11 ЯВЛЯЮТСЯ НХСДОМ CUpCC i, ВЫХОД

элемента НЕ GC ссэд;1Ь сн с в орь.:,м входом второго шлемом ;} И 70, ьыход которого подключен К Г;ХОДУ S ЗТОрОГО Тр 1ГГс:ра 73.

Сумматор 6. осуичеотв/ юмд й сумми- ровзние нескольких многоразрядных слзгасг-ibix, Г:ОС уилющ ;х -i его , одио- срименпо мо,;;ет быть рег изосан с по- мощ;ло каскадного соединения типовых сумматоров двух многорззр- Дних чисел.

Бло1-: 9 ключэй может GuT; роалнзован е ииде оосокупности ДБу :-;хсловь.х гпементоз И. Первые входы элемент or. vf объединены и яоляютс.ч yrpaf-ляюи .им ачодом блока 9 клю - с-; :. Пторыа входи .-:-мтоа И соеди- мены соотг.йгственно с выходами п полосо- оых филы ров 4

Блок 12 установки порога может быть резлидопли с сиде соьокупнести К5-триггеров, устд.човочныр сходы которых при pea- лизйци1/. подг.лючаюгсх к шинам .логическою нуля или логической единицы в соотпотстпии с необходимым значением порога, и информация всегда может быть считано с выходов этих триггеров.

Рйбоо блоксп цифроаого корректора нсрзг.:|о:. рностп группового .времени замедление гснзлор си-;: рассматривается соглагл о фиг. 2.

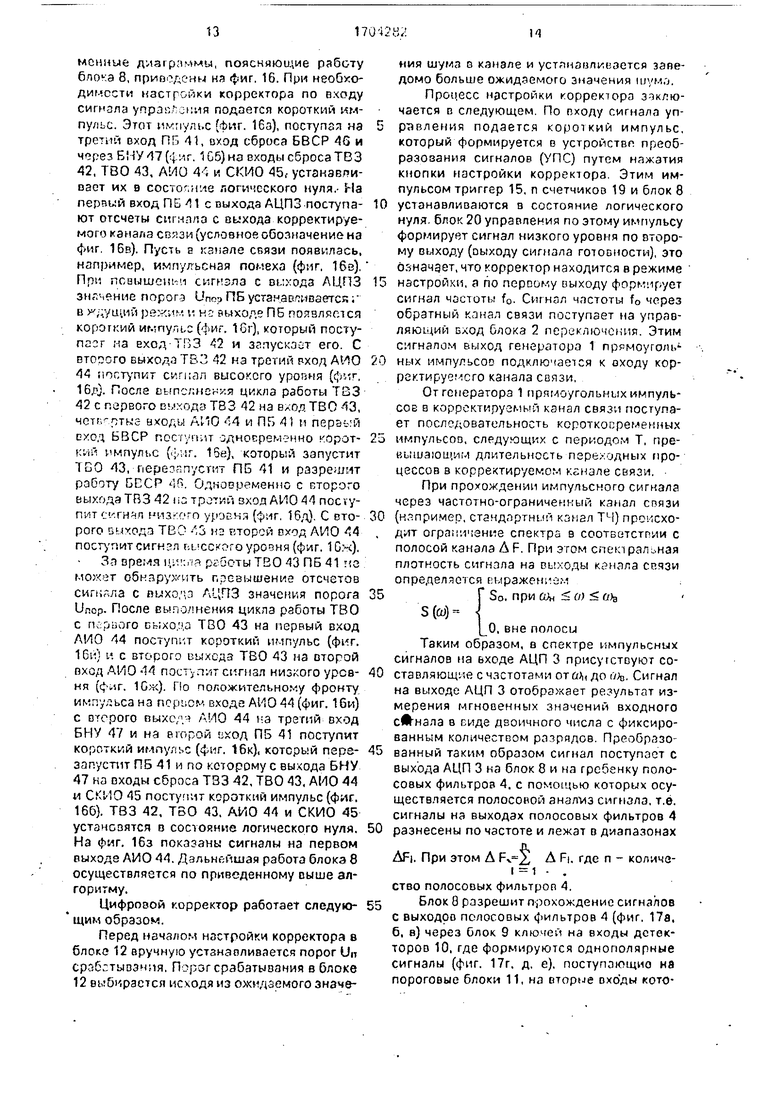

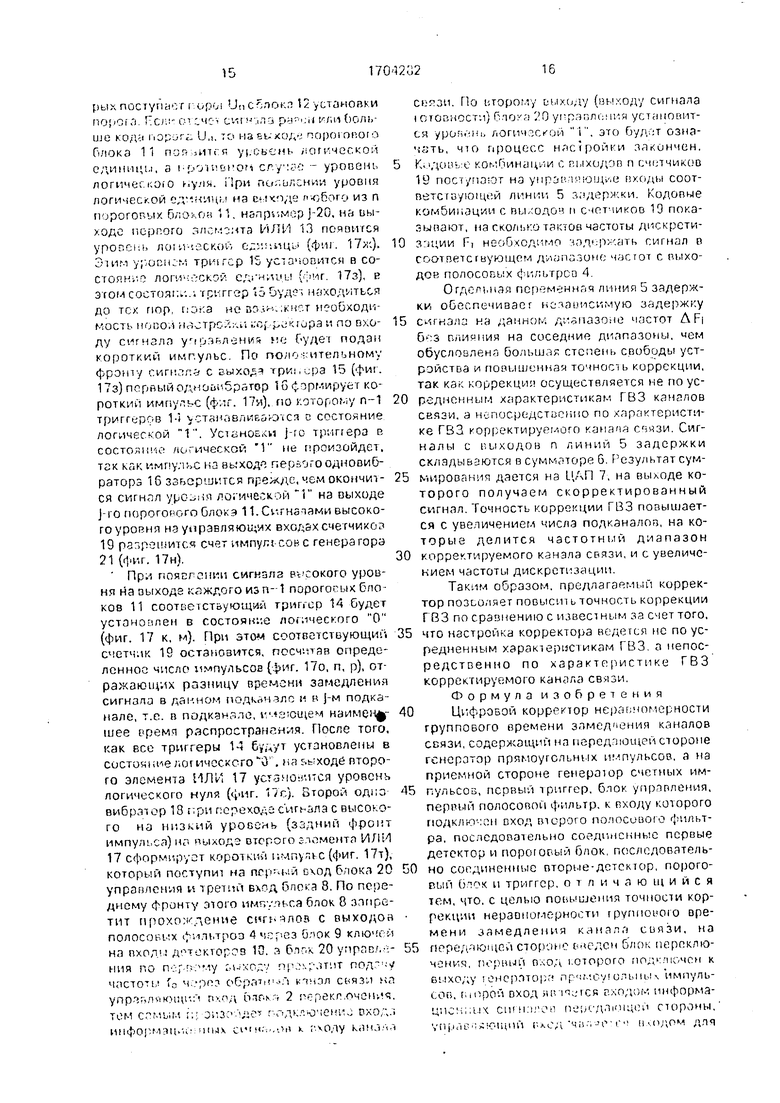

Рассмотр иг работу переменной л,mi и 5 задержки. Временные дияграммь. рчОо- ты переменной линии 5 задпржки прииоде- ны на фиг. 3. Прямоугольные импульсы со скважностью два с п -хола генератора 21 счетных импульсов (. За) поступают на вход одновибратора. на выходе которого формируются короткие импульсы, которые затем задерживаются, инвертируются и поступают на сход чтения-записи блока памяти (фиг. 30). Элемент НЕ 31 о цепи: одяоиисратор 27, элемент 29 задержки, элемент НЕ 31 (фиг. 3) необходим для согласования временных дяафамм работы однооиОрагора 27 и блока 22 памяти, чак как запись Р б..Оч 22 памяти происходит по мя переход; сигнал;; и..; чтения-записи блока 22 пзмяти с РЬ СОКСНО па низкий уровень, а чтэнио дзмных из блока ... памяти по г.игнэлу пысо.ого уровня. Длительность и задержка коротких имг.уль- .сов вмОирпются исходя п з необходимых временных соотношений д/нт работ:,: блока г:; мяги. Однсврег/. и лульсг с гене ратооэ 21 счзтных импульсоз поступают на сход счетчика 26. ма которого формируется адрес записи. Емкость счетчика 26 N устанавливается р а а ной максимчп-.ной длине ли:.-:-; задержки. Адрес ч.О ни: мируотся сумматором за с в; доо.мтпонич к адресу записи числа К (требуемап неличи.н задержки) с выхода 19 { .:.г, Зг), При низком уровне с-игна/ir на упрзвл5:ю: щем : ХОАС ..упьтиплексора 2Л :w Рлресный вход (dM-r, Зе) блока 22 па:. коммутируется адрес чтения с выхода суммглорз 25 (фи(. Зл). Данные по : ы5р нному адресу и блокЈ 22 пзмяти при к ь.: о ком урссно си; нала Тйпи :-записи поступают на вход Буферного регистра 23. В буферный регистр 23 данное зэписывпюгся {фиг. Зи) по сигналу. фop иpyeмoмy с помощью элемента НЕ 32, одно нбратора 28 и элемента 30 -вдержки (фиг. Зз) из тактовых импульсов с выхода генерлторз 21 счетных импульсов. Элемент НЕ 32 в цели: .элемент НЕ 32. одногч-:брэтор 28, эпемент задержка 30 нообходгм для обеспечения запуска одновибратрра положительным фронтом но время действия заднею фронта счетных пмпульсоз с выхода генератора 21 счетных пмлульсоа. При высоком уровне сигнала на упрааляку.дсм входе мультиплексора 24 на адресный вход блока 22 памяти поступает адрес записи с выхода счетчика (фиг. ЗР) и по сигналу чтй- ния-ззписи (фиг, 36) данные с пыхода лоло- сопо. О фильтрп 4 (фиг. Зж) злносятся по устг.сопленному адресу.

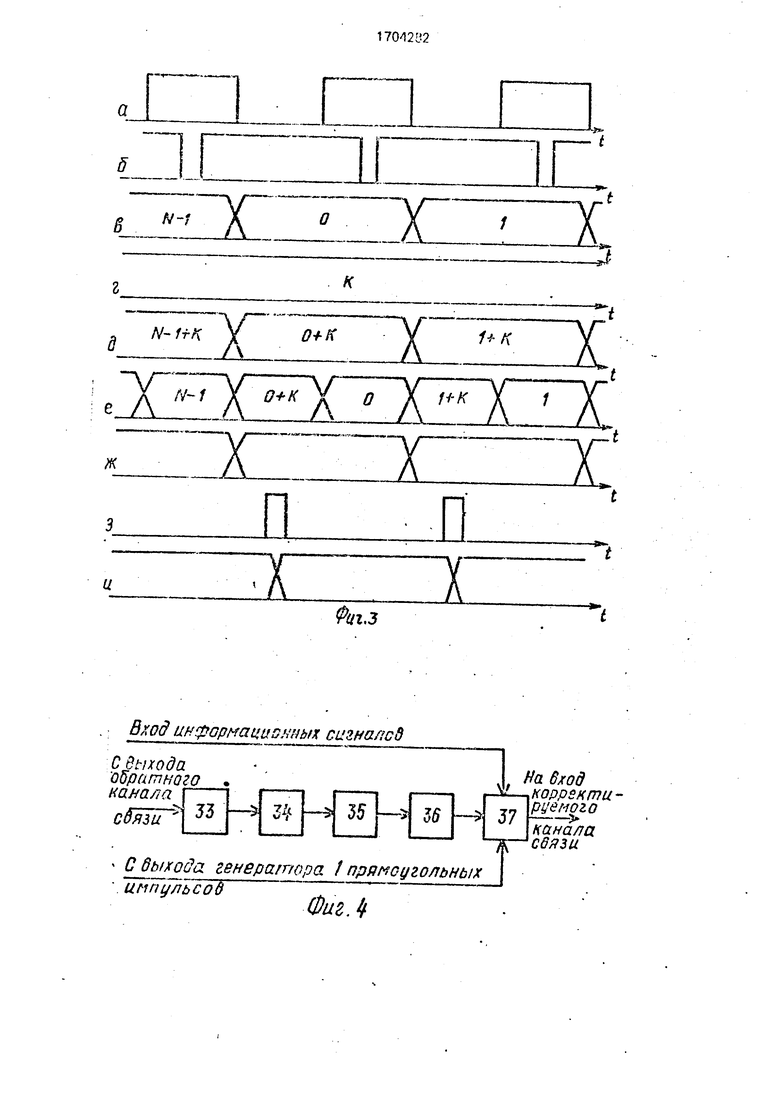

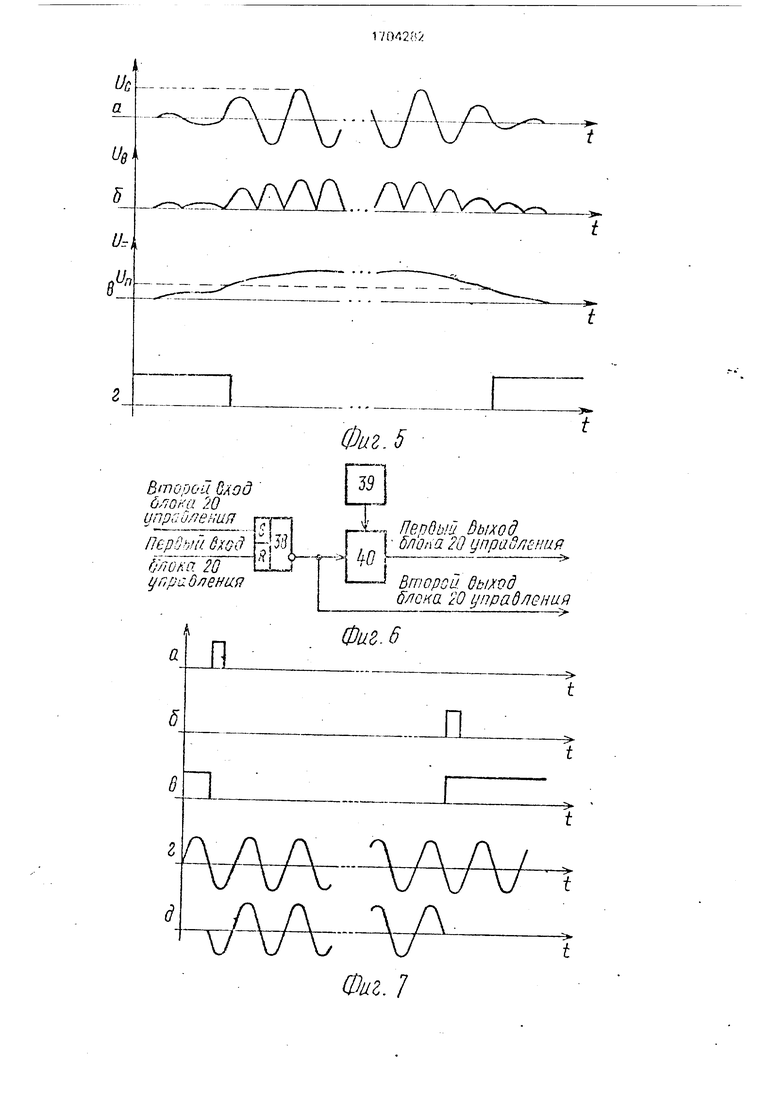

Рассмотрим работу блока 2 переключения (фиг. 1). Временные диаграммы работы

блока 2 переключения приведены мл фиг. :. .пполег Шй фильтр 33 п.|;ь.:/;яет ,13 сигнала, котор:. й поступает на его u/од (упрагыч- юн ий вход Г:лсжн 2 переключения) с первого выхода ,1 20 уирлз-пснп;) нып к а нал м,-;1зи, сигнал частотой т,(фиг. 5а). Затем порешенное р я . н не сигнала Uc с ВЫХОДУ уз; ополоснсло фильтра 33 поступает на вход выпрямителя 34. Выпрямлои- ной напряжение Ue на гн,1ходо выпрямители

34 (Ф/.) содержит пнромеч- ную состаг./;яЮЩУЮ ИЛИ ПуЛЬС ЦИ И. ЧюбЬ ИЗ ВЫПрЯМЛЕНlioro напряжения получить напряжение постоянно:о тог.а, пульсации необходимо устранить. Для этого на выхода выпрямито- ля 3 ; ьключ::н сглаживающий фильтр 35. В результат из выходе сглажпззющего фильтра 35 П0ну ,.5отсй мяпр-:/:-: ;Ние U- (фкг. 5ь). Сигнал с РП/ОДЭ сглаживающего фильтра 35 (фиг. 5в) поступает на пход компаратора 3В. Если входной сигнал ксмнэратсрз 36 меньше напряжения порога Ur, Uc/2. то на его выходе будет сигнал высокого уровня, ео.и же входной сигнал компаратор;) 3G больше напряжения порога Un Uc/2. то но его выходе будет сигнал низкого уровня. Во сремя действия сигнала низкого уровня на псрзсм входе коммутатора 37 его третий РХОД подключается к выходу, т.з. сигналы с выхода генератора 1 прямоугольных импульсов поступают на пход кор-ректируемо- ю канала снязи. Следовательно, во время дейстеия сигнала высокого уровня на пер- пом сходе коммутатор 37 его второй вход соединяется с выходом, т.е. сигналы с входа информационных сигналов поступают на вход корректируемого канала свкзм. Сигнал на выходе коммутатора 37 показан на фиг. 5г.

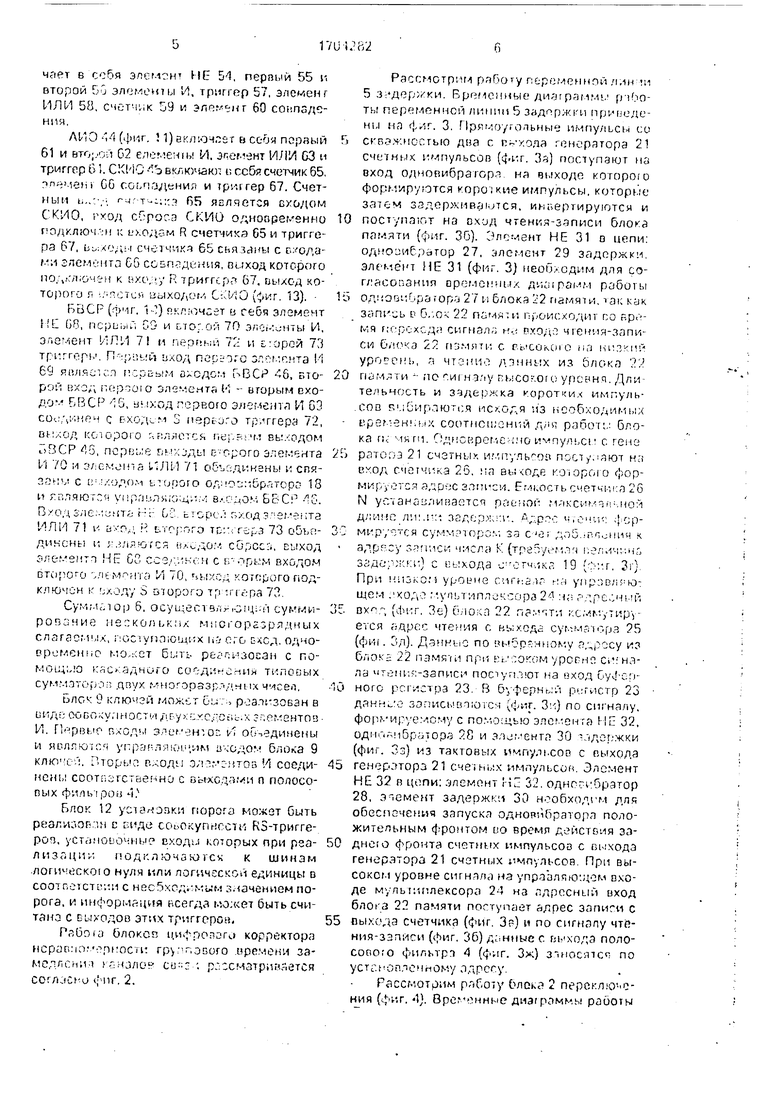

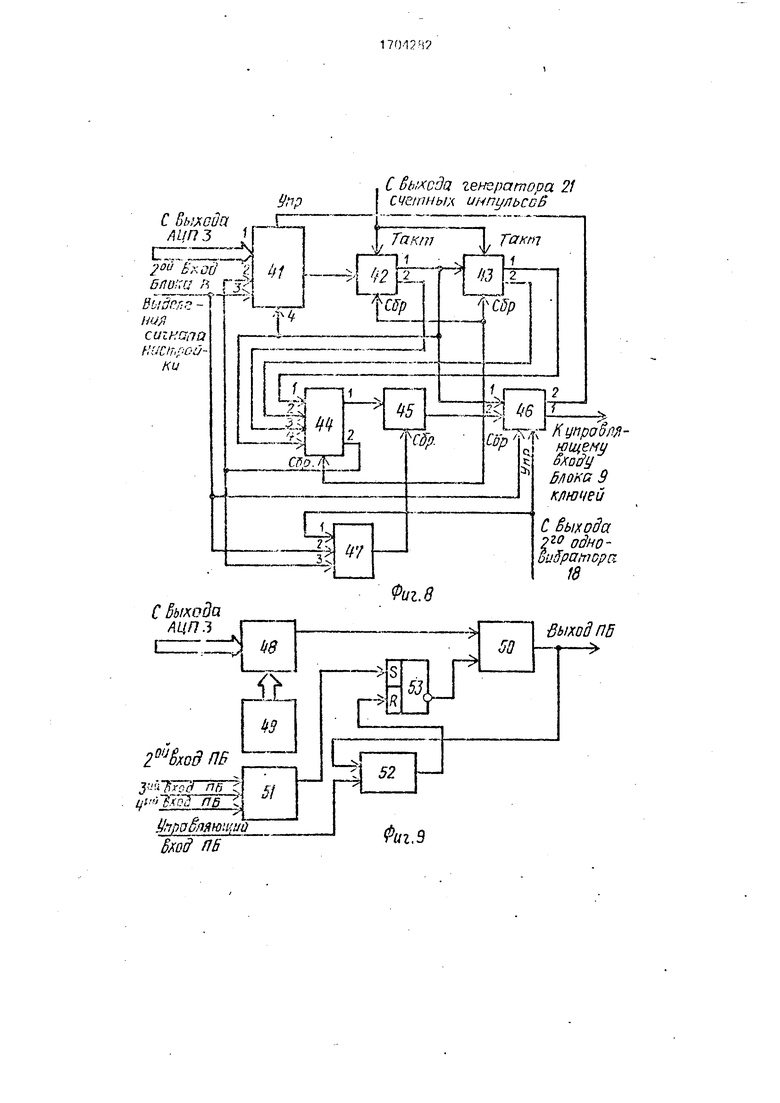

Рассмотрим работу блока 20 управления (см. фиг. 6). Временные диаграммы работы 20 управления приведены нз фиг. 7. При подаче нз второй РХОД блока 20 управления (вход сигнала управления) короткого импульса {фиг. 7а) триггер 38 устанавливается в состояние логической Г , на инверсном выходе которого будет установлен сигнал низкого урог.ня (фиг. 7в). Этот сигнал подается на управляющий вход ключа 40 и разрешает прохождение сигнала с выгода fenep,viopa 39 частоты (0 (фиг. 7г) на первый гшход блока 20 упрлпления (фиг. 7д). Ключ 40 будет находиться в открытом состоянии до тех пор, пока по первому пходу блока 20 упрапления не поступит короткий импульс (фиг. 76). Этим импульсом триггер

35 .1пгя « состояние логического О, а на i-тч-рсном выходе Судет установлен сигнал лмсокого уропмп Этим сигналом ключ -10 лакр.хтся и .мпрогит прохождений

сигнала с выходи генератора 39 частоты f(, на первый выход fviora 20 управлс-ния. При су 1C га .е cm нала тгкого уровня (фиг. 7п) на 1ЛО1/ОМ выходе блок а 20 yi Травления (выходе

сигнала ююпности) показывает, что корректор находится в режиме 1астро; :ка. При сутсшио сигнала высокого уровня (фиг. 7г.) показывает, что корректор и ,it.H в ре- . жиме Работа.

0Работа блока 8 оыдепенил сигнала на- стрсйки будет показана разГ) работы отдельных его узлов.

Рассмотрим работу ПБ 41 блока 8. Ком- nap. JTOD 18 ocyiiioci с.тяет сраанемие огсче5 тов сигнала, поступающих- с выхода АЦЛ 3, со змг:чснием порога Unop, поступающего из Блоки установки порога. На выходе компаратора 48 поясляотся результат С()звнепия, представляющий сигнал высокого уроаня,

0 ес/ш величина отсчетов сигнала с выхода АЦП 3 меньше значения пор ога Умер, и сигнал уровня, если величина отсчетов сигнала с выхода АЦП 3 больше или равна значению порога Unoj;. При необходимости

5 настройки корректора по входу сигнала уп- разления подается короткий импульс. Этот импульс поступает нз третий вход ПБ 41 (второй вход первого элемента ИЛИ 51) и через первый элемент ИЛИ 51 устанавлива0 ет три; гер 53 в состояние логической единицы. Сигнал низкого уровня, поступающий с . инверсного выхода триггера 53 на второй вход элемента ИЛИ-НЕ 50, разрешает прохождение результата сравнения с выхода

5 компаратора с последующей инверсией через элемент ИЛИ-НЕ.50 на выход ПБ. Если величина отсчетов сигнала с выхода АЦП 3 больше или равна значению порога Unop и если из выходе триггера 53 установлен

0 сигнал разрешения прохождения (сигнал низкого уровня) результата сравнения с выхода компаратора через элемент ИЛИ- НЕ 50, то на выходе элемента ИЛИ-НЕ 50 появится сигнал высокого уровня, в про5 тивном случае - сигнал низкого уровня.. Сигнал высокого уровня с выхода элемента ИЛИ-НЕ 50 од но времен но поступит на вход ТВЗ 42 и через второй элемент ИЛИ 52 на вход R триггера 53, устанавливая триггер 53

0 е состояние логического нуля.

Рассмо рим работу ТВЗ 42 блока 8 (фиг. 10). В начале настройки корректора.с выхо- дз БНУ 47 на вход сброса ТВЗ 42 поступает короткий импульс, который, по-.тупля через

5 элемент ИЛИ 53 на R-вмоди триггера 57 и считчика 59, ус танавли чет их в состояние . ого нуля. С { ычода гример,) 57 на торой г.ыход ТВЯ - 2 и iin второй вход р.торо. р элемент,) И 5Я гтоступ.чот сигнал HMjKOio уровне, лч; Mi bi п(л ич;; .1 ние импульсов тактоаой частоты Ff с выхода гене- ратора 21 счетных импульсов через второй элемент И 55 на счетный вход счетчика 59.

КОРОТКИЙ ИМПуЛЬС (С БЬ ХОД ПБ 41). ПОЯВЛЯЯСЬ на входе ТВЗ 42, через первый элемент И Г5 поступает.на вход S триггер.) 57, перевод;; триггер 57 в состояние логической единицы. Сигнал высокого уровня с выхода триггера 57 разрешззт прохождение мм- пуяьсов тактовой частоты FT через второй элемент И 56 на сметный вход счетчика. Счетчик считает импульсы тактовой, частоты Рь При достижении счетчиком 59 состояния, на которое настроен элемент 60 совпадения, с выхода ею появится короткий импульс, который поступит одновременно на персый выход ТВЗ 42 и через элемент ИЛИ 58 на R-входы счетчикз 59 и триггера 57, переводя их в состояние логического нуля. Цикл работы ТВЗ 42 повторится с поступлением следующего копоткого импульса с пы- ходэ ПБ 41 из вход ТВЗ 42.

ТВО 43 может быть реализован также как и ТВЗ 42 с той лишь разницей, что элемент совпадения настроен на другую ко: Акацию. Кс.мбинац .-и, на которые настроены элементы совпадения ТЗЗ 42 и ТВО 43, мокло определять следующим образом. Исходя из известного периода следования прямоугольных v- ,.v.ny;::.coB Т.генэраторз 1 прямоугольных импульсов определяются периоды работы ТВЗ 42 (Ттвэ) и ТВО 43 (Ттво) мз соотношения

1 - ТтвЭ + Ti80/2,

где ТТЙЗ 7/8 Т,

Следовательно, 1/4 Т. Комбинации, на которые- кзстро-зны схемы совпадения ТВЗ и Т80, вычисляются по следующим формулам

Птвз Ттвэ FI - -g- Т FT;

Птао - Ттво FT - FT,

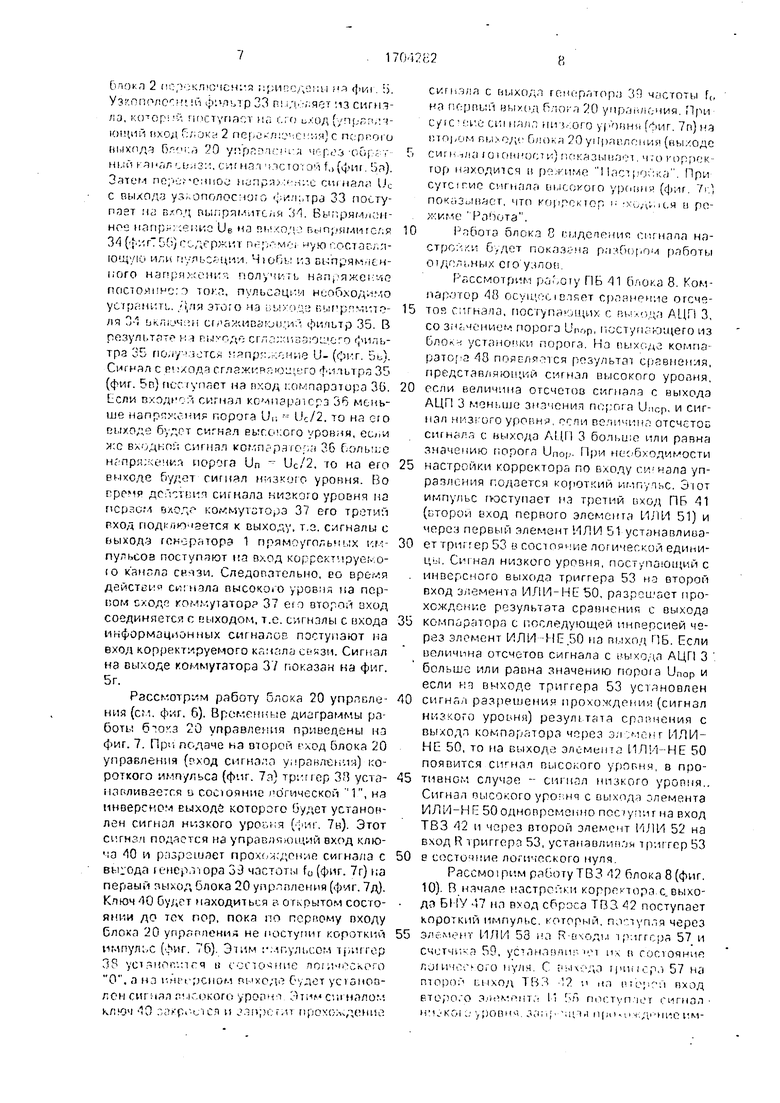

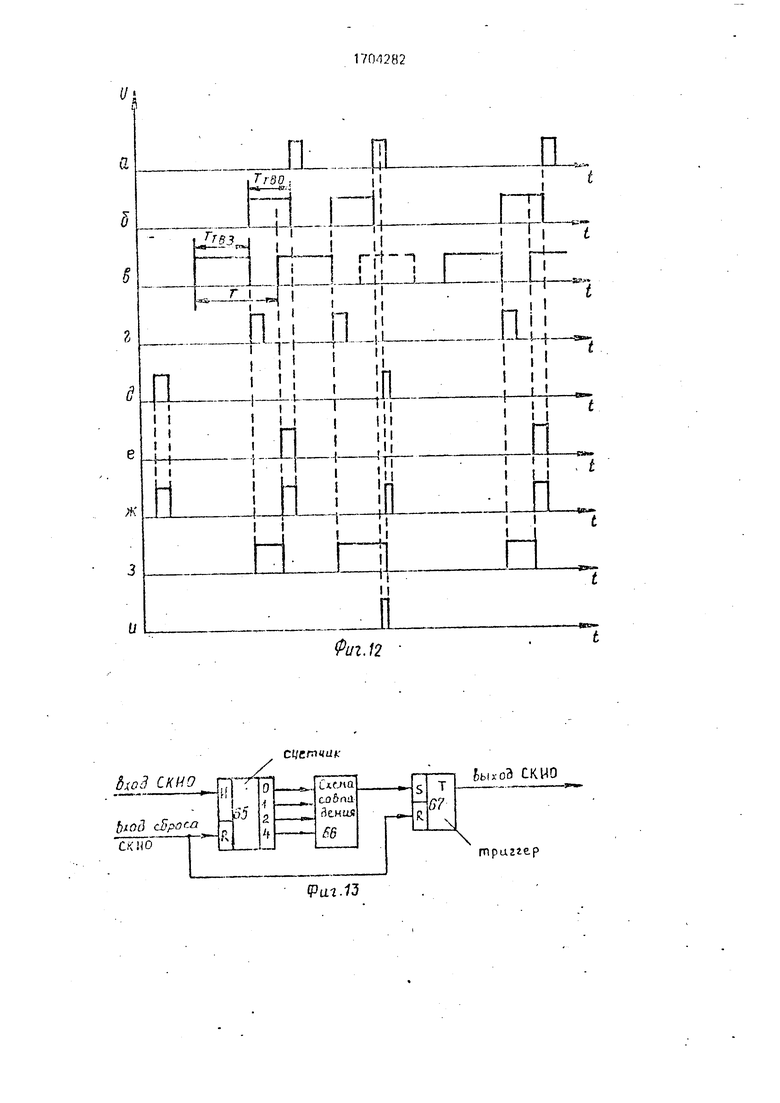

Рассмотрим работу АИО 44 блока 8 со- глпсно фиг. 11. В рем г; н кие диаграммы, поясняющие работу АИО, приведены на фиг. 12. В начале настройки корректора с выхода БНУ 47 на вход сброса АИО 44 поступает короткий импульс (фиг. 12д), который, поступая через элемент ИЛИ 63 (фиг. 12ж) на R-вход триггера 64, установит триггер 64 в состояние логического нуля. Сигнал низкого уровня с выхода триггера 64 (фиг. 12з), поступая на второй вход второго элемента И 62, запрещает прохождение сигнала с пер- сого выхода ТВО 43 (первый вход АИО) (фиг. 12.а) на второй выход АИО (фиг. 12и), При поступлении с первого выхода ТВЗ на четвертый сход сигнала высокого уровня (фиг. 12г) триггер 64 установится о состояние логической единицы. Сигнал высокого уровня с выхода триггера G4 (фиг. 12л). поступая на оторой вход второго элемента И 62, разрешает прохождение сигнала с первого выхода ТВЗ 42 (фиг. 12а) (первый пход АИО) на второй ьыход АИО (фиг. 12и). На втором выходе АИО (фиг. 12и) будет сигнал высокого уровня только при условии, что-на выходе триггера 64 (второй вход второго эле0 мента И 62) и на первом пходе АИО (первый вход второго элемента И 62) одновременно присутствуют сигналы высокого уровни (фиг. 12з и фиг, 12о). При одновременном поступ-. лении на второй и третий пходы АИО сигналов

5 высокого уровня (фиг. 126 и фиг, 12в)с выхода первого элемента И 61 сигнал высокого уровня поступит на первый выход АИО (фиг. 12е) и, поступая через элемент ИЛИ G3 нэ R-ьход триггера 64 (фиг. 12ж), установи

0 триггер 64 в состояние логического нуля.

Рассмотрим работу СКИО 45 блока О согласно фиг. 13. В начале настройки кор- peKiOpa с выхода БНУ 47 на вход сброса СКИО 45 поступает короткий импульс, ксго5 рый устанавливает счетчик С5 и триггер 67 в состояние логического нуля. Счетчик 65 будет считать импульсы, которые поступают на его счет ими вход с иходз СКИО 45. При достижении счетчиком 65 состояния, нз ко0 торое настроен элемент об совладения, с выхода его появится сигнал высокого уровня, который поступит на вход S триггера 67 и установит триггер 67 в состояние логической единицы. С выхода триггера 67 сигнал

5 высокого уровня поступает на выход СКИО 45. При появлении сигнала сысокого уровня на входе сброса СКИО 45 счетчик 65 и триггер 67 установятся в состояние логическою нуля и с выхода триггера 57 на выход СКИО

0 45 будет поступать сигнал низкого урог.ня. Комбинация, на которую настраивается эпе- мент 66 совпадения, в СКИО 45 выбирается из количества импульсных откликов, необходимых для анализа. Пусть анализируются

5 Р импульсных откликов. Тогда комбинация К, на которую будет настроен элемент 66 совпадения, будет следующей: К -- Р-1, так как АИО 44 начинает анализ импульсных откликов, начиная со второго импульсного

О отклика, приходящих из канала связи после начального запуска. .

Рассмотрим работу БВСР 46 согласно фиг. 14, В начале настройки корректора на вход сброса БВСР поступает короткий им5 пульс, который установит первый 72 и второй 73. триггеры в состояние логического нули. На первый и второй выходы БВСР поступают сигналы низкого уровня с выходов первого 72 и второго 73 триггеров. В момент поступления импульса с первого выходя ТКЗ 42 но nopusjii ьход ЬВСР и при наличии curn.via высокого уроки я, поступающего г. р.ихрда СК.ИО 45 на второй вход БВСР, с пмхода п :рг{ого элемента И 69 на вход S первого тр лпор.-) 72 поступит им- пульс. УотогМ М установит первый триггер 72 в состояние лиги1 : сек о и единицы. На пер- пый выход Б6СР с выходч первого триггера 72 будет поступать сигнал высокого уровня. В момент поступления на управляющий вход БВСР .ca с выхода оторого одно- вибрптора 18 с выхода элемента ИЛИ 71 на R-пход борзого триггера 72 и с выхода второго элемента И 70 на S вход второю триггера 73 поступят импульсы, которые установят первый триггер 72 в состояние ло ич ского нуля и второй триггер 73 в состояние логической единицы. С выхода первого триггера 72 на первый РЫХОД БВСР будет поступать сигнал низкого уровня, а с выход второго триггера 73 на второй выход БВСР --.сигнал высокогоуроаня. Цикл работы БВСР повторился, если нз вход сброса БВСР с вход3 сигналя управления вновь подать импульс.

ВНУ может бить реализован в виде трехпходового элемента ИЛИ.

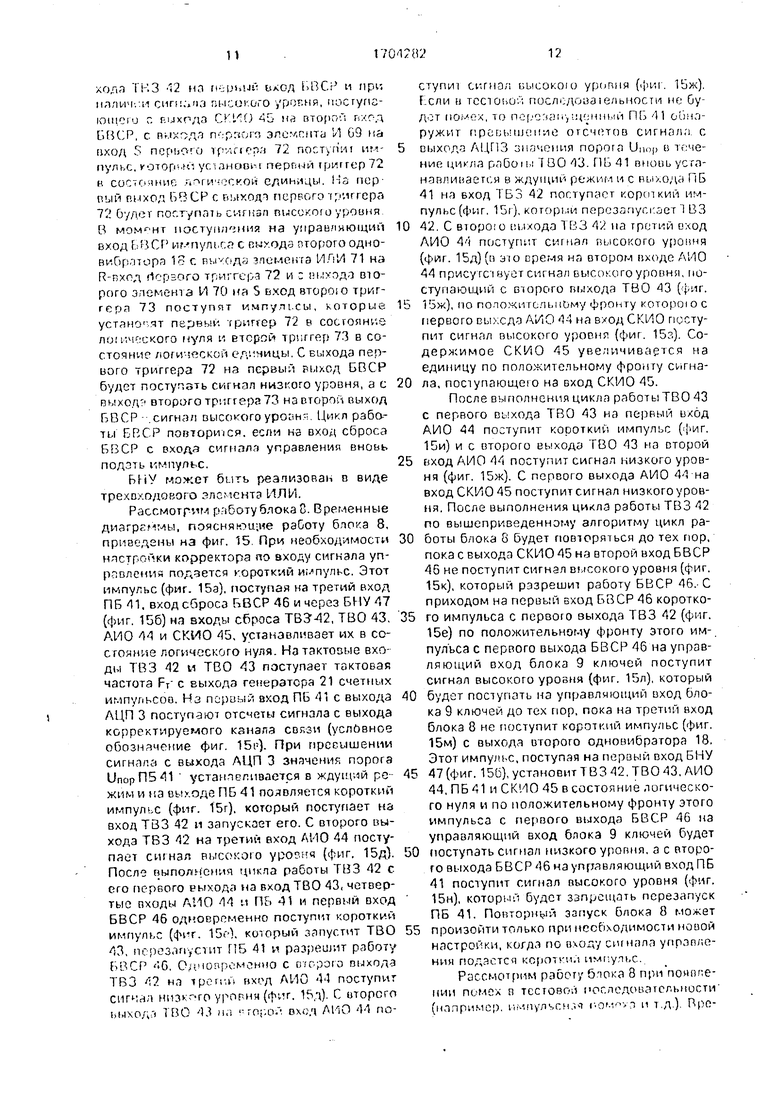

Рассмотрим работу блока 8. Временные диагргнмы. поясняющие работу блока 8, приведены нз фиг. 15. При необходимости нлстройки корректора по входу сигнала управления подается короткий импульс. Этот импульс (фиг. 15а), поступая на третий вход ПБ 41. вход сброса БВСР 46 и через Б НУ 47 (фиг. 156) на входы сброса ТВЗ--42, ТВО 43, At/10 Л4 и СШО 45, устанавливает их в состояние логического нуля. На тактовые входы ТВЗ 42 и ТВО 43 поступает тактовая частота FT с выхода генератора 21 счетных импульсов. Нз первый вход ПБ 41 с выхода АЦП 3 поступают отсчеты сигнала с выхода корректируемого канала с ВЕЗИ (условное обозначение фиг. 15i;). При превышении сигнала с выхода АЦП 3 значения порога ипорП541 устанлег.ивается в ждущий рс жим и на выходе ПБ 41 появляется короткий импульс (фиг. 15г). который поступает на вход ТВЗ 42 и запускает его. С второго выхода ТВЗ 42 на третий вход АИО 44 поступает сигнал высокою уровня (фиг. 15д). После выполнения цикла работы ТВЗ 42 с его первого выхода на вход ТВО 43, четвертые пходы АИО 44 и ПЬ А и первый вход БВСР 46 одновременно поступит короткий импульс (фиг. 15f), который запустит ТВО 43, перезапустит ПБ 41 и разрешит работу БВСР . Одновременно с спорого выхода ТВЗ 42 на ipenui вход АИО 44 поступит сигма;) низкого уровня (фиг. 15д). С второго ьыход:. ТВО 43 на г-горой вход АИО 44 поступит сигнал высокою уровня (фиг. 15ж). Р;сли н тестовой послодоиа елы-юсти не Су- дот помех, то перезапущенный ПБ 41 обнаружит превышение отсчетов сигнал,-), с выхода АЦПЗ значения порога Unop в течение цикла рабоп,: ТОО 43. ПБ 41 вновь устанавливается в ждущий режим и с выхода ПБ 41 на вход ТБЗ 42 поступает короткий импульс (фиг. 15г), который перезапускает 1 ВЗ 42. С второю выхода ТВЗ А 2 на третий сход АИО 4 4 поступит сигнал высокого уровня (фиг. 15д)(в это время нз втором входе А ИО 44 присутствует сигнал высокого уровня, поступающий с второго выхода ТВО 43 (фиг. 15ж), по положительному фронту которою с первого выхода АИО 44 на вход СКИО поступит сигнал высокого уровня (фиг. 15з). Содержимое СКИО 45 увеличивается на единицу по положительному фронту сигнала, поступающею на вход СКИО 45.

После выполнения цикла работы ТВО 43 с первого выхода ТВО 43 на первый вход АИО 44 поступит короткий импульс (фиг. 15и) и с второго выхода ТВО 43 на второй вход АИО 44 поступит сигнал низкого уровня (фиг. 15ж). С первого выхода АИО 44 на вход СКИО 45 поступит сигнал низкого уровня. После выполнения цикла работы ТВЗ 42 по вышеприведенному алгоритму цикл работы блока 8 будет повторяться до тех пор, пока с выхода СКИО 45 на второй вход БВСР

46 не поступит сигнал высокого уровня (фиг. 15к), который разрешит работу БВСР 46.-С приходом на первый вход БВСР 46 короткого импульса с первого выхода ТВЗ 42 (фиг. 15е) по положительному фронту этого импульса с первого выхода БВСР 46 на управляющий вход блока 9 ключей поступит сигнал высокого уровня (фиг. 15л), который будет поступать на управляющий вход блока 9 ключей до тех пор, пока на третий вход блока 8 не поступит короткий импульс (фиг. 15м) с выхода второго одновибратора 18. Этот импульс, поступая на первый вход Б НУ

47 (фиг. 156), установит ТВЗ 42. ТВО 43. АИО 44, ПБ41 и СКИО 45 в состояние логического нуля и по положительному фронту этого импульса с первого выхода БВСР 46 на управляющий вход блока 9 ключей будет поступать сигнал низкого уровня, а с второго выхода БВСР 46 на управляющий вход ПБ 41 поступит сигнал высокого уровня (фиг. 15н), который будет запрещать перезапуск ПБ 41. Повторный запуск блока 8 может произойти только при необходимости новой настройки, когда по входу сигнала управления подастся короткий импульс.

Рассмотрим работу блока 8 при появлении помех в тестовое последовательности (например, импулчсн.т Г-ОМОУЛ и т.д.). Времснные диаграммы, поясняющие работу блока 8, приведены ня фиг. 16. При необходимости настройки корректора по входу сигнала управления подается короткий импульс. Этот импульс (фиг. 16з), поступал на третий вход ПБ 41, сход сброса БВСР Aft и через БНУ 47 (фиг. 1С5)на входы сброса ТВЗ 42, ТВО 43, АИО 44 и СКИО 45, устанавливает их в состояние логического нуля,- На первый вход ПБ 41 с выхода АЦПЗ поступают отсчеты сигнала с выхода корректируемого канала связи (условное обозначение на фиг. 16в). Пусть а канале связи появилась, например, импульсная помеха (фиг. 16в). При повышении сигнзлз с выхода АЦПЗ значение порога Una ГТБ устанавливается; в у;;ущий режим и нг выходе ПБ появляется короткий импульс (фиг. 16г), который посту- паог на вход-ТВЗ 42 и запускает его. С второго выхода ТВЗ 42 на третий вход АИО 44 поступит сигнал высокого уропня (фиг. 16д). После выпст.нен /.я цикла работы ТВЗ 42 с первого выхода ТВЗ 42 на вход ТВО -13, чет к г от к э входы АИО ;4 и ПБ 4) и перзь:й сход БВСР поступит одновременно короткий импульс (Фиг. 16е), который запустит TGO 43, перезапустит ПБ 41 и разрешит работу СССР 4$. Одновременно с второго выхода ТВЗ 42 па третий вход АИО 44 nocvy- пит сигнал низкого уровня (фиг. 16д). С второго выхода ТВО - ;3 нэ второй сход АИО 44 поступит сиги зл высокого уровня (фиг. 1Сх).

За время цикла ргботы ТВО 43 ПБ 41 может обнаружить превышение отсчетов сигнала с выхолз АЦПЗ значения порога Unop. После выполнения цикла работы ТВО с первого сыхода ТВО 43 на первый вход АИО 44 поступит короткий импульс (фиг. 16й) и с второго выхода ТВО 43 на второй вход АИО 44 поступит сигнал низкого уровня (фиг. 1Сж). По положительному фронту импульса на псриом входа АИО 44 (фиг. 16и) с второго выхс/у- АИО 44 на третий вход БНУ 47 и на второй г;ход ПБ 41 поступит короткий импульс (фиг. 16к), который перезапустит П5 41 и по которому с выхода БНУ 47 на входы сброса ТВЗ 42, ТВО 43, АИО 44 и СКИО 45 поступит короткий импульс (фиг. 166). ТВЗ 42, ТБО 43. АИО 44 и СКИО 45 установятся в состояние логического нуля. На фиг. 16з показаны сигналы на первом выходе АИО 44. Дальнейшая работа блока 8 осуществляется по приведенному выше алгоритму.

Цифровой корректор работает следую- щим образом.

Перед началом настройки корректора в блоке 12 вручную устанавливается порог Un срабатывания. Порог срабатывания в блоке 12 выбирается исходя из ожидаемого значения шума в канале и устанавливается заведомо больше ожидаемого значения шумо.

Процесс настройки корректора заключается с следующем. По пходу сигнала упривления подается короткий импульс, который формируется в устройстве преобразования сигналов (УПС) путем нажатия кнопки настройки корректора. Этим импульсом триггер 15. п счетчиков 19 и блок 8

устанавливаются в состояние логического нуля, блок 20 управления по этому импульсу формирует сигнал низкого уровня по второму выходу (выходу сигнала готовности), это означает, что корректор находится в режиме

настройки, а по первому оыходу формирует сигнал частоты f0. Сигнал частоты f0 через обратный канал связи поступает на управляющий вход блока 2 переключения. Этим сигналом выход генератора 1 прямоуголь ных импульсоо подключается к оходу корректируемого канала связи,

От генератора 1 прямоугольных импульсов в корректируемый канал связи поступает последовательность короткопременных

импульсоо, следующих с периодом Т, превышающим длительность переходных процессов в корректируемом канале связи.

При прохождении импульсного сигнала через частотно-ограниченный канал связи

(например, стандартный канал ТЧ) проксходит ограничение спектра в соответствии с

полосой канала Д F. При этом спектральная

плотность сигнала на выходы кйнала связи

определяется выражением

Г So, при со о)

SH-

0. вне полосы

Таким образом, в спектре импульсных сигналов на входе АЦП 3 присутствуют составляющие с частотами от од, до (ih. Сигнал на выходе АЦП 3 отображает результат измерения мгновенных значений входного сигнала в виде двоичного числа с фиксированным количеством разрядов. Преобрязованный таким образом сигнал поступает с выхода АЦП 3 на блок 8 и на гребенку полосовых фильтроа 4. с помощью которых осуществляется полосовой анализ сигнала, т.е. сигналы на выходах полосовых фильтров 4

разнесены по частоте и лежат в диапазонах

AF|. При этом A A FI. где п - количз1 1- .

ство полосовых фильтров 4. Блок 8 разрешит прохождение сигналов с выходов полосовых фильтров 4 (фиг. 17а, б, в) через блок 9 ключей на входы детекторов 10. где формируются однополярные сигналы (фиг. 17г. д, е), поступающие на пороговые блоки 11, на вторые входы которык поступает ciopoi U(, сспокл 12 установки порог л. Пел: ог:.чоч ..na .-n и/;и(юль- ше коду порога U.I. то нзеь-ход порогового блока 11 погьэитг.я уровень логическом единицы, а р лчоном сг. - уровень логического ьуля. При пог.илснии уровня логической од .ници на п -обого из п пороговых блоков 11. например J-20, на ш- ходс перг.ого злсмонта ИЛИ 13 появится yponoiib логической .яицы (фиг. 17/г.). Зтим уросн;-м rpnircp IS установится в СО- СТОЯНИО ЛОГИЧЕСКОЙ СДГНИЦЫ (фмг. 17з), Р.

этом состоя ;/..; триггер 15 находиться до тех пор, пока не .,;кнст необходимость попой гмстрс/.;-.и ьорр кгора и по входу сигнала уфзьлений не будет подан короткий импульс. По положительному фронт/ сигнала с выхода трш.сра 15 (фиг. 17з) первыйоднойибратор 16 формирует короткий импульс (фиг. 17и). по которому п-1 триггеров 1-1 устанавливаются с состояние логической 1. Установки -го триггера в состояние логической 1 не произойдет, тгк как импу;и с на выходе г.ерйогоодновии- раторз 16 завершится прежде, чем окончится сигнал урезам логической 1 на выходе j-ro порогового блока 11. Сигналами высокого уровня нз управляющих входахсчетчиксз 19 разрешится счет импульсов с генератора 21 (фиг. 17н).

При появлении сигнала evcoKoro уровня на выходе каждого из п-1 порогосых блоков 11 соответствующий триггер 14 будет установлен в состояние логического О (фиг. 17 к, м). При этом соответствующий сметчик 19 остановится, посчитав определенное число импульсов {фиг. 17о, п, р), отражающих разницу времени замедления сигнала в да к ном подканале и в j-м подканале, т.е. в подканале, iv.s -сщем наимен - iuee сремл распространения. После того, как все триггеры 1-1 бу.чут установлены в состояние логического О, и a st; ходе второго элемента ИЛИ 17 устзно.пся уровень логического нуля (фиг. М г,}. Второй одпз- вибратор 18 при переходе сигнала с высокого на низкий уровень (задний фронт импульса) нг пыходэ второго гломента ИЛИ 17 сформирует короткий пмпупкс (фиг. 17т), который поступи на первый вход блока 20 управления и третий вход блока 8. По переднему франту этого нмг. /лы.а блок 8 запретит прохождение сиаолов с выходов полосовых фнльтроз 4 через блок 9 ключей на пходь детекторов 10. а блг.к 20 управления по по. :...i xo,v г р- ,..чт и т . у частоты fa чг. рг; обрачн1- ; ) ктмэл сиязи нп упр.ч; ляющ1-,й nx. v . i 2 пс-рекг.оченич. тем с г MUM i:i эизс Лле годключенио пход.

, Cnni. i,,. k, I .ХОДУ KilHjM,

соязи. По иторому оых.оду (выходу сигнала ютовяости) блок; 20 унраоломия установится логической 1. это будг;т означать, что процесс нлсгройки злкончен.

К;.дсшь:е комбинации с пыходов п сч(лчикоо 19 поступают на упрэр. входы соот- пвтстаующой линии 5 задержки. Кодовые комбинации с пыходов п счетчиков 19 показывают, на сколько тактов частоты дискрети0 змции Н необходимо .ать сигнал в соответствующем диапазоне частот с пыходов полосовых фильтрсо 4.

Отдельная переменная линия 5 задержки обеспечивает независимую задержку

5 сигнала на данном диапазоне частот Лр| влияния на соседние диапазоны, чем обусловлена большая степень свободы устройства и повышенная точность коррекции, так как коррекция осуществляется не по ус0 родненным характеристикам ГВЗ каналов связи, а непосредственно по характеристике ГВЗ корректируемого капана связи. Сигналы с выходов п линий 5 задержки складываются в сумматоре G. Результат сум5 мирования дается на ЦАП 7, на выходе которого получаем скорректированный сигнал. Точность коррекции ГВЗ повышается с увеличением числа подканалов, на которые делится частотный диапазон

0 корректируемого канала связи, и с увеличением частоты дискретизации.

Таким образом, предлагаемый корректор позволяет повысить точность коррекции ГВЗ по сравнению с известным за счет того,

5 что настройка корректора ведется не по усредненным характеристикам ГВЗ, а непосредственно по характеристике ГВЗ корректируемого канала связи.

Формула изобретения

0Цифровой корректор неравномерности группового времени замедления каналов связи, содержащий на передающей стороне генератор прямоугольных импульсов, а на приемной стороне генератор счетных им5 пульсов, первый триггер, блок управления, первый полосовой фильтр, к входу которого гюдклю -юн вход второго полосового фильтра, последовательно соединенные первые детектор и пороговый блок, последователь0 но соединенные пторые-дстсктор, пороговый блок и триггер, отличающийся тем, что. с целью повышения точности коррекции неравномерности группового времени замедления канала связи, на

5 передающей стороне сведен блок переключения, первый вход которого подключен к выходу юнсрглорг прчмоугольньк импульсов, ГмПрОЙ ВХОД ИЩЧ;. ГСК СХОДОМ ИнфОрМЭцпсн;;ич спппгсм передающей стороны,

УП|.МО : ::ОЩПЙ Г-ХОД ЧИ.. - О Г ч ПЛОДОМ ДЛЯ

подключения обратного канала связи, на приемной стороне -знглого-цифровой преобразователь, последовательно соединенные блок; выделения сигнала настройки и блок ключей, последовательно соединенные суммэтор и цифроаняяоговый преобразователь, п-2 полосовых фильтра, п переменных линий задержки, при этом выходы анйлого-цкфроБого преобразователя подключены соответственно к оходз.м блока выделения сигнала нзстройки, а через последовательно соединенные п полосовых фиг.ьтроз, выходы которых подключены к входам блоки ключей, и п переменных линий задержки - к входам сумматоров, а также п счетчиков, последовательно соединенных п- 2 детектороо, п-2 пороговых блоков и п-2 триггеров. Слск установки порога, сыход которого подключен к вторым зходам п пороговых блоков, аь .ход первого из которых подключен к первому входу первого триггера, последовательно соединенные псрзый элемент ИЛИ. к входам которого подключены выходы п пороговых блоков, входной триггер и первый одновибраюр, выход которого подключен к вторым входим п триггеров, выходы которых подключены к управляющим входам п счетчиков, последовательно соединенные второй элемент ИЛИ, к входам которого подключены выходы п триггеров, и второй одновибратор. выход которого подключен к входу блока управления, второму ьходу блока выделс- ния сигнала настройки, к тактовому входу которого, тактовым входам п полосовых фильтра и п переменных линий задержки, счетным входам п счотчикоз, выходы кото- рых подключены к управляющим сходам п переменных линий задержки, подключен выход генератора счетных импульсов, а управляющий вход блока управления, первый выход которого является выходом для под- ключения обратного канала, подключен к установочным входам п счетчиков и третьему входу блока выделения сигнала настрой- км.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1990 |

|

SU1809441A1 |

| Устройство для передачи и приема кодированного сигнала изображения | 1989 |

|

SU1686706A1 |

| Устройство для определения постоянной времени фотоприемных устройств | 1988 |

|

SU1518682A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство для сопряжения цифровой вычислительной машины с кассетным магнитофоном звукозаписи | 1983 |

|

SU1101811A1 |

| Способ А.Н.Алексеева для управления подачей воды в промывные ванны гальванических линий и устройство для его осуществления | 1987 |

|

SU1504294A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2009 |

|

RU2415465C2 |

«SI

t

UG g

UB 5

.

Второй влод блоха 20 ynpsMeHUff

Пердьтбжд Щ

rr- - -iTST-- t I V

1 q

v - w

управления

а

д

- t

f

..-, Пеодьт Выход

20 управления

W ---------

-- Второй, выход

блока 20 упрадления

Фиг. 6

п

Фиг. 1

CN

1

Vo

p -.

ff

Цг-

ГЧ

CS fh: Cc: G

& t- C- lo

12

Cj

a Ј

A

§.|Ј sЈ1- S

§ 1§3 §§gsa

С выхода генератора 2t счетных импцпь сой

lr

Јvnr л ц ft

Ilsf u-J /i flu

2°ц$хсд АИО

Т 61

3 дхйд /1ИО

5W9 С$УО(.Р .4ИВ

ёхсд AMD

-i

H 1

--- i-

1

Smupo) Ьы/ос- Т83

.„.

ПерВыи Выход

„„-N.

- 5

Bmopnu Выход АИО

-

6V faiJ1

см CD CN

Ci

ЬЬСР

ВНР

1 i- - J эле-.

исит И

fi 7

:

oil

«L- HtHpr.

И V

,n

э/е.- j.J

МС.М.-.-.17/

КСМг Ь-о™L

Фиг. I1

Фиг. 15

т

72

пс.рбыи ЬыдоЗ

з

Б&СР

N J Ы11

1 триггер Ьторой Ььпод

ЬЬСР

2ой триггер

J

.JL

|| , Г 1

Л...

m I ni г

1 i

.|.

... л..

JL

...

п

Ј .Я

а j

i.

-;.J

Ll „ 1J

,

-Cl-

i

.L

,fj.T$,

- -MijL 11г. U 1пт

4 J

I

, -no

,Т.,

VlX

-

:),r,,

-. I

JDbffljk..-bLrj ь;--ль

ilhlTLiM,П -ТгГП

{---f {-т

л Я с

Г - --

tf .

A

14 - Zl.

«13iiҐi SliZZIIZ

JliiiiiiiliL

. I

ГГ.М i JLiiim -iCULT...

-Ј

-;.. L m

Ll ( 1J,. JHT

,- - -

-Cl- П. PLl

.Л1

i

,Т.,

. t

-

-р™ zf

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| кл | |||

| Н 0 В 3/01; 18.10.83 | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Mf.:PHUCr / | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой корректор нерчз | |||

Авторы

Даты

1992-01-07—Публикация

1989-10-13—Подача